#### **HIGH VOLTAGE 3 PHASE GATE DRIVER IC**

#### **Features**

- Drives up to six IGBT/MOSFET power devices

- Gate drive supplies up to 20 V per channel

- Integrated bootstrap functionality (IRS2336(4)D)

- Over-current protection

- Over-temperature shutdown input

- Advanced input filter

- Integrated deadtime protection

- Shoot-through (cross-conduction) protection

- Undervoltage lockout for V<sub>CC</sub> & V<sub>BS</sub>

- Enable/disable input and fault reporting

- Adjustable fault clear timing

- Separate logic and power grounds

- 3.3 V input logic compatible

- Tolerant to negative transient voltage

- Designed for use with bootstrap power supplies

- Matched propagation delays for all channels

- -40°C to 125°C operating range

- RoHS compliant

- Lead-Free

#### Typical Applications

- Appliance motor drives

- Servo drives

- Micro inverter drives

- General purpose three phase inverters

#### **Product Summary**

| Topology                                     | ,         | 3 Phase         |

|----------------------------------------------|-----------|-----------------|

| V <sub>OFFSET</sub>                          |           | ≤ 600 V         |

| IRS2336(D)                                   |           | 10 V – 20 V     |

| V <sub>OUT</sub>                             | IRS23364D | 11.5 V – 20 V   |

| I <sub>0+</sub> & I <sub>0-</sub> (t         | ypical)   | 200 mA & 350 mA |

| t <sub>ON</sub> & t <sub>OFF</sub> (typical) |           | 530 ns & 530 ns |

| Deadtime (typical)                           |           | 275 ns          |

#### **Package Options**

www.irf.com © 2008 International Rectifier

| Table of Contents                              | Page  |

|------------------------------------------------|-------|

| Description                                    | 3     |

| Feature Comparison                             | 3     |

| Simplified Block Diagram                       | 4     |

| Typical Application Diagram                    | 4     |

| Qualification Information                      | 5     |

| Absolute Maximum Ratings                       | 6     |

| Recommended Operating Conditions               | 7     |

| Static Electrical Characteristics              | 8-9   |

| Dynamic Electrical Characteristics             | 10    |

| Functional Block Diagram                       | 11-12 |

| Input/Output Pin Equivalent Circuit Diagram    | 13-14 |

| Lead Definitions                               | 15-16 |

| Lead Assignments                               | 17    |

| Application Information and Additional Details | 18-34 |

| Parameter Temperature Trends                   | 35-38 |

| Package Details                                | 39-42 |

| Tape and Reel Details                          | 43-45 |

| Part Marking Information                       | 46    |

| Ordering Information                           | 47    |

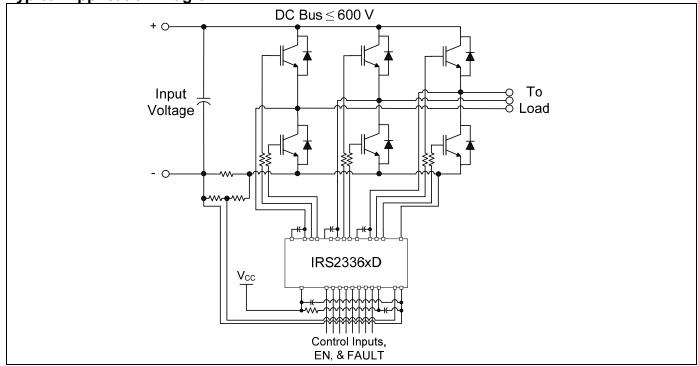

#### Description

The IRS2336xD are high voltage, high speed, power MOSFET and IGBT gate drivers with three high-side and three low-side referenced output channels for 3-phase applications. This IC is designed to be used with low-cost bootstrap power supplies; the bootstrap diode functionality has been integrated into this device to reduce the component count and the PCB size. Proprietary HVIC and latch immune CMOS technologies have been implemented in a rugged monolithic structure. The floating logic input is compatible with standard CMOS or LSTTL outputs (down to 3.3 V logic). A current trip function which terminates all six outputs can be derived from an external current sense resistor. Enable functionality is available to terminate all six outputs simultaneously. An open-drain FAULT signal is provided to indicate that a fault (e.g., over-current, over-temperature, or undervoltage shutdown event) has occurred. Fault conditions are cleared automatically after a delay programmed externally via an RC network connected to the RCIN input. The output drivers feature a high-pulse current buffer stage designed for minimum driver cross-conduction. Shoot-through protection circuitry and a minimum deadtime circuitry have been integrated into this IC. Propagation delays are matched to simplify the HVIC's use in high frequency applications. The floating channels can be used to drive N-channel power MOSFETs or IGBTs in the high-side configuration, which operate up to 600 V.

Feature Comparison: IRS2336xD Family

| Part Number | Input Logic  | UVLO           | $V_{\text{IT,TH}}$ | t <sub>ON</sub> , t <sub>OFF</sub> | V <sub>OUT</sub> |

|-------------|--------------|----------------|--------------------|------------------------------------|------------------|

| IRS2336(D)  | HIN/N, LIN/N | 8.9 V/ 8.2 V   | 0.46 V             | 530 ns, 530 ns                     | 10 V – 20 V      |

| IRS23364D   | HIN, LIN     | 11.1 V/ 10.9 V | 0.46 V             | 530 ns, 530 ns                     | 11.5 V – 20 V    |

3

Downloaded from Elcodis.com electronic components distributor

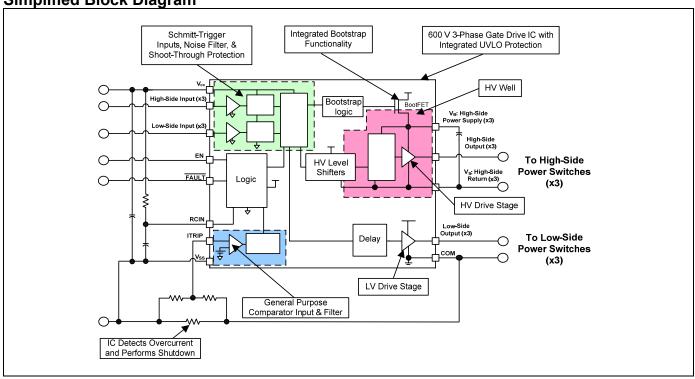

**Simplified Block Diagram**

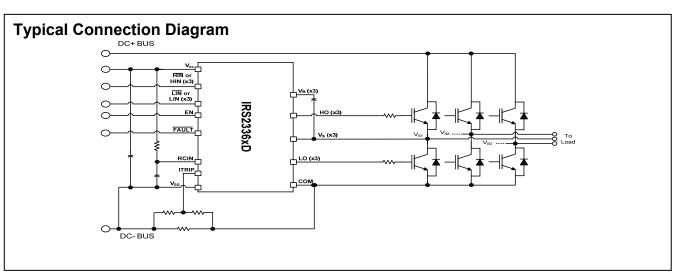

**Typical Application Diagram**

#### **Qualification Information**<sup>†</sup>

|                            |                   | Industrial <sup>††</sup>                                                                                                                                            |                                                          |  |  |  |

|----------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|

| Qualification Level        |                   | Comments: This family of ICs has passed JEDEC's Industrial qualification. IR's Consumer qualification level is granted by extension of the higher Industrial level. |                                                          |  |  |  |

|                            |                   | SOIC28W                                                                                                                                                             | MSL3 <sup>†††</sup> , 260°C                              |  |  |  |

|                            |                   | MLPQ7X7                                                                                                                                                             | (per IPC/JEDEC J-STD-020)                                |  |  |  |

| Moisture Sensitivity Level |                   | PLCC44                                                                                                                                                              | MSL3 <sup>†††</sup> , 245°C<br>(per IPC/JEDEC J-STD-020) |  |  |  |

|                            |                   |                                                                                                                                                                     | Not applicable (non-surface mount package style)         |  |  |  |

|                            | Human Body Model  | Class 2 (per JEDEC standard JESD22-A114)                                                                                                                            |                                                          |  |  |  |

| ESD                        | ESD Machine Model |                                                                                                                                                                     | Class B (per EIA/JEDEC standard EIA/JESD22-A115)         |  |  |  |

| Charged Device Model ††††  |                   | Class IV<br>(per JEDEC standard JESD22-C101)                                                                                                                        |                                                          |  |  |  |

| IC Latch-Up Test           |                   | Class I, Level A (per JESD78)                                                                                                                                       |                                                          |  |  |  |

| RoHS Compliant             |                   | Yes                                                                                                                                                                 |                                                          |  |  |  |

- † Qualification standards can be found at International Rectifier's web site <a href="http://www.irf.com/">http://www.irf.com/</a>

- †† Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information.

- ††† Higher MSL ratings may be available for the specific package types listed here. Please contact your International Rectifier sales representative for further information.

- †††† Charged Device Model classification is based on SOIC28W package.

#### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to  $V_{SS}$  unless otherwise stated in the table. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions. Voltage clamps are included between  $V_{CC}$  & COM (25 V),  $V_{CC}$  &  $V_{SS}$  (20 V), and  $V_B$  &  $V_S$  (20 V).

| Symbol              | Definition                                                | Min          | Max                      | Units                |      |  |

|---------------------|-----------------------------------------------------------|--------------|--------------------------|----------------------|------|--|

| V <sub>CC</sub>     | Low side supply voltage                                   |              | -0.3                     | 20 <sup>†</sup>      |      |  |

| \/                  | Logic input voltage (HIN, LIN, ITRIP, EN)                 | IRS2336(D)   | V <sub>SS</sub> -0.3     | V <sub>SS</sub> +5.2 |      |  |

| $V_{IN}$            | Logic input voitage (Hilly, Lily, HRIP, EN)               | IRS23364D    | V <sub>SS</sub> -0.3     | V <sub>CC</sub> +0.3 |      |  |

| $V_{RCIN}$          | RCIN input voltage                                        |              | V <sub>SS</sub> -0.3     | $V_{CC}$ +0.3        |      |  |

| $V_{B}$             | High-side floating well supply voltage                    |              | -0.3                     | 620 <sup>†</sup>     | V    |  |

| Vs                  | High-side floating well supply return voltage             |              | $V_{B}$ -20 <sup>†</sup> | V <sub>B</sub> +0.3  | 7 °  |  |

| V <sub>HO</sub>     | Floating gate drive output voltage                        |              | V <sub>S</sub> -0.3      | V <sub>B</sub> +0.3  |      |  |

| $V_{LO}$            | Low-side output voltage                                   |              | COM-0.3                  | V <sub>CC</sub> +0.3 |      |  |

| $V_{FLT}$           | Fault output voltage                                      |              | V <sub>SS</sub> -0.3     | V <sub>CC</sub> +0.3 |      |  |

| COM                 | Power ground                                              |              | V <sub>CC</sub> -25      | $V_{CC}$ +0.3        |      |  |

| dV <sub>S</sub> /dt | Allowable V <sub>S</sub> offset supply transient relative | _            | 50                       | V/ns                 |      |  |

| $PW_{HIN}$          | High-side input pulse width                               |              | 500                      | _                    | ns   |  |

|                     | Package power dissipation @ T <sub>A</sub> ≤+25°C         | 28-Lead PDIP | _                        | 1.5                  |      |  |

|                     |                                                           | 28-Lead      |                          | 1.6                  | _ W  |  |

| P <sub>D</sub>      |                                                           | SOICW        |                          |                      |      |  |

|                     |                                                           | 44-Lead PLCC | _                        | 2.0                  |      |  |

|                     |                                                           | 48-Lead      |                          | 2.0                  |      |  |

|                     |                                                           | MLPQ7X7      |                          |                      |      |  |

|                     |                                                           | 28-Lead PDIP | _                        | 83                   |      |  |

|                     |                                                           | 28-Lead      | _                        | 78                   |      |  |

| $Rth_{JA}$          | Thermal resistance, junction to ambient                   | SOICW        |                          | 00                   | °C/W |  |

|                     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                   | 44-Lead PLCC | _                        | 63                   | 4    |  |

|                     |                                                           | 48-Lead      | _                        | 63                   |      |  |

| т                   | lunction tomporature                                      | MLPQ7X7      |                          |                      |      |  |

| TJ                  | Junction temperature                                      |              | 150<br>150               | °C                   |      |  |

| T <sub>S</sub>      | Storage temperature                                       |              | -55                      | 300                  |      |  |

| ΙL                  | Lead temperature (soldering, 10 seconds)                  | _            | 300                      |                      |      |  |

<sup>†</sup> All supplies are tested at 25 V. An internal 20 V clamp exists for each supply.

### **Recommended Operating Conditions**

For proper operation, the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to  $V_{SS}$  unless otherwise stated in the table. The offset rating is tested with supplies of  $(V_{CC}\text{-COM}) = (V_B\text{-}V_S) = 15 \text{ V}$ .

| Symbol             | Definition                                    | Min        | Max                  | Units              |  |  |

|--------------------|-----------------------------------------------|------------|----------------------|--------------------|--|--|

| $V_{CC}$           | Low-side supply voltage                       | IRS2336(D) | 10                   | 20                 |  |  |

| V CC               | Low-side supply voltage                       | IRS23364D  | 11.5                 | 20                 |  |  |

| $V_{IN}$           | HIN, LIN, & EN input voltage                  | IRS2336(D) | $V_{SS}$             | V <sub>SS</sub> +5 |  |  |

| VIN                | Tilly, Lily, & Ely input voltage              | IRS23364D  | V <sub>SS</sub>      | $V_{CC}$           |  |  |

| $V_{B}$            | High-side floating well supply voltage        | IRS2336(D) | V <sub>S</sub> +10   | V <sub>S</sub> +20 |  |  |

| v <sub>B</sub>     | High-side floating well supply voltage        | IRS23364D  | V <sub>S</sub> +11.5 | V <sub>S</sub> +20 |  |  |

| Vs                 | High-side floating well supply offset voltage | COM-8      | 600                  | V                  |  |  |

| V <sub>S</sub> (t) | Transient high-side floating supply voltage   | -50        | 600                  | V                  |  |  |

| $V_{HO}$           | Floating gate drive output voltage            |            | Vs                   | $V_B$              |  |  |

| $V_{LO}$           | Low-side output voltage                       |            | COM                  | V <sub>CC</sub>    |  |  |

| COM                | Power ground                                  | -5         | 5                    |                    |  |  |

| $V_{FLT}$          | FAULT output voltage                          | $V_{SS}$   | $V_{CC}$             |                    |  |  |

| $V_{RCIN}$         | RCIN input voltage                            | $V_{SS}$   | V <sub>CC</sub>      |                    |  |  |

| $V_{ITRIP}$        | ITRIP input voltage                           | $V_{SS}$   | V <sub>SS</sub> +5   |                    |  |  |

| T <sub>A</sub>     | Ambient temperature                           | -40        | 125                  | °C                 |  |  |

<sup>†</sup> Logic operation for  $V_S$  of -8 V to 600 V. Logic state held for  $V_S$  of -8 V to  $-V_{BS}$ . Please refer to Design Tip DT97-3 for more details.

<sup>††</sup> Operational for transient negative  $V_S$  of  $V_{SS}$  - 50 V with a 50 ns pulse width. Guaranteed by design. Refer to the Application Information section of this datasheet for more details.

#### **Static Electrical Characteristics**

$(V_{CC}\text{-COM}) = (V_B\text{-V}_S) = 15 \text{ V}$ .  $T_A = 25^{\circ}\text{C}$  unless otherwise specified. The  $V_{IN}$  and  $I_{IN}$  parameters are referenced to  $V_{SS}$  and are applicable to all six channels. The  $V_O$  and  $I_O$  parameters are referenced to respective  $V_S$  and COM and are applicable to the respective output leads HO or LO. The  $V_{CCUV}$  parameters are referenced to  $V_{SS}$ . The  $V_{BSUV}$  parameters are referenced to  $V_S$ .

| Symbol                | Definition                                       |                  | Min  | Тур  | Max  | Units                                                           | Test Conditions                                                    |  |

|-----------------------|--------------------------------------------------|------------------|------|------|------|-----------------------------------------------------------------|--------------------------------------------------------------------|--|

| V <sub>CCUV+</sub>    | V <sub>CC</sub> supply undervoltage positive     | IRS2336(D)       | 8    | 8.9  | 9.8  |                                                                 |                                                                    |  |

| ▼ CCUV+               | going threshold                                  | IRS23364D        | 10.4 | 11.1 | 11.6 |                                                                 |                                                                    |  |

| V                     | V <sub>CC</sub> supply undervoltage negative     | IRS2336(D)       | 7.4  | 8.2  | 9    |                                                                 |                                                                    |  |

| V <sub>CCUV</sub> -   | going threshold                                  | IRS23364D        | 10.2 | 10.9 | 11.4 |                                                                 |                                                                    |  |

| V                     | V <sub>CC</sub> supply undervoltage              | IRS2336(D)       | 0.3  | 0.7  | _    |                                                                 |                                                                    |  |

| V <sub>CCUVHY</sub>   | hysteresis                                       | IRS23364D        | —    | 0.2  | _    | V                                                               | NA                                                                 |  |

| V                     | V <sub>BS</sub> supply undervoltage positive     | IRS2336(D)       | 8    | 8.9  | 9.8  | ]                                                               | INA                                                                |  |

| V <sub>BSUV+</sub>    | going threshold                                  | IRS23364D        | 10.4 | 11.1 | 11.6 |                                                                 |                                                                    |  |

| V                     | V <sub>BS</sub> supply undervoltage negative     | IRS2336(D)       | 7.4  | 8.2  | 9    |                                                                 |                                                                    |  |

| $V_{BSUV}$            | going threshold                                  | IRS23364D        | 10.2 | 10.9 | 11.4 |                                                                 |                                                                    |  |

| V                     | V <sub>BS</sub> supply undervoltage              | IRS2336(D)       | 0.3  | 0.7  | _    |                                                                 |                                                                    |  |

| V <sub>BSUVHY</sub>   | hysteresis                                       | IRS23364D        | —    | 0.2  | _    |                                                                 |                                                                    |  |

| I <sub>LK</sub>       | High-side floating well offset supply            | leakage          | _    | _    | 50   |                                                                 | $V_{B} = V_{S} = 600 \text{ V}$                                    |  |

| I <sub>QBS</sub>      | Quiescent V <sub>BS</sub> supply current         | <del>-</del>     | _    | 70   | 120  | μA                                                              |                                                                    |  |

| _                     | 1 1 2                                            | IRS2336          | _    | 2    | 3    | A                                                               | All inputs are in the                                              |  |

| I <sub>QCC</sub>      | Quiescent V <sub>CC</sub> supply current         | IR2336(4)D       | _    | 3    | 4    | mA                                                              | off state                                                          |  |

| V <sub>OH</sub>       | High level output voltage drop, V <sub>BIA</sub> | s-V <sub>O</sub> | _    | 0.90 | 1.4  | V                                                               | I - 20 m A                                                         |  |

| V <sub>OL</sub>       | Low level output voltage drop, V <sub>O</sub>    |                  | _    | 0.40 | 0.6  | V                                                               | $I_0$ = 20 mA                                                      |  |

| I <sub>o+</sub>       | Output high short circuit pulsed current         |                  | 120  | 200  | _    | A                                                               | $V_O=0 \text{ V}, V_{IN}=0 \text{ V},$<br>$PW \le 10  \mu\text{s}$ |  |

| I <sub>o-</sub>       | Output low short circuit pulsed curre            | ent              | 250  | 350  | mA   | $V_{O} = 15 \text{ V}, V_{IN} = 5 \text{ V},$<br>PW \le 10 \mus |                                                                    |  |

| M                     | Logic "0" input voltage                          |                  | 2.5  |      |      |                                                                 | •                                                                  |  |

| V <sub>IH</sub>       | Logic "1" input voltage                          |                  | 2.5  | _    |      |                                                                 | NA                                                                 |  |

| \/                    | Logic "1" input voltage                          |                  |      |      | 0.0  | V                                                               | INA                                                                |  |

| $V_{IL}$              | Logic "0" input voltage                          |                  |      | _    | 0.8  | V                                                               |                                                                    |  |

| V <sub>IN,CLAMP</sub> | Input voltage clamp<br>(HIN, LIN, ITRIP and EN)  | IRS2336(D)       | 4.8  | 5.2  | 5.65 |                                                                 | I <sub>IN</sub> = 100 μA                                           |  |

| 1                     | Input bias current (HO = High)                   | IRS2336(D)       | _    | 150  | 200  |                                                                 | $V_{IN} = 0 V$                                                     |  |

| I <sub>HIN+</sub>     |                                                  | IRS23364D        | _    | 120  | 165  |                                                                 | V <sub>IN</sub> = 4 V                                              |  |

| 1                     | Input bias current (HO = Low)                    | IRS2336(D)       | —    | 110  | 150  | ]                                                               | v <sub>IN</sub> – 4 v                                              |  |

| I <sub>HIN-</sub>     |                                                  | IRS23364D        | —    | _    | 1    |                                                                 | V <sub>IN</sub> = 0 V                                              |  |

| 1                     | Input bigg ourrent (I O = High)                  | IRS2336(D)       | —    | 150  | 200  | μA                                                              | V <sub>IN</sub> – U V                                              |  |

| I <sub>LIN+</sub>     | Input bias current (LO = High)                   | IRS23364D        | _    | 120  | 165  | 1                                                               | \/ = 4\/                                                           |  |

| I.                    | Input bias current (LO = Low)                    | IRS2336(D)       | _    | 110  | 150  | -                                                               | $V_{IN} = 4 V$                                                     |  |

| I <sub>LIN-</sub>     | Imput bias current (LO – LOW)                    | IRS23364D        | _    |      | 1    |                                                                 | $V_{IN} = 0 V$                                                     |  |

| $V_{RCIN,TH}$         | RCIN positive going threshold                    |                  |      | 8    |      | V                                                               | NA                                                                 |  |

| V <sub>RCIN,HY</sub>  | RCIN hysteresis                                  |                  |      | 3    |      |                                                                 |                                                                    |  |

| I <sub>RCIN</sub>     | RCIN input bias current                          |                  |      |      | 1    | μΑ                                                              | $V_{RCIN} = 0 V \text{ or } 15 V$                                  |  |

| R <sub>ON,RCIN</sub>  | RCIN low on resistance                           |                  |      | 50   | 100  | Ω                                                               | I = 1.5 mA                                                         |  |

### **Static Electrical Characteristics (continued)**

| Symbol              | Definition                             |            | Min  | Тур  | Max  | Units | <b>Test Conditions</b> |

|---------------------|----------------------------------------|------------|------|------|------|-------|------------------------|

| $V_{IT,TH+}$        | ITRIP positive going threshold         |            | 0.37 | 0.46 | 0.55 |       |                        |

| $V_{\text{IT,TH-}}$ | ITRIP negative going threshold         |            | _    | 0.4  | _    | V     | NA                     |

| $V_{\text{IT,HYS}}$ | ITRIP hysteresis                       |            | _    | 0.07 | _    |       |                        |

| ı                   | "High" ITRIP input bias current        | IRS2336(D) | _    | 5    | 20   |       | V <sub>IN</sub> = 4 V  |

| I <sub>ITRIP+</sub> | High Trkie input bias current          | IRS23364D  | _    | 5    | 40   | μΑ    | V <sub>IN</sub> = 4 V  |

| I <sub>ITRIP-</sub> | "Low" ITRIP input bias current         |            |      |      | 1    | μ     | $V_{IN} = 0 V$         |

| $V_{\text{EN,TH+}}$ | Enable positive going threshold        |            | _    | _    | 2.5  | V     | NA                     |

| V <sub>EN,TH-</sub> | Enable negative going threshold        |            | 0.8  | _    | _    |       | INA                    |

|                     | "High" enable input bias current       | IRS2336(D) | _    | 5    | 20   |       | \/ - 4 \/              |

| I <sub>EN+</sub>    | High enable input bias current         | IRS23364D  | _    | 120  | 165  | μA    | $V_{IN} = 4 V$         |

| I <sub>EN-</sub>    | "Low" enable input bias current        |            | _    | —    | 1    |       | $V_{IN} = 0 V$         |

| R <sub>ON,FLT</sub> | FAULT low on resistance                |            | _    | 50   | 100  |       | I = 1.5 mA             |

| R <sub>BS</sub>     | Internal BS diode Ron<br>(IRS2336(4)D) |            | _    | 200  | _    | Ω     | NA                     |

**Dynamic Electrical Characteristics**  $V_{CC}$ =  $V_B$  = 15 V,  $V_S$  =  $V_{SS}$  = COM,  $T_A$  = 25°C, and  $C_L$  = 1000 pF unless otherwise specified.

| Symbol                 | Definition                                               | Min | Тур  | Max  | Units | Test Conditions                                                     |

|------------------------|----------------------------------------------------------|-----|------|------|-------|---------------------------------------------------------------------|

| t <sub>ON</sub>        | Turn-on propagation delay                                | 400 | 530  | 750  |       |                                                                     |

| t <sub>OFF</sub>       | Turn-off propagation delay                               | 400 | 530  | 750  |       |                                                                     |

| $t_R$                  | Turn-on rise time                                        | _   | 125  | 190  |       | V <sub>IN</sub> = 0 V & 5 V                                         |

| t <sub>F</sub>         | Turn-off fall time                                       | _   | 50   | 75   |       | V <sub>IN</sub> = 0 V & 5 V                                         |

| t <sub>FIL,IN</sub>    | Input filter time <sup>†</sup><br>(HIN, LIN, ITRIP)      | 200 | 350  | 510  | ns    |                                                                     |

| t <sub>EN</sub>        | Enable low to output shutdown propagation delay          | 350 | 460  | 650  |       | $V_{IN, V_{EN}} = 0 \text{ V or 5 V}$                               |

| t <sub>FILTER,EN</sub> | Enable input filter time                                 | 100 | 200  | _    |       | NA                                                                  |

| t <sub>FLTCLR</sub>    | FAULT clear time<br>RCIN: R = 2 M $\Omega$ , C = 1 nF    | 1.3 | 1.65 | 2    | ms    | $V_{IN} = 0 \text{ V or } 5 \text{ V}$<br>$V_{ITRIP} = 0 \text{ V}$ |

| t <sub>ITRIP</sub>     | ITRIP to output shutdown propagation delay               | 500 | 750  | 1200 |       | V <sub>ITRIP</sub> = 5 V                                            |

| $t_{BL}$               | ITRIP blanking time                                      | _   | 400  | _    |       | $V_{IN} = 0 \text{ V or } 5 \text{ V}$                              |

| $t_{FLT}$              | ITRIP to FAULT propagation delay                         | 400 | 600  | 950  |       | $V_{ITRIP} = 5 V$                                                   |

| DT                     | Deadtime                                                 | 190 | 275  | 420  | ns    | $V_{IN} = 0 V \& 5 V$ without                                       |

| MDT                    | DT matching <sup>††</sup>                                |     |      | 60   |       | external deadtime                                                   |

| MT                     | Delay matching time $(t_{ON}, t_{OFF})^{\dagger\dagger}$ | _   |      | 50   |       | V <sub>IN</sub> = 0 V & 5 V with external deadtime larger than DT   |

| PM                     | Pulse width distortion <sup>†††</sup>                    |     |      | 75   |       | PW input=10 μs                                                      |

- The minimum width of the input pulse is recommended to exceed 500 ns to ensure the filtering time of the † input filter is exceeded.

- This parameter applies to all of the channels. Please see the application section for more details.

- ††† PM is defined as PW<sub>IN</sub> PW<sub>OUT</sub>.