# **Spartan-II/Spartan-IIE Family OTP Configuration PROMs (XC17S00A)**

DS078 (v1.10) June 25, 2007

**Product Specification**

#### **Features**

- Configuration one-time programmable (OTP) read-only memory designed to store configuration bitstreams for Spartan™-II/Spartan-IIE FPGA devices

- · Simple interface to the Spartan device

- Programmable reset polarity (active High or active Low)

- Low-power CMOS floating gate process

- 3.3V PROM

- Available in compact plastic 8-pin DIP, 8-pin VOIC, 20-pin SOIC, or 44-pin VQFP packages

- Programming support by leading programmer manufacturers

- Design support using the Xilinx Alliance and Foundation™ series software packages

- Guaranteed 20-year life data retention

- Pb-free (RoHS-compliant) packaging available

#### Introduction

The XC17S00A family of PROMs provide an easy-to-use, cost-effective method for storing Spartan-II/Spartan-IIE device configuration bitstreams.

When the Spartan device is in Master Serial mode, it generates a configuration clock that drives the Spartan PROM. A short access time after the rising clock edge, data appears on the PROM DATA output pin that is connected to the Spartan device  $D_{\text{IN}}$  pin. The Spartan device generates

the appropriate number of clock pulses to complete the configuration. Once configured, it disables the PROM. When a Spartan device is in Slave Serial mode, the PROM and the Spartan device must both be clocked by an incoming signal.

For device programming, either the Xilinx Alliance or the Spartan device design file into a standard HEX format which is then transferred to most commercial PROM programmers.

| Spartan-II/IIE FPGA     | Configuration Bits | Compatible Spartan-II/IIE PROM |

|-------------------------|--------------------|--------------------------------|

| XC2S15                  | 197,696            | XC17S15A                       |

| XC2S30                  | 336,768            | XC17S30A                       |

| XC2S50                  | 559,200            | XC17S50A                       |

| XC2S100                 | 781,216            | XC17S100A                      |

| XC2S150                 | 1,040,096          | XC17S150A                      |

| XC2S200                 | 1,335,840          | XC17S200A                      |

| XC2S50E                 | 630,048            | XC17S50A                       |

| XC2S100E                | 863,840            | XC17S100A                      |

| XC2S150E <sup>(1)</sup> | 1,134,496          | XC17S200A                      |

| XC2S200E                | 1,442,016          | XC17S200A                      |

| XC2S300E                | 1,875,648          | XC17S300A                      |

| XC2S400E                | 2,693,440          | XC17V04 <sup>(2)</sup>         |

| XC2S600E                | 3,961,632          | XC17V04 <sup>(2)</sup>         |

#### Notes:

- 1. Due to the higher configuration bit requirements of the XC2S150E device, an XC17S200A PROM is required to configure this FPGA.

- 2. See XC17V00 series configuration PROMs data sheet

## XC17S15A, XC17S30A, XC17S50A, XC17S100A, XC17S150A, XC17S200A, and XC17S300A

## **Absolute Maximum Ratings**(1)

| Symbol           | Description                       | Value                        | Units |

|------------------|-----------------------------------|------------------------------|-------|

| V <sub>CC</sub>  | Supply voltage relative to GND    | -0.5 to +4.0                 | V     |

| V <sub>IN</sub>  | Input voltage with respect to GND | -0.5 to V <sub>CC</sub> +0.5 | V     |

| V <sub>TS</sub>  | Voltage applied to High-Z output  | -0.5 to V <sub>CC</sub> +0.5 | V     |

| T <sub>STG</sub> | Storage temperature (ambient)     | -65 to +150                  | °C    |

#### Notes:

### Operating Conditions<sup>(1)</sup>

| Symbol           | Description |                                                                                          | Min | Max | Units |

|------------------|-------------|------------------------------------------------------------------------------------------|-----|-----|-------|

| V <sub>CC</sub>  | Commercial  | Supply voltage relative to GND ( $T_A = 0^{\circ} C$ to $+70^{\circ} C$ )                | 3.0 | 3.6 | V     |

|                  | Industrial  | Supply voltage relative to GND ( $T_A = -40^{\circ} \text{C to } +85^{\circ} \text{C}$ ) | 3.0 | 3.6 | V     |

| T <sub>VCC</sub> |             | V <sub>CC</sub> rise time from 0V to nominal voltage                                     | 1.0 | 50  | ms    |

#### Notes:

- 1. During normal read operation, both  $V_{\mbox{\footnotesize{CC}}}$  pins must be connected together.

- 2. At power-up, the device requires the V<sub>CC</sub> power supply to monotonically rise from 0V to nominal voltage within the specified V<sub>CC</sub> rise time. If the power supply cannot meet this requirement, then the device may not perform a power-on-reset properly.

### **DC Characteristics Over Operating Condition**

| Symbol           | Description                                             | Min | Max             | Units |

|------------------|---------------------------------------------------------|-----|-----------------|-------|

| V <sub>IH</sub>  | High-level input voltage                                | 2.0 | V <sub>CC</sub> | V     |

| $V_{IL}$         | Low-level input voltage                                 | 0   | 0.8             | V     |

| V <sub>OH</sub>  | High-level output voltage ( $I_{OH} = -3 \text{ mA}$ )  | 2.4 | -               | V     |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +3 mA)      | -   | 0.4             | V     |

| I <sub>CCA</sub> | Supply current, active mode (at maximum frequency)      | _   | 15              | mA    |

| I <sub>CCS</sub> | Supply current, standby mode                            | _   | 1               | mA    |

| ال               | Input or output leakage current                         | -10 | 10              | μΑ    |

| C <sub>IN</sub>  | Input Capacitance (V <sub>IN</sub> = GND, f = 1.0 MHz)  | _   | 10              | pF    |

| C <sub>OUT</sub> | Output Capacitance (V <sub>IN</sub> = GND, f = 1.0 MHz) | _   | 10              | pF    |

Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time might affect device reliability.

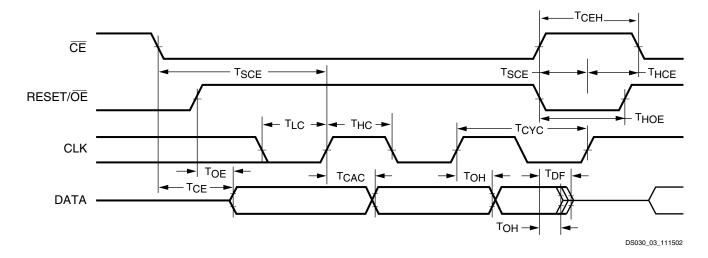

## **AC Characteristics Over Operating Condition**(1)

| Symbol           | Description                                         | Min | Max | Units |

|------------------|-----------------------------------------------------|-----|-----|-------|

| T <sub>OE</sub>  | RESET/OE to Data Delay                              | _   | 45  | ns    |

| T <sub>CE</sub>  | CE to Data Delay                                    | _   | 60  | ns    |

| T <sub>CAC</sub> | CLK to Data Delay                                   | _   | 80  | ns    |

| T <sub>OH</sub>  | Data Hold From CE, RESET/OE, or CLK(2)              | 0   | -   | ns    |

| T <sub>DF</sub>  | CE or RESET/OE to Data Float Delay <sup>(2,3)</sup> | _   | 50  | ns    |

| T <sub>CYC</sub> | Clock Periods                                       | 100 | -   | ns    |

| T <sub>LC</sub>  | CLK Low Time <sup>(2)</sup>                         | 50  | _   | ns    |

| T <sub>HC</sub>  | CLK High Time <sup>(2)</sup>                        | 50  | _   | ns    |

| T <sub>SCE</sub> | CE Setup Time to CLK (to guarantee proper counting) | 25  | _   | ns    |

| T <sub>HCE</sub> | CE Hold Time to CLK (to guarantee proper counting)  | 0   | -   | ns    |

| T <sub>HOE</sub> | RESET/OE Hold Time (guarantees counters are reset)  | 25  | _   | ns    |

| T <sub>CEH</sub> | CE High time (guarantees counters are reset)        | 20  | _   | ns    |

#### Notes:

- 1. AC test load = 50 pF

- 2. Guaranteed by design, not tested.

- 3. Float delays are measured with 5 pF AC loads. Transition is measured at ±200 mV from steady state active levels.

- 4. All AC parameters are measured with  $V_{IL} = 0.0V$  and  $V_{IH} = 3.0V$ .

- 5. If  $T_{CEH}$  High <  $2\mu s$ ,  $T_{CE}$  =  $2 \mu s$ .

- 6. If  $T_{HOE}$  High <  $2\mu s$ ,  $T_{CE} = 2 \mu s$ .

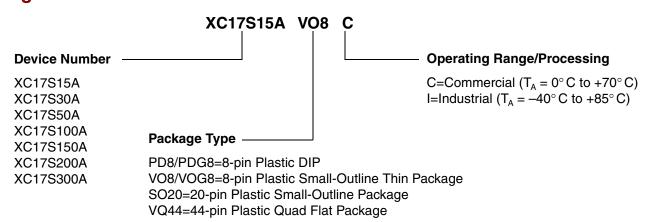

## **Ordering Information**

## 3.3V Valid Ordering Combinations

| XC17S15APD8C  | XC17S50APD8C   | XC17S150APD8C  |

|---------------|----------------|----------------|

| XC17S15AVO8C  | XC17S50APDG8C  | XC17S150AVO8C  |

| XC17S15AVOG8C | XC17S50AVO8C   | XC17S150ASO20C |

| XC17S15ASO20C | XC17S50AVOG8C  | XC17S150APD8I  |

| XC17S15APD8I  | XC17S50ASO20C  | XC17S150AVO8I  |

| XC17S15AVO8I  | XC17S50APD8I   | XC17S150ASO20I |

| XC17S15ASO20I | XC17S50AVO8I   |                |

|               | XC17S50ASO20I  |                |

| XC17S30APD8C  | XC17S100APD8C  | XC17S200APD8C  |

| XC17S30AVO8C  | XC17S100AVO8C  | XC17S200APDG8C |

| XC17S30ASO20C | XC17S100AVOG8C | XC17S200AVO8C  |

| XC17S30APD8I  | XC17S100ASO20C | XC17S200AVOG8C |

| XC17S30AVO8I  | XC17S100APD8I  | XC17S200APD8I  |

| XC17S30ASO20I | XC17S100AVO8I  | XC17S200APDG8I |

|               | XC17S100ASO20I | XC17S200AVO8I  |

|               |                | XC17S200AVOG8I |

|               |                | XC17S200AVQ44C |

|               |                | XC17S200AVQ44I |

|               |                | XC17S300AVQ44C |

|               |                | XC17S300AVQ44I |