# Quad Matched 741-Type Operational Amplifiers

0P11

### **FEATURES**

Guaranteed Vos: 500 μV maximum

Guaranteed matched CMRR: 94 dB minimum Guaranteed matched Vos: 750 μV maximum

LM148/LM348 direct replacement

Low noise

Silicon-nitride passivation Internal frequency compensation Low crossover distortion Continuous short-circuit protection

Low input bias current

#### **GENERAL DESCRIPTION**

The OP11 provides four matched 741-type operational amplifiers in a single 14-lead PDIP. The OP11 is pin compatible with the LM148, LM348, RM4156, RM4158, and HA4741 amplifiers. The amplifier is matched for common-mode rejection ratio and offset voltage, which is very important in designing instrumentation amplifiers. In addition, the amplifier is designed to have equal positive-going and negative-going slew rates, which is an important consideration for good audio system performance.

The OP11 is ideal for use in designs requiring minimum space and cost while maintaining performance.

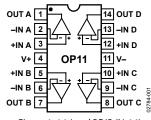

#### PIN CONFIGURATION

Figure 1. 14-Lead PDIP (N-14) (P Suffix)

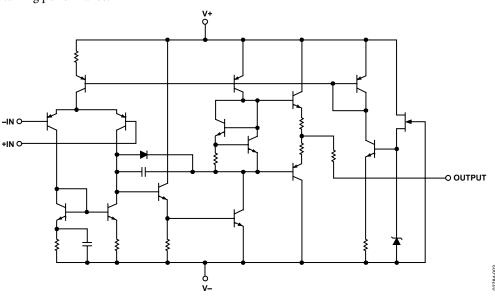

Figure 2. Simplified Schematic

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **SPECIFICATIONS**

## **ELECTRICAL CHARACTERISTICS**

$V_{\text{S}}$  = ±15 V,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

Table 1.

| Parameter                                       | Symbol             | Conditions                                                                 | Min  | Тур  | Max | Unit   |

|-------------------------------------------------|--------------------|----------------------------------------------------------------------------|------|------|-----|--------|

| Input Offset Voltage                            | Vos                | $R_S \le 10 \text{ k}\Omega$                                               |      | 0.3  | 0.5 | mV     |

| Input Offset Current                            | los                |                                                                            |      | 5.5  | 20  | nA     |

| Input Bias Current                              | I <sub>B</sub>     |                                                                            |      | 180  | 300 | nA     |

| Input Resistance Differential Mode <sup>1</sup> | R <sub>IN</sub>    |                                                                            | 0.17 | 0.29 |     | ΜΩ     |

| Input Voltage Range                             | IVR                |                                                                            | ±12  | ±13  |     | V      |

| Common-Mode Rejection Ratio                     | CMRR               | $V_{CM} = \pm 12 \text{ V}, R_S \leq 10 \text{ k}\Omega$                   | 100  | 120  |     | dB     |

| Power Supply Rejection Ratio                    | PSRR               | $V_S = \pm 5 \text{ V to } \pm 15 \text{ V, } R_S \leq 10 \text{ k}\Omega$ |      | 4    | 32  | μV/V   |

| Output Voltage Swing                            | Vo                 | $R_L = 2 k\Omega$                                                          | ±11  | ±13  |     | V      |

| Large Signal Voltage Gain                       | Avo                | $R_L \le 2 k\Omega$ , $V_O = \pm 10 V$                                     | 100  | 650  |     | V/mV   |

| Power Consumption <sup>2</sup>                  | P <sub>d</sub>     | $V_0 = 0 V$                                                                |      | 105  | 180 | mW     |

| Input Noise Voltage                             | e <sub>n</sub> p-p | 0.1 Hz to 10 Hz                                                            |      | 0.7  |     | μV p-p |

| Input Noise Voltage Density                     | e <sub>n</sub>     | $f_0 = 10 \text{ Hz}$                                                      |      | 18   |     | nV/√Hz |

|                                                 |                    | f <sub>O</sub> = 100 Hz                                                    |      | 14   |     | nV/√Hz |

|                                                 |                    | $f_0 = 1 \text{ kHz}$                                                      |      | 12   |     | nV/√Hz |

| Input Noise Current                             | I <sub>n</sub> p-p | 0.1 Hz to 10 Hz                                                            |      | 17   |     | рА р-р |

| Input Noise Current Density                     | I <sub>n</sub>     | $f_O = 10 \text{ Hz}$                                                      |      | 1.8  |     | pA/√Hz |

|                                                 |                    | f <sub>0</sub> = 100 Hz                                                    |      | 1.5  |     | pA/√Hz |

|                                                 |                    | $f_0 = 1 \text{ kHz}$                                                      |      | 1.2  |     | pA/√Hz |

| Channel Separation                              | CS                 |                                                                            | 100  | 130  |     | dB     |

| Slew Rate <sup>3</sup>                          | SR                 |                                                                            | 0.7  | 1.0  |     | V/µs   |

| Large Signal Bandwidth <sup>3</sup>             |                    | $V_0 = 20 \text{ V p-p}$                                                   | 11   | 16   |     | kHz    |

| Closed-Loop Bandwidth⁴                          | BW                 | $A_{VCL} = 1$                                                              | 2.4  | 3.0  |     | MHz    |

| Rise Time <sup>3</sup>                          | t <sub>f</sub>     | $A_V = 1, V_{IN} = 50 \text{ mV}$                                          |      | 110  | 145 | ns     |

| Overshoot <sup>3</sup>                          | OS                 |                                                                            |      | 15   | 25  | %      |

<sup>&</sup>lt;sup>1</sup> Guaranteed by input bias current. <sup>2</sup> Total dissipation for all four amplifiers in package. <sup>3</sup> Sample tested.

<sup>&</sup>lt;sup>4</sup> Guaranteed by rise time.

# **OP11**

$V_S = \pm 15 \text{ V}, 0^{\circ}\text{C} \le T_A \le 70^{\circ}\text{C}$ , unless otherwise noted.

Table 2.

| Parameter                                       | Symbol          | Conditions                                                                 | Min | Тур | Max | Unit  |

|-------------------------------------------------|-----------------|----------------------------------------------------------------------------|-----|-----|-----|-------|

| Input Offset Voltage                            | Vos             | $R_S \le 10 \text{ k}\Omega$                                               |     | 0.4 | 0.8 | mV    |

| Average Input Offset Voltage Drift <sup>1</sup> | TCVos           | $R_S \le 10 \text{ k}\Omega$                                               |     | 2.0 | 10  | μV/°C |

| Input Offset Current                            | los             |                                                                            |     | 14  | 30  | nA    |

| Average Input Offset Current Drift <sup>1</sup> | TClos           |                                                                            |     | 0.1 | 0.3 | nA/°C |

| Input Bias Current                              | I <sub>B</sub>  |                                                                            |     | 200 | 350 | nA    |

| Input Voltage Range                             | IVR             |                                                                            | ±12 | ±13 |     | V     |

| Common-Mode Rejection Ratio                     | CMRR            | $V_{CM} = \pm 12 \text{ V, } R_S \leq 10 \text{ k}\Omega$                  | 100 | 120 |     | dB    |

| Power Supply Rejection Ratio                    | PSRR            | $V_S = \pm 5 \text{ V to } \pm 15 \text{ V, } R_S \leq 10 \text{ k}\Omega$ |     | 4   | 32  | μV/V  |

| Large Signal Voltage Gain                       | A <sub>vo</sub> | $R_L \ge 2 \text{ k}\Omega, V_O = \pm 10 \text{ V}$                        | 50  | 250 |     | V/mV  |

| Output Voltage Swing                            | Vo              | $R_L \ge 2 \ k\Omega$                                                      | ±11 | ±13 |     | V     |

| Power Consumption <sup>2</sup>                  | $P_d$           | $V_O = 0 V$                                                                |     | 115 | 200 | mW    |

## **MATCHING CHARACTERISTICS**

$V_{\text{S}}=\pm 15$  V,  $T_{\text{A}}=25^{\circ}\text{C},\,R_{\text{S}}\leq 100~\Omega,$  unless otherwise noted.

Table 3.

| Parameter                  | Symbol          | Conditions          | Min | Тур | Max  | Unit |

|----------------------------|-----------------|---------------------|-----|-----|------|------|

| Input Offset Voltage Match | $\Delta V_{OS}$ |                     |     | 0.5 | 0.75 | mV   |

| Common-Mode Rejection      | ΔCMRR           | $V_{CM} = \pm 12 V$ |     | 1   | 20   | μV/V |

| Ratio Match                |                 | $V_{CM} = \pm 12 V$ | 94  | 120 |      | dB   |

$V_S = \pm 15 \text{ V}, 0^{\circ}\text{C} \le T_A \le 70^{\circ}\text{C}, R_S \le 100 \Omega$ , unless otherwise noted.

Table 4.

| Parameter                  | Symbol          | Conditions          | Min | Тур | Max | Unit |

|----------------------------|-----------------|---------------------|-----|-----|-----|------|

| Input Offset Voltage Match | $\Delta V_{OS}$ |                     |     | 0.6 | 1.0 | mV   |

| Common-Mode Rejection      | ΔCMRR           | $V_{CM} = \pm 12 V$ |     | 3.2 | 20  | μV/V |

| Ratio Match                |                 | $V_{CM} = \pm 12 V$ | 94  | 110 |     | dB   |

<sup>&</sup>lt;sup>1</sup> Guaranteed but not tested. <sup>2</sup> Total dissipation for all four amplifiers in package.

## **ABSOLUTE MAXIMUM RATINGS**

Table 5.

| Parameter                            | Rating                       |

|--------------------------------------|------------------------------|

| Supply Voltage (V <sub>5</sub> )     | ±22 V                        |

| Differential Input Voltage           | ±30 V                        |

| Input Voltage                        | Supply Voltage               |

| Output Short-Circuit Duration        | Continuous<br>(One Amp Only) |

| Storage Temperature Range            | −65°C to +125°C              |

| Lead Temperature (Soldering, 60 sec) | 300°C                        |

| Operating Temperature Range          | 0°C to 70°C                  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 6. Thermal Resistance

| Package Type        | $\theta_{JA}^1$ | θ,ς | Unit |

|---------------------|-----------------|-----|------|

| 14-Lead PDIP (N-14) | 83              | 39  | °C/W |

$<sup>^1</sup>$   $\theta_{JA}$  is specified for worst-case conditions, that is,  $\theta_{JA}$  is specified for device in socket for PDIP.

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

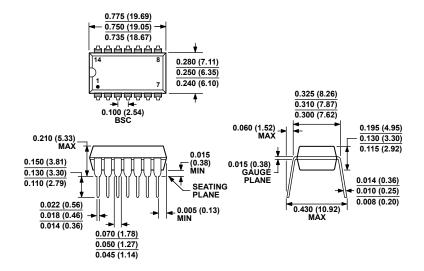

## **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-001

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.

Figure 21. 14-Lead Plastic Dual In-Line Package [PDIP]

(N-14)

[P Suffix]

Dimensions shown in inches and (millimeters)

## **ORDERING GUIDE**

| Model                | Temperature Range | Package Description                         | Package Option  |

|----------------------|-------------------|---------------------------------------------|-----------------|

| OP11EP               | 0°C to 70°C       | 14-Lead Plastic Dual In-Line Package (PDIP) | N-14 (P-Suffix) |

| OP11EPZ <sup>1</sup> | 0°C to 70°C       | 14-Lead Plastic Dual In-Line Package (PDIP) | N-14 (P-Suffix) |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

For military processed devices, refer to the Standard Microcircuit Drawing (SMD) available at

| SMD Part Number | Analog Devices, Inc. Equivalent |

|-----------------|---------------------------------|

| 5962-89801012A  | OP11ARCMDA                      |

| 5962-8980101CA  | OP11AYMDA                       |