April 2000

QFET™

# FQPF6P25

# 250V P-Channel MOSFET

# **General Description**

These P-Channel enhancement mode power field effect transistors are produced using Fairchild's proprietary, planar stripe, DMOS technology.

This advanced technology has been especially tailored to minimize on-state resistance, provide superior switching performance, and withstand high energy pulse in the avalanche and commutation mode. These devices are well suited for high efficiency switching DC/DC converters.

# **Features**

- -4.2A, -250V,  $R_{DS(on)} = 1.1\Omega$  @ $V_{GS} = -10$  V

- Low gate charge (typical 21 nC)

- Low Crss (typical 20 pF)

- Fast switching

- 100% avalanche tested

- · Improved dv/dt capability

# Absolute Maximum Ratings $T_C = 25$ °C unless otherwise noted

| Symbol                            | Parameter                                                                     |          | FQPF6P25    | Units |  |

|-----------------------------------|-------------------------------------------------------------------------------|----------|-------------|-------|--|

| V <sub>DSS</sub>                  | Drain-Source Voltage                                                          |          | -250        | V     |  |

| I <sub>D</sub>                    | Drain Current - Continuous (T <sub>C</sub> = 25°                              | C)       | -4.2        | А     |  |

|                                   | - Continuous (T <sub>C</sub> = 100                                            | O°C)     | -1.78       | А     |  |

| I <sub>DM</sub>                   | Drain Current - Pulsed                                                        | (Note 1) | -16.8       | А     |  |

| V <sub>GSS</sub>                  | Gate-Source Voltage                                                           |          | ± 30        | V     |  |

| E <sub>AS</sub>                   | Single Pulsed Avalanche Energy                                                | (Note 2) | 540         | mJ    |  |

| I <sub>AR</sub>                   | Avalanche Current                                                             | (Note 1) | -4.2        | А     |  |

| E <sub>AR</sub>                   | Repetitive Avalanche Energy                                                   | (Note 1) | 4.5         | mJ    |  |

| dv/dt                             | Peak Diode Recovery dv/dt                                                     | (Note 3) | -5.5        | V/ns  |  |

| $P_D$                             | Power Dissipation (T <sub>C</sub> = 25°C) - Derate above 25°C                 |          | 45          | W     |  |

|                                   |                                                                               |          | 0.36        | W/°C  |  |

| T <sub>J</sub> , T <sub>STG</sub> | Operating and Storage Temperature Range                                       |          | -55 to +150 | °C    |  |

| T <sub>L</sub>                    | Maximum lead temperature for soldering purposes, 1/8" from case for 5 seconds |          | 300         | °C    |  |

| .r                                |                                                                               |          | 300         |       |  |

# **Thermal Characteristics**

| Symbol          | Parameter                               | Тур | Max  | Units |

|-----------------|-----------------------------------------|-----|------|-------|

| $R_{\theta JC}$ | Thermal Resistance, Junction-to-Case    |     | 2.78 | °C/W  |

| $R_{\theta JA}$ | Thermal Resistance, Junction-to-Ambient |     | 62.5 | °C/W  |

Rev. A, April 2000

| Symbol                                             | Parameter                                                         | Test Conditions                                                                | Min  | Тур              | Max              | Units          |

|----------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------|------|------------------|------------------|----------------|

| Off Cha                                            | aracteristics                                                     |                                                                                |      |                  |                  |                |

| BV <sub>DSS</sub>                                  | Drain-Source Breakdown Voltage                                    | $V_{GS} = 0 \text{ V, } I_{D} = -250 \mu\text{A}$                              | -250 |                  |                  | V              |

| ΔBV <sub>DSS</sub><br>/ ΔT <sub>J</sub>            | Breakdown Voltage Temperature<br>Coefficient                      | I <sub>D</sub> = -250 μA, Referenced to 25°C                                   |      | -0.1             |                  | V/°C           |

| I <sub>DSS</sub>                                   | Zero Gate Voltage Drain Current                                   | V <sub>DS</sub> = -250 V, V <sub>GS</sub> = 0 V                                |      |                  | -1               | μΑ             |

|                                                    |                                                                   | V <sub>DS</sub> = -200 V, T <sub>C</sub> = 125°C                               |      |                  | -10              | μΑ             |

| I <sub>GSSF</sub>                                  | Gate-Body Leakage Current, Forward                                | V <sub>GS</sub> = -30 V, V <sub>DS</sub> = 0 V                                 |      |                  | -100             | nA             |

| I <sub>GSSR</sub>                                  | Gate-Body Leakage Current, Reverse                                | V <sub>GS</sub> = 30 V, V <sub>DS</sub> = 0 V                                  |      |                  | 100              | nA             |

| On Cha                                             | aracteristics                                                     |                                                                                |      |                  |                  |                |

| V <sub>GS(th)</sub>                                | Gate Threshold Voltage                                            | $V_{DS} = V_{GS}, I_{D} = -250 \mu A$                                          | -3.0 |                  | -5.0             | V              |

| R <sub>DS(on)</sub>                                | Static Drain-Source<br>On-Resistance                              | V <sub>GS</sub> = -10 V, I <sub>D</sub> = -2.1 A                               |      | 0.82             | 1.1              | Ω              |

| 9 <sub>FS</sub>                                    | Forward Transconductance                                          | V <sub>DS</sub> = -40 V, I <sub>D</sub> = -2.1 A (Note 4)                      |      | 2.8              |                  | S              |

| C <sub>iss</sub> C <sub>oss</sub> C <sub>rss</sub> | Input Capacitance Output Capacitance Reverse Transfer Capacitance | $V_{DS} = -25 \text{ V}, V_{GS} = 0 \text{ V},$ $f = 1.0 \text{ MHz}$          |      | 600<br>115<br>20 | 780<br>150<br>25 | pF<br>pF<br>pF |

|                                                    | ,                                                                 |                                                                                |      | 20               | 25               | рг             |

|                                                    | ing Characteristics                                               |                                                                                |      | 40               | 0.5              |                |

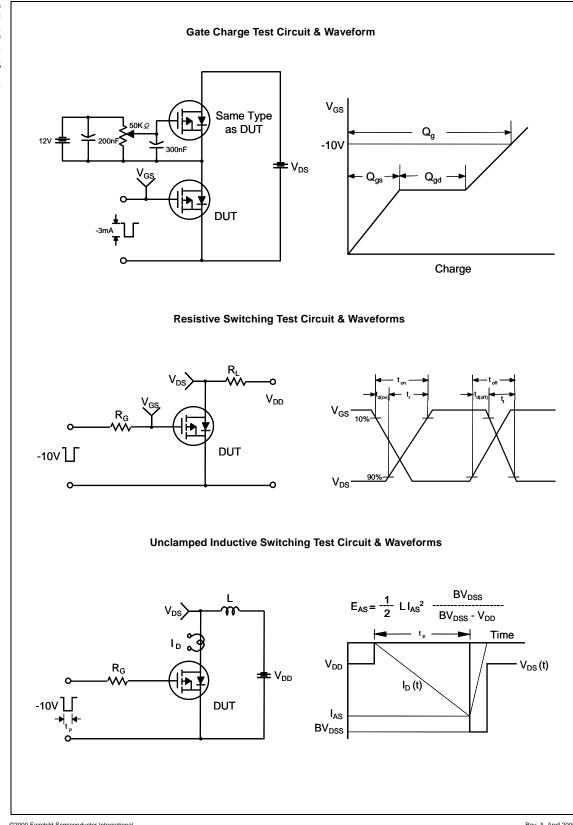

| t <sub>d(on)</sub>                                 | Turn-On Delay Time                                                | $V_{DD} = -125 \text{ V}, I_D = -6.0 \text{ A},$                               |      | 13               | 35               | ns             |

| t <sub>r</sub>                                     | Turn-On Rise Time Turn-Off Delay Time                             | $R_G = 25 \Omega$                                                              |      | 75<br>40         | 160<br>90        | ns             |

| t <sub>d(off)</sub>                                | Turn-Off Fall Time                                                | (Note 4, 5                                                                     |      | 50               | 110              | ns<br>ns       |

| Q <sub>g</sub>                                     | Total Gate Charge                                                 | V 200 V I 6 0 A                                                                |      | 21               | 27               | nC             |

| Q <sub>gs</sub>                                    | Gate-Source Charge                                                | $V_{DS} = -200 \text{ V}, I_{D} = -6.0 \text{ A},$<br>$V_{GS} = -10 \text{ V}$ |      | 4.7              |                  | nC             |

| Q <sub>qd</sub>                                    | Gate-Drain Charge                                                 | (Note 4, 5                                                                     |      | 10.7             |                  | nC             |

| gu                                                 | 3.                                                                |                                                                                | _    | _                |                  |                |

| Drain-S                                            | Source Diode Characteristics at                                   | nd Maximum Ratings                                                             |      |                  |                  |                |

| I <sub>S</sub>                                     | Maximum Continuous Drain-Source Diode Forward Current             |                                                                                |      |                  | -4.2             | Α              |

| I <sub>SM</sub>                                    | Maximum Pulsed Drain-Source Diode Forward Current                 |                                                                                |      |                  | -16.8            | Α              |

| $V_{SD}$                                           | Drain-Source Diode Forward Voltage                                | $V_{GS} = 0 \text{ V}, I_{S} = -4.2 \text{ A}$                                 |      |                  | -5.0             | V              |

| t <sub>rr</sub>                                    | Reverse Recovery Time                                             | $V_{GS} = 0 \text{ V}, I_S = -6.0 \text{ A},$                                  |      | 170              |                  | ns             |

| Q <sub>rr</sub>                                    |                                                                   | $dI_F / dt = 100 \text{ A/}\mu\text{s}$ (Note 4)                               |      |                  |                  |                |

- **Notes:**1. Repetitive Rating: Pulse width limited by maximum junction temperature 2. L = 49mH, I<sub>AS</sub> = -4.2A, V<sub>DD</sub> = -50V, R<sub>G</sub> = 25 Ω. Starting T<sub>J</sub> = 25°C 3. I<sub>SD</sub>  $\leq$  -6.0A, di/dt  $\leq$  300A/μs, V<sub>DD</sub>  $\leq$  BV<sub>DSS</sub>. Starting T<sub>J</sub> = 25°C 4. Pulse Test: Pulse width  $\leq$  300μs, Duty cycle  $\leq$  2% 5. Essentially independent of operating temperature

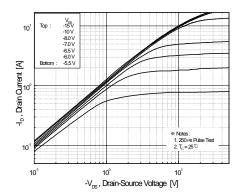

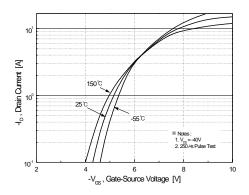

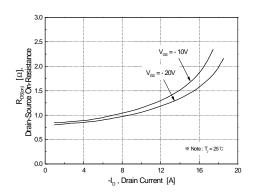

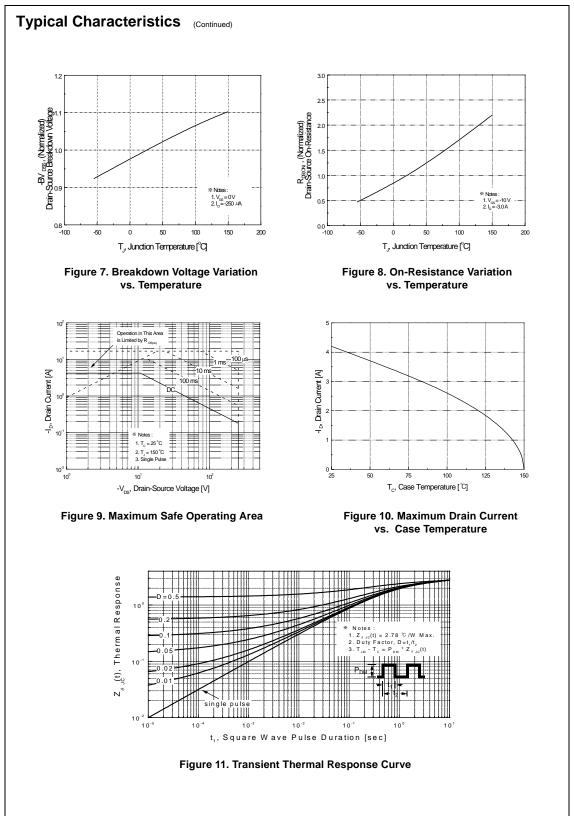

# **Typical Characteristics**

Figure 1. On-Region Characteristics

Figure 2. Transfer Characteristics

Figure 3. On-Resistance Variation vs.

Drain Current and Gate Voltage

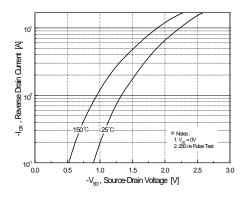

Figure 4. Body Diode Forward Voltage Variation vs. Source Current and Temperature

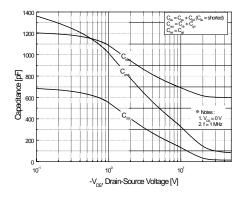

Figure 5. Capacitance Characteristics

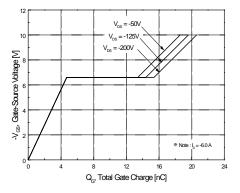

Figure 6. Gate Charge Characteristics

©2000 Fairchild Semiconductor International Rev. A, April 2000

# Peak Diode Recovery dv/dt Test Circuit & Waveforms I<sub>SD</sub> Driver Compliment of DUT (N-Channel) $V_{DD}$ $\prod \!\!\!\! \int V_{GS}$ • dv/dt controlled by R<sub>G</sub> • I<sub>SD</sub> controlled by pulse period Gate Pulse Width ${ m V}_{\rm GS}$ Gate Pulse Period 10V (Driver) **Body Diode Reverse Current** $\mathbf{I}_{\text{SD}}$ (DUT) di/dt I<sub>FM</sub>, Body Diode Forward Current V<sub>DS</sub> ( DUT ) **Body Diode** Forward Voltage Drop Body Diode Recovery dv/dt

### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

FACT™ QFET™ FACT Quiet Series™ QS™

$\begin{array}{lll} \mathsf{FAST}^{(\!R\!)} & \mathsf{Quiet} \; \mathsf{Series}^\mathsf{TM} \\ \mathsf{FASTr}^\mathsf{TM} & \mathsf{SuperSOT}^\mathsf{TM}\text{-}3 \\ \mathsf{GTO}^\mathsf{TM} & \mathsf{SuperSOT}^\mathsf{TM}\text{-}6 \end{array}$

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

# LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR INTERNATIONAL.

As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to

result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

# **PRODUCT STATUS DEFINITIONS**

### **Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                            |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or In<br>Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                    |

| Preliminary              | First Production          | This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                       |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                                   |

©2000 Fairchild Semiconductor International Rev. A, January 2000