## **General Description**

The MAX19527 evaluation kit (EV kit) is a fully assembled and tested circuit board that contains all the components necessary to evaluate the performance of the MAX19527 50Msps octal, 12-bit analog-to-digital converter (ADC). The EV kit also includes Windows® 2000-, Windows XP®-, and Windows Vista®-compatible software that provides a simple graphical user interface (GUI) for exercising the features of the ADC.

The EV kit accepts single-ended analog inputs from an analog signal source and provides an on-board circuit that transforms the analog single-ended signal into a differential signal. The ADC digital LVDS outputs can be captured easily with Maxim's data converter evaluation platform (DCEP). The EV kit operates from a single 3.3V power supply and provides on-board regulation for the analog, digital, and logic circuitries.

## **Features**

- Single Power-Supply Operation

- Direct Interface with the Maxim DCEP Data Board Using a QSH Connector

- Low-Voltage and Low-Power Operation

- On-Board Single-Ended-to-Differential Transformer Circuitry

- Differential or Single-Ended Clock Configuration

- On-Board Clock-Shaping Circuit with Adjustable Duty Cycle

- ◆ On-Board or Stand-Alone SPI<sup>™</sup> Interface Control

- DCEP Board Available

- Fully Assembled and Tested

## **Ordering Information**

| PART           | ТҮРЕ                               |

|----------------|------------------------------------|

| MAX19527EVKIT+ | EV Kit                             |

| DCEP           | Data Converter Evaluation Platform |

+Denotes lead(Pb)-free and RoHS compliant.

## Component List

| DESIGNATION                   | QTY | DESCRIPTION                                                                                        |

|-------------------------------|-----|----------------------------------------------------------------------------------------------------|

| B9, CMOUT,<br>TP1–TP8         | 10  | Red PC test points                                                                                 |

| C1–C16, C58,<br>C62–C65, C114 | 22  | 0.1µF ±10%, 10V X5R ceramic<br>capacitors (0402)<br>TDK C1005X5R1A104K or<br>Murata GRM155R61A104K |

| C41–C56                       | 16  | 39pF ±5%, 50V C0G ceramic<br>capacitors (0402)<br>TDK C1005C0G1H390J or<br>Murata GRM1555C1H390J   |

| C57, C77, C81                 | 3   | 1μF ±10%, 6.3V X5R ceramic<br>capacitors (0402)<br>TDK C1005X5R0J105K or<br>Murata GRM155R60J105K  |

| DESIGNATION                                                                                                                       | QTY | DESCRIPTION                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------|

| C59, C89, C90,<br>C95–C98,<br>C103–C106, C111,<br>C112, C113, C130,<br>C133, C135, C136,<br>C137, C140, C141,<br>C144, C145, C146 | 24  | 0.1µF ±10%, 50V X5R ceramic<br>capacitors (0603)<br>TDK C1608X5R1H104K or<br>Murata GRM188R51H104K      |

| C60, C61,<br>C66–C69                                                                                                              | 0   | Not installed, ceramic<br>capacitors (0603)                                                             |

| C74, C78                                                                                                                          | 2   | 220µF ±20%, 6.3V tantalum<br>capacitors (C case)<br>AVX TPSC227M006R0250 or<br>KEMET T495C227K006ATE225 |

| C75, C79                                                                                                                          | 0   | Not installed, tantalum capacitors (C case)                                                             |

Windows, Windows XP, and Windows Vista are registered trademarks of Microsoft Corp.

SPI is a trademark of Motorola, Inc.

##

Maxim Integrated Products 1

Evaluates: MAX19527

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

Evaluates: MAX19527

| DESIGNATION                                                    | QTY | DESCRIPTION                                                                                               |

|----------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------|

| C76, C80, C82                                                  | 3   | 10μF ±20%, 10V X5R ceramic<br>capacitors (1210)<br>TDK C3225X5R1A106M or<br>Murata GRM32ER61A106K         |

| C83, C85, C86,<br>C88, C131                                    | 5   | 10μF ±20%, 10V X5R ceramic<br>capacitors (0805)<br>TDK C2012X5R1A106K<br>Murata GRM219R61A106K            |

| C84, C87,<br>C91–C94,<br>C99-C102,<br>C107–C110,<br>C115, C116 | 16  | 0.01µF ±10%, 50V X5R ceramic<br>capacitors (0603)<br>Murata GRM188R61H103K or<br>TDK C1608X5R1H103K       |

| C132                                                           | 1   | 1μF ±10%, 10V X5R ceramic<br>capacitor (0603)<br>TDK C1608X5R1A105K<br>Murata GRM188R61A105K              |

| C134                                                           | 1   | 0.033µF ±10%, 16V (min) X5R<br>ceramic capacitor (0603)<br>Murata GRM188R71E333K or<br>TDK C1608X7R1E333K |

| C138, C139, C142,<br>C143                                      | 4   | 22pF ±5%, 50V C0G ceramic<br>capacitors (0603)<br>TDK C1608C0G1H220J                                      |

| CLK, IN1–IN8                                                   | 9   | SMA PC-mount connectors                                                                                   |

| D1                                                             | 1   | Dual Schottky diode (SOT23)<br>Central Semi CMPD6263S+<br>(Top Mark: D96)                                 |

| H1                                                             | 1   | 120-position high-speed connector                                                                         |

| H2                                                             | 1   | Dual-row (2 x 20) 40-pin header                                                                           |

| J1                                                             | 1   | Dual-row (2 x 16) 32-pin header                                                                           |

| J2                                                             | 1   | 2-pin header                                                                                              |

| J10                                                            | 1   | Dual-row (2 x 5) 10-pin header                                                                            |

| JU1–JU8, JU10,<br>JU14, JU15                                   | 11  | 2-pin headers                                                                                             |

| JU9                                                            | 1   | 3-pin header                                                                                              |

| JU11, JU12, JU13                                               | 3   | 4-pin headers                                                                                             |

| JU20–JU27                                                      | 0   | Not installed, 2-pin headers—<br>short                                                                    |

| L101                                                           | 0   | Not installed, ferrite bead<br>(0603)                                                                     |

## Component List (continued)

| DESIGNATION                                                  | QTY                                         | DESCRIPTION                                                                                         |

|--------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------|

| P1                                                           | 1                                           | USB type-B right-angle<br>PC-mount receptacle                                                       |

| R1–R32, R73–R76,<br>R81–R84, R89,<br>R90, R93, R95           | 32, R73–R76,<br>–R84, R89, 44 100Ω ±1% resi |                                                                                                     |

| R33–R48                                                      | 16                                          | $10\Omega \pm 1\%$ resistors (0402)                                                                 |

| R57–R72                                                      | 16                                          | $0\Omega \pm 5\%$ resistors (0805)                                                                  |

| R77–R80, R85–<br>R88, R91, R92,<br>R96, R98, R99, 0 R99, R10 |                                             | Not installed, resistors (0603)<br>R99, R103, and R104 are short<br>(PC trace); all others are open |

| R94                                                          | 1                                           | 10k $\Omega$ potentiometer, 19-turn, 3/8in                                                          |

| R97                                                          | 1                                           | 100k $\Omega$ ±1% resistor (0603)                                                                   |

| R100, R101                                                   | 2                                           | 49.9 $\Omega$ ±1% resistors (0603)                                                                  |

| R130, R131                                                   | 2                                           | $27\Omega \pm 5\%$ resistors (0603)                                                                 |

| R132                                                         | 1                                           | 1.5k $\Omega$ ±5% resistor (0603)                                                                   |

| R133                                                         | 1                                           | 2.2k $\Omega$ ±5% resistor (0603)                                                                   |

| R134, R137                                                   | 2                                           | 10k $\Omega$ ±5% resistors (0603)                                                                   |

| R135                                                         | 1                                           | 470Ω ±5% resistor (0603)                                                                            |

| R136                                                         | 1                                           | 1.1Ω ±5% resistor (0603)                                                                            |

| SW1                                                          | 1                                           | Momentary 6mm pushbutton switch                                                                     |

| T1–T8                                                        | 8                                           | 1:1, 800MHz RF transformers<br>Mini-Circuits ADT1-1WT+                                              |

| Т9                                                           | 1                                           | 1:2 RF transformer<br>Coilcraft TTWB-2-B                                                            |

| U1                                                           | 1                                           | Octal 12-bit 50Msps ADC<br>(144 CTBGA)<br>Maxim MAX19527EXE+                                        |

| U2, U3                                                       | 2                                           | 500mA LDO regulators<br>(8 TDFN-EP*)<br>Maxim MAX8902AATA+<br>(Top Mark: ABG)                       |

| U4, U5, U6                                                   | 3                                           | Dual 2 x 2 crosspoint switches<br>(32 TQFP)<br>Maxim MAX9392EHJ+                                    |

| U7                                                           | 1                                           | TinyLogic ULP-A inverter<br>(6 SC70)<br>Fairchild NC7WV04P6X<br>(Top Mark: V07)                     |

## **Component List (continued)**

| DESIGNATION | QTY | DESCRIPTION                                                          |

|-------------|-----|----------------------------------------------------------------------|

| U8          | 1   | UART-to-USB converter<br>(32 TQFP)<br>FTDI FT232BL                   |

| U9          | 1   | 93C46 type 3-wire EEPROM<br>(8 SO)<br>Atmel AT93C46EN-SH-B           |

| U10         | 1   | Ultra-high-speed<br>microcontroller (44 TQFP)<br>Maxim DS89C450-ENL+ |

| U11         | 1   | Level translator (20 TSSOP)<br>Maxim MAX3002EUP+                     |

| DESIGNATION        | QTY | DESCRIPTION                                            |

|--------------------|-----|--------------------------------------------------------|

| U12                | 1   | Quad three-state driver (14 SO)<br>Fairchild 74AC125SC |

| U13                | 0   | Not installed, LDO regulator<br>(5 SC70)               |

| U14                | 0   | Not installed, level translator<br>(14 TSSOP)          |

| Y1                 | 1   | 14.7456MHz crystal                                     |

| Y2                 | 1   | 6MHz crystal                                           |

| _                  | 15  | Shunts (JU1–JU15)                                      |

| _                  | 1   | PCB: MAX19527 EVALUATION<br>KIT+                       |

| *EP = Exposed pad. |     |                                                        |

## **Component Suppliers**

| SUPPLIER                               | PHONE        | WEBSITE                     |

|----------------------------------------|--------------|-----------------------------|

| AVX Corporation                        | 843-946-0238 | www.avxcorp.com             |

| Central Semiconductor Corp.            | 631-435-1110 | www.centralsemi.com         |

| Coilcraft, Inc.                        | 847-639-6400 | www.coilcraft.com           |

| Fairchild Semiconductor                | 888-522-5372 | www.fairchildsemi.com       |

| KEMET Corp.                            | 864-963-6300 | www.kemet.com               |

| Mini-Circuits                          | 718-934-4500 | www.minicircuits.com        |

| Murata Electronics North America, Inc. | 770-436-1300 | www.murata-northamerica.com |

| Samtec, Inc.                           | 800-726-8329 | www.samtec.com              |

| TDK Corp.                              | 847-803-6100 | www.component.tdk.com       |

Note: Indicate that you are using the MAX19527 when contacting these component suppliers.

## **MAX19527 EV Kit Files**

| FILE                    | DESCRIPTION                                |

|-------------------------|--------------------------------------------|

| INSTALL.EXE             | Installs the EV kit files on your computer |

| MAX19527.EXE            | Application program                        |

| FTD2XX.INF              | USB device driver file                     |

| UNINST.INI              | Uninstalls the EV kit software             |

| USB_Driver_Help_200.PDF | USB driver installation help file          |

**Evaluates: MAX19527**

# Evaluates: MAX19527

## **Quick Start**

#### **Recommended Equipment**

- MAX19527 EV kit

- Single 3.3V, 1A DC power supply

- Signal generator with low phase noise and low jitter for clock input (e.g., HP 8644B)

- Signal generator for analog signal input (e.g., HP 8644B)

- Maxim DCEP

- Analog bandpass filters (e.g., K&L Microwave) for input and clock signals

- User-supplied Windows 2000, Windows XP, or Windows Vista PC with two spare USB ports

**Note:** In the following sections, software-related items are identified by bolding. Text in **bold** refers to items from the EV kit software. Text in **bold and underlined** refers to items from the Windows operating system.

#### Procedure

The EV kit is a fully assembled and tested surface-mount board. Follow the steps below to verify board operation. **Caution: Do not turn on power supplies or enable signal generators until all connections are completed.**

- Verify that shunts are configured in their default positions (Table 1) for proper startup operation of the EV kit software.

- 2) Connect the clock generator output to the clock bandpass filter input.

- Connect the output of the clock bandpass filter to the EV kit CLK SMA connector.

- 4) Connect the outputs of the analog signal generators to the input of the signal bandpass filters. Keep the cable connection between the signal generators, filters, and EV kit board as short as possible for optimum dynamic performance.

- 5) Connect the output of the signal bandpass filters to the IN\_ SMA connectors. It is recommended that a 3dB or 6dB attenuation pad be used to reduce reflections and distortion from the bandpass filter.

- Carefully connect the boards by aligning J5 on the DCEP board to H1 on the EV kit. Gently press them together.

- 7) Connect the USB cable from the computer's type-A USB port to the DCEP board's type-B USB port.

- Connect the 3.3V, 1A power supply to the +3.3V PCB pad. Connect the ground terminal of this supply to the corresponding GND pad.

- 9) Visit <u>www.maxim-ic.com/evkitsoftware</u> to download the latest version of the EV kit software and install it on your computer by running the INSTALL.EXE program. The program files are copied and icons are created in the Windows <u>Start I</u> <u>Programs</u> menu.

- 10) Apply power to the DCEP board at J4 using the DCEP board provided supply connector.

- 11) Enable the 3.3V power supply.

- 12) Enable the signal generators.

- Set the clock signal generator for an output amplitude of ≥ 2.7VP-P (recommended +16dBm to +19dBm for optimum AC performance for input frequencies > 25MHz) and the frequency (fCLK) as appropriate.

- 14) Set the analog input signal generators for an output amplitude of  $\leq$  1.5VP-P, and to the desired frequency.

- 15) Verify that the signal generators are phase locked to each other. Adjust the output power level of the signal generators to overcome cable, bandpass filter, and attenuation pad losses at the input.

- 16) Start the EV kit program by opening its icon in the **Start I Programs** menu.

- 17) Refer to the Data Converter Evaluation Platform (DCEP) User's Guide for information on installing the DCEP software.

- Start the DCEP program by opening its icon in the Start | Programs menu.

- 19) Create a new database in the DCEP by adding the device module file, MAX19527-EVK-xx.dsm. Refer to the Opening a New Database section in the Data Converter Evaluation Platform (DCEP) User's Guide for additional information.

- 20) Collect data using the DCEP software.

## Table 1. Jumper Configuration (JU1–JU15)

| JUMPER  | SHUNT POSITION | EV KIT FUNCTION                                            |

|---------|----------------|------------------------------------------------------------|

| JU1     | Not installed  | IN1 input network disconnected from CMOUT                  |

| 301     | Installed*     | IN1 input network connected to CMOUT                       |

|         | Not installed  | IN2 input network disconnected from CMOUT                  |

| JU2     | Installed*     | IN2 input network connected to CMOUT                       |

| 11.10   | Not installed  | IN3 input network disconnected from CMOUT                  |

| JU3     | Installed*     | IN3 input network connected to CMOUT                       |

| 11.1.4  | Not installed  | IN4 input network disconnected from CMOUT                  |

| JU4     | Installed*     | IN4 input network connected to CMOUT                       |

| 11.15   | Not installed  | IN5 input network disconnected from CMOUT                  |

| JU5     | Installed*     | IN5 input network connected to CMOUT                       |

| 11.10   | Not installed  | IN6 input network disconnected from CMOUT                  |

| JU6     | Installed*     | IN6 input network connected to CMOUT                       |

|         | Not installed  | IN7 input network disconnected from CMOUT                  |

| JU7     | Installed*     | IN7 input network connected to CMOUT                       |

|         | Not installed  | IN8 input network disconnected from CMOUT                  |

| JU8     | Installed*     | IN8 input network connected to CMOUT                       |

|         | 1-2            | SHDN connected to AVDD (power-management mode to SHDN = 1) |

| JU9     | 2-3*           | SHDN connected to GND (power-management mode to SHDN = 0)  |

|         | Not installed  | CMOUT disconnected from input networks                     |

| JU10    | Installed*     | CMOUT connected to input networks                          |

|         | 1-2*           | SCLK signal supplied by the USB circuitry                  |

| JU11    | 1-3            | Maintains the ADC register's content                       |

| JUTT    | 1-4            | For future use                                             |

|         | Not installed  | SCLK signal supplied by an external source at header J10   |

|         | 1-2*           | SDIO signal supplied by the USB circuitry                  |

| JU12    | 1-3            | Maintains the ADC register's content                       |

| JUIZ    | 1-4            | For future use                                             |

|         | Not installed  | SDIO signal supplied by an external source at header J10   |

|         | 1-2*           | CS signal supplied by the USB circuitry                    |

| 11 11 2 | 1-3            | Maintains the ADC register's content                       |

| JU13    | 1-4            | For future use                                             |

|         | Not installed  | CS signal supplied by an external source at header J10     |

| JU14    | Installed*     | 1.8V LDO (U2) powers the AVDD input                        |

| JU 14   | Not installed  | 1.8V LDO(U2) output disconnected from the AVDD input       |

| 1115    | Installed*     | 1.8V LDO (U3) powers the OVDD input                        |

| JU15    | Not installed  | 1.8V LDO (U3) output disconnected from the OVDD input      |

\*Default position.

**Evaluates: MAX19527**

## Detailed Description of Software

#### Software Startup

Before starting the MAX19527 EV kit software, verify that shunts are configured in their default states, as shown in Table 1 and a valid clock signal is applied at the EV kit CLK SMA connector. Upon starting the program, the EV kit software searches for the DS89C40 microcontroller interface circuit. The software then reads the ADC's registers (0x00 to 0x10), updates the software GUI in the **Input/Output/Clock** and **Power Management** tab sheets, and places the register contents (in hex format) next to their respective **Reg00-Reg10** register designators.

#### **User-Interface Panel**

The program's main window contains two tabs, **Input/Output/Clock** (Figure 1) and **Power Management** (Figure 2), which provide controls for the ADC's software-configurable features. The **Input/Output/Clock** tab sheet provides group box controls for **Output Format**, **LVDS Output Adjustments**, **Input Common Mode**

## **Voltage**, and **System Timing**. The **Power Management** tab sheet provides controls for power management.

Changes to the controls result in a write operation that updates the appropriate registers of the ADC. The registers are automatically read after each write operation to verify data sent. Additionally, a **ReadRegs** button is available to read all the ADC registers and to update the main window Reg00–Reg10 register designators. For reference, a list of registers and their content (in hex format) is provided in a column on the right side of the program's main window.

The **Reset** button resets the ADC registers to their power-on-default state.

The bottom status bar of the main window provides the communication status of the EV kit microcontroller interface circuitry. The **Address** and **Data** labels display the last register address written to and its corresponding data, respectively.

| le <u>O</u> ptions <u>H</u> elp     |                                    |                                          |               |      |

|-------------------------------------|------------------------------------|------------------------------------------|---------------|------|

|                                     |                                    |                                          | <u>Req00:</u> | 0x11 |

| nput/Output/Clock Power Management  | ]                                  |                                          | <u>Req01:</u> | 0x00 |

| Output Format                       | CVDS Output Adjustments            | stem Timing                              | <u>Req02:</u> | 0x00 |

| Data<br>Reverse Bit Order LSB First | <sup>CM_Adjust</sup>  1.2V  ▼      | RAME Output<br>est FRAME Level: Normal 🔽 | <u>Req03:</u> | 0x00 |

| Format Binary                       | Current Adjust 3.5mA               |                                          | <u>Req04:</u> | 0x08 |

| Test Data Level: Normal 🔽           |                                    | LK Controls                              | <u>Req05:</u> | 0xFf |

| Data Test Pattern                   | Termination None 🔽                 | PLL Frequency: 39-50MHz                  | <u>Req06:</u> | 0x0( |

| Test Data: Normal 🔽                 |                                    |                                          | <u>Req07:</u> | 0xA/ |

| Test Pattern: Skew 💌                | Input Common Mode Voltage     SELF | Output Phase: Static Low                 | <u>Req08:</u> | 0x55 |

| 0x4A WriteCUSTOM1                   | Adjust: 1.1V 💌                     |                                          | Req09         | 0x5  |

| 0x55 WriteCUSTOM2                   |                                    | st CLKOUT Level: Normal                  | <u>Req10</u>  | 0x5  |

| 0x5A WriteCUST0M1-2                 | Reset ReadRegs                     | 🗖 100 Ohm Input Term.                    | Address:      | 0x00 |

| THREE TENTE                         |                                    |                                          | Data:         | 0x00 |

Figure 1. MAX19527 EV Kit Software (Input/Output/Clock Tab)

#### Input/Output/Clock Tab **Output Format**

The Output Format group box contains several functions that format the output data.

The Reverse Bit Order checkbox allows the user to change the LVDS output data to a MSB-first format and displays the bit-order configuration. The Format checkbox configures the output data format to binary or two's complement, and displays the current data format. The Test Data Level drop-down list gives the user the option of configuring the ADC's OUT1-OUT8 channels to display the normal LVDS data outputs, or setting the channel's outputs to a static high or low state.

#### Data Test Pattern

The Test Data drop-down list gives the user the option to choose between normal and test data modes. Select **Normal** from the drop-down list to operate the LVDS outputs under normal conditions. In normal operation, all GUI functions in the Data Test Pattern group box (with the exception of the **Test Data** drop-down list) are disabled. When Pattern is selected, all GUI functions in the Data Test Pattern group box become active.

The Test Pattern drop-down list allows the user to choose between several test patterns for data-timing alignment. Selecting Normal from the Test Data dropdown list configures the test pattern channels according to the option selected in the Test Data Level drop-down list. Selecting Pattern from the Test Data drop-down list allows the user to generate factory test and custom patterns at the output channels. See Table 2 for generating the IC test patterns.

Three buttons (WriteCUSTOM1, WriteCUSTOM2, and WriteCUSTOM1-2) and their respective edit boxes also become active when Pattern is selected from the Test Data drop-down list. The buttons are available for loading customized 8-bit test patterns in the ADC's 0x07, 0x08, and 0x09 registers. The registers are updated by pressing the WriteCUSTOM1, WriteCUSTOM2, or WriteCUSTOM1-2 buttons.

#### LVDS Output Adjustments

The LVDS Output Adjustments group box contains controls to set the channel OUT1-OUT8 common-mode output voltage, output current, and back termination. The CM\_Adjust drop-down list sets the output driver's common-mode voltage. The Current Adjust drop-down list sets the output driver's current. The Termination drop-down list sets the termination resistance.

#### Input Common-Mode Voltage

When checked, the SELF checkbox applies a commonmode voltage to the ADC's IN\_+/IN\_- input pins and disables the common-mode input pins when not selected. The Adjust drop-down list sets the common-mode voltage according to the value selected. The selected common-mode voltage can be monitored through the CMOUT test point. When enabling SELF, verify that shunts are not installed on jumpers JU1–JU8

#### System Timing

The Test FRAME Level drop-down list gives the user the option of configuring the ADC's FRAME LVDS output channel to display the normal FRAME output frequency (identical to input clock frequency), or setting the FRAME output to a static high or low state.

The CLK Controls group box contains controls for manipulating the input clock signal. The PLL Frequency drop-down list programs the clock multiplier for the internal PLL in order to set the sampling frequency range. Ensure that the input clock frequency, applied at the EV kit CLK SMA connector, falls between the selected minimum and maximum frequency in the drop-down list.

The Output Phase drop-down list adjusts the phase of the serial LVDS output clock (CLKOUT), relative to the output data frame. Refer to the timing diagrams in the MAX19527 IC data sheet for additional information.

The Test CLKOUT Level drop-down list gives the user the option of configuring the ADC's CLKOUT LVDS output channel to display the normal CLKOUT signal, or setting the output signal to a static high or low state.

The 100 Ohm Input Term checkbox switches  $100\Omega$ across differential clock inputs when checked.

| TEST<br>PATTERNS | OUTPUT                                                       |

|------------------|--------------------------------------------------------------|

| Skew             | (010101010101) → repeats every frame                         |

| SYNC             | (111111000000) → repeats every frame                         |

| Custom           | Custom test pattern $\rightarrow$ repeats every two frames   |

| Ramp             | 12-bit ramp from 0 to 4095 and repeats                       |

| Pseudo9          | Pseudorandom data pattern<br>(short 2 <sup>9</sup> sequence) |

| Pseudo23         | Pseudorandom data pattern<br>(long 2 <sup>23</sup> sequence) |

#### Table 2. Test Pattern Selection

\_\_\_\_

valuates: MAX19527

L

Refer to the *System Timing Requirements* section in the MAX19527 IC data sheet for additional information for configuring the Data, FRAME, and CLKOUT test levels.

#### **Power Management Tab** Power Management Controls

The **Power Management** group box contains two sets of controls. The first set is used only when the SHDN pin on the EV kit is set low and the second set is used only when the SHDN pin on the EV kit is set high. When checked, the **IN1 Active-IN8 Active** checkboxes enable the input channel, or disable the input channel when left unchecked. The **Sleep/Nap Mode** checkbox toggles between nap mode when checked and sleep mode when unchecked, as long as the **IN1 Active-IN8 Active** checkboxes are left unchecked. The **Enable AII** and **Disable AII** buttons are available to enable and disable all input channels simultaneously. For more details on power management, refer to the MAX19527 IC data sheet.

#### **Advanced User Interface**

A serial interface can be used by advanced users by selecting the **Options I Interface (Advanced Users)** menu item. Custom bit-banging firmware commands are used to implement a bidirectional SPI interface. Read addresses always begin with 0x8\_ and write addresses always begin with 0x0\_.

For writing to registers, click on the **Connection** tab (Figure 3). Enter the raw command bytes value of **0x77 0x05 0xA0 0xA0** (where 0x05 is the register write address in hexadecimal, and 0xA0, 0xA0 are the data in this example), then press the **Send raw command bytes** button. Note that the custom firmware uses data transfer of two bytes.

For reading registers, enter the raw command bytes value of **0x72 0x85** (where 0x85 is the register read address in hexadecimal), then press the **Send raw command bytes** button. The register address and content are displayed as the first and second byte of data listed under the **Returned data [hexadecimal]** label, respectively (Figure 4).

|                                     |                                     | <u>Req00:</u> 0x1 |

|-------------------------------------|-------------------------------------|-------------------|

| nput/Dutput/Clock Power Management  |                                     | <u>Req01:</u> 0x0 |

| -Power Management                   | 1                                   | <u>Req02:</u> 0x0 |

| **Use when SHDN = 0 (IC bump B10)** | **Use when SHDN = 1 (IC bump B10)** | <u>Req03:</u> 0x0 |

| ☑ IN1 Active Enable All             | IN1 Active Enable All               | <u>Req04:</u> 0x0 |

| ☑ IN2 Active                        | IN2 Active                          | Reg05: 0xFi       |

| ☑ IN3 Active Disable All            | IN3 Active Disable All              |                   |

| ☑ IN4 Active                        | ☐ IN4 Active                        | <u>Req06:</u> 0x0 |

| IN5 Active                          | IN5 Active                          | <u>Req07:</u> 0xA |

| IN6 Active                          | IN6 Active                          | <u>Req08:</u> 0x5 |

| V IN7 Active                        | IN7 Active                          |                   |

| ☑ IN8 Active                        | IN8 Active                          | <u>Req09</u> 0x5  |

| ☑ Sleep/Nap Mode                    | 🗖 Sleep/Nap Mode                    | Reg10 0x5         |

|                                     |                                     | Address: 0x0      |

|                                     |                                     | Data: 0x0         |

Figure 2. MAX19527 EV Kit Software (Power Management Tab)

M/IXI/M

| Connection Hardware Connection to Command Module Connect to hardware Disconnect USB:0@115200 baud USB not connected; no VID/PID value Baud Rate: Automatic  Firmware banner must begin with: Maxim Connect Commands                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0xFF       Rx payload bytes expected:         Send packet (0xAA, Length16, payload, checksum) (0x80=escape)       1         0x77 0x00 0xA0 0xA0       Rx bytes expected:         0xr77 0x00 0xA0 0xA0       1         Send raw command bytes       1 |

| Returned data (hexadecimal):<br>0x2B 0x3E                                                                                                                                                                                                            |

| Returned data (characters):<br>+><br>Maxim MAX19527 EVKIT USB:0 @ 115200 baud Speed failed                                                                                                                                                           |

Figure 3. Advanced User Interface Window (3-Wire Interface Tab)—Writing to a Register

| Advanced User Interface<br>Dptions Help<br>Connection<br>Hardware Connection to Command M<br>Connect to hardware Discon<br>Baud Rate: Automatic Firmw<br>Low Level Commands<br>DxFF<br>Send packet (0xAA, Length16, page<br>0x72 0x85<br>Send raw command bytes<br>Returned data (hexadecimal):<br>0x85 0xA0 0x00 0x28 0x3E | MAX19527 EVKIT<br>USB:0 @ 115200 baud<br>USB not connected; no<br>vare banner must begin with: | axim Rx payload bytes expected: |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------|--|

| Returned data (characters):<br>+>                                                                                                                                                                                                                                                                                           |                                                                                                |                                 |  |

| Maxim MAX19527 EVKIT                                                                                                                                                                                                                                                                                                        | USB:0 @ 115200 baud                                                                            | Speed failed                    |  |

Figure 4. Advanced User Interface Window (3-Wire Interface Tab)—Reading a Register

**Evaluates: MAX19527**

#### **Keyboard Navigation**

Press Ctrl + Tab to navigate to the tab sheets. The selected tab sheet is indicated by a dotted outline. Press the Tab key to select each GUI control. The selected control is indicated by a dotted outline. Using Shift + Tab moves the selection to the previously selected control. Buttons respond to the keyboard's space bar and some controls respond to the keyboard's up and down arrow keys. Activate the program's menu bar by pressing the F10 key and then press the letter of the desired menu item. Most menu items have one letter underlined, indicating their shortcut key.

When a number is entered into the edit boxes, it can be sent to the device by pressing the Enter key. The data is also sent when Tab or Shift + Tab is pressed.

## \_Detailed Description of Hardware

The MAX19527 EV kit is a fully assembled and tested circuit board that contains all the components necessary to evaluate the performance of the MAX19527 50Msps octal, 12-bit ADC.

The ADC accepts differential input signals; however, on-board transformers (T1–T8) convert the single-ended signals applied to the IN1–IN8 SMA connectors to the required differential signals. The input signals of the ADC can be measured using a differential oscilloscope probe at header J1. The ADC's digital LVDS output signals are accessible at header H2. Output drivers (U4, U5, and U6) are used for buffering the LVDS output signals when interfacing the EV kit to the DCEP board.

The EV kit can be configured for communicating to the SPI interface using the on-board USB circuitry or a usersupplied external 3-wire controller using jumpers JU11 JU12, and JU13.

The EV kit is designed as a six-layer PCB to optimize the performance of the ADC. Separate analog, digital, and buffer power planes minimize noise coupling between analog and digital signals. The analog and clock inputs

# Table 3. AVDD Input Power Configuration (JU14)

| SHUNT POSITION | AVDD (V)                                  |

|----------------|-------------------------------------------|

| Installed*     | 1.8V LDO (U2) powers the AVDD<br>input    |

| Not installed  | Power disconnected from the<br>AVDD input |

\*Default position.

and the LVDS outputs use 100 $\Omega$  differential microstrip transmission lines. All singled-ended digital outputs use 50 $\Omega$  microstrip transmission lines. The trace lengths of the 100 $\Omega$  differential LVDS output lines are matched to within a few thousands of an inch to minimize layout-dependent output-signal skew.

#### **Power Supplies**

The EV kit operates from a single 3.3V DC power supply applied at the +3.3V and GND PCB pads and provides on-board regulation to power the IC analog and digital circuit blocks, and the MAX9392 LVDS buffers.

The analog circuit block (AVDD) is regulated to 1.8V using the MAX8902A (U2). To power the analog circuit using the EV kit circuitry, install a shunt on jumper JU14. To disconnect the 1.8V power source, remove the shunt at JU14. See Table 3 for proper JU14 configuration.

The digital circuit block (OVDD) is regulated to 1.8V using the MAX8902A (U3). To power the digital circuit using the EV kit circuitry, install a shunt on jumper JU15. To disconnect the 1.8V power source from OVDD, remove the shunt on JU15. See Table 4 for proper JU15 configuration.

Jumpers JU14 and JU15 are provided to disconnect the power sources or to measure current through AVDD and OVDD, respectively.

#### **Clock Input**

The data converter allows either differential or singleended signals to drive the clock inputs. The EV kit supports both methods.

In single-ended operation, the clock signal is applied at the CLK SMA connector and connects to the ADC through a buffer (U7). In differential mode, an on-board transformer converts a user-supplied single-ended analog input and generates a differential analog signal, which is then applied to the ADC's input pins. The clock signal applied to the ADC can be observed at header J2.

# Table 4. OVDD Input Power Configuration (JU15)

| SHUNT POSITION | OVDD (V)                                  |

|----------------|-------------------------------------------|

| Installed*     | 1.8V LDO (U3) powers the OVDD<br>input    |

| Not installed  | Power disconnected from the<br>OVDD input |

\*Default position.

#### Configuring the EV Kit for Single-Ended Clock Operation

To configure the EV kit for single-ended clock operation, the following modifications must be made to the clock circuit:

- 1) Cut the traces at locations R99, R103, and R104.

- 2) Install 0 $\Omega$  resistors at locations R96, R102, and R105.

- 3) Install a 49.9 $\Omega$  ±1% resistor at location R98.

In single-ended clock configuration, potentiometer R94 can be utilized to control the duty cycle of the clock input signal. Measure the clock input at header J2 and adjust R94 until the desired duty cycle is achieved.

#### Input Signals

Although the ADC accepts differential analog input signals, the EV kit only requires single-ended analog input signals. Insertion losses due to a series-connected filter and the interconnecting cables decrease the amount of power seen at the EV kit input. Account for these losses when setting the signal generator amplitude. On-board transformers (T1–T8) convert the single-ended analog input signals and generate the recommended differential analog signals at the ADC's differential input pins.

Jumpers JU1–JU8 are available to provide a common-mode voltage to the EV kit input circuit networks when jumper JU10 is installed. JU10 supplies the programmed common-mode voltage supplied by the ADC's CMOUT output. Install a shunt on JU10 and the respective IN\_ channel jumpers to set the input network

common-mode voltage. See Table 5 for proper jumper configuration.

#### **Output Signals**

The ADC features eight 12-bit, serial, LVDS digital outputs (OUT\_) that transmit the converted differential analog input signals (IN1–IN8). Two additional outputs (CLKOUT and FRAME) are provided for system timing. Refer to the *System Timing Requirements* section in the MAX19527 IC data sheet for additional information.

#### **Output Termination**

The ADC features trimmed, selectable internal termination resistors between the positive and negative line of each output (OUT1-OUT8, CLKOUT, and FRAME). The EV kit circuit also features  $100\Omega$  termination resistors for the ADC output, located at the inputs of the MAX9392 LVDS crosspoint switches (U4, U5, and U6). MAX9392 ICs are used to buffer the ADC's outputs when connecting the DCEP board to the EV kit, which allows monitoring of the output signals at header H2.

#### **SPI Interface Control**

The EV kit communicates to the ADC's SPI interface using the on-board USB circuitry or external 3-wire signals (applied at header J10).

Place shunts across pins 1-2 of jumpers JU11, JU12, and JU13 to control the SPI interface using the USB circuitry. Remove shunts from JU11, JU12, and JU13 when using external 3-wire signals at header J10. See Tables 6, 7, and 8 for proper JU11, JU12, and JU13 configuration, respectively.

### Table 5. IN\_ Common-Mode Input-Voltage Configuration (JU10, JU1–JU8)

| SHUNT F           | POSITION      | INPUT NETWORKS (IN1–IN8)                          |  |

|-------------------|---------------|---------------------------------------------------|--|

| JU10              | JU1–JU8       | COMMON-MODE SETTING                               |  |

| lo atalla d*      | Installed*    | Input network connected to CMOUT                  |  |

| Installed* Not    | Not installed | Input common-mode voltage disconnected from CMOUT |  |

| Not installed     | Х             | Input networks disconnected from CMOUT            |  |

| Default position. | · · · · · ·   |                                                   |  |

X = Don't care

## Table 6. SCLK Input Configuration (JU11)

| SHUNT POSITION | SCLK PIN                                              | EV KIT FUNCTION                                          |

|----------------|-------------------------------------------------------|----------------------------------------------------------|

| 1-2*           | Connects to SCLK EV kit level<br>translator circuitry | SCLK signal supplied by USB circuitry                    |

| 1-3            | Connects to ground                                    | Maintains the ADC register's content                     |

| 1-4            | Connects to SCLK DCEP<br>level translator circuitry   | For future use                                           |

| Not installed  | Connects to header J10-1                              | SCLK signal supplied by an external source at header J10 |

\*Default position.

To maintain the ADC's current register content, place shunts across pins 1-3 of JU11, JU12, and JU13.

#### Shutdown (SHDN)

The ADC can also be placed in a low-power shutdown mode through jumper JU9. The SHDN pin is a toggle switch between two power-management states, shown in Figure 2 under the **Power Management** group box of the software interface. When a shunt is installed on pins 1-2 of JU9, SHDN is connected to AVDD and the user can select the appropriate settings for inputs **IN1 Active-IN8 Active** and **Sleep/Nap Mode** under the label **\*\*Use when SHDN = 1 (IC bump B10)\*\***. When a shunt is installed on pins 2-3 of JU9, SHDN is connected to GND and the user can select the appropriate settings for inputs **IN1 Active-IN8 Active** and **Sleep/Nap Mode** under the label **\*\*Use when SHDN = 0 (IC bump B10)\*\***. See Table 9 for proper JU9 configuration for shutdown control of the EV kit.

#### Connecting the DCEP to the EV Kit

The DCEP and EV kit board can be connected using the specified on-board connectors. H1 on the EV kit mates with J5 on the DCEP board. Alternatively, the two boards can be connected with coaxial ribbon cables (Samtec, part no. HQCD-060.00-STR-TBR-1). Note that it is necessary to use either the on-board connectors or cables to obtain a reliable electrical connection between the two boards.

#### Using the DCEP with the EV Kit

Maxim's DCEP is required for evaluation of this EV kit. An EV kit-specific device module file is required to configure the DCEP software. The most up-to-date device module file can be downloaded from <u>www.maxim-ic.</u> <u>com/evkitsoftware</u>. When loading the DCEP device module file, select MAX19527-EVK-xx.dsm and verify that the device module GUI window corresponds to Figure 5. Refer to the *Opening a New Database* section in the Data Converter Evaluation Platform (DCEP) User's Guide for additional information.

| SHUNT POSITION | SDIO PIN                                              | EV KIT FUNCTION                                          |

|----------------|-------------------------------------------------------|----------------------------------------------------------|

| 1-2*           | Connects to SDIO EV kit level<br>translator circuitry | SDIO signal supplied by USB circuitry                    |

| 1-3            | Connects to ground                                    | Maintains the ADC register's content                     |

| 1-4            | Connects to SDIO DCEP level<br>translator circuitry   | For future use                                           |

| Not installed  | Connects to header J10-5                              | SDIO signal supplied by an external source at header J10 |

## Table 7. SDIO Input Configuration (JU12)

\*Default position.

## Table 8. CS Input Configuration (JU13)

| SHUNT POSITION | CS PIN                                                               | EV KIT FUNCTION                                        |

|----------------|----------------------------------------------------------------------|--------------------------------------------------------|

| 1-2*           | Connects to $\overline{\text{CS}}$ EV kit level translator circuitry | CS signal supplied by USB circuitry EV kit software    |

| 1-3            | Connects to ground                                                   | Maintains the ADC register's content                   |

| 1-4            | Connects to CS DCEP level translator circuitry                       | For future use                                         |

| Not installed  | Connects to header J10-3                                             | CS signal supplied by an external source at header J10 |

\*Default position.

### Table 9 SHDN Configuration (JU9)

| SHUNT POSITION | SHND PIN          | EV KIT FUNCTION                                                         |

|----------------|-------------------|-------------------------------------------------------------------------|

| 1-2*           | Connected to AVDD | Use <b>**When SHDN = 1 (IC bump B10)**</b><br>software GUI box controls |

| 2-3            | Connected to GND  | Use <b>**When SHDN = 0 (IC bump B10)**</b><br>software GUI box controls |

\*Default position.

12 \_

MAX19527

Evaluates:

#### **Evaluates: MAX19527** × 🗆 -× NIXVN Channel #1 Channel #2 Channel #3 Channel #4 Channel #5 Channel #5 Channel #5 Channel #5 Data Valid Code Number RAW DATA 📺 Raw Data 🛃 Normalized Data 🛄 FFT 📑 Info 🛄 Histogram 🔟 INL 🔤 DNL ▶ ▶ ▶ | ▶ | <sup>0</sup> = <sup>3</sup> = 2 Channel: Channel #1 • | ⊡ 函 | ⊡ 函 | ⊡ ⊡ 函 eule Value [19527.ddb] - [Channel Eile <u>View Hardware Window Help</u> Engineering × न ٣ ADC Test Parameters and ADC Record Info d -Offset Binary 0 Hz 0 dBm Offset Binary 0 Hz 0 dBm 🗋 💕 📕 🗄 k Pointer • 🏽 🕲 🕄 0 Hz 0 dBm 4096 None EEE Independent Window Func False Independent Calculation OF False --1 of 1 11월 12 - 11월 12 - 114 ADC Test Parameters 😴 Status: Connected Window Function FFT Filter Type Input (Channel I Digital Data Type I Input (Channel Digital Data Type Record: 🕅 🤞 Number of Points Data Conv Frequency Amplitude Link To: ADC Notes Frequency Amplitude Frequency Amplitude Link To: Link To: AR

# **MAX19527 Evaluation Kit**

Figure 5. Device Module DCEP GUI Window

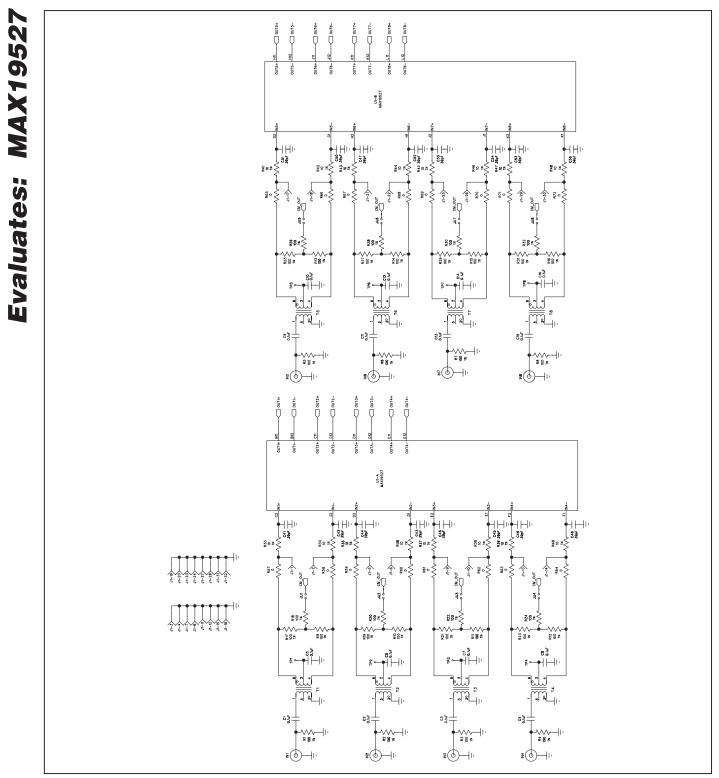

Figure 6a. MAX19527 EV Kit Schematic (Sheet 1 of 4)

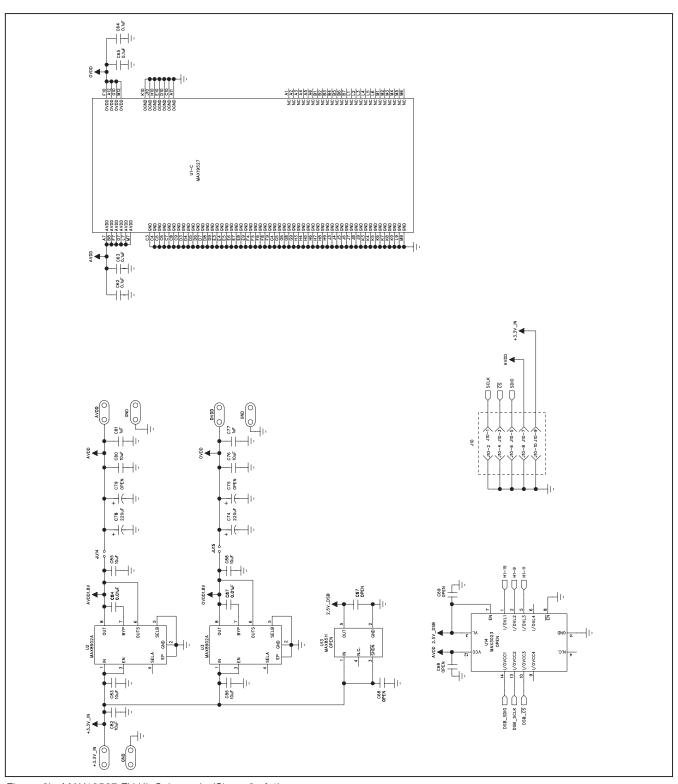

Figure 6b. MAX19527 EV Kit Schematic (Sheet 2 of 4)

**Evaluates: MAX19527**

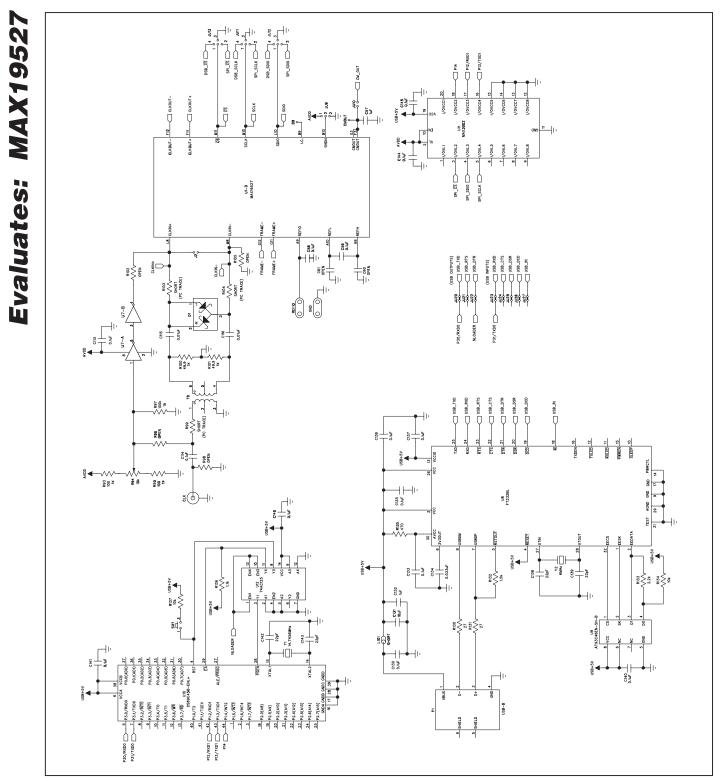

Figure 6c. MAX19527 EV Kit Schematic (Sheet 3 of 4)

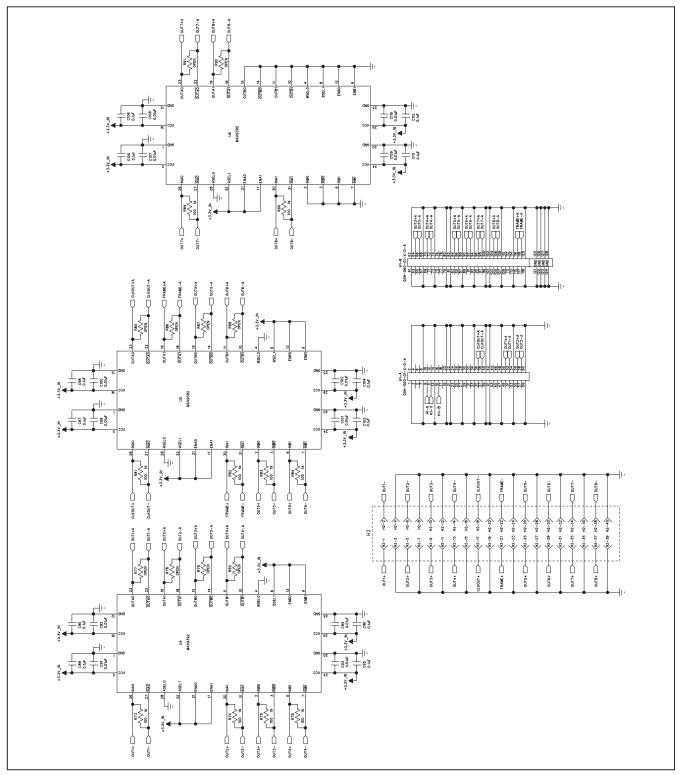

Figure 6d. MAX19527 EV Kit Schematic (Sheet 4 of 4)

**Evaluates: MAX19527**

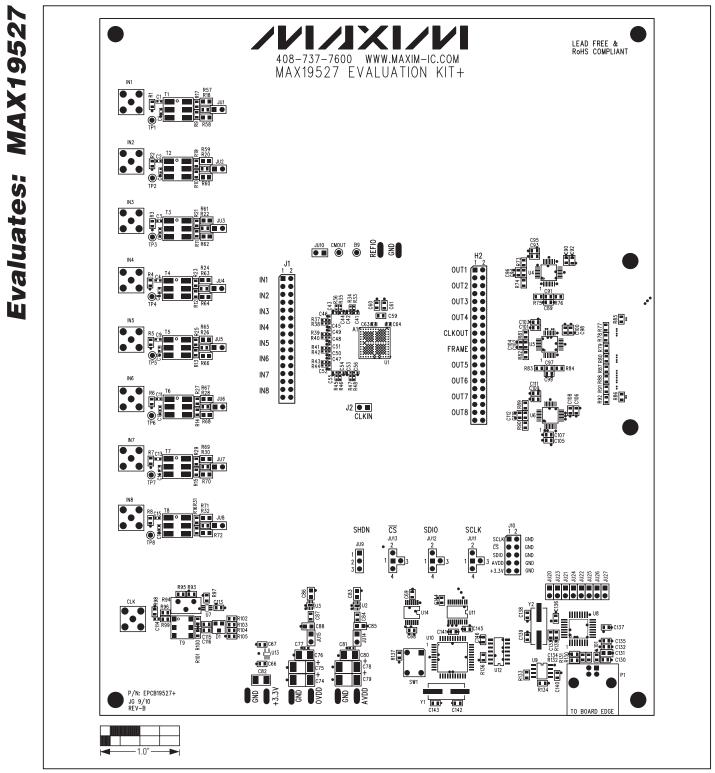

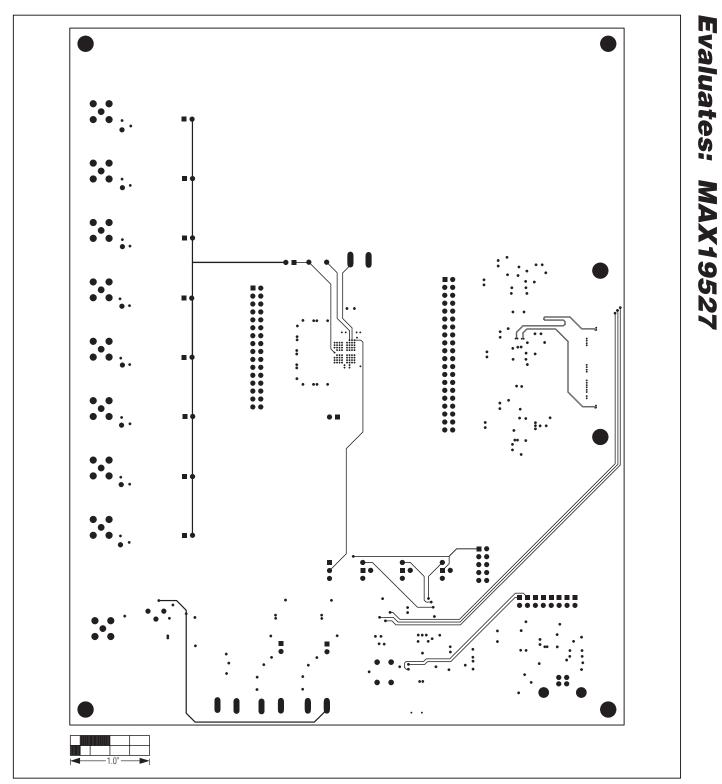

Figure 7. MAX19527 EV Kit Component Placement Guide—Component Side

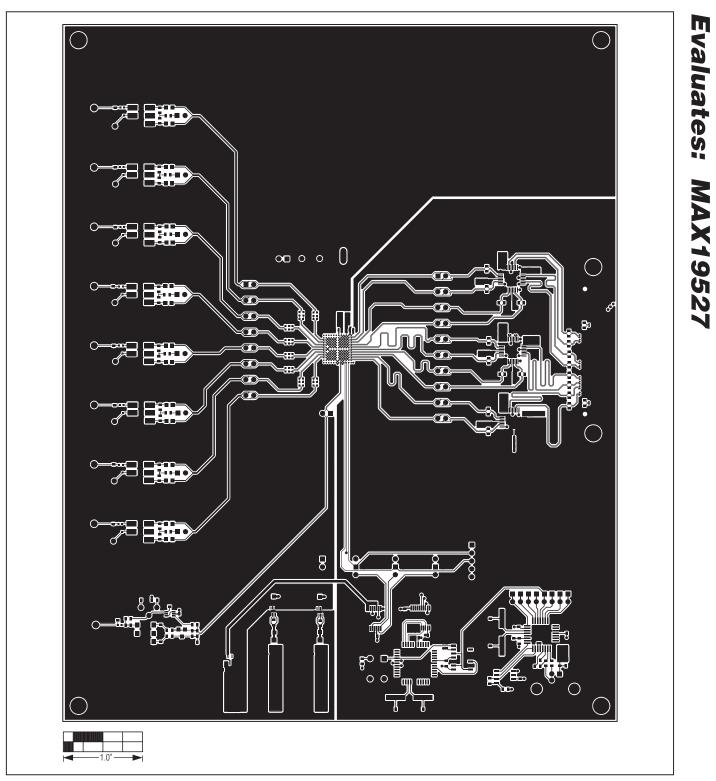

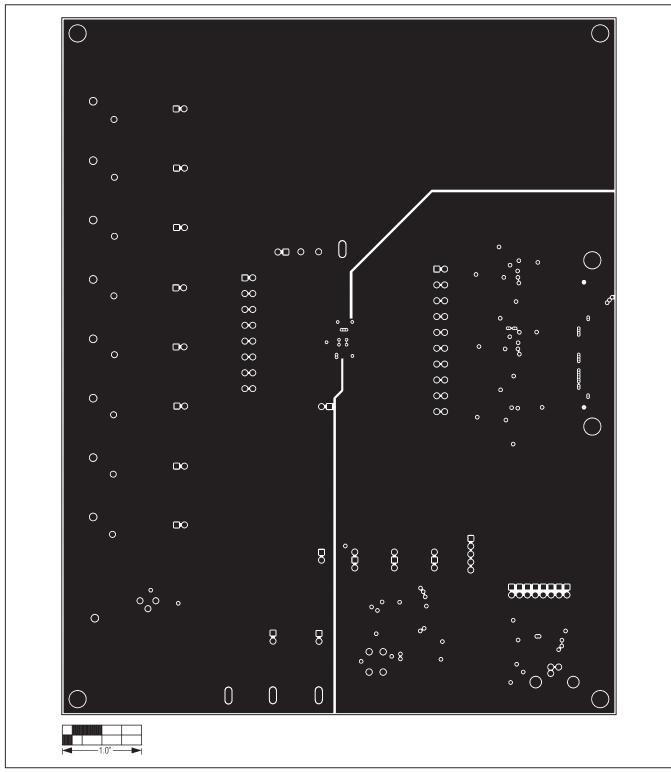

Figure 8. MAX19527 EV Kit PCB Layout—Component Side

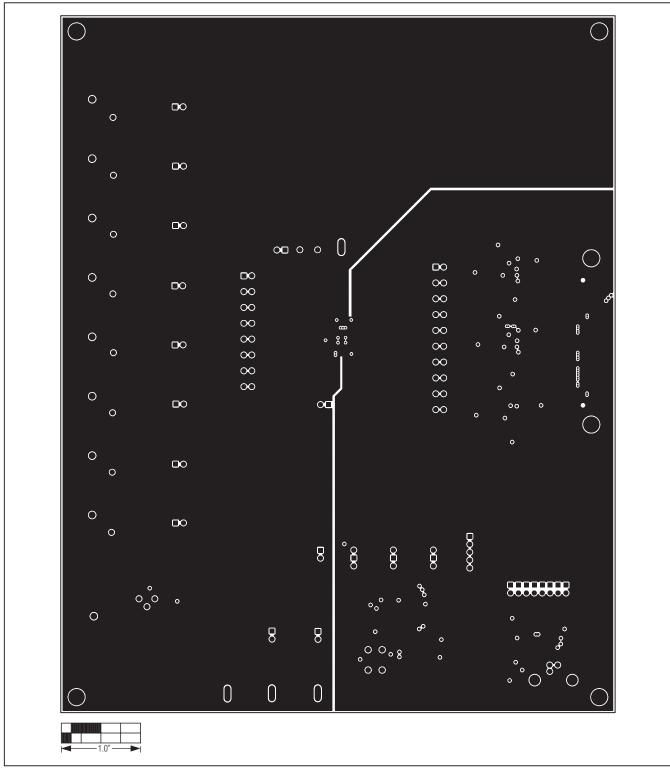

Figure 9. MAX19527 EV Kit PCB Layout (Inner Layer 2)—Ground Planes

Evaluates: MAX19527

Downloaded from Elcodis.com electronic components distributor

20

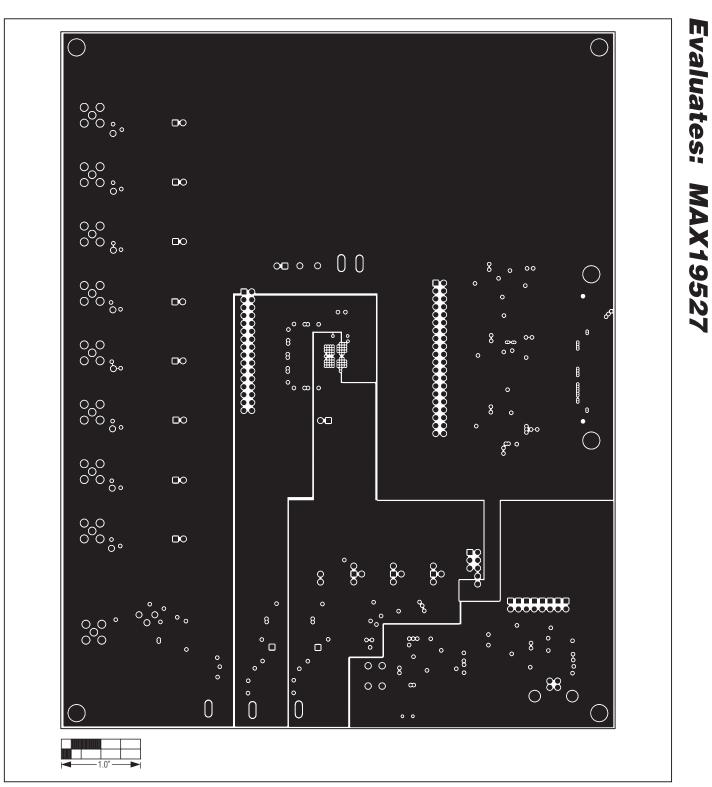

Figure 10. MAX19527 EV Kit PCB Layout (Inner Layer 3)—Power Planes

# **MAX19527 Evaluation Kit**

Figure 11. MAX19527 EV Kit PCB Layout (Inner Layer 4)—Ground Planes

Figure 12. MAX19527 EV Kit PCB Layout (Inner Layer 5)—Routing Plane

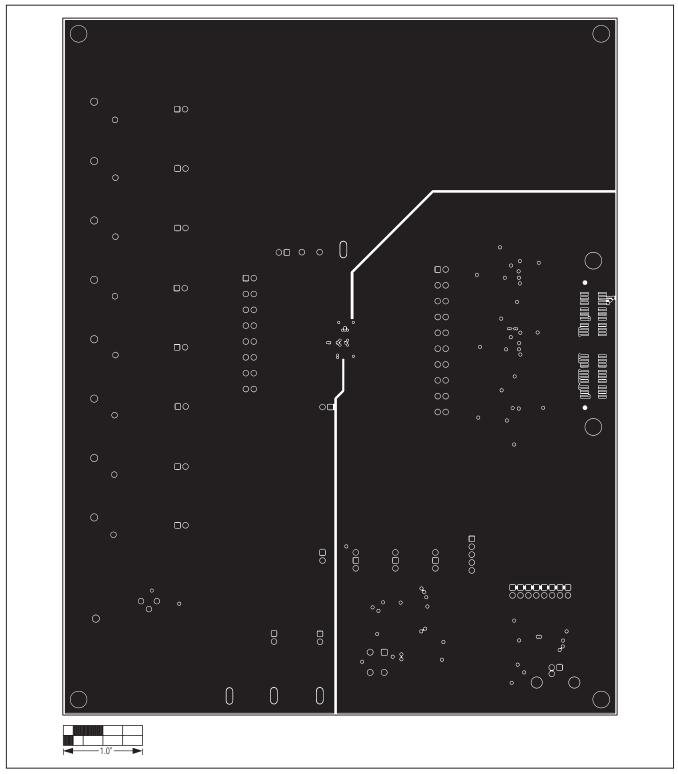

Figure 13. MAX19527 EV Kit PCB Layout—Solder Side

Evaluates: MAX19527

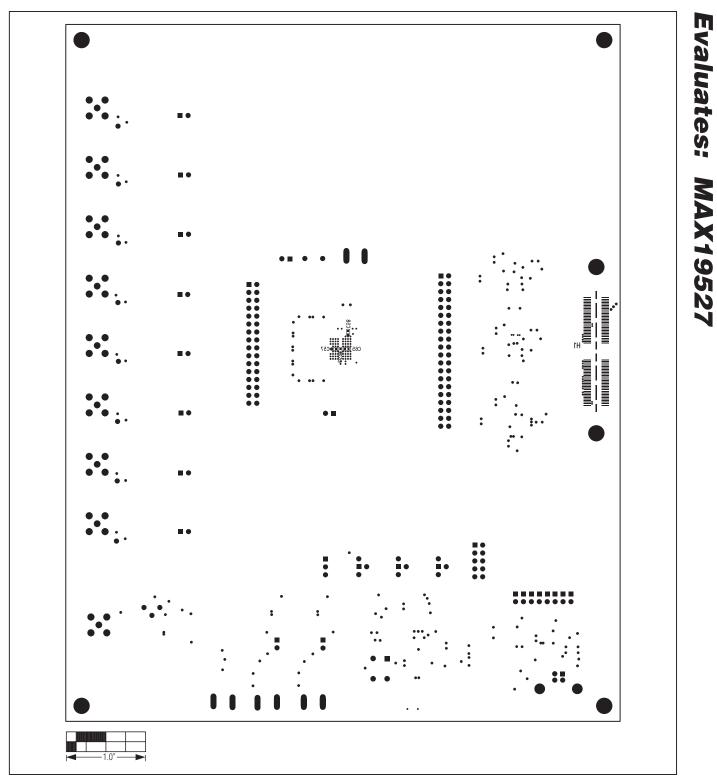

Figure 14. MAX19527 EV Kit PCB Component Placement Guide—Solder Side

Initial release

# Evaluates: MAX19527

REVISION

NUMBER

0

REVISION

DATE

9/10

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

DESCRIPTION

26

\_\_\_\_\_ Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2010 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.

**Revision History**

PAGES

CHANGED

\_\_\_\_