# 5V, 64 Kbit (8Kb x 8) ZEROPOWER® SRAM

### **FEATURES SUMMARY**

- INTEGRATED, ULTRA LOW POWER SRAM AND POWER-FAIL CONTROL CIRCUIT

- UNLIMITED WRITE CYCLES

- READ CYCLE TIME EQUALS WRITE CYCLE TIME

- AUTOMATIC POWER-FAIL CHIP DESELECT AND WRITE PROTECTION

- WRITE PROTECT VOLTAGES (V<sub>PFD</sub> = Power-fail Deselect Voltage):

- M48Z08: V<sub>CC</sub> = 4.75 to 5.5V

4.5V ≤ V<sub>PFD</sub> ≤ 4.75V

- M48Z18:  $V_{CC} = 4.5 \text{ to } 5.5V$  $4.2V \le V_{PFD} \le 4.5V$

- SELF-CONTAINED BATTERY IN THE CAPHAT™ DIP PACKAGE

- PIN AND FUNCTION COMPATIBLE WITH JEDEC STANDARD 8K x 8 SRAMs

- RoHS COMPLIANCE

Lead-free components are compliant with the RoHS Directive.

# **SUMMARY DESCRIPTION**

The M48Z08/18 ZEROPOWER® RAM is a 8K x 8 non-volatile static RAM which is pin and functional compatible with the DS1225.

The monolithic chip is available in two special packages to provide a highly integrated battery backed-up memory solution.

The M48Z08/18 is a non-volatile pin and function equivalent to any JEDEC standard 8K x 8 SRAM.

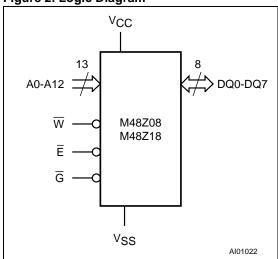

Figure 2. Logic Diagram

Figure 3. DIP Connections

|                      |        |        | •     |

|----------------------|--------|--------|-------|

| NC [ 1               | $\cup$ | 28     | ] ∨cc |

| A12 🛚 2              |        | 27     | j W   |

| A7 [ 3               |        | 26     | ] NC  |

| A6 🛚 4               |        | 25     | ] A8  |

| A5 [ 5               |        | 24     | ] A9  |

| A4 [ 6               |        | 23     | A11   |

| A3 [ 7               | M48Z08 | 22     | ] G   |

| A2 [ 8               | M48Z18 | 21     | ] A10 |

| A1 [ 9               |        | 20     | JĒ    |

| A0 [ 10              |        | 19     | DQ7   |

| DQ0 [ 11             |        | 18     | DQ6   |

| DQ1 [ 12             |        | 17     | ] DQ5 |

| DQ2 [ 13             |        | 16     | ] DQ4 |

| V <sub>SS</sub> [ 14 |        | 15     | DQ3   |

|                      | А      | 101183 | •     |

|                      |        |        |       |

It also easily fits into many ROM, EPROM, and EEPROM sockets, providing the non-volatility of PROMs without any requirement for special write timing or limitations on the number of writes that can be performed.

The 28-pin, 600mil DIP CAPHAT™ houses the M48Z08/18 silicon with a long life lithium button cell in a single package.

Table 1. Signal Names

| A0-A12          | Address Inputs           |

|-----------------|--------------------------|

| DQ0-DQ7         | Data Inputs / Outputs    |

| Ē               | Chip Enable              |

| G               | Output Enable            |

| W               | WRITE Enable             |

| Vcc             | Supply Voltage           |

| V <sub>SS</sub> | Ground                   |

| NC              | Not Connected Internally |

#### **READ Mode**

The M48Z08/18 is in the READ Mode whenever  $\overline{W}$  (WRITE Enable) is high and  $\overline{E}$  (Chip Enable) is low. The device architecture allows ripple-through access of data from eight of 65,536 locations in the static storage array. Thus, the unique address specified by the 13 address inputs defines which one of the 8,192 bytes of data is to be accessed. Valid data will be available at the Data I/O pins within address access time ( $t_{AVQV}$ ) after the last address input signal is stable, providing that the  $\overline{E}$  and  $\overline{G}$  access times are also satisfied. If the  $\overline{E}$  and  $\overline{G}$  access times are not met, valid data will be

available after the latter of the Chip Enable Access time ( $t_{\text{ELQV}}$ ) or Output Enable Access time ( $t_{\text{GLQV}}$ ).

The state of the eight three-state Data I/O signals is controlled by  $\overline{E}$  and  $\overline{G}.$  If the outputs are activated before  $t_{AVQV},$  the data lines will be driven to an indeterminate state until  $t_{AVQV}.$  If the address inputs are changed while  $\overline{E}$  and  $\overline{G}$  remain active, output data will remain valid for Output Data Hold time  $(t_{AXQX})$  but will go indeterminate until the next address access.

tAVAV VALID A0-A12 tAVQV tAXQX tELQV tEHQZ Ē tELQX tGLQV tGHQZ G tGLQX VALID DQ0-DQ7 AI01385

Figure 5. READ Mode AC Waveforms

Note: WRITE Enable  $(\overline{W})$  = High.

**Table 3. READ Mode AC Characteristics**

| Symbol                           | D (1)                                   | M48Z08        | M48Z08/M48Z18 |      |  |

|----------------------------------|-----------------------------------------|---------------|---------------|------|--|

|                                  | Parameter <sup>(1)</sup>                | Min           | Max           | Unit |  |

| t <sub>AVAV</sub>                | READ Cycle Time                         | 100           |               | ns   |  |

| t <sub>AVQV</sub>                | Address Valid to Output Valid           |               | 100           | ns   |  |

| t <sub>ELQV</sub>                | Chip Enable Low to Output Valid         | put Valid 100 |               | ns   |  |

| t <sub>GLQV</sub>                | Output Enable Low to Output Valid       |               | 50            | ns   |  |

| t <sub>ELQX</sub> (2)            | Chip Enable Low to Output Transition    | 10            |               | ns   |  |

| t <sub>GLQX</sub> <sup>(2)</sup> | Output Enable Low to Output Transition  | 5             |               | ns   |  |

| t <sub>EHQZ</sub> (2)            | Chip Enable High to Output Hi-Z         |               | 50            | ns   |  |

| t <sub>GHQZ</sub> <sup>(2)</sup> | Output Enable High to Output Hi-Z       |               | 40            | ns   |  |

| t <sub>AXQX</sub>                | Address Transition to Output Transition | 5             |               | ns   |  |

Note: 1. Valid for Ambient Operating Temperature:  $T_A = 0$  to  $70^{\circ}$ C;  $V_{CC} = 4.75$  to 5.5V or 4.5 to 5.5V (except where noted).

2.  $C_L = 30pF$ .

**Table 4. WRITE Mode AC Characteristics**

| 0                                  | Paramatar(1)                            | M48Z08 | /M48Z18 | 1124 |

|------------------------------------|-----------------------------------------|--------|---------|------|

| Symbol                             | Parameter <sup>(1)</sup>                | Min    | Max     | Unit |

| t <sub>AVAV</sub>                  | WRITE Cycle Time                        | 100    |         | ns   |

| t <sub>AVWL</sub>                  | Address Valid to WRITE Enable Low       | 0      |         | ns   |

| t <sub>AVEL</sub>                  | Address Valid to Chip Enable 1 Low      | 0      |         | ns   |

| t <sub>WLWH</sub>                  | WRITE Enable Pulse Width                | 80     |         | ns   |

| teleh                              | Chip Enable Low to Chip Enable 1 High   | 80     |         | ns   |

| t <sub>WHAX</sub>                  | WRITE Enable High to Address Transition | 10     |         | ns   |

| t <sub>EHAX</sub>                  | Chip Enable High to Address Transition  | 10     |         | ns   |

| t <sub>DVWH</sub>                  | Input Valid to WRITE Enable High        | 50     |         | ns   |

| t <sub>DVEH</sub>                  | Input Valid to Chip Enable 1 High       | 30     |         | ns   |

| t <sub>WHDX</sub>                  | WRITE Enable High to Input Transition   | 5      |         | ns   |

| t <sub>EHDX</sub>                  | Chip Enable High to Input Transition    | 5      |         | ns   |

| t <sub>WLQZ</sub> (2,3)            | WRITE Enable Low to Output Hi-Z         |        | 50      | ns   |

| t <sub>AVWH</sub>                  | Address Valid to WRITE Enable High      | 80     |         | ns   |

| t <sub>AVEH</sub>                  | Address Valid to Chip Enable High       | 80     |         | ns   |

| t <sub>WHQX</sub> <sup>(2,3)</sup> | WRITE Enable High to Output Transition  | 10     |         | ns   |

Note: 1. Valid for Ambient Operating Temperature: T<sub>A</sub> = 0 to 70°C; V<sub>CC</sub> = 4.75 to 5.5V or 4.5 to 5.5V (except where noted).

2. C<sub>L</sub> = 30pF.

3. If E goes low simultaneously with W going low, the outputs remain in the high impedance state.

### **MAXIMUM RATING**

Stressing the device above the rating listed in the "Absolute Maximum Ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is

not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

**Table 5. Absolute Maximum Ratings**

| Symbol                          | Parameter                                                 | Value     | Unit |

|---------------------------------|-----------------------------------------------------------|-----------|------|

| T <sub>A</sub>                  | Ambient Operating Temperature                             | 0 to 70   | °C   |

| T <sub>STG</sub>                | Storage Temperature (V <sub>CC</sub> Off, Oscillator Off) | -40 to 85 | °C   |

| T <sub>SLD</sub> <sup>(1)</sup> | Lead Solder Temperature for 10 seconds                    | 260       | °C   |

| V <sub>IO</sub>                 | Input or Output Voltages                                  | -0.3 to 7 | V    |

| Vcc                             | Supply Voltage                                            | -0.3 to 7 | V    |

| Io                              | Output Current                                            | 20        | mA   |

| P <sub>D</sub>                  | Power Dissipation                                         | 1         | W    |

Note: 1. For DIP package: Soldering temperature not to exceed 260°C for 10 seconds (total thermal budget not to exceed 150°C for longer than 30 seconds).

CAUTION: Negative undershoots below -0.3V are not allowed on any pin while in the Battery Back-up mode.

**A7/**

# DC AND AC PARAMETERS

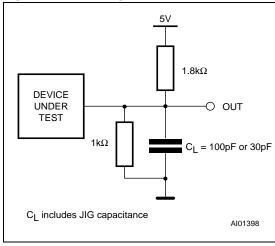

This section summarizes the operating and measurement conditions, as well as the DC and AC characteristics of the device. The parameters in the following DC and AC Characteristic tables are derived from tests performed under the Measure-

ment Conditions listed in the relevant tables. Designers should check that the operating conditions in their projects match the measurement conditions when using the quoted parameters.

**Table 6. Operating and AC Measurement Conditions**

| Parameter                                       | M48Z08      | M48Z18     | Unit |

|-------------------------------------------------|-------------|------------|------|

| Supply Voltage (V <sub>CC</sub> )               | 4.75 to 5.5 | 4.5 to 5.5 | V    |

| Ambient Operating Temperature (T <sub>A</sub> ) | 0 to 70     | 0 to 70    | °C   |

| Load Capacitance (C <sub>L</sub> )              | 100         | 100        | pF   |

| Input Rise and Fall Times                       | ≤ 5         | ≤ 5        | ns   |

| Input Pulse Voltages                            | 0 to 3      | 0 to 3     | V    |

| Input and Output Timing Ref. Voltages           | 1.5         | 1.5        | V    |

Note: Output Hi-Z is defined as the point where data is no longer driven.

Figure 9. AC Testing Load Circuit

Table 7. Capacitance

| Symbol                         | Parameter <sup>(1,2)</sup> | Min | Max | Unit |

|--------------------------------|----------------------------|-----|-----|------|

| C <sub>IN</sub>                | Input Capacitance          |     | 10  | pF   |

| C <sub>IO</sub> <sup>(3)</sup> | Input / Output Capacitance |     | 10  | pF   |

Note: 1. Effective capacitance measured with power supply at 5V; sampled only, not 100% tested.

- 2. At 25°C, f = 1MHz.

- 3. Outputs deselected.

**Table 8. DC Characteristics**

| Symbol                         | Parameter                     | Test Condition <sup>(1)</sup>           | Min  | Max                   | Unit |

|--------------------------------|-------------------------------|-----------------------------------------|------|-----------------------|------|

| ILI                            | Input Leakage Current         | $0V \le V_{IN} \le V_{CC}$              |      | ±1                    | μΑ   |

| I <sub>LO</sub> <sup>(2)</sup> | Output Leakage Current        | 0V ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub> |      | ±1                    | μΑ   |

| Icc                            | Supply Current                | Outputs open                            |      | 80                    | mA   |

| I <sub>CC1</sub>               | Supply Current (Standby) TTL  | E = V <sub>IH</sub>                     |      | 3                     | mA   |

| I <sub>CC2</sub>               | Supply Current (Standby) CMOS | $\overline{E} = V_{CC} - 0.2V$          |      | 3                     | mA   |

| V <sub>IL</sub>                | Input Low Voltage             |                                         | -0.3 | 0.8                   | V    |

| V <sub>IH</sub>                | Input High Voltage            |                                         | 2.2  | V <sub>CC</sub> + 0.3 | V    |

| V <sub>OL</sub>                | Output Low Voltage            | I <sub>OL</sub> = 2.1mA                 |      | 0.4                   | V    |

| VoH                            | Output High Voltage           | I <sub>OH</sub> = -1mA                  | 2.4  |                       | V    |

Note: 1. Valid for Ambient Operating Temperature: T<sub>A</sub> = 0 to 70°C; V<sub>CC</sub> = 4.75 to 5.5V or 4.5 to 5.5V (except where noted). 2. Outputs deselected.

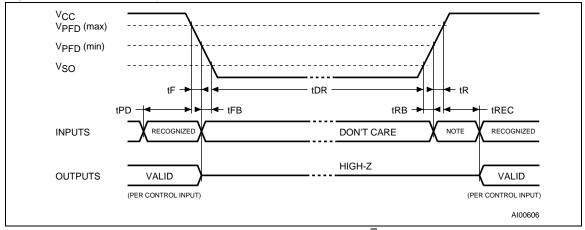

Figure 10. Power Down/Up Mode AC Waveforms

Note: Inputs may or may not be recognized at this time. Caution should be taken to keep  $\overline{E}$  high as  $V_{CC}$  rises past  $V_{PFD}$  (min). Some systems may perform inadvertent WRITE cycles after V<sub>CC</sub> rises above V<sub>PFD</sub> (min) but before normal system operations begin. Even though a power on reset is being applied to the processor, a reset condition may not occur until after the system is running.

Table 9. Power Down/Up AC Characteristics

| Symbol                         | Parameter <sup>(1)</sup>                                                   | Min | Max | Unit |

|--------------------------------|----------------------------------------------------------------------------|-----|-----|------|

| t <sub>PD</sub>                | Ē or ₩ at V <sub>IH</sub> before Power Down                                | 0   |     | μs   |

| t <sub>F</sub> <sup>(2)</sup>  | V <sub>PFD</sub> (max) to V <sub>PFD</sub> (min) V <sub>CC</sub> Fall Time | 300 |     | μs   |

| t <sub>FB</sub> <sup>(3)</sup> | V <sub>PFD</sub> (min) to V <sub>SS</sub> V <sub>CC</sub> Fall Time        | 10  |     | μs   |

| t <sub>R</sub>                 | V <sub>PFD</sub> (min) to V <sub>PFD</sub> (max) V <sub>CC</sub> Rise Time | 0   |     | μs   |

| t <sub>RB</sub>                | Vss to V <sub>PFD</sub> (min) V <sub>CC</sub> Rise Time                    | 1   |     | μs   |

| t <sub>rec</sub>               | Ē or ₩ at V <sub>IH</sub> before Power Up                                  | 2   |     | ms   |

Table 10. Power Down/Up Trip Points DC Characteristics

| Symbol                         | Parameter <sup>(1,2)</sup>                                 | Min | Тур | Max | Unit |       |

|--------------------------------|------------------------------------------------------------|-----|-----|-----|------|-------|

| Voca                           | V <sub>PFD</sub> Power-fail Deselect Voltage M48Z08 M48Z18 |     | 4.5 | 4.6 | 4.75 | V     |

| VPFD                           |                                                            |     | 4.2 | 4.3 | 4.5  | V     |

| V <sub>SO</sub>                | Battery Back-up Switchover Voltage                         |     |     | 3.0 |      | V     |

| t <sub>DR</sub> <sup>(3)</sup> | Expected Data Retention Time                               |     | 11  |     |      | YEARS |

3. At 25°C, V<sub>CC</sub> = 0V.

Note: 1. Valid for Ambient Operating Temperature: T<sub>A</sub> = 0 to 70°C; V<sub>CC</sub> = 4.75 to 5.5V or 4.5 to 5.5V (except where noted).

2. V<sub>PFD</sub> (max) to V<sub>PFD</sub> (min) fall time of less than tF may result in deselection/write protection not occurring until 200µs after V<sub>CC</sub> passes V<sub>PFD</sub> (min).

<sup>3.</sup> V<sub>PFD</sub> (min) to V<sub>SS</sub> fall time of less than t<sub>FB</sub> may cause corruption of RAM data.

Note: 1. All voltages referenced to V<sub>SS</sub>.

2. Valid for Ambient Operating Temperature: T<sub>A</sub> = 0 to 70°C; V<sub>CC</sub> = 4.75 to 5.5V or 4.5 to 5.5V (except where noted).

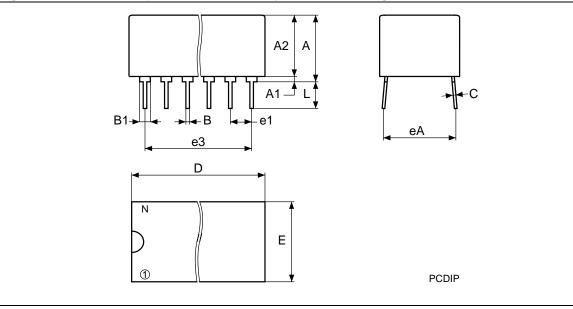

# PACKAGE MECHANICAL INFORMATION

Figure 11. PCDIP28 – 28-pin Plastic DIP, battery CAPHAT, Package Outline

Note: Drawing is not to scale.

Table 11. PCDIP28 – 28-pin Plastic DIP, battery CAPHAT, Package Mechanical Data

| Cumb |     | mm    |       |     | inches |       |

|------|-----|-------|-------|-----|--------|-------|

| Symb | Тур | Min   | Max   | Тур | Min    | Max   |

| А    |     | 8.89  | 9.65  |     | 0.350  | 0.380 |

| A1   |     | 0.38  | 0.76  |     | 0.015  | 0.030 |

| A2   |     | 8.38  | 8.89  |     | 0.330  | 0.350 |

| В    |     | 0.38  | 0.53  |     | 0.015  | 0.021 |

| B1   |     | 1.14  | 1.78  |     | 0.045  | 0.070 |

| С    |     | 0.20  | 0.31  |     | 0.008  | 0.012 |

| D    |     | 39.37 | 39.88 |     | 1.550  | 1.570 |

| E    |     | 17.83 | 18.34 |     | 0.702  | 0.722 |

| e1   |     | 2.29  | 2.79  |     | 0.090  | 0.110 |

| e3   |     | 29.72 | 36.32 |     | 1.170  | 1.430 |

| eA   |     | 15.24 | 16.00 |     | 0.600  | 0.630 |

| L    |     | 3.05  | 3.81  |     | 0.120  | 0.150 |

| N    |     | 28    |       |     | 28     |       |

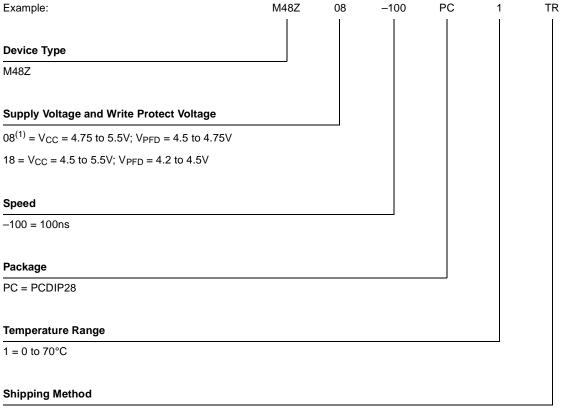

# **PART NUMBERING**

### **Table 12. Ordering Information Scheme**

blank = ECOPACK Package, Tubes

TR = ECOPACK Package, Tape & Reel

Note: 1. The M48Z08/18 part is offered with the PCDIP28 (e.g., CAPHAT™) package only.

For other options, or for more information on any aspect of this device, please contact the ST Sales Office nearest you.