# 5 V, 16 Kbit (2 Kb x 8) ZEROPOWER® SRAM

### **Features**

- Integrated, ultra low power SRAM and powerfail control circuit

- Unlimited WRITE cycles

- READ cycle time equals WRITE cycle time

- Automatic power-fail chip deselect and WRITE protection

- WRITE protect voltages (V<sub>PFD</sub> = Power-fail deselect voltage):

- M48Z02:  $V_{CC}$  = 4.75 to 5.5 V; 4.5 V  $\leq$  V<sub>PFD</sub>  $\leq$  4.75 V

- M48Z12:  $V_{CC} = 4.5 \text{ to } 5.5 \text{ V}$ ;  $4.2 \text{ V} \le V_{PFD} \le 4.5 \text{ V}$

- Self-contained battery in the CAPHAT<sup>™</sup> DIP package

- Pin and function compatible with JEDEC standard 2 K x 8 SRAMs

- RoHS compliant

- Lead-free second level interconnect

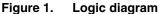

M48Z02, M48Z12 Description

### 1 Description

The M48Z02/12 ZEROPOWER<sup>®</sup> RAM is a 2 K x 8 non-volatile static RAM which is pin and functional compatible with the DS1220.

A special 24-pin, 600 mil DIP CAPHAT™ package houses the M48Z02/12 silicon with a long life lithium button cell to form a highly integrated battery backed-up memory solution.

The M48Z02/12 button cell has sufficient capacity and storage life to maintain data functionality for an accumulated time period of at least 10 years in the absence of power over commercial operating temperature range.

The M48Z02/12 is a non-volatile pin and function equivalent to any JEDEC standard 2 K x 8 SRAM. It also easily fits into many ROM, EPROM, and EEPROM sockets, providing the non-volatility of PROMs without any requirement for special WRITE timing or limitations on the number of WRITEs that can be performed.

Table 1. Signal names

| A0-A10          | Address inputs        |

|-----------------|-----------------------|

| DQ0-DQ7         | Data inputs / outputs |

| Ē               | Chip enable           |

| G               | Output enable         |

| W               | WRITE enable          |

| V <sub>CC</sub> | Supply voltage        |

| V <sub>SS</sub> | Ground                |

Operation modes M48Z02, M48Z12

A0-A10

VALID

tAVQV

tELQV

tGLQV

tGLQX

TGLQX

VALID

AI01330

Figure 4. Read mode AC waveforms

Note: WRITE enable  $(\overline{W})$  = high.

DQ0-DQ7

Table 3. Read mode AC characteristics

|                   | Parameter <sup>(1)</sup>                |    | M48Z02/M48Z12 |     |     |      |     |      |

|-------------------|-----------------------------------------|----|---------------|-----|-----|------|-----|------|

| Symbol            |                                         |    | -70           |     | 50  | -200 |     | Unit |

|                   |                                         |    | Max           | Min | Max | Min  | Max |      |

| t <sub>AVAV</sub> | READ cycle time                         | 70 |               | 150 |     | 200  |     | ns   |

| t <sub>AVQV</sub> | Address valid to output valid           |    | 70            |     | 150 |      | 200 | ns   |

| t <sub>ELQV</sub> | Chip enable low to output valid         |    | 70            |     | 150 |      | 200 | ns   |

| t <sub>GLQV</sub> | Output enable low to output valid       |    | 35            |     | 75  |      | 80  | ns   |

| t <sub>ELQX</sub> | Chip enable low to output transition    | 5  |               | 10  |     | 10   |     | ns   |

| t <sub>GLQX</sub> | Output enable low to output transition  | 5  |               | 5   |     | 5    |     | ns   |

| t <sub>EHQZ</sub> | Chip enable high to output Hi-Z         |    | 25            |     | 35  |      | 40  | ns   |

| t <sub>GHQZ</sub> | Output enable high to output Hi-Z       |    | 25            |     | 35  |      | 40  | ns   |

| t <sub>AXQX</sub> | Address transition to output transition | 10 |               | 5   |     | 5    |     | ns   |

Valid for ambient operating temperature: T<sub>A</sub> = 0 to 70°C or -40 to 85°C; V<sub>CC</sub> = 4.75 to 5.5 V or 4.5 to 5.5 V (except where noted).

### 2.2 Write mode

The M48Z02/12 is in the WRITE mode whenever  $\overline{W}$  and  $\overline{E}$  are active. The start of a WRITE is referenced from the latter occurring falling edge of  $\overline{W}$  or  $\overline{E}$ . A WRITE is terminated by the earlier rising edge of  $\overline{W}$  or  $\overline{E}$ . The addresses must be held valid throughout the cycle.  $\overline{E}$  or  $\overline{W}$  must return high for a minimum of  $t_{EHAX}$  from chip enable or  $t_{WHAX}$  from WRITE enable prior to the initiation of another READ or WRITE cycle. Data-in must be valid  $t_{DVWH}$  prior to the end of WRITE and remain valid for  $t_{WHDX}$  afterward.  $\overline{G}$  should be kept high during WRITE cycles to avoid bus contention; although, if the output bus has been activated by a low on  $\overline{E}$  and  $\overline{G}$ , a low on  $\overline{W}$  will disable the outputs  $t_{WLOZ}$  after  $\overline{W}$  falls.

Operation modes M48Z02, M48Z12

Table 4. Write mode AC characteristics

|                   |                                         |    | ľ   | M48Z02 | 2/M48Z1 | 2   |      |    |

|-------------------|-----------------------------------------|----|-----|--------|---------|-----|------|----|

| Symbol            | Parameter <sup>(1)</sup>                | _  | -70 |        | -150    |     | -200 |    |

|                   |                                         |    | Max | Min    | Max     | Min | Max  |    |

| t <sub>AVAV</sub> | WRITE cycle time                        | 70 |     | 150    |         | 200 |      | ns |

| t <sub>AVWL</sub> | Address valid to WRITE enable low       | 0  |     | 0      |         | 0   |      | ns |

| t <sub>AVEL</sub> | Address valid to chip enable 1 low      | 0  |     | 0      |         | 0   |      | ns |

| t <sub>WLWH</sub> | WRITE enable pulse width                | 50 |     | 90     |         | 120 |      | ns |

| t <sub>ELEH</sub> | Chip enable low to chip enable 1 high   | 55 |     | 90     |         | 120 |      | ns |

| t <sub>WHAX</sub> | WRITE enable high to address transition | 0  |     | 10     |         | 10  |      | ns |

| t <sub>EHAX</sub> | Chip enable high to address transition  | 0  |     | 10     |         | 10  |      | ns |

| t <sub>DVWH</sub> | Input valid to WRITE enable high        | 30 |     | 40     |         | 60  |      | ns |

| t <sub>DVEH</sub> | Input valid to Chip enable high         | 30 |     | 40     |         | 60  |      | ns |

| t <sub>WHDX</sub> | WRITE enable high to input transition   | 5  |     | 5      |         | 5   |      | ns |

| t <sub>EHDX</sub> | Chip enable high to input transition    | 5  |     | 5      |         | 5   |      | ns |

| t <sub>WLQZ</sub> | WRITE enable low to output Hi-Z         |    | 25  |        | 50      |     | 60   | ns |

| t <sub>AVWH</sub> | Address valid to WRITE enable high      | 60 |     | 120    |         | 140 |      | ns |

| t <sub>AVEH</sub> | Address valid to chip enable high       | 60 |     | 120    |         | 140 |      | ns |

| t <sub>WHQX</sub> | WRITE enable high to output transition  | 5  |     | 10     |         | 10  |      | ns |

Valid for ambient operating temperature: T<sub>A</sub> = 0 to 70°C or -40 to 85°C; V<sub>CC</sub> = 4.75 to 5.5 V or 4.5 to 5.5 V (except where noted).

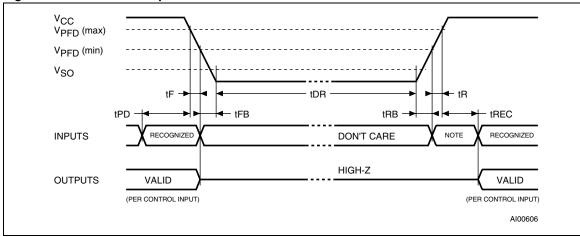

### 2.3 Data retention mode

With valid  $V_{CC}$  applied, the M48Z02/12 operates as a conventional BYTEWIDE<sup>TM</sup> static RAM. Should the supply voltage decay, the RAM will automatically power-fail deselect, write protecting itself when  $V_{CC}$  falls within the  $V_{PFD}$  (max),  $V_{PFD}$  (min) window. All outputs become high impedance, and all inputs are treated as "don't care."

Note:

A power failure during a WRITE cycle may corrupt data at the currently addressed location, but does not jeopardize the rest of the RAM's content. At voltages below  $V_{PFD}$  (min), the user can be assured the memory will be in a write protected state, provided the  $V_{CC}$  fall time is not less than  $t_F$  The M48Z02/12 may respond to transient noise spikes on  $V_{CC}$  that reach into the deselect window during the time the device is sampling  $V_{CC}$ . Therefore, decoupling of the power supply lines is recommended.

The power switching circuit connects external  $V_{CC}$  to the RAM and disconnects the battery when  $V_{CC}$  rises above  $V_{SO}$ . As  $V_{CC}$  rises, the battery voltage is checked. If the voltage is too low, an internal Battery Not OK ( $\overline{BOK}$ ) flag will be set. The  $\overline{BOK}$  flag can be checked after power up. If the  $\overline{BOK}$  flag is set, the first WRITE attempted will be blocked. The flag is automatically cleared after the first WRITE, and normal RAM operation resumes. *Figure 7 on page 11* illustrates how a  $\overline{BOK}$  check routine could be structured.

For more information on a battery storage life refer to the application note AN1012.

577

M48Z02, M48Z12 Maximum ratings

# 3 Maximum ratings

Stressing the device above the rating listed in the absolute maximum ratings table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

Table 5. Absolute maximum ratings

| Symbol                          | Parameter                                                 | Value     | Unit |   |

|---------------------------------|-----------------------------------------------------------|-----------|------|---|

| $T_A$                           | Ambient operating temperature                             | 0 to 70   | °C   |   |

| T <sub>STG</sub>                | Storage temperature (V <sub>CC</sub> off, oscillator off) | -40 to 85 | °C   |   |

| T <sub>SLD</sub> <sup>(1)</sup> | Lead solder temperature for 10 seconds                    | 260       | °C   |   |

| V <sub>IO</sub>                 | Input or output voltages                                  | -0.3 to 7 | V    |   |

| V <sub>CC</sub>                 | Supply voltage                                            | -0.3 to 7 | V    |   |

| I <sub>O</sub>                  | Output current                                            | 20        | mA   |   |

| P <sub>D</sub>                  | Power dissipation                                         |           | 1    | W |

Soldering temperature not to exceed 260°C for 10 seconds (total thermal budget not to exceed 150°C for longer than 30 seconds).

#### Caution:

Negative undershoots below -0.3 V are not allowed on any pin while in the battery backup mode.

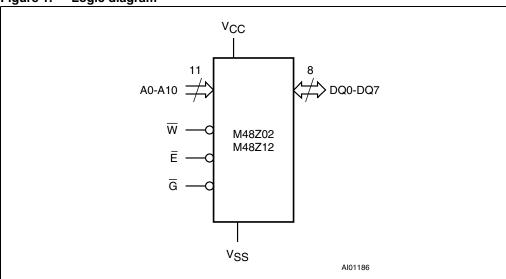

## 4 DC and AC parameters

This section summarizes the operating and measurement conditions, as well as the DC and AC characteristics of the device. The parameters in the following DC and AC characteristic tables are derived from tests performed under the measurement conditions listed in *Table 6: Operating and AC measurement conditions*. Designers should check that the operating conditions in their projects match the measurement conditions when using the quoted parameters.

Table 6. Operating and AC measurement conditions

| Parameter                                       |         | M48Z02      | M48Z12     | Unit |

|-------------------------------------------------|---------|-------------|------------|------|

| Supply voltage (V <sub>CC</sub> )               |         | 4.75 to 5.5 | 4.5 to 5.5 | V    |

| Ambient operating temperature (T <sub>A</sub> ) | Grade 1 | 0 to 70     | 0 to 70    | °C   |

| Load capacitance (C <sub>L</sub> )              |         | 100         | 100        | pF   |

| Input rise and fall times                       |         | ≤ 5         | ≤ 5        | ns   |

| Input pulse voltages                            |         | 0 to 3      | 0 to 3     | V    |

| Input and output timing ref. voltages           |         | 1.5         | 1.5        | V    |

Note: Output Hi-Z is defined as the point where data is no longer driven.

Figure 9. AC testing load circuit

Table 7. Capacitance

| Symbol              | Parameter <sup>(1)(2)</sup> | Min | Max | Unit |

|---------------------|-----------------------------|-----|-----|------|

| C <sub>IN</sub>     | Input capacitance           |     | 10  | pF   |

| C <sub>IO</sub> (3) | Input / output capacitance  |     | 10  | pF   |

- 1. Effective capacitance measured with power supply at 5 V. Sampled only, not 100% tested.

- 2. At 25°C, f = 1 MHz.

- Outputs deselected.

477

Table 8. DC characteristics

| Symbol                         | Parameter                     | Test condition <sup>(1)</sup>  | Min  | Max                   | Unit |

|--------------------------------|-------------------------------|--------------------------------|------|-----------------------|------|

| I <sub>LI</sub>                | Input leakage current         | $0V \le V_{IN} \le V_{CC}$     |      | ±1                    | μΑ   |

| I <sub>LO</sub> <sup>(2)</sup> | Output leakage current        | $0V \le V_{OUT} \le V_{CC}$    |      | ±1                    | μΑ   |

| I <sub>CC</sub>                | Supply current                | Outputs open                   |      | 80                    | mA   |

| I <sub>CC1</sub>               | Supply current (standby) TTL  | E = V <sub>IH</sub>            |      | 3                     | mA   |

| I <sub>CC2</sub>               | Supply current (standby) CMOS | $\overline{E} = V_{CC} - 0.2V$ |      | 3                     | mA   |

| V <sub>IL</sub>                | Input low voltage             |                                | -0.3 | 0.8                   | V    |

| V <sub>IH</sub>                | Input high voltage            |                                | 2.2  | V <sub>CC</sub> + 0.3 | V    |

| V <sub>OL</sub>                | Output low voltage            | I <sub>OL</sub> = 2.1mA        |      | 0.4                   | V    |

| V <sub>OH</sub>                | Output high voltage           | I <sub>OH</sub> = -1mA         | 2.4  |                       | V    |

- 1. Valid for ambient operating temperature:  $T_A = 0$  to  $70^{\circ}C$ ;  $V_{CC} = 4.75$  to 5.5 V or 4.5 to 5.5 V (except where noted).

- 2. Outputs deselected.

Figure 10. Power down/up mode AC waveforms

Note:

Inputs may or may not be recognized at this time. Caution should be taken to keep  $\overline{E}$  high as  $V_{CC}$  rises past  $V_{PFD}$  (min). Some systems may perform inadvertent WRITE cycles after  $V_{CC}$  rises above  $V_{PFD}$  (min) but before normal system operations begin. Even though a power on reset is being applied to the processor, a reset condition may not occur until after the system is running.

Table 9. Power down/up AC characteristics

| Symbol                         | Parameter <sup>(1)</sup>                                                   | Min | Max | Unit |

|--------------------------------|----------------------------------------------------------------------------|-----|-----|------|

| t <sub>PD</sub>                | E or W at V <sub>IH</sub> before power down                                | 0   |     | μs   |

| t <sub>F</sub> <sup>(2)</sup>  | V <sub>PFD</sub> (max) to V <sub>PFD</sub> (min) V <sub>CC</sub> fall time | 300 |     | μs   |

| t <sub>FB</sub> <sup>(3)</sup> | V <sub>PFD</sub> (min) to V <sub>SS</sub> V <sub>CC</sub> fall time        | 10  |     | μs   |

| t <sub>R</sub>                 | V <sub>PFD</sub> (min) to V <sub>PFD</sub> (max) V <sub>CC</sub> rise time | 0   |     | μs   |

| t <sub>RB</sub>                | V <sub>SS</sub> to V <sub>PFD</sub> (min) V <sub>CC</sub> rise time        | 1   |     | μs   |

| t <sub>REC</sub>               | Ē or ₩ at V <sub>IH</sub> after power up                                   | 2   |     | ms   |

<sup>1.</sup> Valid for ambient operating temperature:  $T_A = 0$  to  $70^{\circ}C$ ;  $V_{CC} = 4.75$  to 5.5 V or 4.5 to 5.5 V (except where noted).

Table 10. Power down/up trip points DC characteristics

| Symbol              | Parameter <sup>(1)(2)</sup>       |        | Min | Тур | Max  | Unit  |

|---------------------|-----------------------------------|--------|-----|-----|------|-------|

| V                   | Power-fail deselect voltage       | M48Z02 | 4.5 | 4.6 | 4.75 | V     |

| V <sub>PFD</sub>    | M48Z12                            |        | 4.2 | 4.3 | 4.5  | V     |

| V <sub>SO</sub>     | Battery backup switchover voltage |        |     | 3.0 |      | V     |

| t <sub>DR</sub> (3) | Expected data retention time      |        | 10  |     |      | YEARS |

<sup>1.</sup> All voltages referenced to  $V_{SS}$ .

<sup>2.</sup>  $V_{PFD}$  (max) to  $V_{PFD}$  (min) fall time of less than tF may result in deselection/write protection not occurring until 200  $\mu$ s after  $V_{CC}$  passes  $V_{PFD}$  (min).

<sup>3.</sup>  $V_{PFD}$  (min) to  $V_{SS}$  fall time of less than  $t_{FB}$  may cause corruption of RAM data.

<sup>2.</sup> Valid for ambient operating temperature:  $T_A = 0$  to  $70^{\circ}C$ ;  $V_{CC} = 4.75$  to 5.5 V or 4.5 to 5.5 V (except where noted).

<sup>3.</sup> At  $25^{\circ}$ C,  $V_{CC} = 0$  V.

### 5 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK<sup>®</sup> packages. These packages have a lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

Figure 11. PCDIP24 – 24-pin plastic DIP, battery CAPHAT™, package outline

Note: Drawing is not to scale.

Table 11. PCDIP24 – 24-pin plastic DIP, battery CAPHAT™, package mechanical data

| Cromb |     | mm    |       |     | inches |       |

|-------|-----|-------|-------|-----|--------|-------|

| Symb  | Тур | Min   | Max   | Тур | Min    | Max   |

| Α     |     | 8.89  | 9.65  |     | 0.350  | 0.380 |

| A1    |     | 0.38  | 0.76  |     | 0.015  | 0.030 |

| A2    |     | 8.38  | 8.89  |     | 0.330  | 0.350 |

| В     |     | 0.38  | 0.53  |     | 0.015  | 0.021 |

| B1    |     | 1.14  | 1.78  |     | 0.045  | 0.070 |

| С     |     | 0.20  | 0.31  |     | 0.008  | 0.012 |

| D     |     | 34.29 | 34.80 |     | 1.350  | 1.370 |

| Е     |     | 17.83 | 18.34 |     | 0.702  | 0.722 |

| e1    |     | 2.29  | 2.79  |     | 0.090  | 0.110 |

| e3    |     | 25.15 | 30.73 |     | 0.990  | 1.210 |

| eA    |     | 15.24 | 16.00 |     | 0.600  | 0.630 |

| L     |     | 3.05  | 3.81  |     | 0.120  | 0.150 |

| N     |     | 24    |       |     | 24     |       |

57

Part numbering M48Z02, M48Z12

# 6 Part numbering

blank = ECOPACK® package, tubes

For a list of available options (e.g., speed, package) or for further information on any aspect of this device, please contact the ST sales office nearest you.