#### **ON Semiconductor®**

# 256-Kb I<sup>2</sup>C CMOS Serial EEPROM

### **FEATURES**

- Supports Standard and Fast I<sup>2</sup>C Protocol

- 1.8V to 5.5V Supply Voltage Range

- 64-Byte Page Write Buffer

- Hardware Write Protection for entire memory

- Schmitt Triggers and Noise Suppression Filters on I<sup>2</sup>C Bus Inputs (SCL and SDA).

- Low power CMOS technology

- 1,000,000 program/erase cycles

- 100 year data retention

- Industrial temperature range

- RoHS-compliant 8-pin PDIP, SOIC, TSSOP and 8-pad TDFN packages

For Ordering Information details, see page 15.

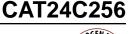

#### **PIN CONFIGURATION**

For the location of Pin 1, please consult the corresponding package drawing.

### **PIN FUNCTIONS**

| A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> | Device Address |

|--------------------------------------------------|----------------|

| SDA                                              | Serial Data    |

| SCL                                              | Serial Clock   |

| WP                                               | Write Protect  |

| V <sub>CC</sub>                                  | Power Supply   |

| V <sub>SS</sub>                                  | Ground         |

## **DEVICE DESCRIPTION**

The CAT24C256 is a 256-Kb Serial CMOS EEPROM, internally organized as 32,768 words of 8 bits each.

It features a 64-byte page write buffer and supports both the Standard (100kHz) as well as Fast (400kHz) I<sup>2</sup>C protocol.

Write operations can be inhibited by taking the WP pin High (this protects the entire memory).

External address pins make it possible to address up to eight CAT24C256 devices on the same bus.

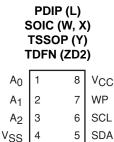

### FUNCTIONAL SYMBOL

\* Catalyst carries the I<sup>2</sup>C protocol under a license from the Philips Corporation.

© 2008 SCILLC. All rights reserved

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Storage Temperature                                      | -65°C to +150°C  |

|----------------------------------------------------------|------------------|

| Voltage on Any Pin with Respect to Ground <sup>(2)</sup> | -0.5 V to +6.5 V |

#### **RELIABILITY CHARACTERISTICS**<sup>(3)</sup>

| Symbol                          | Parameter      | Min       | Units                 |

|---------------------------------|----------------|-----------|-----------------------|

| N <sub>END</sub> <sup>(4)</sup> | Endurance      | 1,000,000 | Program/ Erase Cycles |

| T <sub>DR</sub>                 | Data Retention | 100       | Years                 |

#### **D.C. OPERATING CHARACTERISTICS**

$V_{CC}$  = 1.8 V to 5.5 V,  $T_A$  = -40°C to 85°C, unless otherwise specified.

| Symbol           | Parameter          | Test Conditions                                            | Min                   | Max                   | Units |

|------------------|--------------------|------------------------------------------------------------|-----------------------|-----------------------|-------|

| I <sub>CC</sub>  | Supply Current     | Read or Write at 400kHz                                    |                       | 1                     | mA    |

| I <sub>SB</sub>  | Standby Current    | All I/O Pins at GND or $V_{\text{CC}}$                     |                       | 1                     | μA    |

| IL.              | I/O Pin Leakage    | Pin at GND or V <sub>CC</sub>                              |                       | 1                     | μA    |

| VIL              | Input Low Voltage  |                                                            | -0.5                  | V <sub>CC</sub> x 0.3 | V     |

| V <sub>IH</sub>  | Input High Voltage |                                                            | V <sub>CC</sub> x 0.7 | V <sub>CC</sub> + 0.5 | V     |

| V <sub>OL1</sub> | Output Low Voltage | $V_{CC} \ge 2.5 \text{ V}, \text{ I}_{OL} = 3.0 \text{mA}$ |                       | 0.4                   | V     |

| V <sub>OL2</sub> | Output Low Voltage | V <sub>CC</sub> < 2.5 V, I <sub>OL</sub> = 1.0mA           |                       | 0.2                   | V     |

#### **PIN IMPEDANCE CHARACTERISTICS**

$V_{CC}$  = 1.8 V to 5.5 V,  $T_A$  = -40°C to 85°C, unless otherwise specified.

| Symbol                         | Parameter                        | Conditions                                                | Min | Max | Units |

|--------------------------------|----------------------------------|-----------------------------------------------------------|-----|-----|-------|

| C <sub>IN</sub> <sup>(3)</sup> | SDA I/O Pin Capacitance          | $V_{IN} = 0V$                                             |     | 8   | pF    |

| C <sub>IN</sub> <sup>(3)</sup> | Input Capacitance (other pins)   | $V_{IN} = 0V$                                             |     | 6   | pF    |

| I <sub>WP</sub> <sup>(5)</sup> | WP Input Current                 | V <sub>IN</sub> < V <sub>IH,</sub> V <sub>CC</sub> = 5.5V |     | 200 |       |

|                                | (CAT24C256 Rev. C - New Product) | $V_{IN} < V_{IH}, V_{CC} = 3.3V$                          |     | 150 | μA    |

|                                |                                  | $V_{\rm IN} < V_{\rm IH,} V_{\rm CC} = 1.8 V$             |     | 100 |       |

|                                |                                  | $V_{\rm IN} > V_{\rm IH}$                                 |     | 1   |       |

Notes:

- (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

- (2) The DC input voltage on any pin should not be lower than -0.5V or higher than V<sub>CC</sub> + 0.5V. During transitions, the voltage on any pin may undershoot to no less than -1.5V or overshoot to no more than V<sub>CC</sub> + 1.5V, for periods of less than 20 ns.

- (3) These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC-Q100 and JEDEC test methods.

- (4) Page Mode,  $V_{CC} = 5V$ ,  $25^{\circ}C$

- (5) When not driven, the WP pin is pulled down to GND internally. For improved noise immunity, the internal pull-down is relatively strong; therefore the external driver must be able to supply the pull-down current when attempting to drive the input HIGH. To conserve power, as the input level exceeds the trip point of the CMOS input buffer (~ 0.5 x V<sub>CC</sub>), the strong pull-down reverts to a weak current source. The variable WP input impedance is available only for Die Rev. C, New Product.

Doc. No. MD-1104, Rev. G

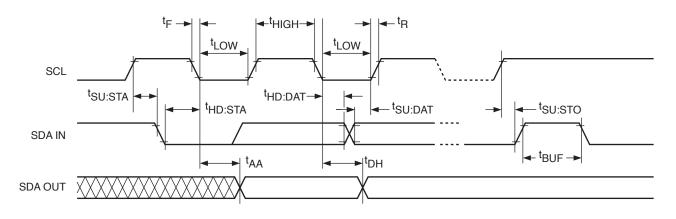

### A.C. CHARACTERISTICS<sup>(1)</sup>

$V_{CC}$  = 1.8 V to 5.5 V,  $T_A$  = -40°C to 85°C, unless otherwise specified.

|                                   |                                            | Standard |      | Fast |     |       |

|-----------------------------------|--------------------------------------------|----------|------|------|-----|-------|

| Symbol                            | Parameter                                  | Min      | Max  | Min  | Max | Units |

| $F_{SCL}$                         | Clock Frequency                            |          | 100  |      | 400 | kHz   |

| t <sub>HD:STA</sub>               | START Condition Hold Time                  | 4        |      | 0.6  |     | μs    |

| t <sub>LOW</sub>                  | Low Period of SCL Clock                    | 4.7      |      | 1.3  |     | μs    |

| t <sub>HIGH</sub>                 | High Period of SCL Clock                   | 4        |      | 0.6  |     | μs    |

| t <sub>SU:STA</sub>               | START Condition Setup Time                 | 4.7      |      | 0.6  |     | μs    |

| t <sub>HD:DAT</sub>               | Data In Hold Time                          | 0        |      | 0    |     | μs    |

| t <sub>SU:DAT</sub>               | Data In Setup Time                         | 250      |      | 100  |     | ns    |

| t <sub>R</sub> <sup>(2)</sup>     | SDA and SCL Rise Time                      |          | 1000 |      | 300 | ns    |

| t <sub>F</sub> <sup>(2)</sup>     | SDA and SCL Fall Time                      |          | 300  |      | 300 | ns    |

| t <sub>SU:STO</sub>               | STOP Condition Setup Time                  | 4        |      | 0.6  |     | μs    |

| t <sub>BUF</sub>                  | Bus Free Time Between STOP and START       | 4.7      |      | 1.3  |     | μs    |

| t <sub>AA</sub>                   | SCL Low to Data Out Valid                  |          | 3.5  |      | 0.9 | μs    |

| t <sub>DH</sub>                   | Data Out Hold Time                         | 100      |      | 100  |     | ns    |

| T <sub>i</sub> <sup>(2)</sup>     | Noise Pulse Filtered at SCL and SDA Inputs |          | 100  |      | 100 | ns    |

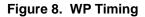

| t <sub>SU:WP</sub>                | WP Setup Time                              | 0        |      | 0    |     | μs    |

| t <sub>HD:WP</sub>                | WP Hold Time                               | 2.5      |      | 2.5  |     | μs    |

| t <sub>WR</sub>                   | Write Cycle Time                           |          | 5    |      | 5   | ms    |

| t <sub>PU</sub> <sup>(2, 3)</sup> | Power-up to Ready Mode                     |          | 1    |      | 1   | ms    |

Notes:

(1) Test conditions according to "A.C. Test Conditions" table.

(2) Tested initially and after a design or process change that affects this parameter.

(3)  $t_{PU}$  is the delay between the time  $V_{CC}$  is stable and the device is ready to accept commands.

### A.C. TEST CONDITIONS

| Input Levels              | $0.2 \times V_{CC}$ to $0.8 \times V_{CC}$                                                              |

|---------------------------|---------------------------------------------------------------------------------------------------------|

| Input Rise and Fall Times | ≤ 50ns                                                                                                  |

| Input Reference Levels    | $0.3 \times V_{CC}, 0.7 \times V_{CC}$                                                                  |

| Output Reference Levels   | $0.5 \times V_{CC}$                                                                                     |

| Output Load               | Current Source: $I_{OL}$ = 3mA ( $V_{CC} \ge 2.5V$ ); $I_{OL}$ = 1 mA ( $V_{CC}$ < 2.5V); $C_L$ = 100pF |

### **POWER-ON RESET (POR)**

The CAT24C256 Die Rev. C incorporates Power-On Reset (POR) circuitry which protects the internal logic against powering up in the wrong state.

The device will power up into Standby mode after  $V_{CC}$  exceeds the POR trigger level and will power down into Reset mode when  $V_{CC}$  drops below the POR trigger level. This bi-directional POR feature protects the device against 'brown-out' failure following a temporary loss of power.

### **PIN DESCRIPTION**

**SCL:** The Serial Clock input pin accepts the Serial Clock generated by the Master.

**SDA:** The Serial Data I/O pin receives input data and transmits data stored in EEPROM. In transmit mode, this pin is open drain. Data is acquired on the positive edge, and is delivered on the negative edge of SCL.

$A_0$ ,  $A_1$  and  $A_2$ : The Address pins accept the device address. These pins have on-chip pull-down resistors.

**WP:** The Write Protect input pin inhibits all write operations, when pulled HIGH. This pin has an on-chip pull-down resistor.

### FUNCTIONAL DESCRIPTION

The CAT24C256 supports the Inter-Integrated Circuit (I<sup>2</sup>C) Bus data transmission protocol, which defines a device that sends data to the bus as a transmitter and a device receiving data as a receiver. Data flow is controlled by a Master device, which generates the serial clock and all START and STOP conditions. The CAT24C256 acts as a Slave device. Master and Slave alternate as either transmitter or receiver. Up to 8 devices may be connected to the bus as determined by the device address inputs  $A_0$ ,  $A_1$ , and  $A_2$ .

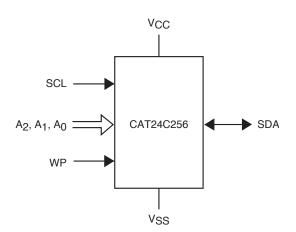

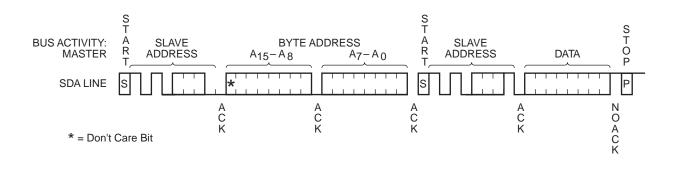

# I<sup>2</sup>C BUS PROTOCOL

The l<sup>2</sup>C bus consists of two 'wires', SCL and SDA. The two wires are connected to the  $V_{CC}$  supply via pull-up resistors. Master and Slave devices connect to the 2-wire bus via their respective SCL and SDA pins. The transmitting device pulls down the SDA line to 'transmit' a '0' and releases it to 'transmit' a '1'.

Data transfer may be initiated only when the bus is not busy (see A.C. Characteristics).

During data transfer, the SDA line must remain stable while the SCL line is HIGH. An SDA transition while SCL is HIGH will be interpreted as a START or STOP condition (Figure 1).

#### START

The START condition precedes all commands. It consists of a HIGH to LOW transition on SDA while SCL is HIGH. The START acts as a 'wake-up' call to all receivers. Absent a START, a Slave will not respond to commands.

#### STOP

The STOP condition completes all commands. It consists of a LOW to HIGH transition on SDA while SCL is HIGH. The STOP starts the internal Write cycle (when following a Write command) or sends the Slave into standby mode (when following a Read command).

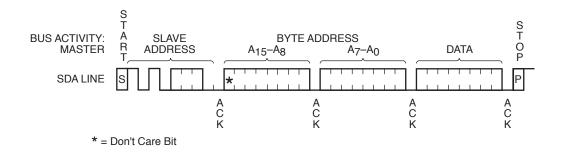

#### **Device Addressing**

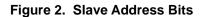

The Master initiates data transfer by creating a START condition on the bus. The Master then broadcasts an 8-bit serial Slave address. The first 4 bits of the Slave address are set to 1010, for normal Read/Write operations (Figure 2). The next 3 bits,  $A_2$ ,  $A_1$  and  $A_0$ , select one of 8 possible Slave devices. The last bit, R/W, specifies whether a Read (1) or Write (0) operation is to be performed.

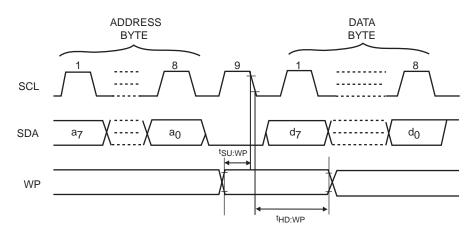

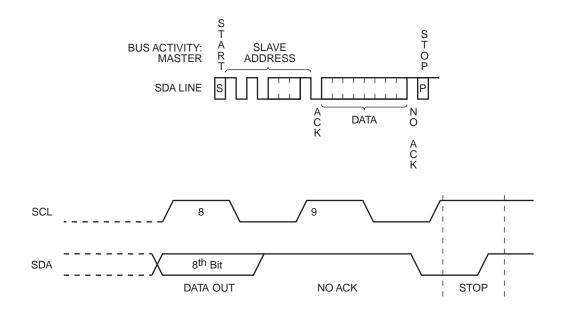

#### Acknowledge

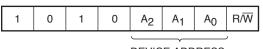

After processing the Slave address, the Slave responds with an acknowledge (ACK) by pulling down the SDA line during the 9<sup>th</sup> clock cycle (Figure 3). The Slave will also acknowledge the byte address and every data byte presented in Write mode. In Read mode the Slave shifts out a data byte, and then releases the SDA line during the 9<sup>th</sup> clock cycle. If the Master acknowledges the data, then the Slave continues transmitting. The Master terminates the session by not acknowledging the last data byte (NoACK) and by sending a STOP to the Slave. Bus timing is illustrated in Figure 4.

#### Figure 1. Start/Stop Timing

DEVICE ADDRESS

Figure 3. Acknowledge Timing

© 2008 SCILLC. All rights reserved

### WRITE OPERATIONS

#### **Byte Write**

In Byte Write mode the Master sends a START, followed by Slave address, two byte address and data to be written (Figure 5). The Slave acknowledges all 4 bytes, and the Master then follows up with a STOP, which in turn starts the internal Write operation (Figure 6). During internal Write, the Slave will not acknowledge any Read or Write request from the Master.

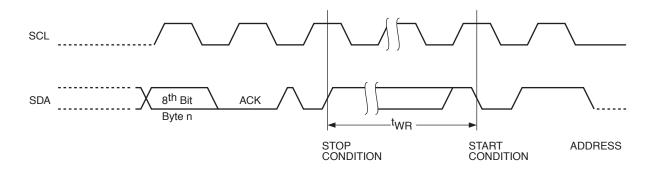

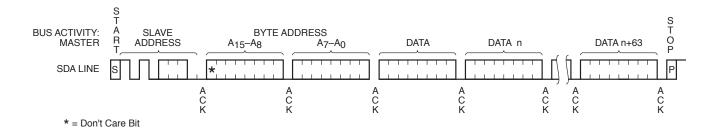

#### **Page Write**

The CAT24C256 contains 32,768 bytes of data, arranged in 512 pages of 64 bytes each. A two byte address word, following the Slave address, points to the first byte to be written. The most significant bit of the address word is 'don't care', the next 9 bits identify the page and the last 6 bits identify the byte within the page. Up to 64 bytes can be written in one Write cycle (Figure 7).

The internal byte address counter is automatically incremented after each data byte is loaded. If the Master transmits more than 64 data bytes, then earlier bytes will be overwritten by later bytes in a 'wrap-around' fashion (within the selected page). The internal Write cycle starts immediately following the STOP.

#### **Acknowledge Polling**

Acknowledge polling can be used to determine if the CAT24C256 is busy writing or is ready to accept commands. Polling is implemented by interrogating the device with a 'Selective Read' command (see READ OPERATIONS).

The CAT24C256 will not acknowledge the Slave address, as long as internal Write is in progress.

#### **Hardware Write Protection**

With the WP pin held HIGH, the entire memory is protected against Write operations. If the WP pin is left floating or is grounded, it has no impact on the operation of the CAT24C256. The state of the WP pin is strobed on the last falling edge of SCL immediately preceding the first data byte (Figure 8). If the WP pin is HIGH during the strobe interval, the CAT24C256 will not acknowledge the data byte and the Write request will be rejected.

#### **Delivery State**

The CAT24C256 is shipped erased, i.e., all bytes are FFh.

#### Figure 5. Byte Write Timing

Figure 6. Write Cycle Timing

### **READ OPERATIONS**

#### Immediate Address Read

In standby mode, the CAT24C256 internal address counter points to the data byte immediately following the last byte accessed by a previous operation. If that 'previous' byte was the last byte in memory, then the address counter will point to the 1<sup>st</sup> memory byte, etc.

When, following a START, the CAT24C256 is presented with a Slave address containing a '1' in the R/W bit position (Figure 9), it will acknowledge (ACK) in the 9<sup>th</sup> clock cycle, and will then transmit data being pointed at by the internal address counter. The Master can stop further transmission by issuing a NoACK, followed by a STOP condition.

#### **Selective Read**

The Read operation can also be started at an address different from the one stored in the internal address counter. The address counter can be initialized by performing a 'dummy' Write operation (Figure 10). Here the START is followed by the Slave address (with the R/W bit set to '0') and the desired two byte address. Instead of following up with data, the Master then issues a 2<sup>nd</sup> START, followed by the 'Immediate Address Read' sequence, as described earlier.

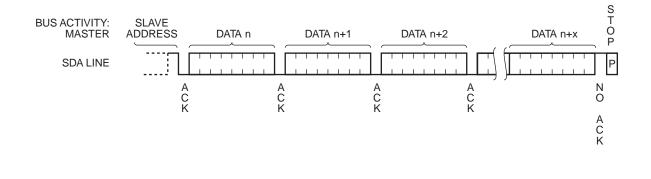

#### Sequential Read

If the Master acknowledges the 1<sup>st</sup> data byte transmitted by the CAT24C256, then the device will continue transmitting as long as each data byte is acknowledged by the Master (Figure 11). If the end of memory is reached during sequential Read, then the address counter will 'wrap-around' to the beginning of memory, etc. Sequential Read works with either 'Immediate Address Read' or 'Selective Read', the only difference being the starting byte address.

Figure 9. Immediate Address Read Timing

Figure 10. Selective Read Timing

Figure 11. Sequential Read Timing

© 2008 SCILLC. All rights reserved Characteristics subject to change without notice

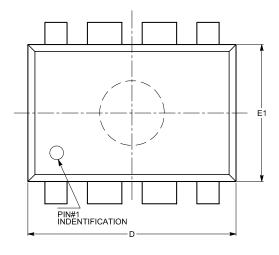

### PACKAGE OUTLINE DRAWINGS

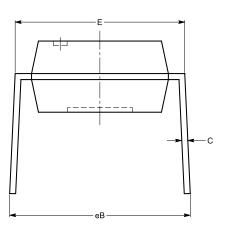

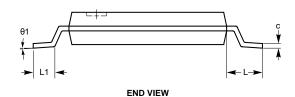

PDIP 8-Lead 300 mils (L)

#### PDIP 8-Lead 300mils (L)

| A2 | 2.92 | 3.30     | 4.95  |

|----|------|----------|-------|

| b  | 0.36 | 0.46     | 0.56  |

| b2 | 1.14 | 1.52     | 1.78  |

| С  | 0.20 | 0.25     | 0.36  |

| D  | 9.02 | 9.27     | 10.16 |

| Е  | 7.62 | 7.87     | 8.25  |

| е  |      | 2.54 BSC |       |

| E1 | 6.10 | 6.35     | 7.11  |

| eB | 7.87 |          | 10.92 |

| L  | 2.92 | 3.30     | 3.80  |

NOM

MAX

5.33

SYMBOL

А

A1

MIN

0.38

TOP VIEW

SIDE VIEW

END VIEW

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf

Notes:

(1) All dimensions are in millimeters.

(2) Complies with JEDEC MS-001.

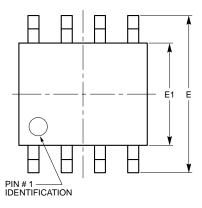

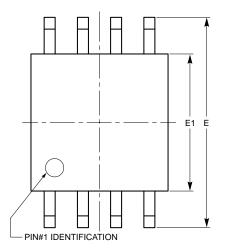

#### SOIC 8-Lead 150 mils (W)

MAX SYMBOL MIN NOM А 1.35 1.75 A1 0.10 0.25 0.51 b 0.33 0.19 0.25 с D 5.00 4.80 Е 5.80 6.20 E1 3.80 4.00 1.27 BSC е 0.25 0.50 h L 0.40 1.27 θ 0° 8º

SIDE VIEW

TOP VIEW

END VIEW

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf

#### Notes:

- (1) Complies with JEDEC specification MS-012 dimensions.

- (2) All linear dimensions are in millimeters.

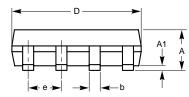

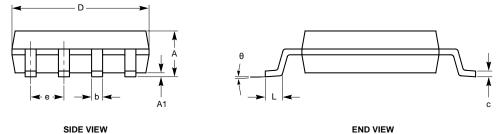

#### SOIC 8-Lead 208 mils (X)

TOP VIEW

| SYMBOL | MIN  | NOM      | МАХ  |

|--------|------|----------|------|

| A      |      |          | 2.03 |

| A1     | 0.05 |          | 0.25 |

| b      | 0.36 |          | 0.48 |

| с      | 0.19 |          | 0.25 |

| D      | 5.13 |          | 5.33 |

| E      | 7.75 |          | 8.26 |

| E1     | 5.13 |          | 5.38 |

| е      |      | 1.27 BSC |      |

| L      | 0.51 |          | 0.76 |

| θ      | 0°   |          | 8º   |

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf

Notes:

(1) Complies with EIAJ specification.

(2) All linear dimensions are in millimeters.

Doc. No. MD-1104, Rev. G

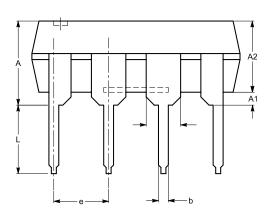

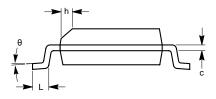

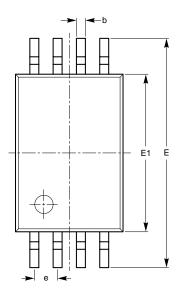

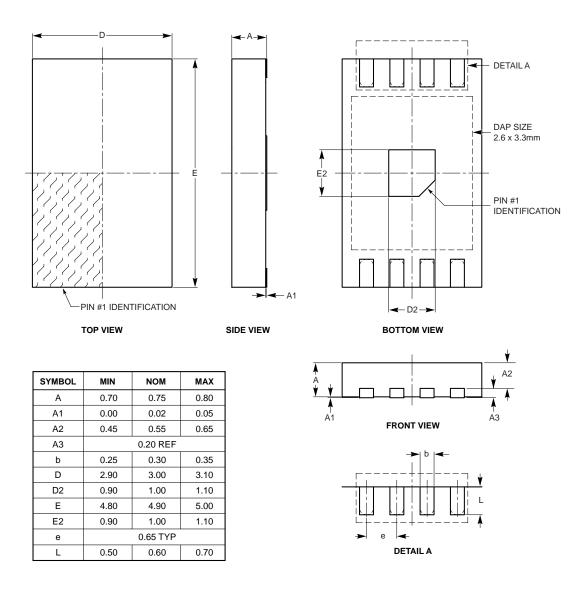

#### TSSOP 8-Lead 4.4mm (Y)

| SYMBOL | MIN      | NOM      | MAX  |

|--------|----------|----------|------|

| A      |          |          | 1.20 |

| A1     | 0.05     |          | 0.15 |

| A2     | 0.80     | 0.90     | 1.05 |

| b      | 0.19     |          | 0.30 |

| с      | 0.09     |          | 0.20 |

| D      | 2.90     | 3.00     | 3.10 |

| E      | 6.30     | 6.40     | 6.50 |

| E1     | 4.30     | 4.40     | 4.50 |

| е      |          | 0.65 BSC |      |

| L      | 1.00 REF |          |      |

| L1     | 0.50     | 0.60     | 0.75 |

| θ1     | 0°       |          | 8°   |

TOP VIEW

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf

#### Notes:

- All dimensions are in milimiters. Angles in degrees

Complies with JEDEC MO-153.

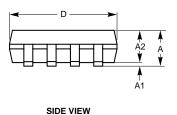

#### TDFN 8-Pad 3 x 4.9mm (ZD2)

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf

Notes:

(1) All dimensions are in milimiters.

(2) Complies with JEDEC MO-229.

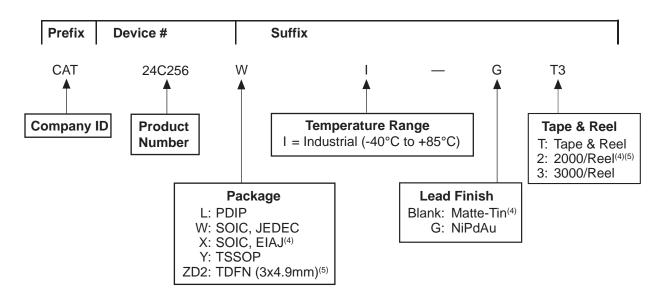

#### **ORDERING INFORMATION**

#### Notes:

- (1) All packages are RoHS-compliant (Lead-free, Halogen-free).

- (2) The standard lead finish is NiPdAu.

- (3) The device used in the above example is a CAT24C256WI-GT3 (SOIC-JEDEC, Industrial Temperature, NiPdAu, Tape & Reel).

- (4) For SOIC, EIAJ (X) package the standard lead finish is Matte-Tin. This package is available in 2000 pcs/reel, i.e. CAT24C256XI-T2.

- (5) The TDFN 3x4.9mm (ZD2) package is available in 2000 pcs/reel, i.e., CAT24C256ZD2I-GT2.

- (6) For additional package and temperature options, please contact your nearest ON Semiconductor Sales office.

© 2008 SCILLC. All rights reserved Characteristics subject to change without notice

### **REVISION HISTORY**

| Date      | Revision | Comments                                                     |

|-----------|----------|--------------------------------------------------------------|

| 10/07/05  | А        | Initial Issue                                                |

| 44/40/05  | D        | Update Ordering Information                                  |

| 11/16/05  | В        | Add Tape and Reel Specifications                             |

| 02/02/06  | С        | Update Ordering Information                                  |

|           |          | Update Package Outlines. Add SOIC, EIAJ Package Outlines     |

|           |          | Update A.C. Characteristics. Add A.C. Test Conditions        |

| 01/12/07  | D        | Update Figures 1, 3 and 4                                    |

|           |          | Delete Package Marking. Deleted Tape and Reel                |

|           |          | Update Ordering Information                                  |

|           |          | Update Features/Packages                                     |

|           |          | Update Pin Configuration                                     |

|           |          | Update Pin Impedance Characteristics                         |

|           |          | Add Power-On Reset (POR) text                                |

| 05/08/07  | Е        | Update Hardware Write Protection                             |

|           |          | Add WP Timing (Figure 8) (Renumbered Figures 9 & 11)         |

|           |          | Add 8-Lead TSSOP Package Outline                             |

|           |          | Add 8-pad TDFN 3x4.9mm Package Outline                       |

|           |          | Updated Ordering Information                                 |

| 08/15/07  | F        | Updated PDIP, SOIC, TSSOP, and TDFN Package Outline Drawings |

| 10 Oct 00 | 0        | Updated SOIC 8L, 208mil, Package Outline Drawing             |

| 12-Oct-08 | G        | Change logo and fine print to ON Semiconductor               |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters, including "Typicals" must be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# PUBLICATION ORDERING INFORMATION LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center: Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative