# **Quad EIA-485 Line Drivers** with Three-State Outputs

The ON Semiconductor MC75172B/174B Quad Line drivers are differential high speed drivers designed to comply with the EIA–485 Standard. Features include three–state outputs, thermal shutdown, and output current limiting in both directions. These devices also comply with EIA–422–A, and CCITT Recommendations V.11 and X.27.

The MC75172B/174B are optimized for balanced multipoint bus transmission at rates in excess of 10 MBPS. The outputs feature wide common mode voltage range, making them suitable for party line applications in noisy environments. The current limit and thermal shutdown features protect the devices from line fault conditions. These devices offer optimum performance when used with the MC75173 and MC75175 line receivers.

Both devices are available in 16-pin plastic PDIP and 20-pin wide body surface mount packages.

#### **Features**

- Meets EIA-485 Standard for Party Line Operation

- Meets EIA-422-A and CCITT Recommendations V.11 and X.27

- Operating Ambient Temperature: -40°C to +85°C

- High Impedance Outputs

- Common Mode Output Voltage Range: −7.0 to 12 V

- Positive and Negative Current Limiting

- Transmission Rates in Excess of 10 MBPS

- Thermal Shutdown at 150°C Junction Temperature, (±20°C)

- Single 5.0 V Supply

- Pin Compatible with TI SN75172/4 and NS μA96172/4

- Interchangeable with MC3487 and AM26LS31 for EIA-422-A Applications

- Pb-Free Packages are Available\*

#### **MAXIMUM RATING**

| Rating                                                                         | Symbol           | Value                    | Unit |

|--------------------------------------------------------------------------------|------------------|--------------------------|------|

| Power Supply Voltage                                                           | V <sub>CC</sub>  | -0.5, +7.0               | Vdc  |

| Input Voltage (Data, Enable)                                                   | V <sub>in</sub>  | +7.0                     | Vdc  |

| Input Current (Data, Enable)                                                   | I <sub>in</sub>  | -24                      | mA   |

| Applied Output Voltage, when in 3–State Condition ( $V_{CC} = 5.0 \text{ V}$ ) | V <sub>za</sub>  | -10, +14                 | Vdc  |

| Applied Output Voltage, when V <sub>CC</sub> = 0 V                             | V <sub>zb</sub>  | ±14                      | Vdc  |

| Output Current                                                                 | Io               | Self-Limiting            | -    |

| Storage Temperature                                                            | T <sub>stg</sub> | <b>−65</b> , <b>+150</b> | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Devices should not be operated at these limits. The "Recommended Operating Conditions" table provides for actual device operation.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### ON Semiconductor®

http://onsemi.com

# **QUAD EIA-485 LINE DRIVERS**

SOIC-20 WB DW SUFFIX CASE 751D

PDIP-16 P SUFFIX CASE 648

#### **MARKING DIAGRAMS**

x = 2 or 4

A = Assembly Location

WL = Wafer Lot YY = Year WW = Work Week

G = Pb-Free Package

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 11 of this data sheet.

#### **RECOMMENDED OPERATING CONDITIONS**

| Characteristic                                                     | Symbol          | Min      | Тур  | Max             | Unit |

|--------------------------------------------------------------------|-----------------|----------|------|-----------------|------|

| Power Supply Voltage                                               | V <sub>CC</sub> | +4.75    | +5.0 | +5.25           | Vdc  |

| Input Voltage (All Inputs)                                         | V <sub>in</sub> | 0        | -    | V <sub>CC</sub> | Vdc  |

| Output Voltage in 3–State Condition, or when V <sub>CC</sub> = 0 V | V <sub>cm</sub> | -7.0     | -    | +12             | Vdc  |

| Output Current (Normal data transmission)                          | I <sub>O</sub>  | -65      | -    | +65             | mA   |

| Operating Ambient Temperature (see text)  EIA-485  EIA-422         | T <sub>A</sub>  | -40<br>0 | -    | +85             | °C   |

<sup>2.</sup> All limits are not necessarily functional concurrently.

# **ELECTRICAL CHARACTERISTICS** ( $-40^{\circ}C \le T_{A} \le 85^{\circ}C$ , $4.75 \text{ V} \le V_{CC} \le 5.25 \text{ V}$ , unless otherwise noted.)

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                             | Symbol                                                                                                                                                     | Min                       | Тур                                         | Max                                       | Unit                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------------|-------------------------------------------|---------------------------------------------------|

| Output Voltage Single–Ended Voltage $I_O = 0$ High @ $I_O = -33$ mA Low @ $I_O = +33$ mA Differential Voltage Open Circuit ( $I_O = 0$ ) $I_C = 10$ RL = 54 $I_C = 10$ (Figure 1)                                                                                                                                                                                                                          | Vo<br>Voh<br>Vol<br> V <sub>OD1</sub>  <br> V <sub>OD2</sub>                                                                                               | 0<br>-<br>-<br>1.5<br>1.5 | -<br>4.0<br>1.6<br>3.4<br>2.3               | 6.0<br>-<br>-<br>6.0<br>5.0               | Vdc                                               |

| Change in Differential*, $R_L = 54~\Omega$ (Figure 1) Differential Voltage, $R_L = 100~\Omega$ (Figure 1) Change in Differential*, $R_L = 100~\Omega$ (Figure 1) Differential Voltage, $-7.0~V \le V_{\text{cm}} \le 12~V$ (Figure 2) Change in Differential*, $-7.0~V \le V_{\text{cm}} \le 12~V$ (Figure 2) Offset Voltage, $R_L = 54~\Omega$ (Figure 1) Change in Offset*, $R_L = 54~\Omega$ (Figure 1) | ΔV <sub>OD2</sub>  <br> V <sub>OD2</sub>  <br> ΔV <sub>OD2</sub>  <br> V <sub>OD3</sub>  <br> ΔV <sub>OD3</sub>  <br> V <sub>OS</sub><br> ΔV <sub>OS</sub> | -<br>-<br>1.5<br>-<br>-   | 5.0<br>2.2<br>5.0<br>-<br>5.0<br>2.9<br>5.0 | 200<br>-<br>200<br>5.0<br>200<br>-<br>200 | mVdc<br>Vdc<br>mVdc<br>Vdc<br>mVdc<br>Vdc<br>mVdc |

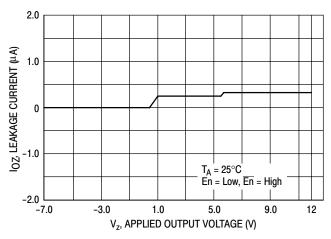

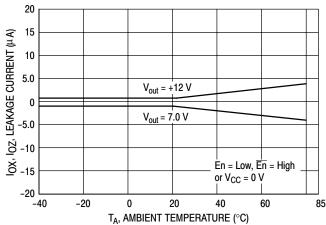

| Output Current (Each Output)  Power Off Leakage, $V_{CC}$ = 0, -7.0 V $\leq$ V <sub>O</sub> $\leq$ 12 V  Leakage in 3–State Mode, -7.0 V $\leq$ V <sub>O</sub> $\leq$ 12 V                                                                                                                                                                                                                                 | I <sub>O(off)</sub><br>I <sub>OZ</sub>                                                                                                                     | -50<br>-50                | 0                                           | +50<br>+50                                | μΑ                                                |

| Short Circuit Current to Ground Short Circuit Current, $-7.0 \text{ V} \leq \text{ V}_{\text{O}} \leq 12 \text{ V}$                                                                                                                                                                                                                                                                                        | I <sub>OSR</sub><br>I <sub>OS</sub>                                                                                                                        | -150<br>-250              | -<br>-                                      | +150<br>+250                              | mA                                                |

| Inputs Low Level Voltage (Pins 4 & 12, MC75174B only) Low Level Voltage (All Other Pins) High Level Voltage (All Inputs)                                                                                                                                                                                                                                                                                   | V <sub>IL(A)</sub><br>V <sub>IL(B)</sub><br>V <sub>IH</sub>                                                                                                | 0<br>0<br>2.0             | -<br>-<br>-                                 | 0.7<br>0.8<br>V <sub>CC</sub>             | Vdc                                               |

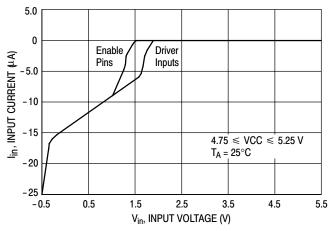

| Current @ V <sub>in</sub> = 2.7 V (All Inputs)<br>Current @ V <sub>in</sub> = 0.5 V (All Inputs)                                                                                                                                                                                                                                                                                                           | l <sub>IH</sub>                                                                                                                                            | -<br>-100                 | 0.2<br>-15                                  | 20<br>-                                   | μΑ                                                |

| Clamp Voltage (All Inputs, I <sub>in</sub> = –18 mA)                                                                                                                                                                                                                                                                                                                                                       | V <sub>IK</sub>                                                                                                                                            | -1.5                      | -                                           | -                                         | Vdc                                               |

| Thermal Shutdown Junction Temperature                                                                                                                                                                                                                                                                                                                                                                      | T <sub>jts</sub>                                                                                                                                           | -                         | +150                                        | -                                         | °C                                                |

| Power Supply Current (Outputs Open, V <sub>CC</sub> = 5.25 V) Outputs Enable Outputs Disabled                                                                                                                                                                                                                                                                                                              | Icc                                                                                                                                                        | -<br>-                    | 60<br>30                                    | 70<br>40                                  | mA                                                |

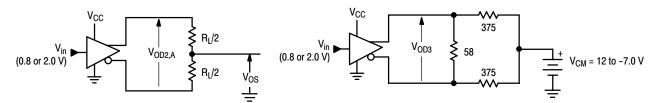

<sup>3. \*</sup>V<sub>in</sub> switched from 0.8 to 2.0 V. Typical values determined at 25°C ambient and 5.0 V supply.

# TIMING CHARACTERISTICS ( $T_A = 25^{\circ}C$ , $V_{CC} = 5.0 \text{ V}$ )

| Characteristics                                                                                                                                                                                                                                                                                                                                                                     | Symbol                                                                               | Min                        | Тур                                          | Max                                    | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------|----------------------------------------------|----------------------------------------|------|

| Propagation Delay – Input to Single-ended Output (Figure 3) Output Low-to-High Output High-to-Low                                                                                                                                                                                                                                                                                   | t <sub>PLH</sub>                                                                     | -<br>-                     | 23<br>18                                     | 30<br>30                               | ns   |

| Propagation Delay – Input to Differential Output (Figure 4) Input Low-to-High Input High-to-Low                                                                                                                                                                                                                                                                                     | t <sub>PLH(D)</sub>                                                                  | -<br>-                     | 15<br>17                                     | 25<br>25                               | ns   |

| Differential Output Transition Time (Figure 4)                                                                                                                                                                                                                                                                                                                                      | t <sub>dr</sub> , t <sub>df</sub>                                                    | -                          | 19                                           | 25                                     | ns   |

| Skew Timing                                                                                                                                                                                                                                                                                                                                                                         | t <sub>SK1</sub><br>t <sub>SK2</sub><br>t <sub>SK3</sub>                             | 1 1                        | 0.2<br>1.5<br>1.5                            |                                        | ns   |

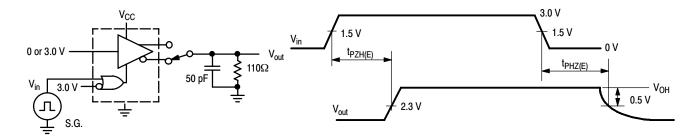

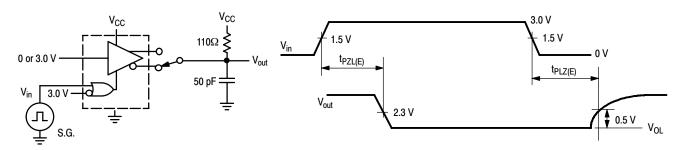

| Enable Timing Single-ended Outputs (Figure 5) Enable to Active High Output Enable to Active Low Output Active High to Disable (using Enable) Active Low to Disable (using Enable) Enable to Active High Output (MC75172B only) Enable to Active Low Output (MC75172B only) Active High to Disable (using Enable, MC75172B only) Active Low to Disable (using Enable, MC75172B only) | tpzh(E)<br>tpzl(E)<br>tphz(E)<br>tplz(E)<br>tpzh(E)<br>tpzl(E)<br>tphz(E)<br>tphz(E) | -<br>-<br>-<br>-<br>-<br>- | 48<br>20<br>35<br>30<br>58<br>28<br>38<br>36 | 60<br>30<br>45<br>50<br>70<br>35<br>50 | ns   |

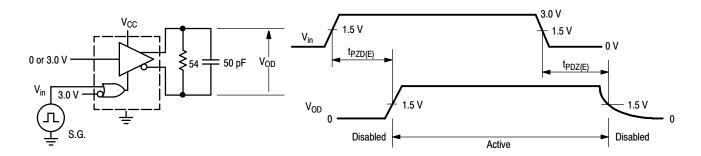

| Differential Outputs (Figure 6) Enable to Active Output Enable to Active Output (MC75172B only) Enable to 3-State Output Enable to 3-State Output (MC75172B only)                                                                                                                                                                                                                   | tPZD(E)<br>tPZD(E)<br>tPDZ(E)<br>tPDZ(E)                                             | -<br>-<br>-<br>-           | 47<br>56<br>32<br>40                         | -<br>-<br>-<br>-                       | ns   |

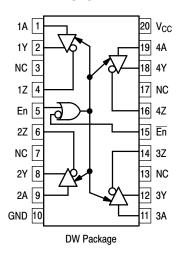

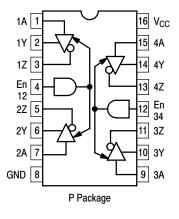

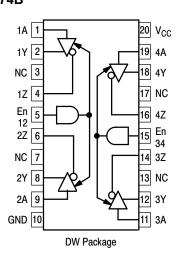

### **PIN CONNECTIONS**

# MC75172B

# MC75174B

Figure 1. V<sub>DD</sub> Measurement

Figure 2. Common Mode Test

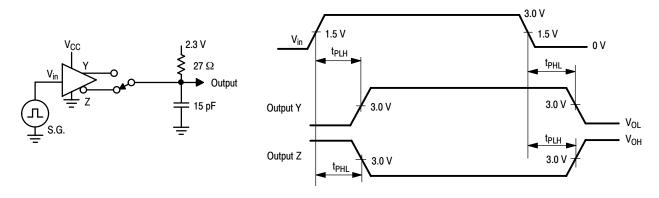

Figure 3. Propagation Delay, Single-Ended Outputs

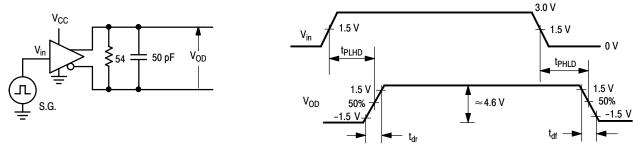

- NOTES: 1.S.G. set to: f  $\leq$  1.0 MHz; duty cycle = 50%;  $t_{f}$ ,  $t_{f}$ ,  $\leq$  5.0 ns.

- $2.t_{SK1} = |t_{PLHD} t_{PHLD}|$  for each driver.

- 3.1 SK2 computed by subtracting the shortest tPLHD from the longest tPLHD of the 4 drivers within a package.

- 4.t<sub>SK3</sub> computed by subtracting the shortest t<sub>PHLD</sub> from the longest t<sub>PHLD</sub> of the 4 drivers within a package.

Figure 4. Propagation Delay, Differential Outputs

Figure 5. Enable Timing, Single-Ended Outputs

$\begin{aligned} \text{NOTES:} \quad & \text{1.S.G. set to: } f \leqslant \text{1.0 MHz; duty cycle} = 50\%; \, t_f, \, t_f, \, \leqslant \text{5.0 ns.} \\ & \text{2.V}_{in} \text{ is inverted for } \overline{\text{Enable}} \text{ measurements.} \end{aligned}$

Figure 6. Enable Timing, Differential Outputs

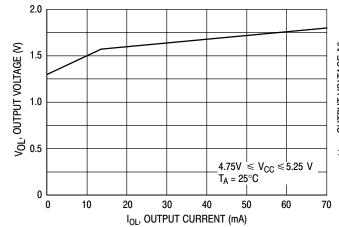

Figure 7. Single-Ended Output Voltage versus Output Sink Current

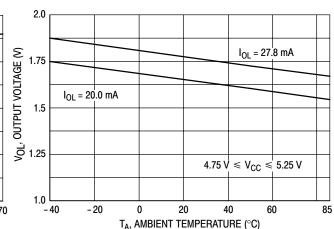

Figure 8. Single-Ended Output Voltage versus Temperature

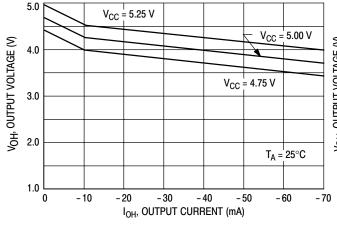

Figure 9. Single-Ended Output Voltage versus Output Source Current

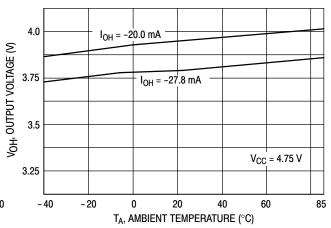

Figure 10. Single-Ended Output Voltage versus Temperature

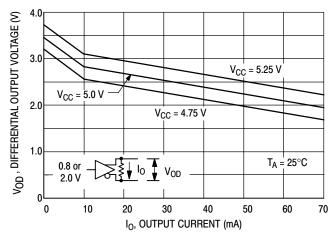

Figure 11. Output Differential Voltage versus Load Current

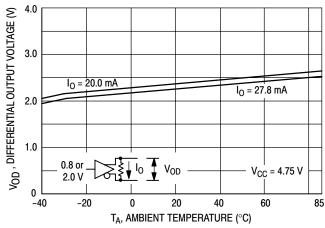

Figure 12. Output Differential Voltage versus Temperature

Figure 13. Output Leakage Current versus Output Voltage

Figure 14. Output Leakage Current versus Temperature

Figure 15. Input Current versus Input Voltage

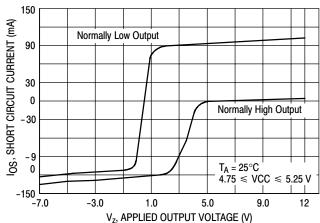

Figure 16. Short Circuit Current versus Common Mode Voltage

#### APPLICATIONS INFORMATION

#### Description

The MC75172B and MC75174B are differential line drivers designed to comply with EIA–485 Standard (April 1983) for use in balanced digital multipoint systems containing multiple drivers. The drivers also comply with EIA–422–A and CCITT Recommendations V.11 and X.27. The drivers meet the EIA–485 requirement for protection from damage in the event that two or more drivers attempt to transmit data simultaneously on the same cable. Data rates in excess of 10 MBPS are possible, depending on the cable length and cable characteristics. A single power supply, 5.0 V, ±5%, is required at a nominal current of 60 mA, plus load currents.

#### **Outputs**

Each output (when active) will be a low or a high voltage, which depends on the input state and the load current (see Table 1, 2 and Figures 7 to 10). The graphs apply to each driver, regardless of how many other drivers within the package are supplying load current.

Table 1. MC75172B Truth Table

|            | Enables |    | Out | puts |

|------------|---------|----|-----|------|

| Data Input | EN      | EN | Y   | Z    |

| Н          | Н       | Х  | Н   | L    |

| L          | Н       | X  | L   | Н    |

| Н          | X       | L  | Н   | L    |

| L          | X       | L  | L   | Н    |

| X          | L       | Н  | Z   | Z    |

Table 2. MC75174B Truth Table

|            |        | Outputs |   |  |

|------------|--------|---------|---|--|

| Data Input | Enable | Y       | Z |  |

| Н          | Н      | Н       | L |  |

| L          | Н      | L       | Н |  |

| X          | L      | Z       | Z |  |

H = Logic high, L = Logic low, X = Irrelevant, Z = High impedance

The two outputs of a driver are always complementary. A "high" output can only source current out, while a "low" output can only sink current (except for short circuit current – see Figure 16).

The outputs will be in the high impedance mode when:

- a) the Enable inputs are set according to Table 1 or 2;

- b) V<sub>CC</sub> is less than 1.5 V;

- c) the junction temperature exceeds the trip point of the thermal shutdown circuit (see below). When in this condition, the output's source and sink capability are shut off, and only leakage currents will flow (see Figures 13, 14). Disabled outputs may be taken to any voltage between -7.0 V and 12 V without damage.

The drivers are protected from short circuits by two methods:

- a) Current limiting is provided at each output, in both the source and sink direction, for shorts to any voltage within the range of 12 V to −7.0 V, with respect to circuit ground (see Figure 16). The short circuit current will flow until the fault is removed, or until the thermal shutdown circuit activates (see below). The current limiting circuit has a negative temperature coefficient and requires no resetting upon removal of the fault condition.

- b) A thermal shutdown circuit disables the outputs when the junction temperature reaches 150°C, ±20°C. The thermal shutdown circuit has a hysteresis of ≈ 12°C to prevent oscillations. When this circuit activates, the output stage of each driver is put into the high impedance mode, thereby shutting off the output currents. The remainder of the internal circuitry remains biased. The outputs will become active once again as the IC cools down.

#### **Driver Inputs**

The driver inputs determine the state of the outputs in accordance with Tables 1 and 2. The driver inputs have a nominal threshold of 1.2 V, and their voltage must be kept within the range of 0 V to V<sub>CC</sub> for proper operation. If the voltage is taken more than 0.5 V below ground, excessive currents will flow, and proper operation of the drivers will be affected. An open pin is equivalent to a logic high, but good design practices dictate that inputs should never be left open. The characteristics of the driver inputs are shown in Figure 15. This graph is not affected by the state of the Enable pins.

#### **Enable Logic**

Each driver's outputs are active when the Enable inputs (Pins 4 and 12) are true according to Tables 1 and 2.

The Enable inputs have a nominal threshold of 1.2~V and their voltage must be kept within the range of 0~V to  $V_{\rm CC}$  for proper operation. If the voltage is taken more than 0.5~V below ground, excessive currents will flow, and proper operation of the drivers will be affected. An open pin is equivalent to a logic high, but good design practices dictate that inputs should never be left open. The Enable input characteristics are shown in Figure 15.

#### **Operating Temperature Range**

The minimum ambient operating temperature is listed as  $-40^{\circ}$ C to meet EIA-485 specifications, and  $0^{\circ}$ C to meet EIA-422-A specifications. The higher  $V_{OD}$  required by EIA-422-A is the reason for the narrower temperature range.

The maximum ambient operating temperature (applicable to both EIA–485 and EIA–422–A) is listed as 85°C. However, a lower ambient may be required depending on system use (i.e. specifically how many drivers within a package are used) and at what current levels they are operating. The maximum power which may be dissipated within the package is determined by:

$$PD_{max} = \frac{T_{Jmax}^{-T}A}{R_{\theta JA}}$$

where:

$R_{\theta JA}$  = package thermal resistance (typical 70°C/W for the DIP package, 85°C/W for SOIC package);

$T_{Jmax} = max$ . operating junction temperature, and

$T_A$  = ambient temperature.

Since the thermal shutdown feature has a trip point of  $150^{\circ}$ C,  $\pm 20^{\circ}$ C,  $T_{Jmax}$  is selected to be  $130^{\circ}$ C. The power dissipated within the package is calculated from:

PD = {[(

$$V_{CC} - V_{OH}) \bullet I_{OH}$$

] +  $V_{OL} \bullet I_{OL}$ )} each driver + ( $V_{CC} \bullet I_{CC}$ )

where:  $V_{CC}$  = the supply voltage;

V<sub>OH</sub>, V<sub>OL</sub> are measured or estimated from

Figures 7 to 10;

$I_{CC}$  = the quiescent power supply current (typical 60 mA).

As indicated in the equation, the first term (in brackets) must be calculated and summed for each of the four drivers, while the last term is common to the entire package.

Example 1:  $T_A = 25^{\circ}C$ ,  $I_{OL} = I_{OH} = 55$  mA for each driver,  $V_{CC} = 5.0$  V, DIP package. How many drivers per package can be used?

Maximum allowable power dissipation is:

$$PD_{max} = \frac{130^{\circ}C - 25^{\circ}C}{70^{\circ}C/W} = 1.5 \text{ W}$$

Since the power supply current of 60 mA dissipates 300 mW, that leaves 1.2 W (1.5 W – 0.3 W) for the drivers. From Figures 7 and 9,  $V_{OL} \approx 1.75$  V, and  $V_{OH} \approx 3.85$  V. The power dissipated in each driver is:

$$\{(5.0 - 3.85) \bullet 0.055\} + (1.75 \bullet 0.055) = 160 \text{ mW}.$$

Since each driver dissipates 160 mW, the four drivers per package could be used in this application.

Example 2:  $T_A = 85^{\circ}C$ ,  $I_{OL} = 27.8$  mA,  $I_{OH} = 20$  mA for each driver,  $V_{CC} = 5.0$  V, SOIC package. How many drivers per package can be used?

Maximum allowable power dissipation is:

$$PD_{max} = \frac{130^{\circ}C - 85^{\circ}C}{85^{\circ}C/W} = 0.53 \text{ W}$$

Since the power supply current of 60 mA dissipates 300 mW, that leaves 230 mW (530 mW - 300 mW) for the

drivers. From Figures 8 and 10 (adjusted for  $V_{CC}$  = 5.0 V),  $V_{OL} \approx 1.38$  V, and  $V_{OH} \approx 4.27$  V. The power dissipated in each driver is:

$$\{(5.0 - 4.27) \bullet 0.020\} + (1.38 \bullet 0.0278) = 53 \text{ mW}$$

Since each driver dissipates 53 mW, the use of all four drivers in a package would be marginal. Options include reducing the load current, reducing the ambient temperature, and/or providing a heat sink.

#### **System Requirements**

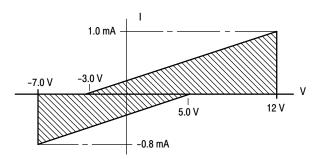

EIA–485 requires each driver to be capable of transmitting data differentially to at least 32 unit loads, plus an equivalent DC termination resistance of  $60\Omega$ , over a common mode voltage of -7.0 to 12 V. A unit load (U.L.), as defined by EIA–485, is shown in Figure 17.

Reprinted from EIA-485, Electronic Industries Association, Washington, DC.

Figure 17. Unit Load Definition

A load current within the shaded regions represents an impedance of less than one U.L., while a load current of a magnitude outside the shaded area is greater than one U.L. A system's total load is the sum of the unit load equivalents of each receiver's input current, and each disabled driver's output leakage current. The  $60\Omega$  termination resistance mentioned above allows for two  $120\Omega$  terminating resistors.

Using the EIA–485 requirements (worst case limits), and the graphs of Figures 7 and 9, it can be determined that the maximum current an MC75172B or MC75174B driver will source or sink is  $\approx$ 65 mA.

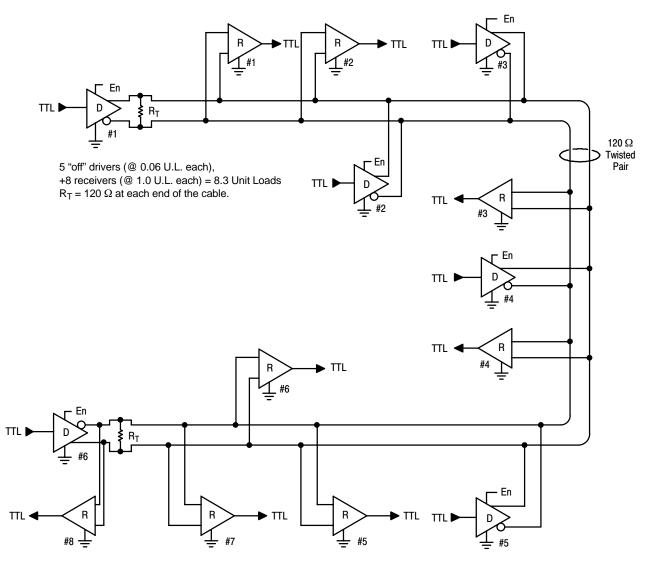

#### System Example

An example of a typical EIA-485 system is shown in Figure 18. In this example, it is assumed each receiver's input characteristics correspond to 1.0 U.L. as defined in Figure 17. Each "off" driver, with a maximum leakage of  $\pm 50~\mu A$  over the common mode range, presents a load of  $\approx 0.06~U.L$ . The total load for the active driver is therefore 8.3 unit loads, plus the parallel combination of the two terminating resistors ( $60\Omega$ ). It is up to the system software to control the driver Enable pins to ensure that only one driver is active at any time.

#### **Termination Resistors**

Transmission line theory states that, in order to preserve the shape and integrity of a waveform traveling along a cable, the cable must be terminated in an impedance equal to its characteristic impedance. In a system such as that depicted in Figure 18, in which data can travel in both directions, both physical ends of the cable must be terminated. Stubs, leading to each receiver and driver, should be as short as possible.

Leaving off the terminations will generally result in reflections which can have amplitudes of several volts above  $V_{CC}$  or below ground. These overshoots and undershoots can disrupt the driver and/or receiver operation, create false data, and in some cases damage components on the bus.

NOTES:

- 1. Terminating resistors R<sub>T</sub> must be located at the physical ends of the cable.

- 2. Stubs should be as short as possible.

- Circuit ground of all drivers and receivers must be connected via a dedicated wire within the cable.Do not rely on chassis ground or power line ground.

Figure 18. Typical EIA-485 System

#### **COMPARING SYSTEM REQUIREMENTS**

| Characteristic                                       | Symbol                               | EIA-485                                       | EIA-422-A                                                                   | V.11 and X.27                                                               |

|------------------------------------------------------|--------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| GENERATOR (Driver)                                   | '                                    | 1                                             | 1                                                                           | '                                                                           |

| Output Impedance (Note 1)                            | Z <sub>out</sub>                     | Not Specified                                 | < 100 Ω                                                                     | 50 10 100 Ω                                                                 |

| Open Circuit Voltage<br>Differential<br>Single–Ended | V <sub>OCD</sub><br>V <sub>OCS</sub> | 1.5 to 6.0 V<br>< 6.0 V                       | ≤ 6.0 V<br>≤ 6.0 V                                                          | ≤ 6.0 V, w/3.9 kΩ, Load<br>≤ 6.0 V, w/3.9 kΩ, Load                          |

| Loaded Differential Voltage                          | V <sub>OD</sub>                      | 1.5 to 5.0 V, w/54 Ω load                     | $\geqslant$ 2.0 V or $\geqslant$ 0.5 V <sub>OCD</sub> , w/100 $\Omega$ load | $\geqslant$ 2.0 V or $\geqslant$ 0.5 V <sub>OCD</sub> , w/100 $\Omega$ load |

| Differential Voltage Balance                         | $\Delta V_{OD}$                      | < 200 mV                                      | ≤ 400 mV                                                                    | < 400 mV                                                                    |

| Output Common Mode Range                             | $V_{CM}$                             | -7.0 to +12 V                                 | Not Specified                                                               | Not Specified                                                               |

| Offset Voltage                                       | V <sub>OS</sub>                      | -1.0 < V <sub>OS</sub> < 3.0 V                | ≤ 3.0 V                                                                     | ≤ 3.0 V                                                                     |

| Offset Voltage Balance                               | $\Delta V_{OS}$                      | < 200 mV                                      | ≤ 400 mV                                                                    | < 400 mV                                                                    |

| Short Circuit Current                                | Ios                                  | ≤ 250 mA for –7.0 to 12 V                     | ≤ 150 mA to ground                                                          | ≤ 150 mA to ground                                                          |

| Leakage Current (V <sub>CC</sub> = 0)                | I <sub>OLK</sub>                     | Not Specified                                 | ≤ 100 μA to −0.25 V thru<br>6.0 V                                           | $\leq$ 100 $\mu A$ to $\pm0.25$ V                                           |

| Output Rise/Fall Time (Note 2)                       | t <sub>r</sub> , t <sub>f</sub>      | ≤ 0.3 T <sub>B</sub> , w/54 Ω/1150 pF<br>load | $\leq$ 0.1 T <sub>B</sub> or $\leq$ 20 ns, w/100 $\Omega$ load              | $\leq$ 0.1 T <sub>B</sub> or $\leq$ 20 ns, w/100 $\Omega$ load              |

| RECEIVER                                             | II.                                  |                                               |                                                                             |                                                                             |

| Input Sensitivity                                    | $V_{th}$                             | ± 200 mV                                      | ± 200 mV                                                                    | ± 300 mV                                                                    |

| Input Bias Voltage                                   | V <sub>bias</sub>                    | ≤ 3.0 V                                       | ≤ 3.0 V                                                                     | ≤ 3.0 V                                                                     |

| Input Common Mode Range                              | V <sub>cm</sub>                      | -7.0 to 12 V                                  | –7.0 to 7.0 V                                                               | –7.0 to 7.0 V                                                               |

| Dynamic Input Impedance                              | R <sub>in</sub>                      | Spec number of U.L.                           | ≥ 4 kΩ                                                                      | ≥ 4 kΩ                                                                      |

NOTES: 1. Compliance with V.11 and X.27 (Blue book) output impedance requires external resistors in series with the outputs of the MC75172B and MC75174B.

### **Additional Information**

Copies of the EIA Recommendations (EIA–485 and EIA–422–A) can be obtained from the Electronics Industries Association, Washington, D.C. (202–457–4966). Copies of the CCITT Recommendations (V.11 and X.27) can be obtained from the United States Department of Commerce, Springfield, VA (703–487–4600).

#### **ORDERING INFORMATION**

| Device        | Operating Temperature Range                         | Package                | Shipping <sup>†</sup> |

|---------------|-----------------------------------------------------|------------------------|-----------------------|

| MC75172BDW    |                                                     | SOIC-20WB              |                       |

| MC75172BDWG   |                                                     | SOIC-20WB<br>(Pb-Free) | 38 Units / Rail       |

| MC75172BDWR2  |                                                     | SOIC-20WB              |                       |

| MC75172BDWR2G |                                                     | SOIC-20WB<br>(Pb-Free) | 1000 / Tape & Reel    |

| MC75174BDW    |                                                     | SOIC-20WB              |                       |

| MC75174BDWG   | $T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}$ | SOIC-20WB<br>(Pb-Free) | 38 Units / Rail       |

| MC75174BDWR2  |                                                     | SOIC-20WB              |                       |

| MC75174BDWR2G |                                                     | SOIC-20WB<br>(Pb-Free) | 1000 / Tape & Reel    |

| MC75174BP     |                                                     | PDIP-16                |                       |

| MC75174BPG    |                                                     | PDIP-16<br>(Pb-Free)   | 25 Units / Rail       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>2.</sup>  $T_B = Bit time$ .

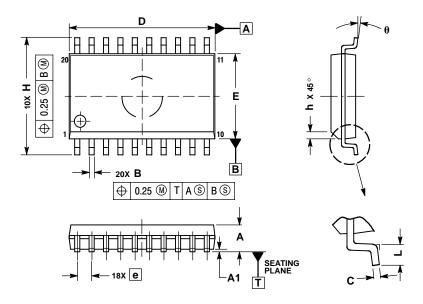

#### PACKAGE DIMENSIONS

SOIC-20 WB **DW SUFFIX PLASTIC PACKAGE CASE 751D-05 ISSUE G**

- NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

3. DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTEUTION.

- PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF B DIMENSION AT MAXIMUM MATERIAL

|     | MILLIMETERS |       |  |  |

|-----|-------------|-------|--|--|

| DIM | MIN         | MAX   |  |  |

| Α   | 2.35        | 2.65  |  |  |

| A1  | 0.10        | 0.25  |  |  |

| В   | 0.35        | 0.49  |  |  |

| C   | 0.23        | 0.32  |  |  |

| D   | 12.65       | 12.95 |  |  |

| Е   | 7.40        | 7.60  |  |  |

| е   | 1.27        | BSC   |  |  |

| Н   | 10.05       | 10.55 |  |  |

| h   | 0.25        | 0.75  |  |  |

| L   | 0.50        | 0.90  |  |  |

| A   | 0 °         | 7 °   |  |  |

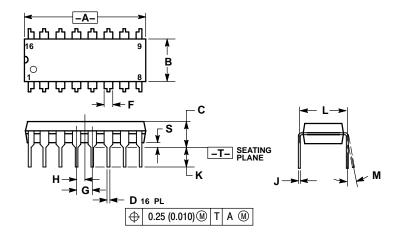

PDIP-16 **P SUFFIX PLASTIC PACKAGE CASE 648-08 ISSUE T**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: INCH.

DIMENSION L TO CENTER OF LEADS

WHEN FORMED PARALLEL.

- DIMENSION B DOES NOT INCLUDE

- MOLD FLASH.

5. ROUNDED CORNERS OPTIONAL.

|     | INCHES    |       | MILLIN   | IETERS |

|-----|-----------|-------|----------|--------|

| DIM | MIN       | MAX   | MIN      | MAX    |

| Α   | 0.740     | 0.770 | 18.80    | 19.55  |

| В   | 0.250     | 0.270 | 6.35     | 6.85   |

| С   | 0.145     | 0.175 | 3.69     | 4.44   |

| D   | 0.015     | 0.021 | 0.39     | 0.53   |

| F   | 0.040     | 0.70  | 1.02     | 1.77   |

| G   | 0.100     | BSC   | 2.54 BSC |        |

| Н   | 0.050 BSC |       | 1.27 BSC |        |

| J   | 0.008     | 0.015 | 0.21     | 0.38   |

| K   | 0.110     | 0.130 | 2.80     | 3.30   |

| L   | 0.295     | 0.305 | 7.50     | 7.74   |

| М   | 0°        | 10 °  | 0 °      | 10 °   |

| S   | 0.020     | 0.040 | 0.51     | 1.01   |

ON Semiconductor and the registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

MC75172B/D