## **General Description**

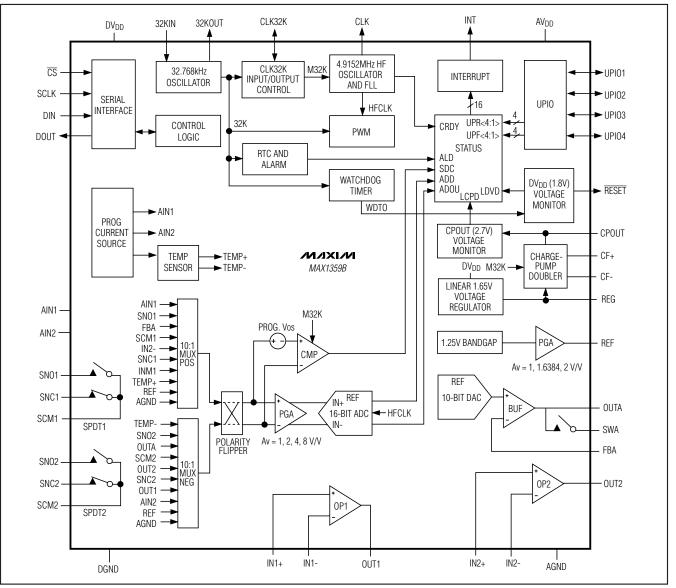

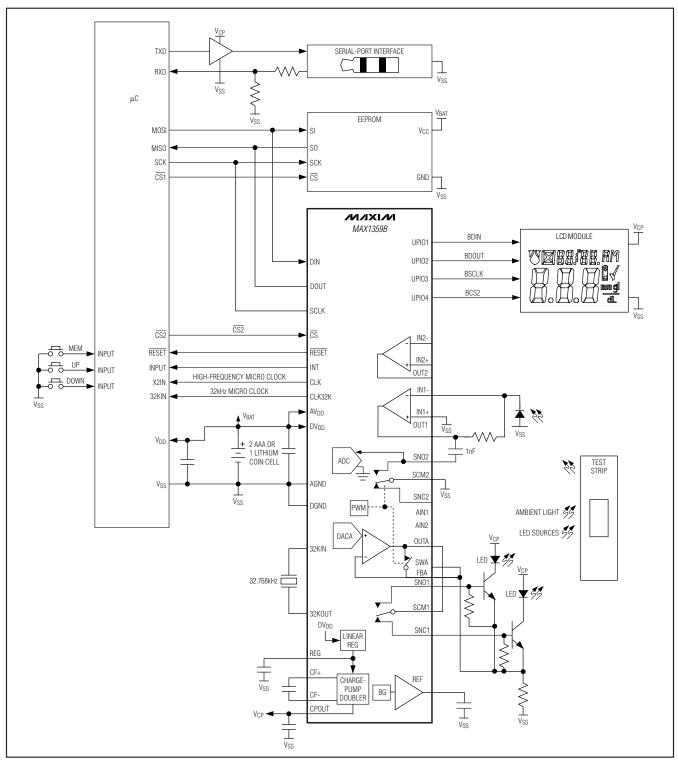

The MAX1359B smart data-acquisition systems (DAS) is based on a 16-bit, sigma-delta analog-to-digital converter (ADC) and system-support functionality for a microprocessor ( $\mu$ P)-based system. This device integrates an ADC, DAC, two operational amplifiers, internal 1.25V/2.048V/2.5V selectable reference, temperature sensors, analog switches, a 32kHz oscillator, a realtime clock (RTC) with alarm, a high-frequency-locked loop (FLL) clock, four user-programmable I/Os, an interrupt generator, and 1.8V and 2.7V voltage monitors in a single chip.

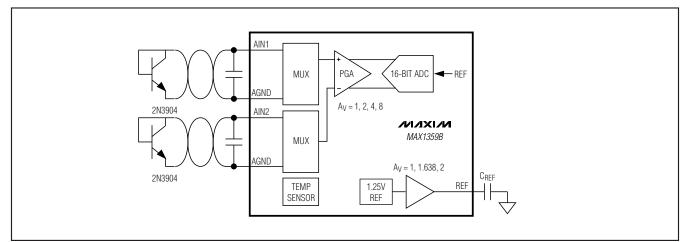

The MAX1359B has dual 10:1 differential input multiplexers (muxes) that accept signal levels from 0 to AV<sub>DD</sub>. An on-chip 1x to 8x programmable-gain amplifier (PGA) measures low-level signals and reduces external circuitry required.

The MAX1359B operates from a single +1.8V to +3.6V supply and consumes only 1.4mA in normal mode and only  $6.1\mu$ A in sleep mode.

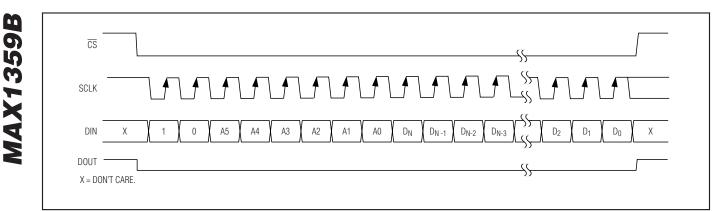

The serial interface is compatible with either SPI™/QSPI™ or MICROWIRE™, and is used to power up, configure, and check the status of all functional blocks.

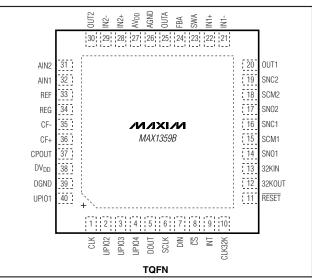

The MAX1359B is available in a space-saving 40-pin TQFN package and is specified over the commercial ( $0^{\circ}C$  to +70°C) and the extended (-40°C to +85°C) temperature ranges.

## **Applications**

Battery-Powered and Portable Devices

Electrochemical and Optical Sensors

Medical Instruments

Industrial Control

Data-Acquisition Systems

#### **Features**

- +1.8V to +3.6V Single-Supply Operation

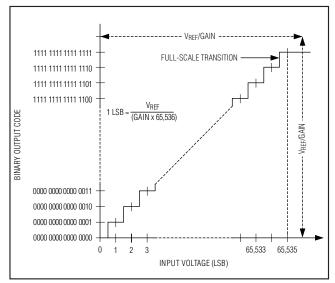

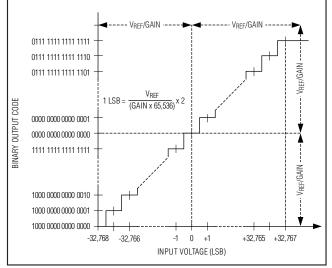

- Multichannel 16-Bit Sigma-Delta ADC 10sps to 512sps Programmable Conversion Rate Self and System Offset and Gain Calibration PGA with Gains of 1, 2, 4, or 8 Unipolar and Bipolar Modes 10-Input Differential Multiplexer

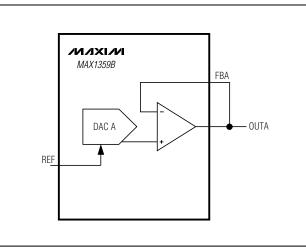

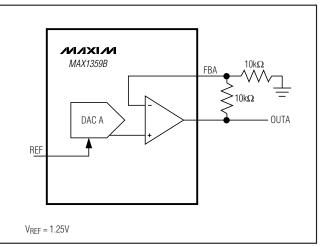

- 10-Bit Force-Sense DAC

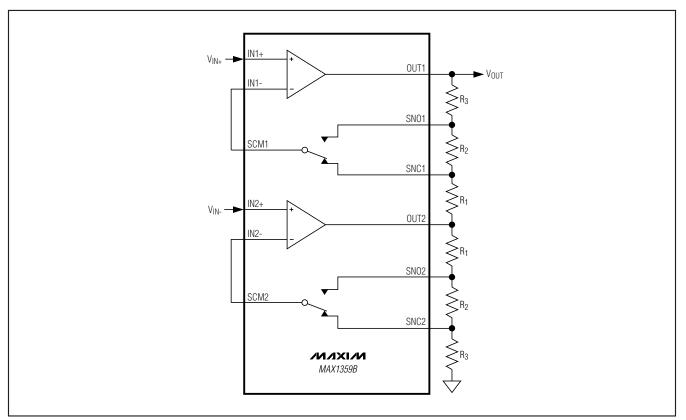

- Uncommitted Op Amps

- Dual SPDT Analog Switches

- 1.25V, 2.048V, or 2.5V Selectable Voltage Reference

- Internal Charge Pump

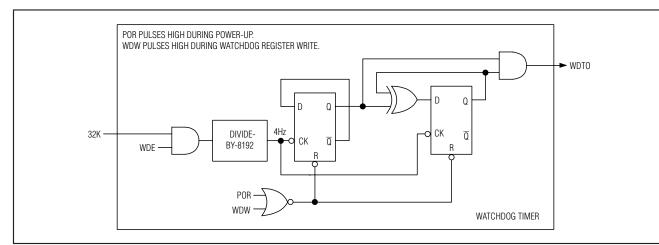

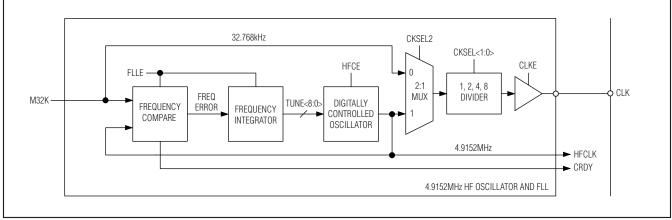

- System Support Real Time Clock and Alarm Register Internal/External Temperature Sensor Internal Oscillator with Clock Output User-Programmable I/O and Interrupt Generator VDD Monitors

- ♦ SPI/QSPI/MICROWIRE, 4-Wire Serial Interface

- Space-Saving (6mm x 6mm x 0.8mm) 40-Pin TQFN Package

## **\_Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE  |

|--------------|----------------|--------------|

| MAX1359BETL+ | -40°C to +85°C | 40 TQFN-EP** |

| MAX1359BCTL+ | 0°C to +70°C   | 40 TQFN-EP** |

\*\* EP = Exposed pad.

+Denotes a lead(Pb)-free/RoHS-compliant package.

## Pin Configuration

SPI/QSPI are trademarks of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

##

\_\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to AGND             |                                   |

|--------------------------------------|-----------------------------------|

| DV <sub>DD</sub> to DGND             | 0.3V to +4V                       |

| AV <sub>DD</sub> to DV <sub>DD</sub> | 4V to +4V                         |

| AGND to DGND                         | -0.3V to +0.3V                    |

| CLK32K to DGND                       | 0.3V to (DV <sub>DD</sub> + 0.3V) |

| UPIO_ to DGND                        | 0.3V to +4V                       |

| Digital Inputs to DGND               | 0.3V to +4V                       |

| Analog Inputs to AGND                | 0.3V to (AV <sub>DD</sub> + 0.3V) |

| Digital Output to DGND               | 0.3V to (DV <sub>DD</sub> + 0.3V) |

| Analog Outputs to AGND               | 0.3V to (AV <sub>DD</sub> + 0.3V) |

| CPOUT                                                |                  |

|------------------------------------------------------|------------------|

| Continuous Current Into Any Pin                      |                  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}$ ) |                  |

| 40-Pin TQFN (derate 25.6mW/°C above                  | e +70°C)2051.3mW |

| Operating Temperature Range                          |                  |

| MAX1359BETL                                          | 40°C to +85°C    |

| MAX1359BCTL                                          | 0°C to +70°C     |

| Junction Temperature                                 | +150°C           |

| Storage Temperature Range                            | 65°C to +150°C   |

| Lead Temperature (soldering, 10s)                    | +260°C           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(AV_{DD} = DV_{DD} = +1.8V \text{ to } +3.6V, V_{REF} = +1.25V, \text{ external reference, } f_{CLK32K} = 32.768kHz \text{ (external clock), } C_{REG} = 10\mu\text{F}, C_{CPOUT} = 10\mu\text{F}, 10\mu\text{F} \text{ between CF+ and CF-}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C.}) \text{ (Note 1)}$

| PARAMETER                                                        | SYMBOL | CONDITIONS                                                                                                          | MIN | ТҮР     | МАХ    | UNITS             |

|------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------|-----|---------|--------|-------------------|

| ADC DC ACCURACY                                                  |        |                                                                                                                     |     |         |        |                   |

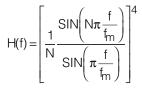

| Noise-Free Resolution                                            |        | Data rate = 10sps, PGA gain = 2;<br>data rate = 10sps to 60sps, PGA gain = 1;<br>no missing codes, Table 1 (Note 2) | 16  |         |        | Bits              |

| Conversion Rate                                                  |        | No missing codes, Table 1                                                                                           | 10  |         | 512    | sps               |

| Output Noise                                                     |        | No missing codes                                                                                                    |     | Table 1 |        | μV <sub>RMS</sub> |

| Integral Nonlinearity                                            | INL    | Unipolar mode, AV <sub>DD</sub> = 3V,<br>data rate = 40sps, PGA gain = 1,<br>T <sub>A</sub> = +25°C                 |     | ±0.004  |        | %FSR              |

| Unipolar Offset Error or Bipolar                                 |        | Uncalibrated                                                                                                        |     | ±1.0    |        | %FSR              |

| Zero Error (Note 3)                                              |        | Data rate = 10sps, PGA gain = 1, calibrated                                                                         |     |         | ±0.003 | %F3R              |

| Unipolar Offset-Error or Bipolar<br>Zero-Error Temperature Drift |        | Bipolar                                                                                                             |     | ±2.0    |        | µV/°C             |

| (Note 4)                                                         |        | Unipolar                                                                                                            |     | ±10     |        | μνγο              |

| Gain Error (Notes 3, 5)                                          |        | Uncalibrated                                                                                                        |     | ±0.6    |        | % FSB             |

| Gain Endr (Notes 3, 5)                                           |        | Data rate = 10sps, PGA = 1, calibrated                                                                              |     | ±0.003  |        | ⁄₀ ron            |

| Gain-Error Temperature<br>Coefficient                            |        | (Notes 4, 6)                                                                                                        |     | ±1.0    |        | ppm/°C            |

| DC Positive Power-Supply<br>Rejection Ratio                      | PSRR   | PGA gain = 1, unipolar mode, measured by full-scale error with $AV_{DD}$ = 1.8V to 3.6V                             |     | 73      |        | dB                |

| ADC ANALOG INPUTS (AIN1, AI                                      | N2)    |                                                                                                                     |     |         |        |                   |

| DC Input Common-Mode<br>Rejection Ratio                          | CMRR   | PGA gain = 1, unipolar mode                                                                                         |     | 85      |        | dB                |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = +1.8V \text{ to } +3.6V, V_{REF} = +1.25V, \text{ external reference, } f_{CLK32K} = 32.768 \text{kHz}$  (external clock),  $C_{REG} = 10 \mu\text{F}, C_{CPOUT} = 10 \mu\text{F}, 10 \mu\text{F}$  between CF+ and CF-,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                            | SYMBOL                   | COND                                                                                  | ITIONS                                        | MIN                         | ТҮР     | MAX                        | UNITS  |

|--------------------------------------|--------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------|---------|----------------------------|--------|

| Normal-Mode 60Hz Rejection<br>Ratio  |                          | Data rate = 10sps or 6<br>unipolar mode (Note 2                                       | 100                                           |                             |         | dB                         |        |

| Normal-Mode 50Hz Rejection<br>Ratio  |                          | Data rate = 10sps or 5<br>unipolar mode (Note 2                                       |                                               | 100                         |         |                            | dB     |

| Absolute Input Range                 |                          |                                                                                       |                                               | AGND                        |         | AV <sub>DD</sub>           | V      |

| Differential Input Penge             |                          | Unipolar mode                                                                         |                                               | -0.05 /<br>Gain             |         | V <sub>REF</sub> /<br>Gain | v      |

| Differential Input Range             |                          | Bipolar mode                                                                          |                                               | -V <sub>REF</sub> /<br>Gain |         | V <sub>REF</sub> /<br>Gain | V      |

| DC Input Current (Note 7)            |                          | ADC not in measurem<br>enabled, $T_A \le +55^{\circ}C$ ,<br>(AV <sub>DD</sub> - 0.1V) | ,                                             |                             |         | ±1                         | nA     |

|                                      |                          | $T_A = +85^{\circ}C$                                                                  |                                               |                             |         | ±5                         |        |

| Input Sampling Capacitance           | CIN                      |                                                                                       |                                               | -                           | 5       |                            | pF     |

| Input Sampling Rate                  | <b>f</b> SAMPLE          |                                                                                       |                                               |                             | 21.84   |                            | kHz    |

| External Source Impedance at Input   |                          | See Table 3                                                                           |                                               |                             | Table 3 |                            | kΩ     |

| FORCE-SENSE DAC (RL = 10k $\Omega$   | and C <sub>L</sub> = 200 | )pF, FBA = OUTA, unle                                                                 | ess otherwise noted)                          |                             |         |                            |        |

| Resolution                           |                          | Guaranteed monotoni                                                                   | С                                             | 10                          |         |                            | Bits   |

| Differential Nonlinearity            | DNL                      | Code 3D hex to 3FF h                                                                  | ex                                            |                             |         | ±1                         | LSB    |

| Integral Nonlinearity                | INL                      | Code 3D hex to 3FF h                                                                  | ex                                            |                             |         | ±4                         | LSB    |

| Offset Error                         |                          | Reference to code 52                                                                  | hex                                           |                             |         | ±20                        | mV     |

| Offset-Error Tempco                  |                          |                                                                                       |                                               |                             | ±4.4    |                            | µV/°C  |

| Gain Error                           |                          | Excludes offset and vo                                                                | oltage reference error                        |                             |         | ±5                         | LSB    |

| Gain-Error Tempco                    |                          | Excludes offset and re                                                                | eference drift                                |                             | ±1      |                            | ppm/°C |

| Input Leakage Current at SWA/B       |                          | SWA/B switches open                                                                   | (Notes 7, 8)                                  |                             |         | ±1                         | nA     |

|                                      |                          | $V_{FBA/B} = +0.3V$ to                                                                | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |                             |         | ±1                         | nA     |

| Input Leakage Current at FBA/B       |                          | (AV <sub>DD</sub> - 0.3V)                                                             | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$   |                             |         | ±600                       | рА     |

|                                      |                          | (Note 7)                                                                              | $T_A = 0^{\circ}C \text{ to } +50^{\circ}C$   |                             |         | ±400                       | рА     |

| DAC Output Buffer Leakage<br>Current |                          | DAC buffer disabled (Note 7)                                                          |                                               |                             |         | ±75                        | nA     |

| Input Common-Mode Voltage            |                          | At FBA                                                                                |                                               | 0                           |         | AV <sub>DD</sub> -<br>0.35 | V      |

| Line Regulation                      |                          | $AV_{DD} = +1.8V$ to +3.6                                                             | V                                             |                             | 40      | 175                        | μV/V   |

| Load Regulation                      |                          | $I_{OUT} = \pm 2mA, C_{L} = 10$                                                       | 00pF (Note 2)                                 |                             |         | 0.5                        | μ٧/μΑ  |

| Output Voltage Range                 |                          |                                                                                       |                                               | AGND                        |         | AV <sub>DD</sub>           | V      |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = +1.8V \text{ to } +3.6V, V_{REF} = +1.25V, \text{ external reference, } f_{CLK32K} = 32.768 \text{kHz}$  (external clock),  $C_{REG} = 10 \mu \text{F}$ ,  $C_{CPOUT} = 10 \mu \text{F}$ ,  $10 \mu \text{F}$  between CF+ and CF-,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C.}$ ) (Note 1)

| PARAMETER                                 | SYMBOL                    | CONDITION                                                         | IS                               | MIN   | ТҮР   | MAX   | UNITS             |

|-------------------------------------------|---------------------------|-------------------------------------------------------------------|----------------------------------|-------|-------|-------|-------------------|

| Output Slew Rate                          |                           | 52 hex to 3FF hex code swifalling, $R_L = 10k\Omega$ , $C_L = 10$ |                                  |       | 40    |       | V/ms              |

| Output-Voltage Settling Time              |                           | 10% to 90% rising or falling                                      | to ±0.5 LSB                      |       | 65    |       | μs                |

| 1 11/10 NI 1                              |                           | Referred to FBA excludes                                          | f = 0.1Hz to<br>10Hz             |       | 80    |       |                   |

| Input Voltage Noise                       |                           | reference noise                                                   | f = 10Hz to<br>10kHz             |       | 200   |       | μV <sub>P-P</sub> |

|                                           |                           | OUTA/B shorted to AGND                                            | ·                                |       | 20    |       |                   |

| Output Short-Circuit Current              |                           | OUTA/B shorted to AV <sub>DD</sub>                                |                                  |       | 15    |       | mA                |

| Input-Output SWA Switch<br>Resistance     |                           | Between SWA and OUTA, HFCK enabled                                |                                  |       |       | 150   | Ω                 |

| SWA Switch Turn-On/Off Time               |                           | HFCK enabled                                                      |                                  |       | 100   |       | ns                |

| Power-On Time                             |                           | Excluding reference                                               |                                  |       | 18    |       | μs                |

| <b>EXTERNAL REFERENCE (REF)</b>           |                           |                                                                   |                                  |       |       |       |                   |

| Input Voltage Range                       |                           |                                                                   |                                  | AGND  |       | AVDD  | V                 |

| Input Resistance                          |                           | DAC on, internal REF and A                                        | DC off                           |       | 2.5   |       | MΩ                |

| DC Input Leakage Current                  |                           | Internal REF, DAC, and AD                                         | C off (Note 7)                   |       |       | 100   | nA                |

| INTERNAL VOLTAGE REFEREN                  | NCE (C <sub>REF</sub> = 4 | l.7μF)                                                            |                                  |       |       |       |                   |

|                                           |                           | $AV_{DD} \ge +1.8V, T_A = +25^{\circ}C$                           |                                  | 1.213 | 1.25  | 1.288 |                   |

| Reference Output Voltage                  | VREF                      | $AV_{DD} \ge +2.2V, T_A = +25^{\circ}C$                           |                                  | 1.987 | 2.048 | 2.109 | V                 |

|                                           |                           | $AV_{DD} \ge +2.7V, T_A = +25^{\circ}C$                           |                                  | 2.425 | 2.5   | 2.575 |                   |

| Output-Voltage Temperature<br>Coefficient | TC                        | (Note 7)                                                          |                                  |       | 15    |       | ppm/⁰C            |

|                                           | 1                         | REF shorted to AGND                                               |                                  |       | 18    |       | mA                |

| Output Short-Circuit Current              | REF shorted to AVDD       |                                                                   | REF shorted to AV <sub>DD</sub>  |       | 90    |       | μA                |

| Line Regulation                           |                           | $T_A = +25^{\circ}C$                                              |                                  |       | 25    |       | μV/V              |

|                                           |                           |                                                                   | ISOURCE = 0<br>to 500µA          |       |       | 1.2   |                   |

| _oad Regulation                           |                           | $T_A = +25^{\circ}C, V_{REF} = 1.25V$                             | I <sub>SINK</sub> = 0 to<br>50µA |       | 1.7   |       | - μV/μΑ           |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = +1.8V$  to +3.6V,  $V_{REF} = +1.25V$ , external reference,  $f_{CLK32K} = 32.768$ kHz (external clock),  $C_{REG} = 10\mu$ F,  $C_{CPOUT} = 10\mu$ F,  $10\mu$ F between CF+ and CF-,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 1)

| PARAMETER                                                  | SYMBOL                  | C                                                                  | ONDITIONS                                     | MIN | TYP   | МАХ                        | UNITS             |

|------------------------------------------------------------|-------------------------|--------------------------------------------------------------------|-----------------------------------------------|-----|-------|----------------------------|-------------------|

| Long-Term Stability                                        |                         | (Note 9)                                                           | (Note 9)                                      |     | 35    |                            | ppm/<br>1000hrs   |

|                                                            |                         | f = 0.1Hz to 10Hz                                                  | z, AV <sub>DD</sub> = 3V                      |     | 50    |                            |                   |

| Output Noise Voltage                                       |                         | f = 10Hz to $10kH$                                                 | łz, AV <sub>DD</sub> = 3V                     |     | 400   |                            | μV <sub>P-P</sub> |

| Turn-On Settling Time                                      |                         | Buffer only, settle                                                | e to 0.1% of final value                      |     | 100   |                            | μs                |

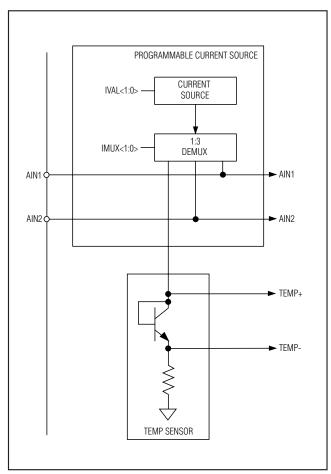

| TEMPERATURE SENSOR                                         |                         |                                                                    |                                               |     |       |                            |                   |

| Temperature Measurement<br>Resolution                      |                         | ADC resolution is                                                  | s 16-bit, 10sps                               |     | 0.11  |                            | °C/LSB            |

| Internal Temperature-Sensor                                |                         | $T_{A} = 0^{\circ}C \text{ to } +70^{\circ}$                       | °C                                            |     | ±0.5  |                            | °C                |

| Measurement Error                                          |                         | $T_A = -40^{\circ}C \text{ to } +8$                                | 35°C                                          |     | ±1    |                            | 10                |

| External Temperature-Sensor<br>Measurement Error (Note 10) |                         | $T_A = +32^{\circ}C \text{ to } + 40^{\circ}C$                     | 43°C                                          |     | ±0.50 |                            |                   |

|                                                            |                         | $T_A = +10^{\circ}C \text{ to } +$                                 | 50°C                                          |     | ±0.5  |                            | °C                |

|                                                            |                         | $T_{A} = 0^{\circ}C \text{ to } +70^{\circ}$                       |                                               |     |       |                            |                   |

|                                                            |                         | $T_A = -40^{\circ}C \text{ to } +8$                                | 35°C                                          |     | ±1    |                            |                   |

| Temperature Measurement Noise                              |                         |                                                                    |                                               |     | 0.18  |                            | °C <sub>RMS</sub> |

| Temperature Measurement<br>Power-Supply Rejection Ratio    |                         |                                                                    |                                               |     | 0.2   |                            | °C/V              |

| OP AMP (R <sub>L</sub> = $10k\Omega$ connected t           | o AV <sub>DD</sub> / 2) |                                                                    |                                               |     |       |                            |                   |

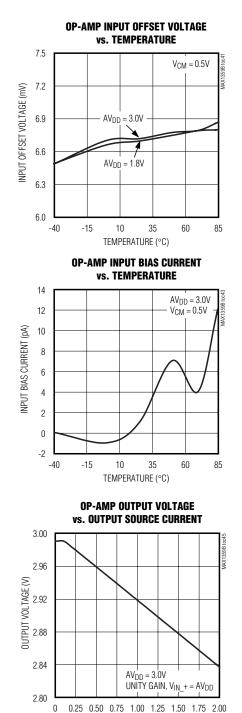

| Input Offset Voltage                                       | Vos                     | $V_{CM} = 0.5V$                                                    |                                               |     |       | ±15                        | mV                |

| Offset-Error Tempco                                        |                         |                                                                    |                                               |     | 3     |                            | µV/⁰C             |

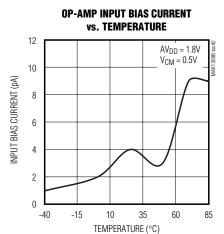

|                                                            |                         |                                                                    | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |     | 0.006 | ±1                         | nA                |

|                                                            |                         | IN1+, IN2+                                                         | $T_A = 0^{\circ}C$ to $+70^{\circ}C$          |     | 4     | ±300                       | <b>n</b> A        |

| Input Bias Current (Note 7)                                | Inua                    |                                                                    | $T_A = 0^{\circ}C$ to $+50^{\circ}C$          |     | 2     | ±200                       | рА                |

|                                                            | IBIAS                   |                                                                    | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |     | 0.025 | ±1                         | nA                |

|                                                            |                         | IN1-, IN2-                                                         | $T_A = 0^{\circ}C$ to $+70^{\circ}C$          |     | 20    | ±600                       | рА                |

|                                                            |                         |                                                                    | $T_A = 0^{\circ}C$ to $+50^{\circ}C$          |     |       | ±400                       | рА                |

| Input Offset Current                                       | IOS                     | $V_{IN1_{, IN2_{}}} = +0.3V \text{ to } (AV_{DD} - 0.3V) (Note 7)$ |                                               |     |       | ±1                         | nA                |

| Input Common-Mode Voltage<br>Range                         | CMVR                    |                                                                    |                                               | 0   |       | AV <sub>DD</sub> -<br>0.35 | V                 |

| Common Mode Dejection Datia                                |                         | $0 \le V_{CM} \le 75 mV$                                           |                                               |     | 60    |                            | dD                |

| Common-Mode Rejection Ratio                                | CMRR                    | $75\text{mV} < \text{V}_{CM} \le \text{AV}_{DD} - 0.35\text{V}$    |                                               | 60  | 75    |                            | dB                |

MAX1359B

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = +1.8V \text{ to } +3.6V, V_{REF} = +1.25V, \text{ external reference, } f_{CLK32K} = 32.768 \text{kHz}$  (external clock),  $C_{REG} = 10 \mu \text{F}$ ,  $C_{CPOUT} = 10 \mu \text{F}$ ,  $10 \mu \text{F}$  between CF+ and CF-,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                  | SYMBOL            | CONDITIONS                      |                                                                                                       | MIN                                  | ТҮР  | MAX   | UNITS   |    |

|--------------------------------------------|-------------------|---------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------|------|-------|---------|----|

| Power-Supply Rejection Ratio               | PSRR              | $AV_{DD} = +1.8V$ to $+3.6V$    | $AV_{DD} = +1.8V$ to $+3.6V$                                                                          |                                      | 100  |       | dB      |    |

| Large-Signal Voltage Gain                  | Avol              | $100mV \le V_{OUT} \le AV_{DE}$ | $100 \text{mV} \le \text{V}_{\text{OUT}} \le \text{AV}_{\text{DD}} - 100 \text{mV} \text{ (Note 11)}$ |                                      | 116  |       | dB      |    |

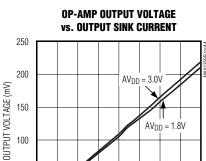

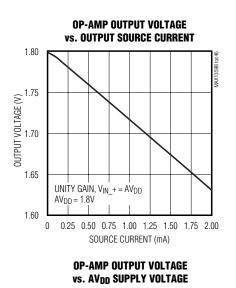

|                                            |                   |                                 | ISOURCE = 10µA                                                                                        |                                      |      | 0.005 |         |    |

|                                            |                   |                                 | ISOURCE = 50µA                                                                                        |                                      |      | 0.025 |         |    |

|                                            |                   | Sourcing                        | ISOURCE = 100µA                                                                                       |                                      |      | 0.05  | 1       |    |

|                                            |                   |                                 | ISOURCE = 500µA                                                                                       |                                      |      | 0.25  |         |    |

|                                            |                   |                                 | ISOURCE = 2mA                                                                                         |                                      |      | 0.5   | v       |    |

| Maximum Current Drive                      | ΔV <sub>OUT</sub> |                                 | I <sub>SINK</sub> = 10µA                                                                              |                                      |      | 0.005 | V       |    |

|                                            |                   |                                 | I <sub>SINK</sub> = 50µA                                                                              |                                      |      | 0.025 |         |    |

|                                            |                   | Sinking                         | I <sub>SINK</sub> = 100µA                                                                             |                                      |      | 0.05  |         |    |

|                                            |                   |                                 | I <sub>SINK</sub> = 500µA                                                                             |                                      |      | 0.25  |         |    |

|                                            |                   |                                 | I <sub>SINK</sub> = 2mA                                                                               |                                      |      | 0.5   |         |    |

| Gain Bandwidth Product                     | GBW               | Unity-gain configuration        | n, CL = 1nF                                                                                           |                                      | 80   |       | kHz     |    |

| Phase Margin                               |                   | Unity-gain configuration        | n, C <sub>L</sub> = 1nF (Note 11)                                                                     |                                      | 60   |       | Degrees |    |

| Output Slew Rate                           | SR                | C <sub>L</sub> = 200pF          |                                                                                                       |                                      | 0.04 |       | V/µs    |    |

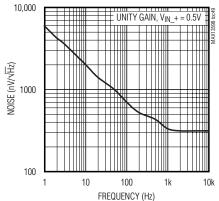

|                                            |                   | Unity-gain                      | f = 0.1Hz to 10Hz                                                                                     |                                      | 80   |       |         |    |

| Input Voltage Noise                        |                   | configuration                   | f = 10Hz to $10kHz$                                                                                   |                                      | 200  |       | μVp-p   |    |

| Outout Chart Circuit Current               |                   |                                 |                                                                                                       |                                      | 20   |       | mA      |    |

| Output Short-Circuit Current               |                   |                                 |                                                                                                       | 15                                   |      | mA    |         |    |

| Power-On Time                              |                   |                                 |                                                                                                       |                                      | 15   |       | μs      |    |

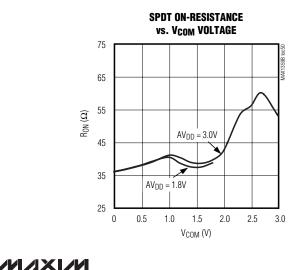

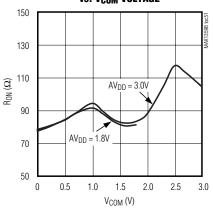

| SPDT SWITCHES (SNO_, SNC_                  | _, SCM_, HFCK     | enabled)                        |                                                                                                       |                                      |      |       |         |    |

|                                            |                   | $V_{SCM} = 0V$                  | $T_A = 0^{\circ}C \text{ to } +50^{\circ}C$                                                           |                                      |      | 45    |         |    |

| On-Resistance                              | R <sub>ON</sub>   | $V_{SCM} = 0.5V$                | $T_A = 0^{\circ}C$ to $+50^{\circ}C$                                                                  |                                      |      | 50    | Ω       |    |

|                                            |                   | $V_{SCM} = 0.5V$ to $AV_{DD}$   |                                                                                                       |                                      |      | 150   |         |    |

|                                            |                   | SNO_, SNC_ = +0.5V,             | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                                         |                                      |      | ±1    | nA      |    |

| SNO_, SNC_ Off-Leakage<br>Current (Note 7) | ISNO_(OFF)        | +1.5V; SCM_ = +1.5V,            | $T_A = 0^{\circ}C$ to $+70^{\circ}C$                                                                  |                                      |      | ±600  |         |    |

|                                            | ISNC_(OFF)        | +0.5V                           | $T_A = 0^{\circ}C$ to $+50^{\circ}C$                                                                  |                                      |      | ±400  | рА      |    |

|                                            |                   | SNO_, SNC_ = +0.5V,             | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                                         |                                      |      | ±2    |         |    |

| SCM_ Off-Leakage Current<br>(Note 7)       | ISCM_(OFF)        | +1.5V; SCM_ = +1.5V,            | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$                                                           |                                      |      | ±1.2  | nA      |    |

|                                            |                   | +0.5V                           | $T_A = 0^{\circ}C$ to $+50^{\circ}C$                                                                  |                                      |      | ±0.8  | 1       |    |

|                                            |                   | SNO_, SNC_ = +0.5V,             | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                                         |                                      |      | ±2    |         |    |

| SCM_ On-Leakage Current                    | Irrent            | Jurrent                         | +1.5V, or open; SCM_                                                                                  | $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |      |       | ±1.2    | nA |

| (Note 7)                                   | /                 | = +1.5V, +0.5V                  | $T_A = 0^{\circ}C$ to $+50^{\circ}C$                                                                  |                                      |      | ±0.8  | 1       |    |

| Input Voltage Range                        |                   |                                 |                                                                                                       | AGND                                 |      | AVDD  | V       |    |

| Turn-On/Off Time                           | ton/toff          | Break-before-make               |                                                                                                       |                                      | 100  |       | ns      |    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = +1.8V \text{ to } +3.6V, V_{REF} = +1.25V, \text{ external reference, } f_{CLK32K} = 32.768 \text{kHz}$  (external clock),  $C_{REG} = 10 \mu \text{F}$ ,  $C_{CPOUT} = 10 \mu \text{F}$ ,  $10 \mu \text{F}$  between CF+ and CF-,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                         | SYMBOL        | CONDITIONS                                                                                                       | MIN  | ТҮР  | МАХ              | UNITS |

|---------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------|------|------|------------------|-------|

|                                                   |               | SNO_, SNC_, or SCM_ = AV <sub>DD</sub> or AGND;<br>switch connected to enabled mux input                         |      | 5    |                  | pF    |

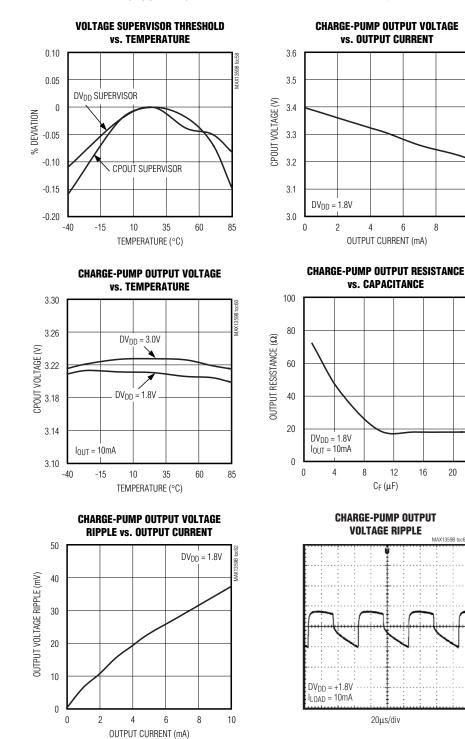

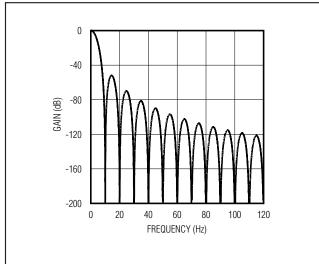

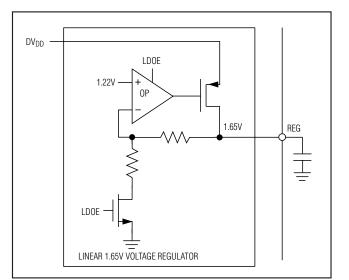

| CHARGE PUMP (10µF at REG a                        | nd 10µF exter | rnal capacitor between CF+ and CF-)                                                                              |      |      |                  |       |

| Maximum Output Current                            | IOUT          |                                                                                                                  | 10   |      |                  | mA    |

|                                                   |               | No load                                                                                                          | 3.2  | 3.3  | 3.6              | V     |

| Output Voltage                                    |               | I <sub>OUT</sub> = 10mA                                                                                          | 3.0  |      |                  | V     |

| Output Voltage Ripple                             |               | $10\mu$ F external capacitor between CPOUT<br>and DGND, $I_{OUT}$ = 10mA, excluding ESR of<br>external capacitor |      |      | 50               | mV    |

| Load Regulation                                   |               | I <sub>OUT</sub> = 10mA, excluding ESR of external capacitor                                                     |      | 15   | 20               | mV/mA |

| REG Input Voltage Range                           |               | Internal linear regulator disabled                                                                               | 1.6  |      | 1.8              | V     |

| REG Input Current                                 |               | Linear regulator off, charge pump off                                                                            |      | 3    |                  | nA    |

| CPOUT Input Voltage Range                         |               | Charge pump disabled                                                                                             | 1.8  |      | 3.6              | V     |

| CPOUT Input Leakage Current                       |               | Charge pump disabled                                                                                             |      | 2    |                  | nA    |

| SIGNAL-DETECT COMPARATO                           | R             |                                                                                                                  |      |      |                  |       |

|                                                   |               | TSEL[2:0] = 0 hex                                                                                                |      | 0    |                  |       |

|                                                   |               | TSEL[2:0] = 4 hex                                                                                                |      | 50   |                  |       |

| Differential Input-Detection<br>Threshold Voltage |               | TSEL[2:0] = 5 hex                                                                                                |      | 100  |                  | mV    |

| Theshold Voltage                                  |               | TSEL[2:0] = 6 hex                                                                                                |      | 150  |                  |       |

|                                                   |               | TSEL[2:0] = 7 hex                                                                                                |      | 200  |                  |       |

| Differential Input-Detection<br>Threshold Error   |               |                                                                                                                  |      | ±10  |                  | mV    |

| Common-Mode Input Voltage<br>Range                |               |                                                                                                                  | AGND |      | AV <sub>DD</sub> | V     |

| Turn-On Time                                      |               |                                                                                                                  |      | 50   |                  | μs    |

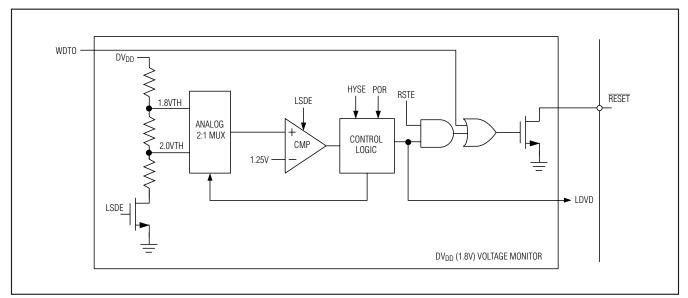

| VOLTAGE MONITORS                                  |               |                                                                                                                  |      |      |                  |       |

| DV <sub>DD</sub> Monitor Supply Voltage<br>Range  |               | For valid reset                                                                                                  | 1.0  |      | 3.6              | V     |

| Trip Threshold (DV <sub>DD</sub> Falling)         |               |                                                                                                                  | 1.80 | 1.85 | 1.95             | V     |

| DV <sub>DD</sub> Monitor Timeout Reset<br>Period  |               |                                                                                                                  |      | 1.5  |                  | S     |

| DV Monitor   hustowed                             |               | HYSE bit set to logic 1                                                                                          |      | 200  |                  |       |

| V <sub>DD</sub> Monitor Hysteresis                |               | HYSE bit set to logic 0                                                                                          |      | 35   |                  | mV    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = +1.8V \text{ to } +3.6V, V_{REF} = +1.25V, \text{ external reference, } f_{CLK32K} = 32.768 \text{kHz}$  (external clock),  $C_{REG} = 10 \mu \text{F}$ ,  $C_{CPOUT} = 10 \mu \text{F}$ ,  $10 \mu \text{F}$  between CF+ and CF-,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                | SYMBOL                         | CONDITIONS                                         | MIN                       | ТҮР    | MAX                       | UNITS |

|------------------------------------------|--------------------------------|----------------------------------------------------|---------------------------|--------|---------------------------|-------|

| DV <sub>DD</sub> Monitor Turn-On Time    |                                |                                                    |                           | 5      |                           | ms    |

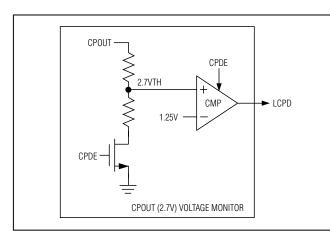

| CPOUT Monitor Supply Voltage<br>Range    |                                |                                                    | 1.0                       |        | 3.6                       | V     |

| CPOUT Monitor Trip Threshold             |                                |                                                    | 2.7                       | 2.8    | 2.9                       | V     |

| CPOUT Monitor Hysteresis                 |                                |                                                    |                           | 35     |                           | mV    |

| CPOUT Monitor Turn-On Time               |                                |                                                    |                           | 5      |                           | ms    |

| Internal Power-On Reset Voltage          |                                |                                                    |                           |        | 1.7                       | V     |

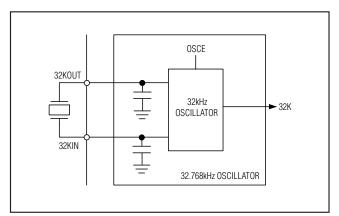

| 32kHz Oscillator (32KIN, 32KOU           | T)                             |                                                    |                           |        |                           |       |

| Clock Frequency                          |                                | $DV_{DD} = 2.7V$                                   |                           | 32.768 |                           | kHz   |

| Stability                                |                                | DV <sub>DD</sub> = 1.8V to 3.6V, excluding crystal |                           | 25     |                           | ppm   |

| Oscillator Startup Time                  |                                |                                                    |                           | 1500   |                           | ms    |

| Crystal Load Capacitance                 |                                |                                                    |                           | 6      |                           | рF    |

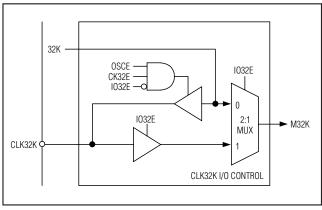

| LOW-FREQUENCY CLOCK INPU                 | JT/OUTPUT (                    | CLK32K)                                            | •                         |        |                           |       |

| Output Clock Frequency                   |                                |                                                    |                           | 32.768 |                           | kHz   |

| Absolute Input to Output Clock<br>Jitter |                                | Cycle to cycle                                     |                           | 5      |                           | ns    |

| Input to Output Rise/Fall Time           |                                | 10% to 90%, 30pF load                              |                           | 5      |                           | ns    |

| Input/Output Duty Cycle                  |                                |                                                    | 40                        |        | 60                        | %     |

| HIGH-FREQUENCY CLOCK OUT                 | PUT (CLK)                      |                                                    |                           |        |                           |       |

|                                          |                                | fout = ffll                                        | 4.8660                    | 4.9152 | 4.9644                    |       |

|                                          |                                | $f_{OUT} = f_{FLL} / 2$ , power-up default         | 2.4330                    | 2.4576 | 2.4822                    | MHz   |

| FLL Output Clock Frequency               |                                | $f_{OUT} = f_{FLL} / 4$                            | 1.2165                    | 1.2288 | 1.2411                    |       |

|                                          |                                | fout = f <sub>FLL</sub> / 8                        | 608.25                    | 614.4  | 620.54                    | kHz   |

|                                          |                                | Cycle to cycle, FLL off                            |                           | 0.15   |                           |       |

| Absolute Clock Jitter                    |                                | Cycle to cycle, FLL on                             |                           | 1      |                           | ns    |

| Rise and Fall Time                       | t <sub>R</sub> /t <sub>F</sub> | 10% to 90%, 30pF load                              |                           |        | 10                        | ns    |

| Duty Cycle                               |                                | $f_{OUT} = 4.9152 MHz$                             | 40                        |        | 60                        | 0/    |

| Duty Cycle                               |                                | f <sub>OUT</sub> = 2.4576MHz, 1.2288MHz, 614.4kHz  | 45                        |        | 55                        | %     |

| Uncalibrated CLK Frequency<br>Error      |                                | FLL calibration not performed                      |                           |        | ±35                       | %     |

| DIGITAL INPUTS (SCLK, DIN, C             | 5, UPIO_, CLI                  |                                                    |                           |        |                           |       |

| Input High Voltage                       | VIH                            |                                                    | 0.7 x<br>DV <sub>DD</sub> |        |                           | V     |

| Input Low Voltage                        | VIL                            |                                                    |                           |        | 0.3 x<br>DV <sub>DD</sub> | V     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = +1.8V \text{ to } +3.6V, V_{REF} = +1.25V, \text{ external reference, } f_{CLK32K} = 32.768 \text{kHz}$  (external clock),  $C_{REG} = 10 \mu\text{F}, C_{CPOUT} = 10 \mu\text{F}, 10 \mu\text{F}$  between CF+ and CF-,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                            | SYMBOL           | CONDITIONS                                                                                          | MIN                       | ТҮР   | МАХ                       | UNITS |

|--------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|---------------------------|-------|---------------------------|-------|

| UPIO_ Input High Voltage             |                  | DV <sub>DD</sub> supply voltage                                                                     | 0.7 x<br>DV <sub>DD</sub> |       |                           | V     |

|                                      |                  | CPOUT supply voltage                                                                                | 0.7 x<br>CPOUT            |       |                           | v     |

| UPIO_ Input Low Voltage              |                  | DV <sub>DD</sub> supply voltage                                                                     |                           |       | 0.3 x<br>DV <sub>DD</sub> | V     |

| OF TO_ Input Low Voltage             |                  | CPOUT supply voltage                                                                                |                           |       | 0.3 x<br>CPOUT            | v     |

| Input Hysteresis                     | V <sub>HYS</sub> | $DV_{DD} = 3.0V$                                                                                    |                           | 200   |                           | mV    |

| Input Current                        | lin              | $V_{IN} = DGND \text{ or } DV_{DD} \text{ (Note 7)}$                                                |                           | ±0.01 | ±100                      | nA    |

| Input Capacitance                    |                  | $V_{IN} = DGND \text{ or } DV_{DD}$                                                                 |                           | 10    |                           | рF    |

|                                      |                  | $V_{IN} = DV_{DD}$ or CPOUT, pullup enabled                                                         |                           | ±0.01 | 1                         |       |

| UPIO_ Input Current                  |                  | V <sub>IN</sub> = DV <sub>DD</sub> or CPOUT or 0V,<br>pullup disabled                               |                           |       | 1                         | μA    |

| UPIO_ Pullup Current                 |                  | $V_{IN} = 0V$ , pullup enabled, UPIO inputs are pulled up to $DV_{DD}$ or CPOUT with pullup enabled | 0.5                       | 2     | 5                         | μA    |

| DIGITAL OUTPUTS (DOUT, RESI          | T, UPIO_, C      | LK32K, INT, CLK)                                                                                    |                           |       |                           |       |

| Output Low Voltage                   | Vol              | I <sub>SINK</sub> = 1mA                                                                             |                           |       | 0.4                       | V     |

| Output High Voltage                  | V <sub>OH</sub>  | Isource = 500µA                                                                                     | 0.8 x<br>DV <sub>DD</sub> |       |                           | V     |

| DOUT Tri-State Leakage Current       | ١L               |                                                                                                     |                           | ±0.01 | ±1                        | μA    |

| DOUT Tri-State Output<br>Capacitance | Соит             |                                                                                                     |                           | 15    |                           | pF    |

| RESET Output Low Voltage             | VOL              | I <sub>SINK</sub> = 1mA                                                                             |                           |       | 0.4                       | V     |

| RESET Output Leakage Current         |                  | Open-drain output, RESET deasserted                                                                 |                           |       | 0.1                       | μΑ    |

| UPIO_ Output Low Voltage             | V <sub>OL</sub>  | $I_{SINK} = 1 \text{mA}, \text{UPIO}_\text{referenced to DV}_{DD}$                                  |                           |       | 0.4                       | V     |

| OFIO_Output Low Voltage              | VOL              | I <sub>SINK</sub> = 4mA, UPIO_ referenced to CPOUT                                                  |                           |       | 0.4                       | v     |

|                                      |                  | $I_{SOURCE} = 500\mu A$ , UPIO_ referenced to $DV_{DD}$                                             | 0.8 x<br>DV <sub>DD</sub> |       |                           |       |

| JPIO_Output High Voltage VOH         |                  | ISOURCE = 4mA, UPIO_ referenced to CPOUT                                                            | VCPOUT<br>- 0.4           |       |                           | V     |

| POWER REQUIREMENT                    | •                |                                                                                                     | •                         |       |                           |       |

| Analog Supply Voltage Range          | AV <sub>DD</sub> |                                                                                                     | 1.8                       |       | 3.6                       | V     |

| Digital Supply Voltage Range         | DVDD             |                                                                                                     | 1.8                       |       | 3.6                       | V     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = +1.8V$  to +3.6V,  $V_{REF} = +1.25V$ , external reference,  $f_{CLK32K} = 32.768$ kHz (external clock),  $C_{REG} = 10\mu$ F,  $C_{CPOUT} = 10\mu$ F,  $10\mu$ F between CF+ and CF-,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 1)

| PARAMETER                 | SYMBOL       | COND                                                                                | ITIONS                                        | MIN | TYP  | MAX  | UNITS |

|---------------------------|--------------|-------------------------------------------------------------------------------------|-----------------------------------------------|-----|------|------|-------|

| Total Supply Current      |              | Everything on,<br>charge pump<br>unloaded, max                                      | $AV_{DD} = DV_{DD} = 3.6V$                    |     | 1.36 | 2.0  |       |

|                           | IMAX         | internal temp-sensor<br>current, clock output<br>buffers unloaded,<br>ADC at 512sps | $AV_{DD} = DV_{DD} = 3.3V$                    |     | 1.15 | 1.7  | mA    |

|                           | INORMAL      | All on except charge<br>sensor, ADC at 512sp<br>enabled, clock output               | s, CLK output buffer                          |     | 1.17 | 1.3  |       |

|                           |              | T 4500 L 0500                                                                       | $AV_{DD} = DV_{DD} = 3.0V$                    |     | 5.18 | 6.5  |       |

| Clean Made Cupply Current | 1            | $T_A = -45^{\circ}C \text{ to } +85^{\circ}C$                                       | $AV_{DD} = DV_{DD} = 3.6V$                    |     | 6.15 | 9    |       |

| Sleep-Mode Supply Current | ISLEEP       | T 05%C                                                                              | $AV_{DD} = DV_{DD} = 3.0V$                    |     | 4.42 | 5.19 | μA    |

|                           |              | $T_A = +25^{\circ}C$                                                                | $AV_{DD} = DV_{DD} = 3.6V$                    |     | 5.56 | 8.3  |       |

| Shutdown Supply Current   |              | All off                                                                             | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |     |      | 4    |       |

|                           | ISHDN All of | HDN All off $T_A = +25^{\circ}C$                                                    |                                               | 1.6 |      | μA   |       |

|                           |              |                                                                                     |                                               |     |      |      |       |

**Note 1:** Devices are production tested at  $T_A = +25^{\circ}$ C and  $T_A = +85^{\circ}$ C. Specifications to  $T_A = -40^{\circ}$ C are guaranteed by design.

**Note 2:** Guaranteed by design or characterization.

**Note 3:** The offset and gain errors are corrected by self-calibration. The calibration process requires measurement to be made at the selected data rate. The calibration error is therefore in the order of peak-to-peak noise for the selected rate.

**Note 4:** Eliminate drift errors by recalibration at the new temperature.

Note 5: The gain error excludes reference error, offset error (unipolar), and zero error (bipolar).

**Note 6:** Gain-error drift does not include unipolar offset drift or bipolar zero-error drift. It is effectively the drift of the part if zero-scale error is removed.

**Note 7:** These specs are obtained from characterization during design or from initial product evaluation. Not production tested or guaranteed.

**Note 8:** OUTA/B = +0.5V or +1.5V, SWA/B = +1.5V or +0.5V,  $T_A = 0^{\circ}C \text{ to } +50^{\circ}C$ .

**Note 9:** Long-term stability is characterized using five to six parts. The bandgaps are turned on for 1000hrs at room temperature with the parts running continuously. Daily measurements are taken and any obvious outlying data points are discarded.

Note 10: All of the stated temperature accuracies assume that 1) the external diode characteristic is precisely known (i.e., ideal) and 2) the ADC reference voltage is exactly equal to 1.25V. Any variations to this known reference characteristic and voltage caused by temperature, loading, or power supply results in errors in the temperature measurement. The actual temperature calculation is performed externally by the microcontroller (μC).

Note 11: Values based on simulation results and are not production tested or guaranteed.

MAX1359B

|            |          | OUTPUT NOISE (µV <sub>RMS</sub> ) |          |          |  |  |  |  |  |

|------------|----------|-----------------------------------|----------|----------|--|--|--|--|--|

| RATE (sps) | GAIN = 1 | GAIN = 2                          | GAIN = 4 | GAIN = 8 |  |  |  |  |  |

| 10         | 1.820    | 3.286                             | 1.345    | 0.660    |  |  |  |  |  |

| 40         | 3.845    | 3.257                             | 1.928    | 0.630    |  |  |  |  |  |

| 50         | 3.065    | 2.317                             | 1.631    | 0.625    |  |  |  |  |  |

| 60         | 2.873    | 2.662                             | 1.519    | 0.728    |  |  |  |  |  |

| 200        | 4.525    | 2.910                             | 1.397    | 0.519    |  |  |  |  |  |

| 240        | 6.502    | 2.954                             | 1.596    | 0.629    |  |  |  |  |  |

| 400        | 5.300    | 80.068                            | 1.686    | 0.436    |  |  |  |  |  |

| 512        | 119.078  | 282.959                           | 281.056  | 28.470   |  |  |  |  |  |

#### Table 1. Output Noise (Notes 12, 13, and 14)

**Note 12:**  $V_{REF} = \pm 1.25V$ , bipolar mode,  $V_{IN} = 1.24912$ , PGA gain = 1,  $T_A = +85^{\circ}C$ .

**Note 13:**  $C_{IN} = 5pF$ , op-amp noise is considered to be the same as the switching noise. The increase of the op amp's noise contribution is due to large input swing (0 to 3.6V).

Note 14: Assume ±3 sigma peak-to-peak variation; noise-free resolution means no code flicker at given bits' LSB.

#### **Table 2. Peak-to-Peak Resolution**

|            | PEAK-TO-PEAK RESOLUTION (Bits) |          |          |          |  |  |  |  |

|------------|--------------------------------|----------|----------|----------|--|--|--|--|

| RATE (sps) | GAIN = 1                       | GAIN = 2 | GAIN = 4 | GAIN = 8 |  |  |  |  |

| 10         | 16.7                           | 14.8     | 15.1     | 15.1     |  |  |  |  |

| 40         | 15.6                           | 14.8     | 14.6     | 15.2     |  |  |  |  |

| 50         | 15.9                           | 15.3     | 14.8     | 15.2     |  |  |  |  |

| 60         | 16.0                           | 15.1     | 14.9     | 15.0     |  |  |  |  |

| 200        | 15.4                           | 15.0     | 15.0     | 15.5     |  |  |  |  |

| 240        | 14.8                           | 15.0     | 14.9     | 15.2     |  |  |  |  |

| 400        | 15.1                           | 10.2     | 14.8     | 15.7     |  |  |  |  |

| 512        | 10.6                           | 8.4      | 7.4      | 9.7      |  |  |  |  |

#### Table 3. Maximum External Source Impedance Without 16-Bit Gain Error

| PARAMETER                | EXTERNAL CAPACITANCE (pF) |    |     |     |      |      |  |  |  |  |

|--------------------------|---------------------------|----|-----|-----|------|------|--|--|--|--|

| PARAMETER                | 0 (Note 15)               | 50 | 100 | 500 | 1000 | 5000 |  |  |  |  |

| Resistance (k $\Omega$ ) | 350                       | 60 | 30  | 10  | 4    | 1    |  |  |  |  |

Note 15: 2pF parasitic capacitance is assumed, which represents pad and any other parasitic capacitance.

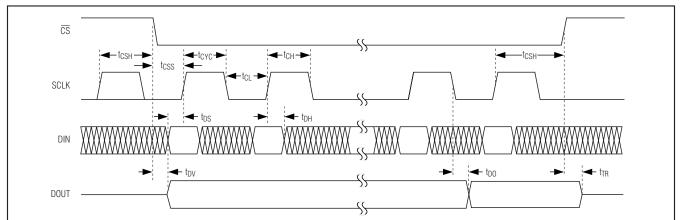

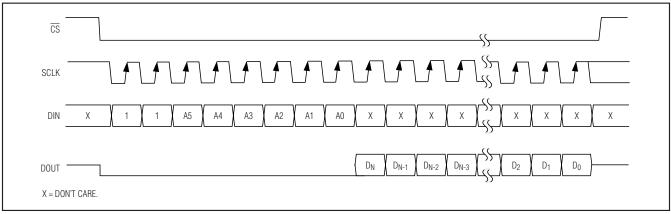

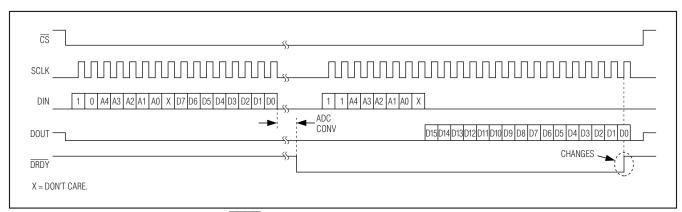

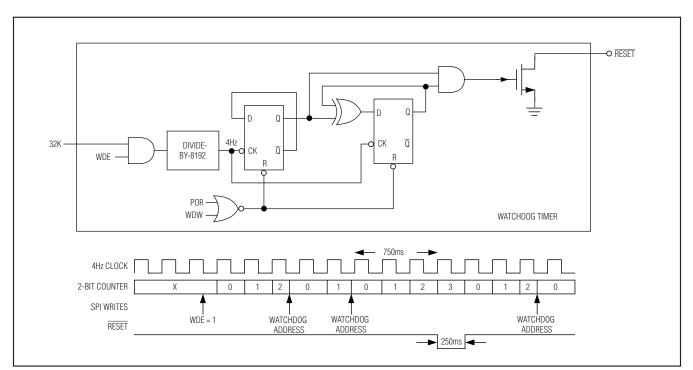

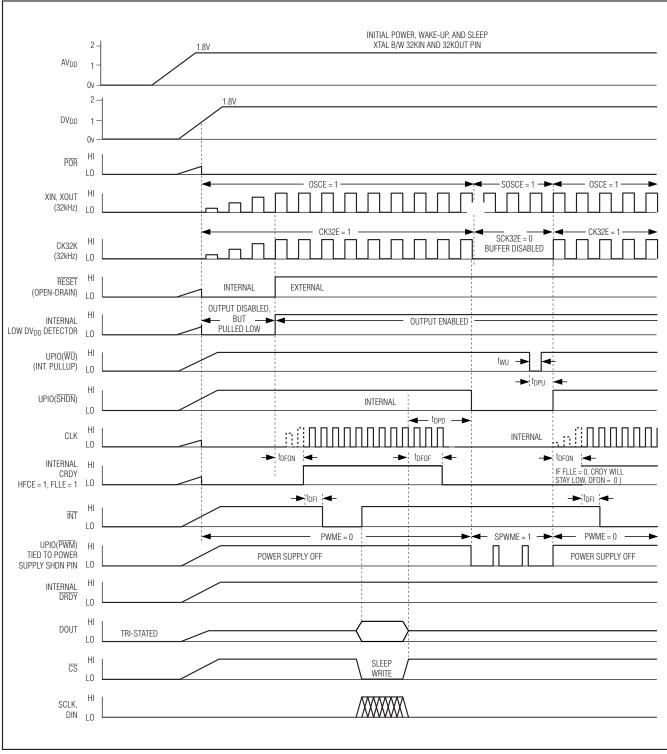

## TIMING CHARACTERISTICS (Figures 1 and 19)

$(AV_{DD} = DV_{DD} = +1.8V \text{ to } +3.6V, \text{ external } V_{REF} = +1.25V, CLK32K = 32.768kHz (external clock), C_{REG} = 10\mu\text{F}, C_{CPOUT} = 10\mu\text{F}, 10\mu\text{F} \text{ between } C\text{F} + \text{ and } C\text{F} -, T_A = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                | SYMBOL            | CONDITIONS                                                                                  | MIN | ТҮР  | MAX | UNITS |

|------------------------------------------|-------------------|---------------------------------------------------------------------------------------------|-----|------|-----|-------|

| SCLK Operating Frequency                 | fsclk             |                                                                                             | 0   |      | 10  | MHz   |

| SCLK Cycle Time                          | tcyc              |                                                                                             | 100 |      |     | ns    |

| SCLK Pulse-Width High                    | tсн               |                                                                                             | 40  |      |     | ns    |

| SCLK Pulse-Width Low                     | t <sub>CL</sub>   |                                                                                             | 40  |      |     | ns    |

| DIN to SCLK Setup                        | tDS               |                                                                                             | 30  |      |     | ns    |

| DIN to SCLK Hold                         | tDH               |                                                                                             | 0   |      |     | ns    |

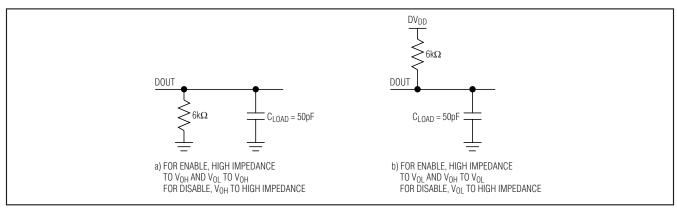

| SCLK Fall to DOUT Valid                  | t <sub>DO</sub>   | $C_L = 50 pF$ , Figure 2                                                                    |     |      | 40  | ns    |

| CS Fall to Output Enable                 | t <sub>DV</sub>   | $C_L = 50 pF$ , Figure 2                                                                    |     |      | 48  | ns    |

| CS Rise to DOUT Disable                  | t <sub>TR</sub>   | $C_L = 50 pF$ , Figure 2                                                                    |     |      | 48  | ns    |

| CS to SCLK Rise Setup                    | tcss              |                                                                                             | 20  |      |     | ns    |

| $\overline{\text{CS}}$ to SCLK Rise Hold | tCSH              |                                                                                             | 0   |      |     | ns    |

| DV <sub>DD</sub> Monitor Timeout Period  | <sup>t</sup> DSLP | (Note 16)                                                                                   |     | 1.5  |     | S     |

| Wake-Up (WU) Pulse Width                 | twu               | Minimum pulse width required to detect a wake-up event                                      |     | 1    |     | μs    |

| Shutdown Delay                           | t <sub>DPU</sub>  | The delay for SHDN to go high after a valid wake-up event                                   |     | 1    |     | μs    |

|                                          | +                 | The turn-on time for the high-frequency clock and FLL (FLLE = 1) (Note 17)                  |     |      | 10  | ms    |

| HFCK Turn-On Time                        | <sup>t</sup> DFON | If FLLE = 0, the turn-on time for the high-<br>frequency clock (Notes 7, 18)                |     |      | 10  | μs    |

| CRDY to INT Delay                        | t <sub>DFI</sub>  | The delay for CRDY to go low after the<br>HFCK clock output has been enabled<br>(Note 19)   |     | 7.82 |     | ms    |

| HFCK Disable Delay                       | <sup>t</sup> DFOF | The delay after a shutdown command has<br>asserted and before HFCK is disabled<br>(Note 20) |     | 1.95 |     | ms    |

| SHDN Assertion Delay                     | t <sub>DPD</sub>  | (Note 21)                                                                                   |     | 2.93 |     | ms    |

Note 16: The delay for the sleep voltage monitor output, RESET, to go high after V<sub>DD</sub> rises above the reset threshold. This is largely driven by the startup of the 32kHz oscillator.

**Note 17:** It is gated by an AND function with three inputs—the external RESET signal, the internal DV<sub>DD</sub> monitor output, and the external SHDN signal. The time delay is timed from the internal LOV<sub>DD</sub> going high or the external RESET going high, whichever happens later. HFCK always starts in the low state.

**Note 18:** If FLLE = 0, the internal signal CRDY is not generated by the FLL block and  $\overline{INT}$  or INT are deasserted.

Note 19: CRDY is used as an interrupt signal to inform the µC that the high-frequency clock has started. Only valid if FLLE = 1.

**Note 20:**  $t_{DFOF}$  gives the  $\mu$ C time to clean up and go into sleep-override mode properly.

**Note 21:** <sup>1</sup><sub>DPD</sub> is greater than the HFCK delay for the MAX1359B chip to clean up before losing power.

Figure 1. Detailed Serial-Interface Timing

Figure 2. DOUT Enable and Disable Time Load Circuits

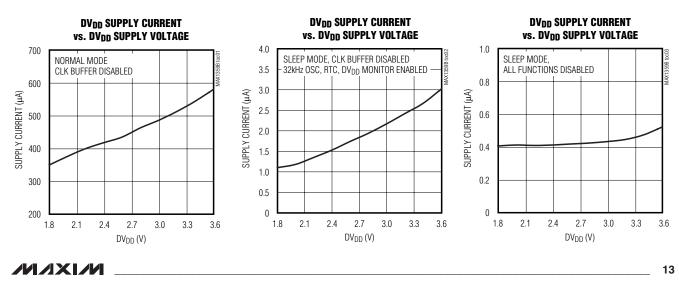

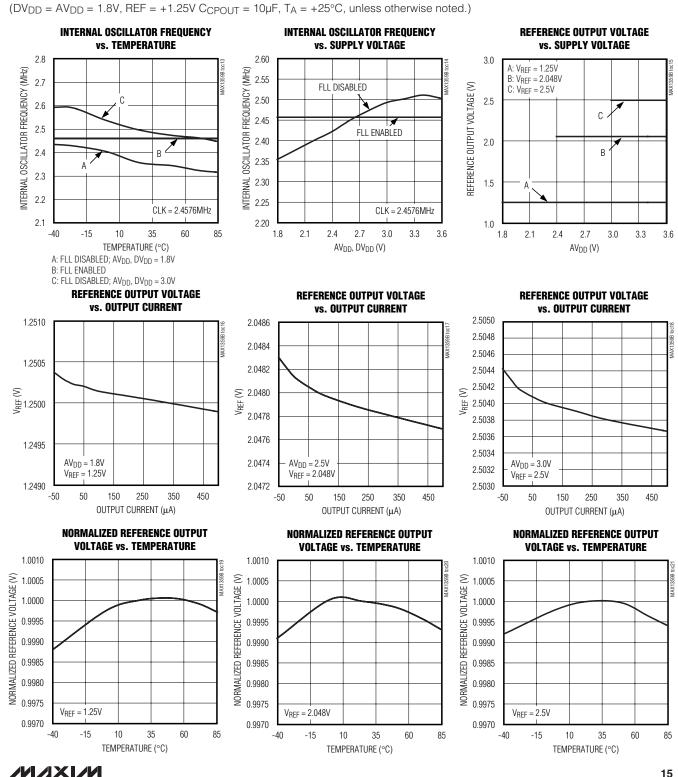

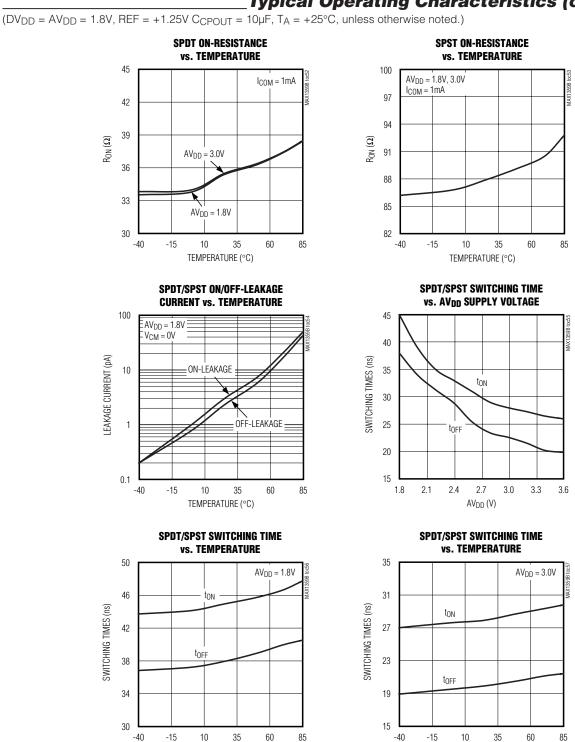

## **Typical Operating Characteristics**

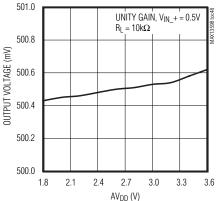

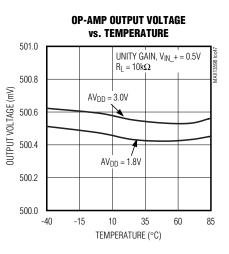

$(DV_{DD} = AV_{DD} = 1.8V, REF = +1.25V C_{CPOUT} = 10\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

(DV<sub>DD</sub> = AV<sub>DD</sub> = 1.8V, REF = +1.25V C<sub>CPOUT</sub> = 10 $\mu$ F, T<sub>A</sub> = +25°C, unless otherwise noted.)

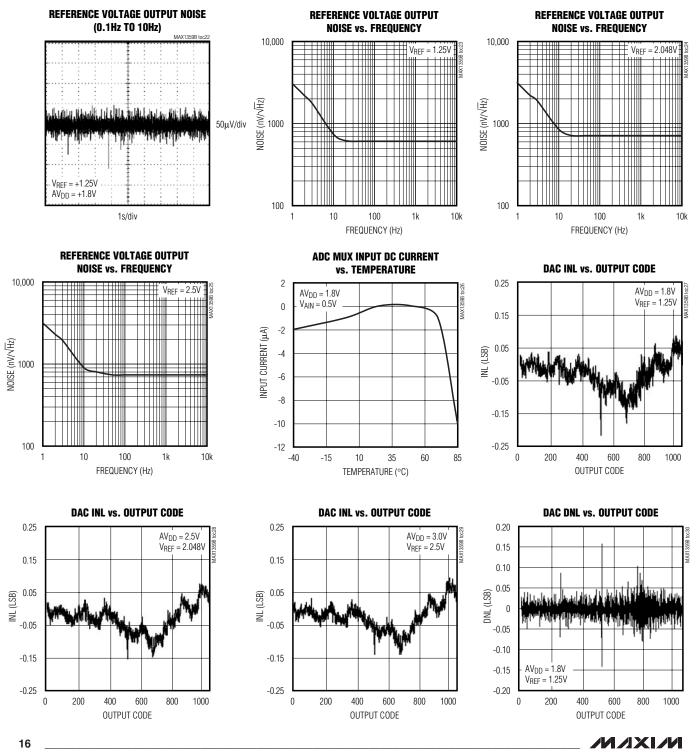

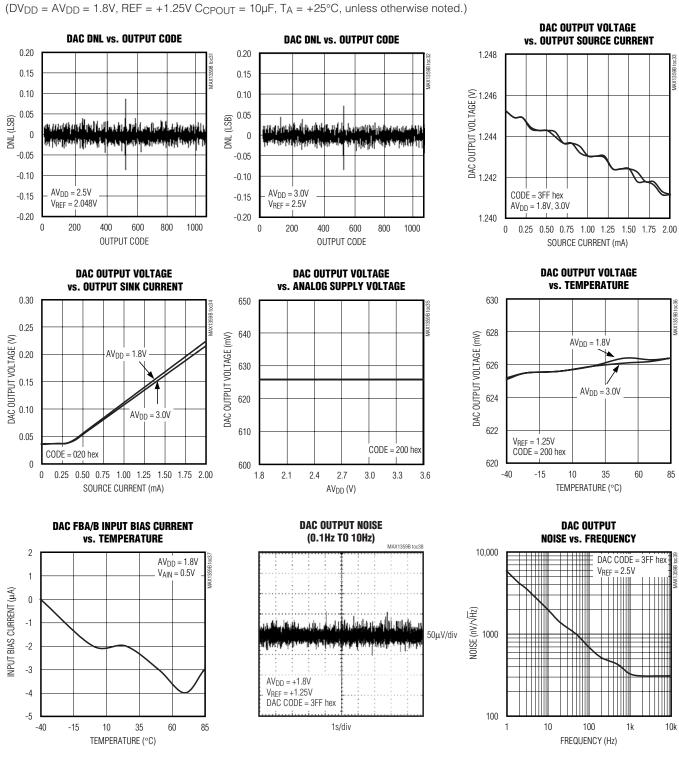

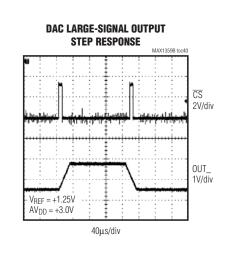

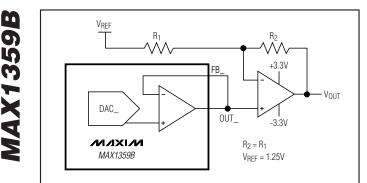

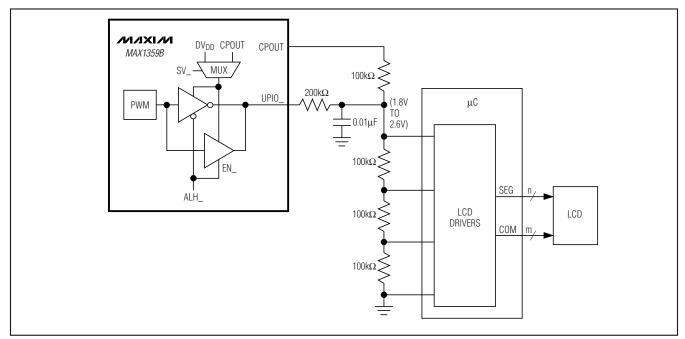

**Typical Operating Characteristics (continued)**