## M48T08 M48T08Y, M48T18

# 5 V, 64 Kbit (8 Kb x 8) TIMEKEEPER® SRAM

#### **Features**

- Integrated ultra low power SRAM, real-time clock, power-fail control circuit, and battery

- BYTEWIDE™ RAM-like clock access

- BCD coded year, month, day, date, hours, minutes, and seconds

- Typical clock accuracy of ±1 minute a month, at 25°C

- Automatic power-fail chip deselect and write protection

- Write protect

V<sub>PFD</sub> = Power-fail deselect voltage):

- M48T08:  $V_{CC} = 4.75$  to 5.5 V

$4.5 \text{ V} \leq \text{V}_{PFD} \leq 4.75 \text{ V}$

- M48T18/T08Y:  $V_{CC} = 4.5 \text{ to } 5.5 \text{ V}$

$4.2 \text{ V} \leq \text{V}_{PFD} \leq 4.5 \text{ V}$

- Software controlled clock calibration for high accuracy applications

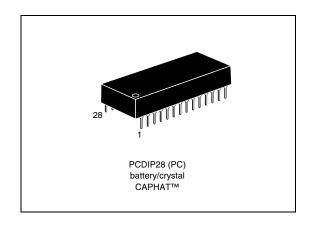

- Self-contained battery and crystal in the CAPHAT™ DIP package

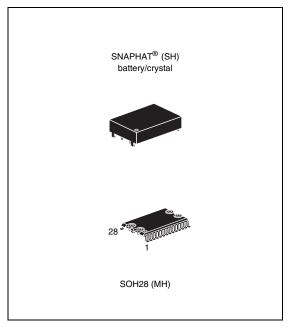

- Packaging includes a 28-lead SOIC and SNAPHAT® top (to be ordered separately)

- SOIC package provides direct connection for a snaphat top which contains the battery and crystal

- Pin and function compatible with DS1643 and JEDEC standard 8 K x 8 SRAMs

- RoHS compliant

- Lead-free second level interconnect

### 1 Description

The M48T08/18/08Y TIMEKEEPER<sup>®</sup> RAM is an 8 K x 8 non-volatile static RAM and real time clock which is pin and functional compatible with the DS1643. The monolithic chip is available in two special packages to provide a highly integrated battery backed-up memory and real time clock solution.

The M48T08/18/08Y is a non-volatile pin and function equivalent to any JEDEC standard 8 K  $\times$  8 SRAM. It also easily fits into many ROM, EPROM, and EEPROM sockets, providing the non-volatility of PROMs without any requirement for special WRITE timing or limitations on the number of WRITEs that can be performed.

The 28-pin, 600 mil DIP CAPHAT™ houses the M48T08/18/08Y silicon with a quartz crystal and a long-life lithium button cell in a single package.

The 28-pin, 330 mil SOIC provides sockets with gold plated contacts at both ends for direct connection to a separate SNAPHAT busing containing the battery and crystal. The unique design allows the SNAPHAT battery package to be mounted on top of the SOIC package after the completion of the surface mount process. Insertion of the SNAPHAT housing after reflow prevents potential battery and crystal damage due to the high temperatures required for device surface-mounting. The SNAPHAT housing is keyed to prevent reverse insertion.

The SOIC and battery/crystal packages are shipped separately in plastic anti-static tubes or in tape & reel form. For the 28-lead SOIC, the battery/crystal package (e.g., SNAPHAT) part number is "M4T28-BR12SH" or "M4T32-BR12SH" (see *Table 17 on page 28*).

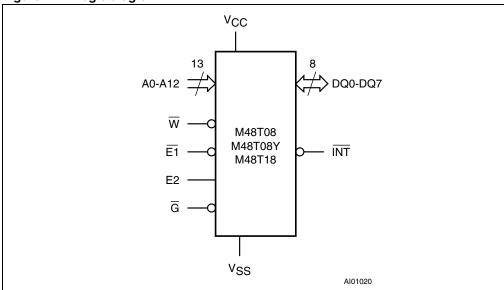

Figure 1. Logic diagram

Table 3. Read mode AC characteristics

| Symbol             | Parameter <sup>(1)</sup>                | -100/-1 | -100/-10 (T08Y) |     | -150/-15 (T08Y) |    |

|--------------------|-----------------------------------------|---------|-----------------|-----|-----------------|----|

|                    |                                         | Min     | Max             | Min | Max             |    |

| t <sub>AVAV</sub>  | READ cycle time                         | 100     |                 | 150 |                 | ns |

| t <sub>AVQV</sub>  | Address valid to output valid           |         | 100             |     | 150             | ns |

| t <sub>E1LQV</sub> | Chip enable 1 low to output valid       |         | 100             |     | 150             | ns |

| t <sub>E2HQV</sub> | Chip enable 2 high to output valid      |         | 100             |     | 150             | ns |

| t <sub>GLQV</sub>  | Output enable low to output valid       |         | 50              |     | 75              | ns |

| t <sub>E1LQX</sub> | Chip enable 1 low to output transition  | 10      |                 | 10  |                 | ns |

| t <sub>E2HQX</sub> | Chip enable 2 high to output transition | 10      |                 | 10  |                 | ns |

| t <sub>GLQX</sub>  | Output enable low to output transition  | 5       |                 | 5   |                 | ns |

| t <sub>E1HQZ</sub> | Chip enable 1 high to output Hi-Z       |         | 50              |     | 75              | ns |

| t <sub>E2LQZ</sub> | Chip enable 2 low to output Hi-Z        |         | 50              |     | 75              | ns |

| t <sub>GHQZ</sub>  | Output enable high to output Hi-Z       |         | 40              |     | 60              | ns |

| t <sub>AXQX</sub>  | Address transition to output transition | 5       |                 | 5   |                 | ns |

Note:

Valid for ambient operating temperature:  $T_A = 0$  to  $70^{\circ}C$ ;  $V_{CC} = 4.75$  to 5.5 V or 4.5 to 5.5 V (except where noted).

#### 2.2 Write mode

The M48T08/18/08Y is in the WRITE mode whenever  $\overline{W}$ ,  $\overline{E1}$ , and E2 are active. The start of a WRITE is referenced from the latter occurring falling edge of  $\overline{W}$  or  $\overline{E1}$ , or the rising edge of E2. A WRITE is terminated by the earlier rising edge of  $\overline{W}$  or  $\overline{E1}$ , or the falling edge of E3. The addresses must be held valid throughout the cycle. E1 or E3 must return high or E3 low for a minimum of E3 must return high or E3 low for a minimum of E3 must return high or E3 low for a minimum of E3 must return high or E3 low for a minimum of E3 must return high or E3 low for a minimum of E3 must return high or E3 low for a minimum of E3 must return high or E3 low for a minimum of E3 must return high or E3 must return high or E3 low for E3 must return high or E

Table 4. Write mode AC characteristics

|                     |                                          |         | M48T08/M48T18/T08Y |     |                 |    |  |

|---------------------|------------------------------------------|---------|--------------------|-----|-----------------|----|--|

| Symbol              | Parameter <sup>(1)</sup>                 | -100/-1 | -100/-10 (T08Y)    |     | -150/-15 (T08Y) |    |  |

|                     |                                          | Min     | Max                | Min | Max             |    |  |

| t <sub>AVAV</sub>   | WRITE cycle time                         | 100     |                    | 150 |                 | ns |  |

| t <sub>AVWL</sub>   | Address valid to WRITE enable low        | 0       |                    | 0   |                 | ns |  |

| t <sub>AVE1L</sub>  | Address valid to chip enable 1 low       | 0       |                    | 0   |                 | ns |  |

| t <sub>AVE2H</sub>  | Address valid to chip enable 2 high      | 0       |                    | 0   |                 | ns |  |

| t <sub>WLWH</sub>   | WRITE enable pulse width                 | 80      |                    | 100 |                 | ns |  |

| t <sub>E1LE1H</sub> | Chip enable 1 low to chip enable 1 high  | 80      |                    | 130 |                 | ns |  |

| t <sub>E2HE2L</sub> | Chip enable 2 high to chip enable 2 low  | 80      |                    | 130 |                 | ns |  |

| t <sub>WHAX</sub>   | WRITE enable high to address transition  | 10      |                    | 10  |                 | ns |  |

| t <sub>E1HAX</sub>  | Chip enable 1 high to address transition | 10      |                    | 10  |                 | ns |  |

| t <sub>E2LAX</sub>  | Chip enable 2 low to address transition  | 10      |                    | 10  |                 | ns |  |

| t <sub>DVWH</sub>   | Input valid to WRITE enable high         | 50      |                    | 70  |                 | ns |  |

| t <sub>DVE1H</sub>  | Input valid to chip enable 1 high        | 50      |                    | 70  |                 | ns |  |

| t <sub>DVE2L</sub>  | Input valid to chip enable 2 low         | 50      |                    | 70  |                 | ns |  |

| t <sub>WHDX</sub>   | WRITE enable high to input transition    | 5       |                    | 5   |                 | ns |  |

| t <sub>E1HDX</sub>  | Chip enable 1 high to input transition   | 5       |                    | 5   |                 | ns |  |

| t <sub>E2LDX</sub>  | Chip enable 2 low to input transition    | 5       |                    | 5   |                 | ns |  |

| t <sub>WLQZ</sub>   | WRITE enable low to output Hi-Z          |         | 50                 |     | 70              | ns |  |

| t <sub>AVWH</sub>   | Address valid to WRITE enable high       | 80      |                    | 130 |                 | ns |  |

| t <sub>AVE1H</sub>  | Address valid to chip enable 1 high      | 80      |                    | 130 |                 | ns |  |

| t <sub>AVE2L</sub>  | Address valid to chip enable 2 low       | 80      |                    | 130 |                 | ns |  |

| t <sub>WHQX</sub>   | WRITE enable high to output transition   | 10      |                    | 10  |                 | ns |  |

<sup>1.</sup> Valid for ambient operating temperature:  $T_A = 0$  to  $70^{\circ}$ C;  $V_{CC} = 4.75$  to 5.5 V or 4.5 to 5.5 V (except where noted).

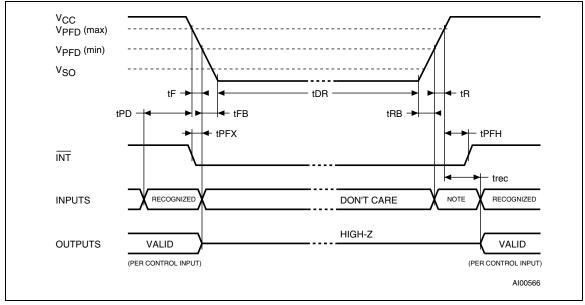

#### 2.3 Data retention mode

With valid  $V_{CC}$  applied, the M48T08/18/08Y operates as a conventional BYTEWIDE<sup>TM</sup> static RAM. Should the supply voltage decay, the RAM will automatically power-fail deselect, write protecting itself when  $V_{CC}$  falls within the  $V_{PFD}$  (max),  $V_{PFD}$  (min) window. All outputs become high impedance, and all inputs are treated as "Don't care."

Note:

A power failure during a WRITE cycle may corrupt data at the currently addressed location, but does not jeopardize the rest of the RAM's content. At voltages below  $V_{PFD}$  (min), the user can be assured the memory will be in a write protected state, provided the  $V_{CC}$  fall time is not less than  $t_F$  The M48T08/18/08Y may respond to transient noise spikes on  $V_{CC}$  that reach into the deselect window during the time the device is sampling  $V_{CC}$ . Therefore, decoupling of the power supply lines is recommended.

## 4 Maximum ratings

Stressing the device above the rating listed in the absolute maximum ratings table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

Table 6. Absolute maximum ratings

| Symbol                                | Parameter                                                 | Value     | Unit |

|---------------------------------------|-----------------------------------------------------------|-----------|------|

| T <sub>A</sub>                        | Ambient operating temperature                             | 0 to 70   | °C   |

| T <sub>STG</sub>                      | Storage temperature (V <sub>CC</sub> off, oscillator off) | -40 to 85 | °C   |

| T <sub>SLD</sub> <sup>(1)(2)(3)</sup> | Lead solder temperature for 10 seconds                    | 260       | °C   |

| V <sub>IO</sub>                       | Input or output voltages                                  | -0.3 to 7 | V    |

| V <sub>CC</sub>                       | Supply voltage                                            | -0.3 to 7 | V    |

| Io                                    | Output current                                            | 20        | mA   |

| P <sub>D</sub>                        | Power dissipation                                         | 1         | W    |

For DIP package: soldering temperature not to exceed 260°C for 10 seconds (total thermal budget not to exceed 150°C for longer than 30 seconds).

**Caution:** Negative undershoots below –0.3 V are not allowed on any pin while in the battery backup mode.

**Caution:** Do NOT wave solder SOIC to avoid damaging SNAPHAT<sup>®</sup> sockets.

For SO package, standard (SnPb) lead finish: reflow at peak temperature of 225°C (the time above 220°C must not exceed 20 seconds).

<sup>3.</sup> For SO package, lead-free (Pb-free) lead finish: reflow at peak temperature of 260°C (the time above 255°C must not exceed 30 seconds).

## 5 DC and AC parameters

This section summarizes the operating and measurement conditions, as well as the DC and AC characteristics of the device. The parameters in the following DC and AC characteristic tables are derived from tests performed under the measurement conditions listed in the relevant tables. Designers should check that the operating conditions in their projects match the measurement conditions when using the quoted parameters.

Table 7. Operating and AC measurement conditions

| Parameter                                       | M48T08      | M48T18/T08Y | Unit |

|-------------------------------------------------|-------------|-------------|------|

| Supply voltage (V <sub>CC</sub> )               | 4.75 to 5.5 | 4.5 to 5.5  | V    |

| Ambient operating temperature (T <sub>A</sub> ) | 0 to 70     | 0 to 70     | °C   |

| Load capacitance (C <sub>L</sub> )              | 100         | 100         | pF   |

| Input rise and fall times                       | ≤ 5         | ≤ 5         | ns   |

| Input pulse voltages                            | 0 to 3      | 0 to 3      | V    |

| Input and output timing ref. voltages           | 1.5         | 1.5         | V    |

Note: Output Hi-Z is defined as the point where data is no longer driven.

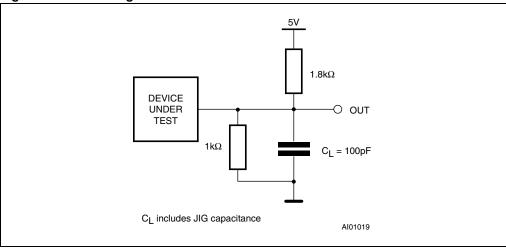

Figure 11. AC testing load circuit

Table 8. Capacitance

| Symbol              | Parameter <sup>(1)(2)</sup> | Min | Max | Unit |

|---------------------|-----------------------------|-----|-----|------|

| C <sub>IN</sub>     | Input capacitance           |     | 10  | pF   |

| C <sub>IO</sub> (3) | Input / output capacitance  |     | 10  | pF   |

- 1. Effective capacitance measured with power supply at 5 V; sampled only, not 100% tested.

- 2. At 25°C, f = 1 MHz.

- 3. Outputs deselected.

477

20/31

Table 9. DC characteristics

| 2 0 0.10.10.000                         |                                                                                                                                                                                      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Dovometov                               | Test condition(1)                                                                                                                                                                    | M48T08/M4 | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |

| Parameter                               | rest condition 7                                                                                                                                                                     | Min       | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ullit                                                 |

| Input leakage current                   | $0V \le V_{IN} \le V_{CC}$                                                                                                                                                           |           | ±1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | μΑ                                                    |

| Output leakage current                  | $0V \le V_{OUT} \le V_{CC}$                                                                                                                                                          |           | ±1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | μΑ                                                    |

| Supply current                          | Outputs open                                                                                                                                                                         |           | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | mA                                                    |

| Supply current (standby) TTL            | $\overline{E1} = V_{IH,} E2 = V_{IL}$                                                                                                                                                |           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mA                                                    |

| Supply current (standby) CMOS           | $\overline{E1} = V_{CC} - 0.2V,$<br>$E2 = V_{SS} + 0.2V$                                                                                                                             |           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mA                                                    |

| Input low voltage                       |                                                                                                                                                                                      | -0.3      | 0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                     |

| Input high voltage                      |                                                                                                                                                                                      | 2.2       | V <sub>CC</sub> + 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V                                                     |

| Output low voltage                      | I <sub>OL</sub> = 2.1 mA                                                                                                                                                             |           | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                     |

| Output low voltage (INT) <sup>(4)</sup> | I <sub>OL</sub> = 0.5 mA                                                                                                                                                             |           | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                     |

| Output high voltage                     | I <sub>OH</sub> = -1 mA                                                                                                                                                              | 2.4       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V                                                     |

|                                         | Output leakage current Supply current Supply current (standby) TTL Supply current (standby) CMOS Input low voltage Input high voltage Output low voltage Output low voltage (INT)(4) |           | $ \begin{array}{ c c c c c } \hline \textbf{Parameter} & \textbf{Test condition}^{(1)} & \hline \textbf{Min} \\ \hline & \textbf{Min} \\ \hline \\ \hline \textbf{Input leakage current} & 0 \textbf{V} \leq \textbf{V}_{IN} \leq \textbf{V}_{CC} \\ \hline \textbf{Output leakage current} & 0 \textbf{V} \leq \textbf{V}_{OUT} \leq \textbf{V}_{CC} \\ \hline \textbf{Supply current} & \textbf{Outputs open} \\ \hline \textbf{Supply current (standby) TTL} & \overline{\textbf{E1}} = \textbf{V}_{IH}, \ \textbf{E2} = \textbf{V}_{IL} \\ \hline \textbf{Supply current (standby) CMOS} & \overline{\textbf{E1}} = \textbf{V}_{CC} - 0.2 \textbf{V}, \\ \hline \textbf{E2} = \textbf{V}_{SS} + 0.2 \textbf{V} \\ \hline \textbf{Input low voltage} & -0.3 \\ \hline \textbf{Input high voltage} & 2.2 \\ \hline \textbf{Output low voltage} & \textbf{I}_{OL} = 2.1 \ \text{mA} \\ \hline \textbf{Output low voltage} & \overline{\textbf{IOL}} = 0.5 \ \text{mA} \\ \hline \end{array} $ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

- 1. Valid for ambient operating temperature:  $T_A = 0$  to  $70^{\circ}C$ ;  $V_{CC} = 4.75$  to 5.5 V or 4.5 to 5.5 V (except where noted).

- 2. Outputs deselected.

- 3. Measured with control bits set as follows: R = '1'; W, ST, FT = '0.'

- 4. The INT pin is open drain.

Figure 12. Power down/up mode AC waveforms

Note:

Inputs may or may not be recognized at this time. Caution should be taken to keep  $\overline{E1}$  high or E2 low as  $V_{CC}$  rises past  $V_{PFD}$  (min). Some systems may perform inadvertent WRITE cycles after  $V_{CC}$  rises above  $V_{PFD}$  (min) but before normal system operations begin. Even though a power on reset is being applied to the processor, a reset condition may not occur until after the system clock is running.

5/

Table 10. Power down/up AC characteristics

| Symbol                        | Parameter <sup>(1)</sup>                                                   | Min | Max | Unit |

|-------------------------------|----------------------------------------------------------------------------|-----|-----|------|

| t <sub>PD</sub>               | E1 or W at V <sub>IH</sub> or E2 at V <sub>IL</sub> before power-down      | 0   |     | μs   |

| t <sub>F</sub> <sup>(2)</sup> | $V_{PFD}$ (max) to $V_{PFD}$ (min) $V_{CC}$ fall time                      | 300 |     | μs   |

| t <sub>FB</sub> (3)           | V <sub>PFD</sub> (min) to V <sub>SS</sub> V <sub>CC</sub> fall time        | 10  |     | μs   |

| t <sub>R</sub>                | V <sub>PFD</sub> (min) to V <sub>PFD</sub> (max) V <sub>CC</sub> rise time | 0   |     | μs   |

| t <sub>RB</sub>               | V <sub>SS</sub> to V <sub>PFD</sub> (min) V <sub>CC</sub> rise time        | 1   |     | μs   |

| t <sub>rec</sub>              | E1 or W at V <sub>IH</sub> or E2 at V <sub>IL</sub> before power-up        | 1   |     | ms   |

| t <sub>PFX</sub>              | INT low to auto deselect                                                   | 10  | 40  | μs   |

| t <sub>PFH</sub>              | V <sub>PFD</sub> (max) to $\overline{\text{INT}}$ high                     |     | 120 | μs   |

Valid for ambient operating temperature: T<sub>A</sub> = 0 to 70°C; V<sub>CC</sub> = 4.75 to 5.5 V or 4.5 to 5.5 V (except where noted).

Table 11. Power down/up trip points DC characteristics

| Symbol           | Parameter <sup>(1)(2)</sup>                  |             | Min               | Тур | Max  | Unit  |

|------------------|----------------------------------------------|-------------|-------------------|-----|------|-------|

| V                | V <sub>PED</sub> Power-fail deselect voltage |             | 4.5               | 4.6 | 4.75 | V     |

| V <sub>PFD</sub> | M48T18/T08Y                                  | M48T18/T08Y | 4.2               | 4.3 | 4.5  | V     |

| V <sub>SO</sub>  | Battery backup switchover voltage            |             |                   | 3.0 |      | V     |

| t <sub>DR</sub>  | Expected data retention time                 |             | 10 <sup>(3)</sup> |     |      | Years |

<sup>1.</sup> All voltages referenced to  $V_{SS}$ .

<sup>2.</sup>  $V_{PFD}$  (max) to  $V_{PFD}$  (min) fall time of less than  $t_F$  may result in deselection/write protection not occurring until 200  $\mu s$  after  $V_{CC}$  passes  $V_{PFD}$  (min).

<sup>3.</sup>  $V_{PFD}$  (min) to  $V_{SS}$  fall time of less than  $t_{FB}$  may cause corruption of RAM data.

<sup>2.</sup> Valid for ambient operating temperature:  $T_A = 0$  to  $70^{\circ}C$ ;  $V_{CC} = 4.75$  to 5.5 V or 4.5 to 5.5 V (except where noted).

<sup>3.</sup> At 55°C,  $V_{CC}$  = 0 V;  $t_{DR}$  = 8.5 years (typ) at 70°C. Requires use of M4T32-BR12SH SNAPHAT® top when using the SOH28 package.

## 6 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

A2 A

A1 L

B1 B B C C

B1 C C

PCDIP

Figure 13. PCDIP28 – 28-pin plastic DIP, battery CAPHAT™, package outline

Note: Drawing is not to scale.

Table 12. PCDIP28 – 28-pin plastic DIP, battery CAPHAT™, package mech. data

| Symb   |     | mm    |       |     | inches |       |

|--------|-----|-------|-------|-----|--------|-------|

| Syllib | Тур | Min   | Max   | Тур | Min    | Max   |

| Α      |     | 8.89  | 9.65  |     | 0.350  | 0.380 |

| A1     |     | 0.38  | 0.76  |     | 0.015  | 0.030 |

| A2     |     | 8.38  | 8.89  |     | 0.330  | 0.350 |

| В      |     | 0.38  | 0.53  |     | 0.015  | 0.021 |

| B1     |     | 1.14  | 1.78  |     | 0.045  | 0.070 |

| С      |     | 0.20  | 0.31  |     | 0.008  | 0.012 |

| D      |     | 39.37 | 39.88 |     | 1.550  | 1.570 |

| Е      |     | 17.83 | 18.34 |     | 0.702  | 0.722 |

| e1     |     | 2.29  | 2.79  |     | 0.090  | 0.110 |

| e3     |     | 29.72 | 36.32 |     | 1.170  | 1.430 |

| eA     |     | 15.24 | 16.00 |     | 0.600  | 0.630 |

| L      |     | 3.05  | 3.81  |     | 0.120  | 0.150 |

| N      |     | 28    |       |     | 28     |       |

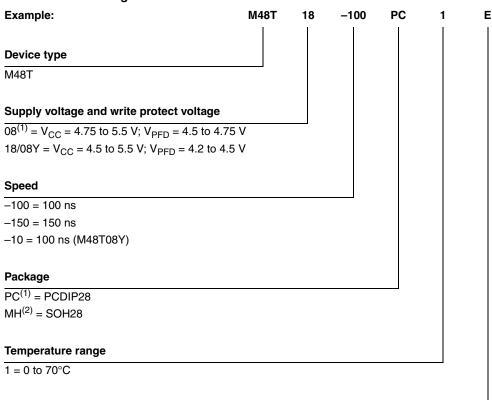

## 7 Part numbering

Table 16. Ordering information scheme

# Shipping method For SOH28:

blank = Tubes (not for new design - use E)

E = ECOPACK® package, tubes

F = ECOPACK® package, tape & reel

TR = Tape & reel (not for new design - use F)

#### For PCDIP28:

blank = ECOPACK® package, tubes

- 1. The M48T08/18 part is offered with the PCDIP28 (e.g., CAPHAT™) package only.

- The SOIC package (SOH28) requires the SNAPHAT<sup>®</sup> battery/crystal package which is ordered separately

under the part number "M4TXX-BR12SH" in plastic tube or "M4TXX-BR12SHTR" in tape & reel form (see

Table 17). The M48T08Y part is offered in the SOH28 (SNAPHAT) package only.

#### Caution:

Do not place the SNAPHAT<sup>®</sup> battery package "M4TXX-BR12SH" in conductive foam as it will drain the lithium button-cell battery.

For other options, or for more information on any aspect of this device, please contact the ST sales office nearest you.

57/