### LM139A/LM139QML Low Power Low Offset Voltage Quad Comparators

### **General Description**

The LM139 series consists of four independent precision voltage comparators with an offset voltage specification as low as 2 mV max for all four comparators. These were designed specifically to operate from a single power supply over a wide range of voltages. Operation from split power supplies is also possible and the low power supply current drain is independent of the magnitude of the power supply voltage. These comparators also have a unique characteristic in that the input common-mode voltage range includes ground, even though operated from a single power supply voltage.

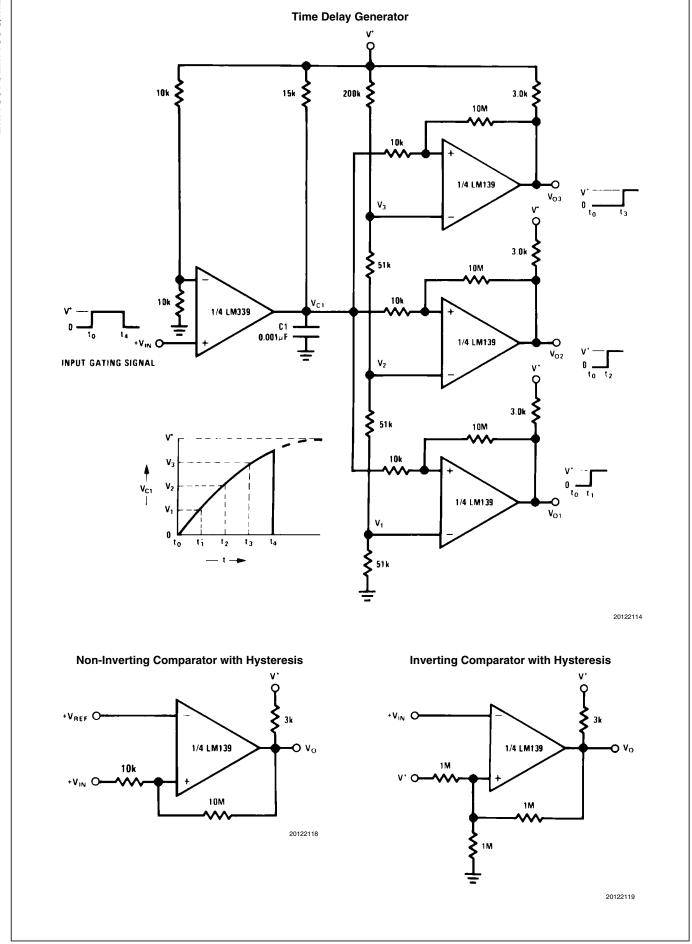

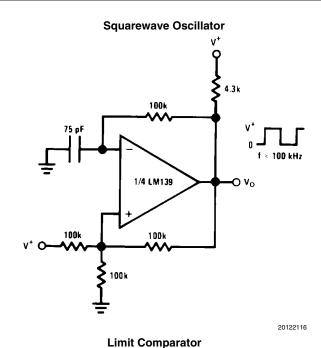

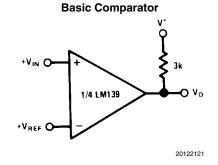

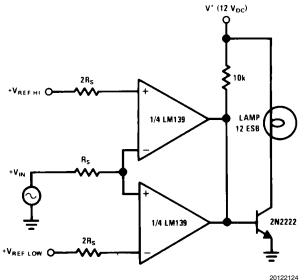

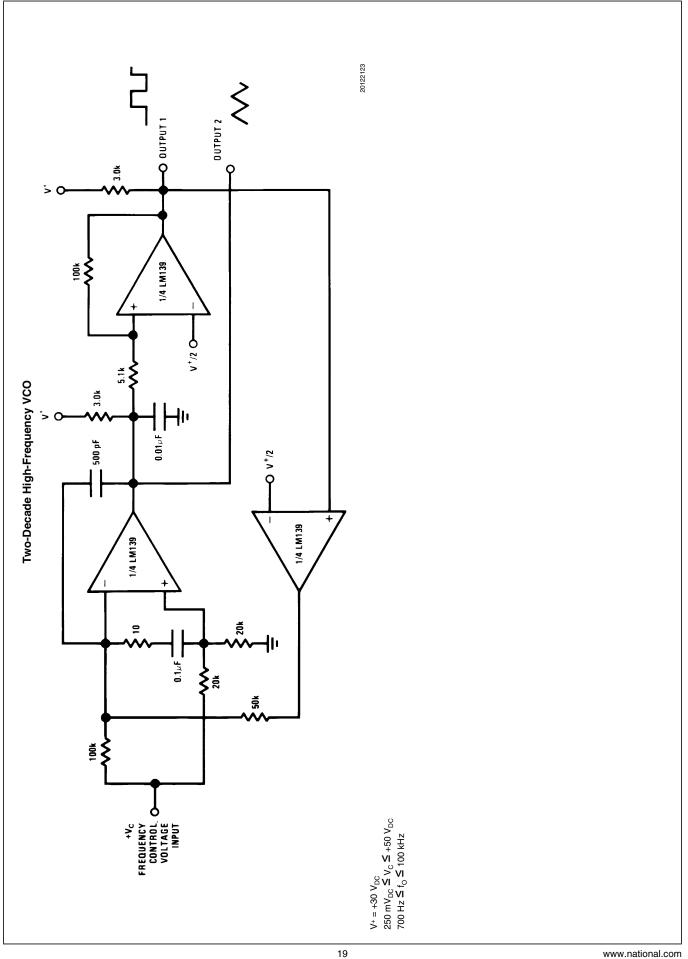

Application areas include limit comparators, simple analog to digital converters; pulse, squarewave and time delay generators; wide range VCO; MOS clock timers; multivibrators and high voltage digital logic gates. The LM139 series was designed to directly interface with TTL and CMOS. When operated from both plus and minus power supplies, they will directly interface with MOS logic—where the low power drain of the LM139/LM139A is a distinct advantage over standard comparators.

### **Features**

Available with Radiation Guarantee

Total Ionizing DoseELDRS Free100 krad(Si)100 krad(Si)

Wide supply voltage range

LM139/139A Series 2 to 36  $V_{DC}$  or  $\pm 1$  to  $\pm 18$   $V_{DC}$

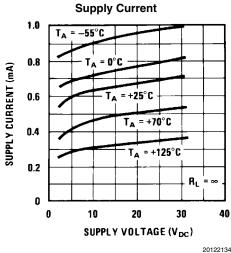

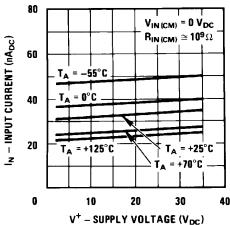

Very low supply current drain (0.8 mA) — independent of supply voltage

Low input biasing current:

Low input offset current:

±5 nA

Offset voltage:

±1 mV

■ Input common-mode voltage range includes GND

Differential input voltage range equal to the power supply voltage

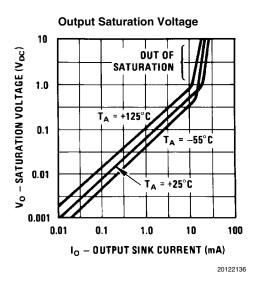

■ Low output saturation voltage: 250 mV at 4 mA

Output voltage compatible with TTL, DTL, ECL, MOS and CMOS logic systems

### **Advantages**

- High precision comparators

- Reduced V<sub>OS</sub> drift over temperature

- Eliminates need for dual supplies

- Allows sensing near GND

- Compatible with all forms of logic

- Power drain suitable for battery operation

### **Ordering Information**

| NS Part Number         | SMD Part Number                 | NS Package<br>Number | Package Description                  |

|------------------------|---------------------------------|----------------------|--------------------------------------|

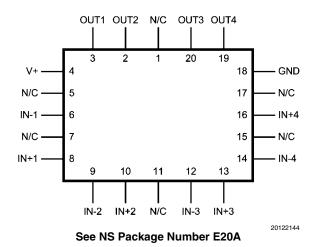

| LM139E/883             |                                 | E20A                 | 20 terminal Leadless Chip<br>Carrier |

| LM139J/883             |                                 | J14A                 | 14LD CERDIP                          |

| LM139W/883             |                                 | W14B                 | 14LD CERPACK                         |

| LM139WG/883            |                                 | WG14A                | 14LD Ceramic SOIC                    |

| LM139AE-SMD            | 5962-87739012A                  | E20A                 | 20 terminal Leadless Chip<br>Carrier |

| LM139AJ-SMD            | 5962-8773901CA                  | J14A                 | 14LD CERDIP                          |

| LM139AW-SMD            | 5962-8773901DA                  | W14B                 | 14LD CERPACK                         |

| LM139AWG-SMD           | 5962-8773901XA                  | WG14A                | 14LD Ceramic SOIC                    |

| LM139AE/883            |                                 | E20A                 | 20 terminal Leadless Chip<br>Carrier |

| LM139AJ-QMLV           | 5962-9673801VCA                 | J14A                 | 14LD CERDIP                          |

| LM139AJ/883            |                                 | J14A                 | 14LD CERDIP                          |

| LM139AJLQMLV (Note 10) | 5962L9673801VCA<br>50 krad(Si)  | J14A                 | 14LD CERDIP                          |

| LM139AJRQMLV (Note 10) | 5962R9673801VCA<br>100 krad(Si) | J14A                 | 14LD CERDIP                          |

| NS Part Number           | SMD Part Number | NS Package<br>Number | Package Description |

|--------------------------|-----------------|----------------------|---------------------|

| LM139AJRLQMLV (Note 14)  | 5962R9673802VCA | J14A                 | 14LD CERDIP         |

| ELDRS Free               | 100 krad(Si)    |                      |                     |

| LM139AW-QMLV             | 5962-9673801VDA | W14B                 | 14LD CERPACK        |

| LM139AW/883              |                 | W14B                 | 14LD CERPACK        |

| LM139AWG-QMLV            | 5962-9673801VXA | WG14A                | 14LD Ceramic SOIC   |

| LM139AWG/883             |                 | WG14A                | 14LD Ceramic SOIC   |

| LM139AWGLQMLV (Note 10)  | 5962L9673801VXA | WG14A                | 14LD Ceramic SOIC   |

|                          | 50 krad(Si)     |                      |                     |

| LM139AWGRQMLV (Note 10)  | 5962R9673801VXA | WG14A                | 14LD Ceramic SOIC   |

|                          | 100 krad(Si)    |                      |                     |

| LM139AWGRLQMLV (Note 14) | 5962R9673802VXA | WG14A                | 14LD Ceramic SOIC   |

| ELDRS Free               | 100 krad(Si)    |                      |                     |

| LM139AWLQMLV (Note 10)   | 5962L9673801VDA | W14B                 | 14LD CERPACK        |

|                          | 50 krad(Si)     |                      |                     |

| LM139AWRQMLV (Note 10)   | 5962R9673801VDA | W14B                 | 14LD CERPACK        |

|                          | 100 krad(Si)    |                      |                     |

| LM139AWRLQMLV (Note 14)  | 5962R9673802VDA | W14B                 | 14LD CERPACK        |

| ELDRS Free               | 100 krad(Si)    |                      |                     |

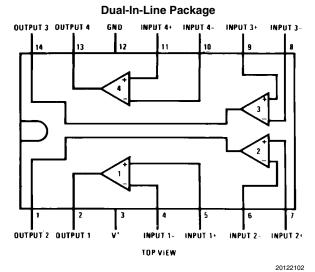

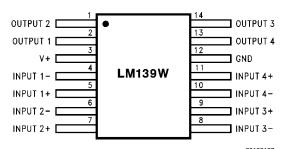

### **Connection Diagrams**

See NS Package NumberJ14A

See NS Package Number W14B, WG14A

### **Absolute Maximum Ratings** (Note 1)

| Supply Voltage, V+ Differential Input Voltage (Note 7) Input Voltage Input Current (V <sub>IN</sub> < -0.3 V <sub>DC</sub> ) (Note 3) Power Dissipation (Notes 4, 13) LCC CERDIP CERPACK SOIC Sink Current (approx) (Note 11) Output Short-Circuit to GND, (Note 2) Storage Temperature Range | LM139 / LM139A $36 V_{DC} \text{ or } \pm 18 V_{DC}$ $36 V_{DC}$ $-0.3 V_{DC} \text{ to } +36 V_{DC}$ $50 \text{ mA}$ $1250 \text{ mW}$ $1200 \text{ mW}$ $680 \text{ mW}$ $680 \text{ mW}$ $20 \text{ mA}$ $Continuous$ $-65°C ≤ T_A ≤ +150°C$ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maximum Junction Temperature (T <sub>J</sub> ) Lead Temperature (Soldering, 10 seconds) Operating Temperature Range                                                                                                                                                                           | $-03 \text{ C} \le 1_A \le +150 \text{ C}$<br>+150°C<br>300°C<br>$-55^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$                                                                                                                         |

| Thermal Resistance  θ <sub>JA</sub> LCC (Still Air)  LCC (500LF / Min Air flow)  CERDIP (Still Air)  CERDIP (500LF / Min Air flow)                                                                                                                                                            | 100°C/W<br>73°C/W<br>103°C/W<br>65°C/W                                                                                                                                                                                                          |

| CERPACK (Still Air) CERPACK (500LF / Min Air flow) SOIC (Still Air) SOIC (500LF / Min Air flow) $\theta_{JC}$                                                                                                                                                                                 | 183°C/W<br>120°C/W<br>183°C/W<br>120°C/W                                                                                                                                                                                                        |

| LCC CERDIP CERPACK SOIC Package Weight (typical)                                                                                                                                                                                                                                              | 28°C/W<br>23°C/W<br>23°C/W<br>23°C/W                                                                                                                                                                                                            |

| LCC CERDIP CERPACK SOIC ESD rating (Note 12)                                                                                                                                                                                                                                                  | 470mg<br>2,190mg<br>460mg<br>410mg<br>600V                                                                                                                                                                                                      |

### **Recommended Operating Conditions**

| Supply Voltage                      | $5.0 \text{ V}_{DC}$ to +30 $\text{V}_{DC}$ |

|-------------------------------------|---------------------------------------------|

| Ambient Operating Temperature Range | -55°C ≤ T <sub>Δ</sub> ≤ +125°C             |

### **Quality Conformance Inspection**

Mil-Std-883, Method 5005 — Group A

| Subgroup | Description         | Temp (°C) |

|----------|---------------------|-----------|

| 1        | Static tests at     | 25        |

| 2        | Static tests at     | 125       |

| 3        | Static tests at     | -55       |

| 4        | Dynamic tests at    | 25        |

| 5        | Dynamic tests at    | 125       |

| 6        | Dynamic tests at    | -55       |

| 7        | Functional tests at | 25        |

| 8A       | Functional tests at | 125       |

| 8B       | Functional tests at | -55       |

| 9        | Switching tests at  | 25        |

| 10       | Switching tests at  | 125       |

| 11       | Switching tests at  | -55       |

### **LM139 883 Electrical Characteristics**

### **DC Parameters**

The following conditions apply, unless otherwise specified. +V = 5V,  $V_{CM} = 0V$

| Symbol              | Parameters                   | Conditions                                                        | Notes    | Min  | Max           | Unit | Sub-<br>groups |

|---------------------|------------------------------|-------------------------------------------------------------------|----------|------|---------------|------|----------------|

| I <sub>cc</sub>     | Supply Current               | R <sub>L</sub> = Infinity                                         |          |      | 2.0           | mA   | 1, 2, 3        |

|                     | Supply Current               | +V = 30V, R <sub>L</sub> = Infinity                               |          |      | 2.0           | mA   | 1, 2, 3        |

| V <sub>IO</sub>     | Input Offset Voltage         | +V = 30V                                                          |          | -5.0 | 5.0           | mV   | 1              |

|                     |                              |                                                                   |          | -9.0 | 9.0           | mV   | 2, 3           |

|                     |                              | +V = 30V, V <sub>CM</sub> = 28.5V                                 |          | -5.0 | 5.0           | mV   | 1              |

|                     |                              | +V = 30V, V <sub>CM</sub> = 28.0V                                 |          | -9.0 | 9.0           | mV   | 2, 3           |

|                     |                              |                                                                   |          | -5.0 | 5.0           | mV   | 1              |

| CMBB                |                              |                                                                   |          | -9.0 | 9.0           | mV   | 2, 3           |

| CMRR                | Common Mode Rejection Ratio  | $+V = 30V$ , $V_{CM} = 0V$ to 28.5V                               |          | 60   |               | dB   | 1              |

| PSRR                | Power Supply Rejection Ratio | +V = 5V to 30V                                                    |          | 60   |               | dB   | 1              |

| ± I <sub>Bias</sub> | Input Bias Current           | V <sub>O</sub> = 1.5V                                             | (Note 5) | -100 | -1.0          | nA   | 1              |

|                     |                              |                                                                   | (Note 5) | -300 | -1.0          | nA   | 2, 3           |

| I <sub>IO</sub>     | Input Offset Current         | V <sub>O</sub> = 1.5V                                             |          | -25  | 25            | nA   | 1              |

|                     |                              |                                                                   |          | -100 | 100           | nA   | 2, 3           |

| I <sub>CEX</sub>    | Output Leakage Current       | $+V = 30V, V_O = 30V$                                             |          |      | 1.0           | μA   | 1, 2, 3        |

| I <sub>Sink</sub>   | Output Sink Current          | V <sub>O</sub> = 1.5V                                             |          | 6.0  |               | mA   | 1              |

| V <sub>Sat</sub>    | Saturation Voltage           | I <sub>Sink</sub> = 4mA                                           |          |      | 400           | mV   | 1              |

|                     |                              |                                                                   |          |      | 700           | mV   | 2, 3           |

| $A_V$               | Voltage Gain                 | $+V = 15V, R_L \ge 15\Omega K, V_I = 1V \text{ to}$<br>11V        |          | 50   |               | V/mV | 1              |

| V <sub>CM</sub>     | Common Mode Voltage Range    | +V = 30V                                                          | (Note 8) | 0    | V+ -<br>(1.5) | V    | 1              |

|                     |                              |                                                                   | (Note 8) | 0    | V+ -<br>(2.0) | V    | 2, 3           |

| V <sub>Diff</sub>   | Differential Input Voltage   | +V = 30V, -V = 0V, +V <sub>1</sub> = 36V, -V <sub>1</sub><br>= 0V | (Note 9) |      | 500           | nA   | 1, 2, 3        |

|                     |                              | +V = 30V, -V = 0V, +V <sub>1</sub> = 0V, -V <sub>1</sub> = 36V    | (Note 9) |      | 500           | nA   | 1, 2, 3        |

### **AC Parameters**

The following conditions apply, unless otherwise specified. +V = 5V

| Symbol           | Parameters    | Conditions             | Notes | Min | Max | Unit | Sub-<br>groups |

|------------------|---------------|------------------------|-------|-----|-----|------|----------------|

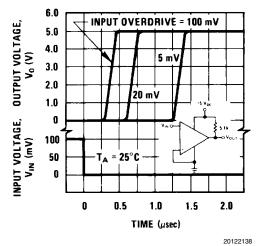

| t <sub>RLH</sub> | Response Time | $V_{OD} = 5mV$         |       |     | 5.0 | μS   | 9              |

|                  |               | V <sub>OD</sub> = 50mV |       |     | 0.8 | μS   | 9              |

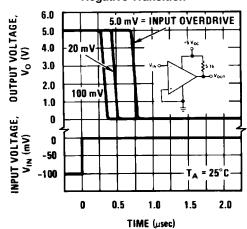

| t <sub>RHL</sub> | Response Time | V <sub>OD</sub> = 5mV  |       |     | 2.5 | μS   | 9              |

|                  |               | V <sub>OD</sub> = 50mV |       |     | 0.8 | μS   | 9              |

### LM139A SMD 5962-8773901 Electrical Characteristics

### **DC Parameters**

The following conditions apply, unless otherwise specified. +V = 5V,  $V_{CM} = 0V$

| Symbol           | Parameter                    | Conditions                                             | Notes    | Min  | Max           | Unit | Sub-<br>groups |

|------------------|------------------------------|--------------------------------------------------------|----------|------|---------------|------|----------------|

| I <sub>CC</sub>  | Supply Current               | +V = 30V, R <sub>L</sub> = Infinity                    |          |      | 3.0           | mA   | 1, 2, 3        |

|                  |                              | R <sub>L</sub> = Infinity                              |          |      | 3.0           | mA   | 1, 2, 3        |

| I <sub>CEX</sub> | Output Leakage Current       | $+V = 30V, -V_1 = 0V, +V_1 \ge 1V, V_0$                |          |      | 0.5           | μΑ   | 1              |

|                  |                              | = 30V                                                  |          |      | 1.0           | μΑ   | 2, 3           |

| V <sub>Sat</sub> | Saturation Voltage           | $I_{Sink} \le 4mA, -V_1 = 1V, +V_1 = 0V$               |          |      | 400           | mV   | 1              |

|                  |                              |                                                        |          |      | 700           | mV   | 2, 3           |

| $I_{Sink}$       | Output Sink Current          | $V_0 \ge 1.5V, -V_1 = 1V, +V_1 = 0V$                   |          | 6.0  |               | mA   | 1              |

| V <sub>IO</sub>  | Input Offset Voltage         | $R_S = 0\Omega$                                        |          | -2.0 | 2.0           | mV   | 1              |

|                  |                              |                                                        |          | -4.0 | 4.0           | mV   | 2, 3           |

|                  |                              | $+V = 30V, R_S = 0\Omega$                              |          | -2.0 | 2.0           | mV   | 1              |

|                  |                              |                                                        |          | -4.0 | 4.0           | mV   | 2, 3           |

|                  |                              | $+V = 30V, V_{CM} = 28V, V_{O} = 1.4V,$                |          | -2.0 | 2.0           | mV   | 1              |

|                  |                              | $R_S = 0\Omega$                                        |          | -4.0 | 4.0           | mV   | 2, 3           |

| ±I <sub>IB</sub> | Input Bias Current           | V <sub>O</sub> = 1.5V                                  | (Note 5) | -100 | -1.0          | nA   | 1              |

|                  |                              |                                                        | (Note 5) | -300 | -1.0          | nA   | 2, 3           |

| $I_{IO}$         | Input Offset Current         | $V_O = 1.5V$                                           |          | -25  | 25            | nA   | 1              |

|                  |                              |                                                        |          | -100 | 100           | nA   | 2, 3           |

| PSRR             | Power Supply Rejection Ratio | +V = 5V to 30V                                         |          | 70   |               | dB   | 1, 2, 3        |

| CMRR             | Common Mode Rejection Ratio  | $+V = 30V$ , $V_{CM} = 0V$ to 28V, $R_L$<br>$\ge 15KΩ$ |          | 70   |               | dB   | 1, 2, 3        |

| A <sub>V</sub>   | Voltage Gain                 | +V = 15V, $R_L$ ≥ 15KΩ, $V_O$ = 1V to                  |          | 50   |               | V/mV | 4              |

|                  |                              | 11V                                                    |          | 25   |               | V/mV | 5, 6           |

| V <sub>CM</sub>  | Common Mode Voltage Range    | +V = 30V                                               | (Note 8) | 0    | V+ -<br>(2.0) | V    | 1, 2, 3        |

|                  |                              | +V = 5V                                                | (Note 8) | 0    | V+ -<br>(2.0) | V    | 1, 2, 3        |

### **AC Parameters**

The following conditions apply, unless otherwise specified. +V = 5V

| Symbol           | Parameters    | Conditions                                       | Notes | Min | Max | Unit | Sub-<br>groups |

|------------------|---------------|--------------------------------------------------|-------|-----|-----|------|----------------|

| t <sub>RLH</sub> | Response Time | $V_{OD} = 5 \text{mV}, R_L = 5.1 \text{K}\Omega$ |       |     | 5.0 | μS   | 9              |

| t <sub>RHL</sub> | Response Time | $V_{OD} = 5 \text{mV}, R_L = 5.1 \text{K}\Omega$ |       |     | 2.5 | μS   | 9              |

### LM139A 883, QMLV & RH, SMD 5962–9673801 Electrical Characteristics

DC Parameters (Notes 10, 14)

The following conditions apply, unless otherwise specified. +V = 5V,  $V_{CM} = 0V$

| Symbol              | Parameters                   | Conditions                                                       | Notes           | Min  | Max           | Unit | Sub-<br>groups |

|---------------------|------------------------------|------------------------------------------------------------------|-----------------|------|---------------|------|----------------|

| I <sub>CC</sub>     | Supply Current               | R <sub>L</sub> = Infinity                                        |                 |      | 2.0           | mA   | 1, 2, 3        |

|                     |                              | +V = 30V, R <sub>L</sub> = Infinity                              |                 |      | 2.0           | mA   | 1, 2, 3        |

| I <sub>CEX</sub>    | Output Leakage Current       | +V = 30V, V <sub>O</sub> = 30V                                   |                 |      | 1.0           | μA   | 1, 2, 3        |

| V <sub>Sat</sub>    | Saturation Voltage           | I <sub>Sink</sub> = 4mA                                          |                 |      | 400           | mV   | 1              |

|                     |                              |                                                                  |                 |      | 700           | mV   | 2, 3           |

| I <sub>Sink</sub>   | Output Sink Current          | V <sub>O</sub> = 1.5V                                            |                 | 6.0  |               | mA   | 1              |

| V <sub>IO</sub>     | Input Offset Voltage         |                                                                  |                 | -2.0 | 2.0           | mV   | 1              |

|                     |                              |                                                                  |                 | -4.0 | 4.0           | mV   | 2, 3           |

|                     |                              | +V = 30V                                                         |                 | -2.0 | 2.0           | mV   | 1              |

|                     |                              |                                                                  |                 | -4.0 | 4.0           | mV   | 2, 3           |

|                     |                              | +V = 30V, V <sub>CM</sub> = 28.5V,<br>V <sub>O</sub> = 1.5V      |                 | -2.0 | 2.0           | mV   | 1              |

|                     |                              | +V = 30V, V <sub>CM</sub> = 28.0V,<br>V <sub>O</sub> = 1.5V      |                 | -4.0 | 4.0           | mV   | 2, 3           |

| ± I <sub>Bias</sub> | Input Bias Current           | V <sub>O</sub> = 1.5V                                            | (Note 5)        | -100 | -1.0          | nA   | 1              |

|                     |                              |                                                                  | (Note 5)        | -300 | -1.0          | nA   | 2, 3           |

| I <sub>IO</sub>     | Input Offset Current         | V <sub>O</sub> = 1.5V                                            |                 | -25  | 25            | nA   | 1              |

|                     |                              |                                                                  |                 | -100 | 100           | nA   | 2, 3           |

| PSRR                | Power Supply Rejection Ratio | +V = 5V to 30V                                                   |                 | 60   |               | dB   | 1              |

| CMRR                | Common Mode Rejection Ratio  | $+V = 30V$ , $V_{CM} = 0V$ to 28.5V                              |                 | 60   |               | dB   | 1              |

| A <sub>V</sub>      | Voltage Gain                 | +V = 15V, R <sub>L</sub> ≥ 15KΩ, V <sub>O</sub> = 1V to 11V      |                 | 50   |               | V/mV | 1              |

| V <sub>CM</sub>     | Common Mode Voltage Range    | +V = 30V                                                         | (Notes 6,<br>8) | 0    | V+ -<br>(1.5) | V    | 1              |

|                     |                              |                                                                  | (Notes 6,<br>8) | 0    | V+ -<br>(2.0) | V    | 2, 3           |

| V <sub>Diff</sub>   | Differential Input Voltage   | +V = 30V, -V =0V, +V <sub>1</sub> = 36V, -V <sub>1</sub><br>= 0V | (Note 9)        |      | 500           | nA   | 1, 2, 3        |

|                     |                              | +V = 30V, -V = 0V, +V <sub>1</sub> = 0V, -V <sub>1</sub> = 36V   | (Note 9)        |      | 500           | nA   | 1, 2, 3        |

### AC Parameters (Notes 10, 14)

The following conditions apply, unless otherwise specified. +V = 5V

| Symbol           | Parameters    | Conditions             | Notes | Min | Max | Unit | Sub-<br>groups |

|------------------|---------------|------------------------|-------|-----|-----|------|----------------|

| t <sub>RLH</sub> | Response Time | V <sub>OD</sub> = 5mV  |       |     | 5.0 | μS   | 4              |

|                  |               | V <sub>OD</sub> = 50mV |       |     | 0.8 | μS   | 4              |

| t <sub>RHL</sub> | Response Time | V <sub>OD</sub> = 5mV  |       |     | 2.5 | μS   | 4              |

|                  |               | V <sub>OD</sub> = 50mV |       |     | 0.8 | μS   | 4              |

### **DC Parameters** Delta Values

The following conditions apply, unless otherwise specified. +V = 5V,  $V_{CM} = 0V$

Deltas required for S-Level, MLS (as specified on Internal Processing instructions (IPI)), and QMLV product at Group B, Subgroup 5

| Symbol              | Parameters           | Conditions            | Notes    | Min  | Max | Unit | Sub-<br>groups |

|---------------------|----------------------|-----------------------|----------|------|-----|------|----------------|

| V <sub>IO</sub>     | Input Offset Voltage |                       |          | -1.0 | 1.0 | mV   | 1              |

| ± I <sub>Bias</sub> | Input Bias Current   | V <sub>O</sub> = 1.5V | (Note 5) | -15  | 15  | nA   | 1              |

| I <sub>IO</sub>     | Input Offset Current | V <sub>O</sub> = 1.5V |          | -10  | +10 | nA   | 1              |

### DC/AC Parameters 50K Post Rad Limits +25°C (Note 10)

The following conditions apply, unless otherwise specified.

DC:  $+V = 5V, V_{CM} = 0V$

AC: +V = 5V

| Symbol              | Parameters           | Conditions                                    | Notes    | Min  | Max  | Unit | Sub-<br>groups |

|---------------------|----------------------|-----------------------------------------------|----------|------|------|------|----------------|

| V <sub>IO</sub>     | Input Offset Voltage | $+V = 5V, V_{CM} = 0$                         |          | -2.5 | 2.5  | mV   | 1              |

|                     |                      | $+V = 30V, V_{CM} = 0$                        |          | -2.5 | 2.5  | mV   | 1              |

| _                   |                      | $+V = 30V, V_{CM} = 28.5V,$<br>$V_{O} = 1.5V$ |          | -2.5 | 2.5  | mV   | 1              |

| ± I <sub>Bias</sub> | Input Bias Current   | V <sub>O</sub> = 1.5V                         | (Note 5) | -110 | -1.0 | nA   | 1              |

| t <sub>RLH</sub>    | Response Time        | V <sub>OD</sub> (Overdrive) = 50mV            |          |      | 0.9  | μS   | 4              |

### DC/AC Parameters 100K Post Rad Limits +25°C (Notes 10, 14)

The following conditions apply, unless otherwise specified.

DC: +V = 5V,  $V_{CM} = 0V$

AC: +V = 5V

| Symbol              | Parameters           | Conditions                                                  | Notes    | Min  | Max  | Unit | Sub-<br>groups |

|---------------------|----------------------|-------------------------------------------------------------|----------|------|------|------|----------------|

| V <sub>IO</sub>     | Input Offset Voltage | $+V = 5V, V_{CM} = 0$                                       |          | -4.0 | 4.0  | mV   | 1              |

|                     |                      | $+V = 30V, V_{CM} = 0$                                      |          | -4.0 | 4.0  | mV   | 1              |

|                     |                      | +V = 30V, V <sub>CM</sub> = 28.5V,<br>V <sub>O</sub> = 1.5V |          | -4.0 | 4.0  | mV   | 1              |

| ± I <sub>Bias</sub> | Input Bias Current   | V <sub>O</sub> = 1.5V                                       | (Note 5) | -110 | -1.0 | nA   | 1              |

| t <sub>RLH</sub>    | Response Time        | V <sub>OD</sub> (Overdrive) = 50mV                          |          |      | 1.0  | μS   | 4              |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guaranteed specific performance limits. For guaranteed specifications and test conditions, see, the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: Short circuits from the output to V+ can cause excessive heating and eventual destruction. When considering short circuits to ground, the maximum output current is approximately 20 mA independent of the magnitude of V+.

Note 3: This input current will only exist when the voltage at any of the input leads is driven negative. It is due to the collector-base junction of the input PNP transistors becoming forward biased and thereby acting as input diode clamps. In addition to this diode action, there is also lateral NPN parasitic transistor action on the IC chip. This transistor action can cause the output voltages of the comparators to go to the V+ voltage level (or to ground for a large overdrive) for the time duration that an input is driven negative. This is not destructive and normal output states will re-establish when the input voltage, which was negative, again returns to a value greater than -0.3 V<sub>DC</sub> (at 25°)C.

Note 4: The low bias dissipation and the ON-OFF characteristics of the outputs keeps the chip dissipation very small (P<sub>D</sub> ≤ 100mW), provided the output transistors are allowed to saturate.

Note 5: The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the output so no loading change exists on the reference or input lines.

Note 6: The input common-mode voltage or either input signal voltage should not be allowed to go negative by more than 0.3V. The upper end of the common-mode voltage range is V+ –1.5V for Subgroup 1, or V+ –2.0V for Subgroup 2 & 3. Either or both inputs can go to +30 V<sub>DC</sub> without damage, independent of the magnitude of V+.

Note 7: Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the comparator will provide a proper output state. The low input voltage state must not be less than -0.3 V<sub>DC</sub> (or 0.3 V<sub>DC</sub> below the magnitude of the negative power supply, if used) (at 25°C).

Note 8: Parameter guaranteed by V<sub>IO</sub> tests

Note 9: The value for V<sub>Diff</sub> is not data logged during Read and Record.

Note 10: Pre and post irradiation limits are identical to those listed under AC and DC electrical characteristics except as listed in the "Post Radiation Limits" table. These parts may be dose rate sensitive in a space environment and demonstrate enhanced low dose rate effect. Radiation end point limits for the noted parameters are guaranteed only for the conditions as specified in Mil-Std-883, Method 1019, Condition A.

Note 11: SMD 5962-8773901 only

Note 12: Human Body model, 1.5 K $\Omega$  in series with 100 pF

Note 13: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$  (maximum junction temperature),  $\theta_{JA}$  (Package junction to ambient thermal resistance), and  $T_A$  (ambient temperature). The maximum allowable power dissipation at any temperature is  $P_{Dmax} = (T_{Jmax} - T_A) / \theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower.

Note 14: Low dose rate testing has been performed on a wafer-by-wafer basis, per test method 1019, condition D, MIL-STD-883, with no enhanced low dose rate sensitivity (ELDRS) effect. Pre and post irradiation limits are identical to those listed under AC and DC electrical characteristics, except as listed in the "Post Radiation Limits" table. Radiation end point limits for the noted parameters are guaranteed for only the conditions as specified in MIL-STD-883, Method 1019, condition D.

### Typical Performance Characteristics LM139, LM139A

20122134

**Response Time for Various Input Overdrives** -Positive Transition

### **Response Time for Various Input Overdrives** -Negative Transition

### **Application Hints**

The LM139 series are high gain, wide bandwidth devices which, like most comparators, can easily oscillate if the output lead is inadvertently allowed to capacitively couple to the inputs via stray capacitance. This shows up only during the output voltage transition intervals as the comparator changes states. Power supply bypassing is not required to solve this problem. Standard PC board layout is helpful as it reduces stray input-output coupling. Reducing this input resistors to < 10 k $\Omega$  reduces the feedback signal levels and finally, adding even a small amount (1 to 10 mV) of positive feedback (hysteresis) causes such a rapid transition that oscillations due to stray feedback are not possible. Simply socketing the IC and attaching resistors to the pins will cause input-output oscillations during the small transition intervals unless hysteresis is used. If the input signal is a pulse waveform, with relatively fast rise and fall times, hysteresis is not required.

All pins of any unused comparators should be tied to the negative supply.

The bias network of the LM139 series establishes a drain current which is independent of the magnitude of the power supply voltage over the range of from 2  $V_{DC}$  to 30  $V_{DC}.$

It is usually unnecessary to use a bypass capacitor across the power supply line.

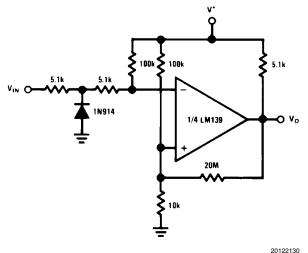

The differential input voltage may be larger than V+ without damaging the device. Protection should be provided to prevent the input voltages from going negative more than -0.3  $V_{DC}$  (at  $25^{\circ}C$ ). An input clamp diode can be used as shown in the applications section.

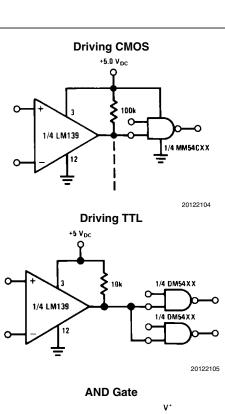

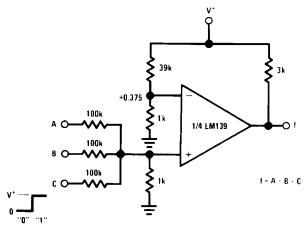

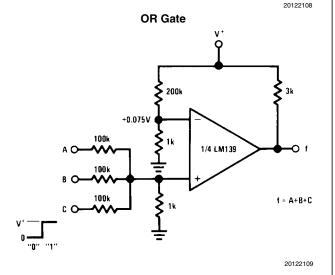

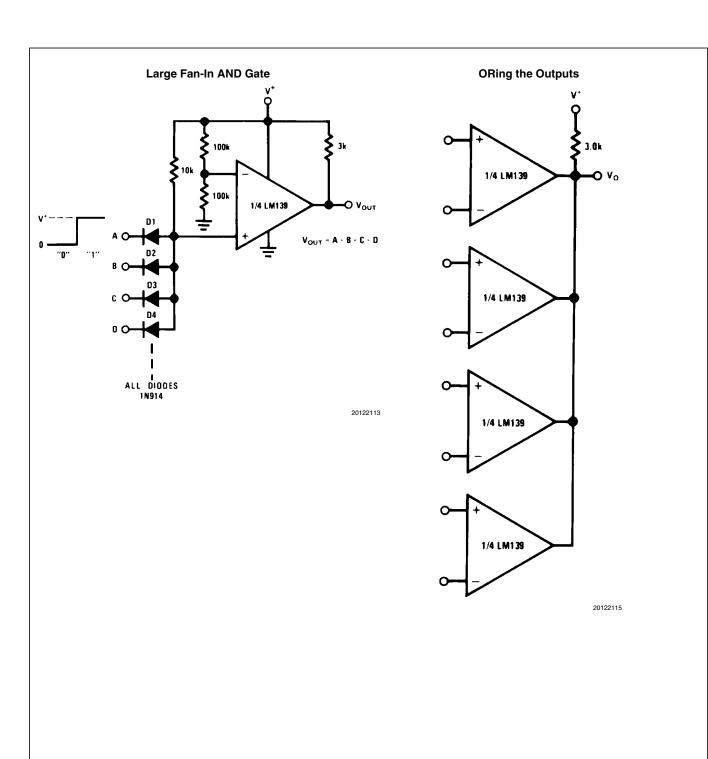

The output of the LM139 series is the uncommitted collector of a grounded-emitter NPN output transistor. Many collectors can be tied together to provide an output OR'ing function. An output pull-up resistor can be connected to any available power supply voltage within the permitted supply voltage range and there is no restriction on this voltage due to the magnitude of the voltage which is applied to the V+ terminal of the LM139A package. The output can also be used as a simple SPST switch to ground (when a pull-up resistor is not used). The amount of current which the output device can sink is limited by the drive available (which is independent of V+) and the  $\beta$  of this device. When the maximum current limit is reached (approximately 16 mA), the output transistor will come out of saturation and the output voltage will rise very rapidly. The output saturation voltage is limited by the approximately  $60\Omega$   $R_{\text{SAT}}$  of the output transistor. The low offset voltage of the output transistor (1 mV) allows the output to clamp essentially to ground level for small load currents.

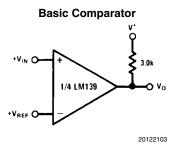

### **Typical Applications**

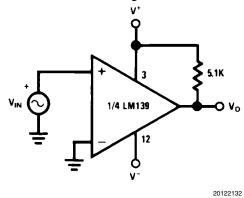

$(V^+ = 5.0 V_{DC})$

www.national.com

### **Typical Applications**

(V+= 15 V<sub>DC</sub>)

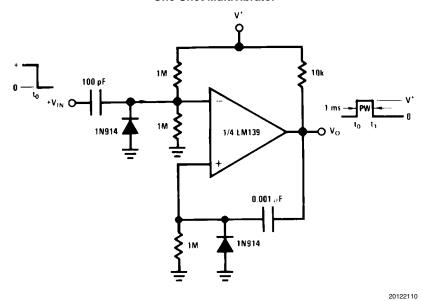

### **One-Shot Multivibrator**

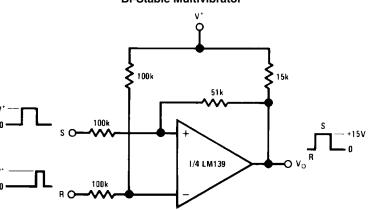

**Bi-Stable Multivibrator**

###

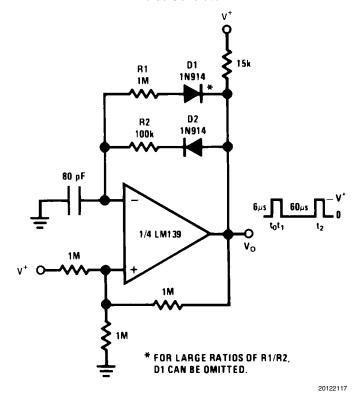

### **Pulse Generator**

### Output Strobing V 6.2k Vo STROBE INPUT

\* Or open-collector logic gate without pull-up resistor

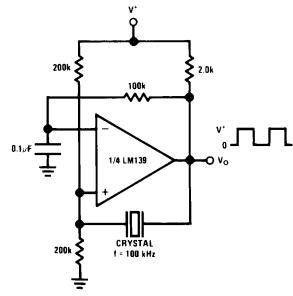

### **Crystal Controlled Oscillator**

## Transducer Amplifier 10k 3.0k 10k 1/4 LM139 20M 20122128

### **Zero Crossing Detector (Single Power Supply)**

20122131

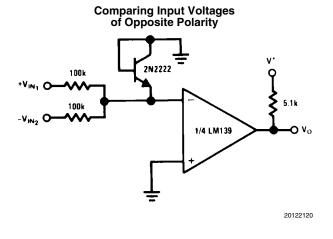

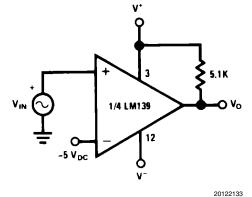

### **Split-Supply Applications**

$$(V^+ = +15 V_{DC} \text{ and } V^- = -15 V_{DC})$$

# MOS Clock Driver V: 51k 10k 2 4k 2 4k 2 4k 2 4k 3 9k 1/4 LM139 1/4 LM139 1/4 LM139 1/4 LM139 1/4 LM139

### **Zero Crossing Detector**

### **Comparator With a Negative Reference**

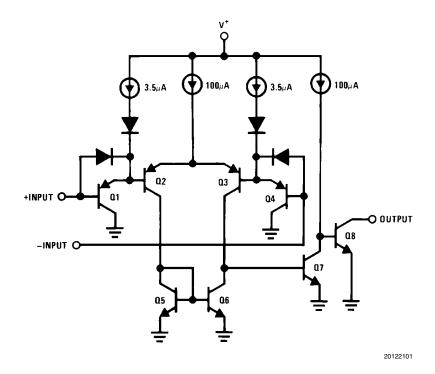

### **Schematic Diagram**

### **Revision History**

| Date     | Revision | Section                                                                                                       | Originator  | Changes                                                                                                                                                                                                                                                                                              |

|----------|----------|---------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Released |          |                                                                                                               |             |                                                                                                                                                                                                                                                                                                      |

| 02/08/05 | A        | New Release to corporate format                                                                               | L. Lytle    | 3 MDS datasheets converted into one Corp. datasheet format. MNLM139A-X-RH rev 4B0, MDLM139A-X rev 0C1, MNLM139–X rev 1A1. MDS datasheets will be archived.                                                                                                                                           |

| 06/28/06 | В        | Features, Ordering Information Table, Rad Hard Electrical Section and Notes                                   | R. Malone   | Added Available with Radiation Guarantee,<br>Low Dose NSID's to table<br>5962R9673802VCA LM139AJRLQMLV,<br>5962R9673802VDA LM139AWRLQMLV,<br>5962R9673802VXA LM139AWGRLQMLV,<br>and reference to Note 11 and 16. Note 16 to<br>Rad Hard Electrical Heading. Note 16 to<br>Notes. Archive Revision A. |

| 02/13/08 | С        | Features, Ordering Table, LM139A<br>883, QMLV & RH, SMD 5962–<br>9673801 Electrical Characteristics,<br>Notes | Larry McGee | Added TID & Eldrs reference, Note 11 -<br>Condition A. Changed VCM parameter - pg<br>8, Title from Drift Values to Delta Values - pg<br>9 & Note 16. Revision B will be Archive.                                                                                                                     |

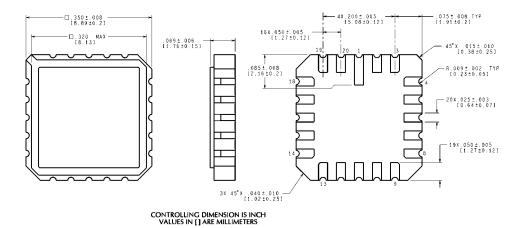

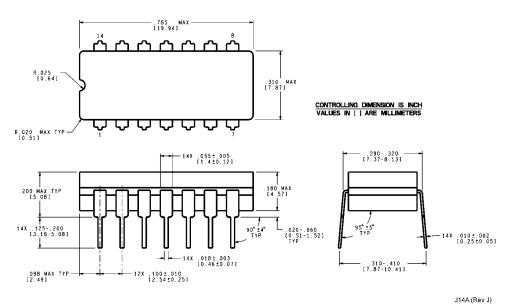

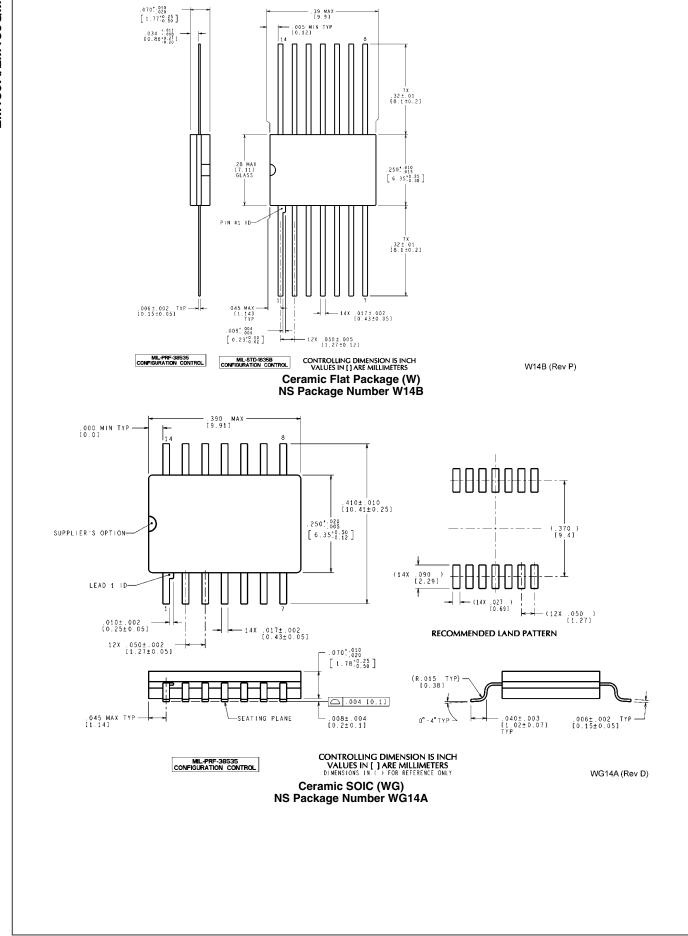

### Physical Dimensions inches (millimeters) unless otherwise noted

Leadless Chip Carrier (E)) NS Package Number E20A E20A (Rev F)

Ceramic Dual-In-Line Package (J) NS Package Number J14A

### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support          |                                |  |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |  |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |  |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |  |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |  |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |  |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |  |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |  |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |  |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |  |

| Switching Regulators           | www.national.com/switchers   |                         |                                |  |  |

| LDOs                           | www.national.com/ldo         |                         |                                |  |  |

| LED Lighting                   | www.national.com/led         |                         |                                |  |  |

| PowerWise                      | www.national.com/powerwise   |                         |                                |  |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |  |  |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |  |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |  |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email:

new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com