## Dual Channel, 20 MHz 10-Bit Resolution CMOS ADC

AD9201

#### **FEATURES**

Complete Dual Matching ADCs Low Power Dissipation: 215 mW (+3 V Supply)

Single Supply: 2.7 V to 5.5 V

**Differential Nonlinearity Error: 0.4 LSB**

**On-Chip Analog Input Buffers**

**On-Chip Reference**

Signal-to-Noise Ratio: 57.8 dB Over Nine Effective Bits

Spurious-Free Dynamic Range: -73 dB

No Missing Codes Guaranteed

28-Lead SSOP

### PRODUCT DESCRIPTION

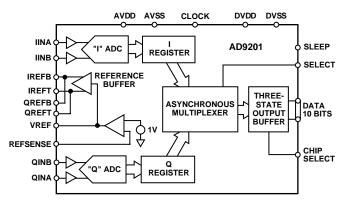

The AD9201 is a complete dual channel, 20 MSPS, 10-bit CMOS ADC. The AD9201 is optimized specifically for applications where close matching between two ADCs is required (e.g., I/Q channels in communications applications). The 20 MHz sampling rate and wide input bandwidth will cover both narrowband and spread-spectrum channels. The AD9201 integrates two 10-bit, 20 MSPS ADCs, two input buffer amplifiers, an internal voltage reference and multiplexed digital output buffers.

Each ADC incorporates a simultaneous sampling sample-and-hold amplifier at its input. The analog inputs are buffered; no external input buffer op amp will be required in most applications. The ADCs are implemented using a multistage pipeline architecture that offers accurate performance and guarantees no missing codes. The outputs of the ADCs are ported to a multiplexed digital output buffer.

The AD9201 is manufactured on an advanced low cost CMOS process, operates from a single supply from 2.7 V to 5.5 V, and consumes 215 mW of power (on 3 V supply). The AD9201 input structure accepts either single-ended or differential signals, providing excellent dynamic performance up to and beyond its 10 MHz Nyquist input frequencies.

#### FUNCTIONAL BLOCK DIAGRAM

#### PRODUCT HIGHLIGHTS

- 1. Dual 10-Bit, 20 MSPS ADCs

- A pair of high performance 20 MSPS ADCs that are optimized for spurious free dynamic performance are provided for encoding of I and Q or diversity channel information.

- 2. Low Power

- Complete CMOS Dual ADC function consumes a low 215 mW on a single supply (on 3 V supply). The AD9201 operates on supply voltages from 2.7 V to 5.5 V.

- 3. On-Chip Voltage Reference

The AD9201 includes an on-chip compensated bandgap voltage reference pin programmable for 1 V or 2 V.

- 4. On-chip analog input buffers eliminate the need for external op amps in most applications.

- Single 10-Bit Digital Output Bus

The AD9201 ADC outputs are interleaved onto a single output bus saving board space and digital pin count.

- Small Package

The AD9201 offers the complete integrated function in a compact 28-lead SSOP package.

- 7. Product Family

The AD9201 dual ADC is pin compatible with a dual 8-bit ADC (AD9281) and has a companion dual DAC product, the AD9761 dual DAC.

REV. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

$\textbf{AD9201-SPECIFICATIONS} \quad \text{(AVDD} = +3 \text{ V, DVDD} = +3 \text{ V, } F_{\text{SAMPLE}} = 20 \text{ MSPS, VREF} = 2 \text{ V, INB} = 0.5 \text{ V, } T_{\text{MIN}} \text{ to } T_{\text{MAX, internal ref, differential input signal, unless otherwise noted)}$

| Parameter                                                                                                                                                                                                                                                                                                                                       | Symbol                                                                     | Min                 | Тур                                                                                      | Max                        | Units                                                    | Condition                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| RESOLUTION                                                                                                                                                                                                                                                                                                                                      |                                                                            |                     | 10                                                                                       |                            | Bits                                                     |                                                                                                                     |

| CONVERSION RATE                                                                                                                                                                                                                                                                                                                                 | Fs                                                                         |                     |                                                                                          | 20                         | MHz                                                      |                                                                                                                     |

| DC ACCURACY Differential Nonlinearity Integral Nonlinearity Differential Nonlinearity (SE) Integral Nonlinearity (SE) Zero-Scale Error, Offset Error Full-Scale Error, Gain Error Gain Match Offset Match                                                                                                                                       | DNL<br>INL<br>DNL<br>INL<br>E <sub>ZS</sub><br>E <sub>FS</sub>             |                     | ±0.4<br>1.2<br>±0.5<br>±1.5<br>±1.5<br>±3.5<br>±0.5<br>±5                                | ±1<br>±2.5<br>±3.8<br>±5.4 | LSB<br>LSB<br>LSB<br>% FS<br>% FS<br>LSB<br>LSB          | REFT = 1 V, REFB = 0 V<br>REFT = 1 V, REFB = 0 V                                                                    |

| ANALOG INPUT Input Voltage Range Input Capacitance Aperture Delay Aperture Uncertainty (Jitter) Aperture Delay Match Input Bandwidth (-3 dB) Small Signal (-20 dB) Full Power (0 dB)                                                                                                                                                            | AIN<br>C <sub>IN</sub><br>t <sub>AP</sub><br>t <sub>AJ</sub><br>BW         | -0.5                | 2<br>4<br>2<br>2<br>2<br>240<br>245                                                      | AVDD/2                     | V<br>pF<br>ns<br>ps<br>ps<br>MHz<br>MHz                  |                                                                                                                     |

| INTERNAL REFERENCE Output Voltage (1 V Mode) Output Voltage Tolerance (1 V Mode) Output Voltage (2 V Mode) Output Voltage Tolerance (2 V Mode) Load Regulation (1 V Mode) Load Regulation (2 V Mode)                                                                                                                                            | VREF<br>VREF                                                               |                     | $ \begin{array}{c} 1 \\ \pm 10 \\ 2 \\ \pm 15 \\ \end{array} $                           | ±28                        | V<br>mV<br>V<br>mV<br>mV                                 | REFSENSE = VREF REFSENSE = GND  1 mA Load Current 1 mA Load Current                                                 |

| POWER SUPPLY Operating Voltage Supply Current Power Consumption Power-Down Power Supply Rejection                                                                                                                                                                                                                                               | AVDD<br>DRVDD<br>I <sub>AVDD</sub><br>I <sub>DRVDD</sub><br>P <sub>D</sub> | 2.7<br>2.7          | 3<br>3<br>71.6<br>0.1<br>215<br>15.5<br>0.8                                              | 5.5<br>5.5<br>245<br>1.3   | V<br>V<br>MA<br>mA<br>mW<br>mW<br>% FS                   | $AVDD - DVDD \le 2.3 \text{ V}$ $AVDD = 3 \text{ V}$ $AVDD = DVDD = 3 \text{ V}$ $STBY = AVDD, \text{Clock} = AVSS$ |

| DYNAMIC PERFORMANCE <sup>1</sup> Signal-to-Noise and Distortion f = 3.58 MHz f = 10 MHz Signal-to-Noise f = 3.58 MHz f = 10 MHz Total Harmonic Distortion f = 3.58 MHz f = 10 MHz Spurious Free Dynamic Range f = 3.58 MHz f = 10 MHz Two-Tone Intermodulation Distortion <sup>2</sup> Differential Phase Differential Gain Crosstalk Rejection | SINAD  SNR  THD  SFDR  IMD  DP  DG                                         | 55.6<br>55.9<br>–66 | 57.3<br>55.8<br>57.8<br>56.2<br>-69<br>-66.3<br>-73<br>-70.5<br>-62<br>0.1<br>0.05<br>68 | -63.3                      | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB | f = 44.49 MHz and 45.52 MHz<br>NTSC 40 IRE Mod Ramp<br>F <sub>S</sub> = 14.3 MHz                                    |

| Parameter                                   | Symbol           | Min  | Тур        | Max | Units  | Condition                              |

|---------------------------------------------|------------------|------|------------|-----|--------|----------------------------------------|

| DYNAMIC PERFORMANCE (SE) <sup>3</sup>       |                  |      |            |     |        |                                        |

| Signal-to-Noise and Distortion              | SINAD            |      |            |     |        |                                        |

| f = 3.58  MHz                               |                  |      | 52.3       |     | dB     |                                        |

| Signal-to-Noise                             | SNR              |      |            |     |        |                                        |

| f = 3.58  MHz                               |                  |      | 55.5       |     | dB     |                                        |

| Total Harmonic Distortion                   | THD              |      |            |     |        |                                        |

| f = 3.58 MHz                                | CEDB             |      | <b>-55</b> |     | dB     |                                        |

| Spurious Free Dynamic Range<br>f = 3.58 MHz | SFDR             |      | -58        |     | dB     |                                        |

| 1 – 3.38 MHZ                                |                  |      | -58        |     | аь     |                                        |

| DIGITAL INPUTS                              |                  |      |            |     |        |                                        |

| High Input Voltage                          | $ m V_{IH}$      | 2.4  |            |     | V      |                                        |

| Low Input Voltage                           | $ m V_{IL}$      |      |            | 0.3 | V      |                                        |

| DC Leakage Current                          | $I_{IN}$         |      | ±6         |     | μA     |                                        |

| Input Capacitance                           | $C_{IN}$         |      | 2          |     | pF     |                                        |

| LOGIC OUTPUT (with DVDD = 3 V)              |                  |      |            |     |        |                                        |

| High Level Output Voltage                   |                  |      |            |     |        |                                        |

| $(I_{OH} = 50 \mu A)$                       | $V_{OH}$         |      | 2.88       |     | V      |                                        |

| Low Level Output Voltage                    |                  |      |            |     |        |                                        |

| $(I_{OL} = 1.5 \text{ mA})$                 | $V_{OL}$         |      | 0.095      |     | V      |                                        |

| LOGIC OUTPUT (with DVDD = 5 V)              |                  |      |            |     |        |                                        |

| High Level Output Voltage                   |                  |      |            |     |        |                                        |

| $(I_{OH} = 50  \mu A)$                      | $V_{OH}$         |      | 4.5        |     | V      |                                        |

| Low Level Output Voltage                    |                  |      |            |     |        |                                        |

| $(I_{OL} = 1.5 \text{ mA})$                 | $V_{OL}$         |      | 0.4        |     | V      |                                        |

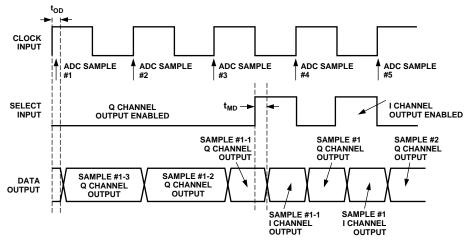

| Data Valid Delay                            | t <sub>OD</sub>  |      | 11         |     | ns     |                                        |

| MUX Select Delay                            | $t_{ m MD}$      |      | 7          |     | ns     |                                        |

| Data Enable Delay                           | $t_{ m ED}$      |      | 13         |     | ns     | $C_L = 20 \text{ pF.}$ Output Level to |

| D . II' 1 7 D 1                             |                  |      | 10         |     |        | 90% of Final Value                     |

| Data High-Z Delay                           | t <sub>DHZ</sub> |      | 13         |     | ns     |                                        |

| CLOCKING                                    |                  |      |            |     |        |                                        |

| Clock Pulsewidth High                       | t <sub>CH</sub>  | 22.5 |            |     | ns     |                                        |

| Clock Pulsewidth Low                        | $t_{CL}$         | 22.5 |            |     | ns     |                                        |

| Pipeline Latency                            |                  |      | 3.0        |     | Cycles |                                        |

### NOTES

Specifications subject to change without notice.

Figure 1. ADC Timing

REV. D -3-

$<sup>^{1}</sup>$ AIN differential 2 V p-p, REFT = 1.5 V, REFB = -0.5 V.  $^{2}$ IMD referred to larger of two input signals.

$<sup>^{3}</sup>$ SE is single ended input, REFT = 1.5 V, REFB = -0.5 V.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Parameter        | With<br>Respect<br>to | Min  | Max        | Units |

|------------------|-----------------------|------|------------|-------|

| AVDD             | AVSS                  | -0.3 | +6.5       | V     |

| DVDD             | DVSS                  | -0.3 | +6.5       | V     |

| AVSS             | DVSS                  | -0.3 | +0.3       | V     |

| AVDD             | DVDD                  | -6.5 | +6.5       | V     |

| CLK              | AVSS                  | -0.3 | AVDD + 0.3 | V     |

| Digital Outputs  | DVSS                  | -0.3 | DVDD + 0.3 | V     |

| AINA, AINB       | AVSS                  | -1.0 | AVDD + 0.3 | V     |

| VREF             | AVSS                  | -0.3 | AVDD + 0.3 | V     |

| REFSENSE         | AVSS                  | -0.3 | AVDD + 0.3 | V     |

| REFT, REFB       | AVSS                  | -0.3 | AVDD + 0.3 | V     |

| Junction Tempera | ture                  |      | +150       | °C    |

| Storage Temperat | ure                   | -65  | +150       | °C    |

| Lead Temperature | 2                     |      |            |       |

| 10 sec           |                       |      | +300       | °C    |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may effect device reliability.

#### **ORDERING GUIDE**

| Temperature<br>Model Range |                |                                  | Package<br>Options* |

|----------------------------|----------------|----------------------------------|---------------------|

| AD9201ARS<br>AD9201-EVAL   | -40°C to +85°C | 28-Lead SSOP<br>Evaluation Board | RS-28               |

<sup>\*</sup>RS = Shrink Small Outline.

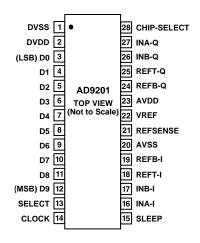

#### PIN CONFIGURATION

#### PIN FUNCTION DESCRIPTIONS

| Pin |             |                                        |

|-----|-------------|----------------------------------------|

| No. | Name        | Description                            |

| 1   | DVSS        | Digital Ground                         |

| 2   | DVDD        | Digital Supply                         |

| 3   | D0          | Bit 0 (LSB)                            |

| 4   | D1          | Bit 1                                  |

| 5   | D2          | Bit 2                                  |

| 6   | D3          | Bit 3                                  |

| 7   | D4          | Bit 4                                  |

| 8   | D5          | Bit 5                                  |

| 9   | D6          | Bit 6                                  |

| 10  | D7          | Bit 7                                  |

| 11  | D8          | Bit 8                                  |

| 12  | D9          | Bit 9 (MSB)                            |

| 13  | SELECT      | Hi I Channel Out, Lo Q Channel Out     |

| 14  | CLOCK       | Clock                                  |

| 15  | SLEEP       | Hi Power Down, Lo Normal Operation     |

| 16  | INA-I       | I Channel, A Input                     |

| 17  | INB-I       | I Channel, B Input                     |

| 18  | REFT-I      | Top Reference Decoupling, I Channel    |

| 19  | REFB-I      | Bottom Reference Decoupling, I Channel |

| 20  | AVSS        | Analog Ground                          |

| 21  | REFSENSE    | Reference Select                       |

| 22  | VREF        | Internal Reference Output              |

| 23  | AVDD        | Analog Supply                          |

| 24  | REFB-Q      | Bottom Reference Decoupling, Q Channel |

| 25  | REFT-Q      | Top Reference Decoupling, Q Channel    |

| 26  | INB-Q       | Q Channel, B Input                     |

| 27  | INA-Q       | Q Channel, A Input                     |

| 28  | CHIP-SELECT | Hi-High Impedance, Lo-Normal Operation |

# DEFINITIONS OF SPECIFICATIONS INTEGRAL NONLINEARITY (INL)

Integral nonlinearity refers to the deviation of each individual code from a line drawn from "zero" through "full scale." The point used as "zero" occurs 1/2 LSB before the first code transition. "Full scale" is defined as a level 1 1/2 LSBs beyond the last code transition. The deviation is measured from the center of each particular code to the true straight line.

### DIFFERENTIAL NONLINEARITY (DNL, NO MISSING CODES)

An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. It is often specified in terms of the resolution for which no missing codes (NMC) are guaranteed.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9201 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.