# 942-285

## 20 M BAUD HIGH CMR LOGIC GATE OPTOCOUPLER

HCPL-2400 HCPL-2411

#### Features

- HIGH SPEED: 40 MBd TYPICAL DATA RATE

- HIGH COMMON MODE REJECTION

- HCPL-2400 = 50 V<sub>CM</sub>

- HCPL-2411 = 300 V<sub>CM</sub>

- AC PERFORMANCE GUARANTEED OVER TEMPERATURE

- COMPATIBLE WITH TTL, STTL, LSTTL, AND HCMOS LOGIC FAMILIES

- NEW, HIGH SPEED AIGaAs EMITTER

- THREE STATE OUTPUT (NO PULL-UP RESISTOR REQUIRED)

- HIGH POWER SUPPLY NOISE IMMUNITY

- RECOGNIZED UNDER THE COMPONENT PROGRAM OF U.L. (FILE NO. E55361) FOR DIELECTRIC WITHSTAND PROOF TEST VOLTAGES OF 1440 Vac, 1 MINUTE AND 2500 Vac, 1 MINUTE (OPTION 010).

- HCPL-5400/1 COMPATIBILITY

## **Applications**

- ISOLATION OF HIGH SPEED LOGIC SYSTEMS

- COMPUTER-PERIPHERAL INTERFACES

- ISOLATED BUS DRIVER (NETWORKING APPLICATIONS)

- SWITCHING POWER SUPPLIES

- GROUND LOOP ELIMINATION

- HIGH SPEED DISK DRIVE I/O

- DIGITAL ISOLATION FOR A/D, D/A CONVERSION

- PULSE TRANSFORMER REPLACEMENT

#### Description

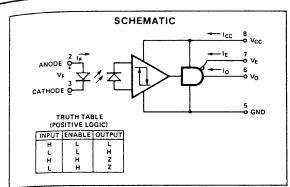

The HCPL-2400/11 high speed optocouplers combine an 820 nm AlGaAs photon emitting diode with a high speed photon detector. This combination results in very high data rate capability and low input current. The three state output eliminates the need for a pull-up resistor and allows for direct drive of data buses. The hysteresis provides typically 0.25 mA of differential mode noise immunity and minimizes the potential for output signal chatter. Improved power supply rejection minimizes the need for special power supply bypassing precautions.

The electrical and switching characteristics of the HCPL-2400/11 are guaranteed over the temperature range of 0°C to 70°C.

The HCPL-2400/11 are compatible with TTL, STTL, LSTTL and HCMOS logic families. When Schottky type TTL devices (STTL) are used, a data rate performance of 20 MBd over temperature is guaranteed when using the application circuit of Figure 13. Typical data rates are 40 MBd.

#### **Recommended Operating Conditions**

| Parameter             | Symbol   | Mín. | Max. | Units     |

|-----------------------|----------|------|------|-----------|

| Power Supply Voltage  | Vcc      | 4.75 | 5.25 | Volts     |

| Input Current (High)  | IF (ON)  | -4-  | -8   | mA        |

| Input Voltage (Low)   | VF (OFF) | -    | 0.8  | Volts     |

| Enable Voltage (Low)  | VEL      | 0    | 0.8  | Volts     |

| Enable Voltage (High) | VEH      | 2.0  | Vcc  | Volts     |

| Operating Temperature | TA       | 0    | 70°  | °C        |

| Fan Out               | N.       |      | 5    | TTL Loads |

## Absolute Maximum Ratings (No derating required up to 85°C)

| Parameter                          | Symbol         | Min.             | Max.            | Units | Note |

|------------------------------------|----------------|------------------|-----------------|-------|------|

| Storage Temperature                | Ts             | -55              | 125             | °C    | 1100 |

| Operating Temperature              | TA             | 0                | 85              | °C    |      |

| Lead Solder Temperature            | 260° C         | for 10 s. (1.6 m | m below seating |       |      |

| Average Forward Input Current      | l <sub>E</sub> |                  | 10.0            | mA    | +    |

| Peak Forward Input Current         | IFPK           |                  | 20.0            | mA    | 9    |

| Reverse Input Voltage              | VR             |                  | 3.0             | V     |      |

| Supply Voltage                     | Vcc            | - 0              | 7.0             | v     | +    |

| Three State Enable Voltage         | VE             | -0.5             | 10.0            | V     |      |

| Average Output Collector Current   | lo             | -25.0            | 25.0            | mA    | +    |

| Output Collector Voltage           | Vo             | -0.5             | 10.0            | V     |      |

| Output Collector Power Dissipation | Po             |                  | 40.0            | mW    | +    |

## **Electrical Characteristics**

For  $0^{\circ}$  C  $\leq$  T<sub>A</sub>  $\leq$  70 $^{\circ}$  C, 4.75 V  $\leq$  V<sub>CC</sub>  $\leq$  5.25 V, 4 mA  $\leq$  I<sub>F(ON)</sub>  $\leq$  8 mA, 2.0 V  $\leq$  V<sub>EH</sub>  $\leq$  5.25, 0 V  $\leq$  V<sub>EL</sub>  $\leq$  0.8 V, 0 V  $\leq$  V<sub>F(OFF)</sub>  $\leq$  0.8 V except where noted. All Typicals at T<sub>A</sub> = 25 $^{\circ}$  C, V<sub>CC</sub> = 5 V, I<sub>F(ON)</sub> = 5.0 mA, V<sub>F(OFF)</sub> = 0 V except where noted.

| Parameter                           | Symbol                     | Min. | Typ.  | Max. | Units | Test Conditions  IoL = 8.0 mA (5 TTL Loads)                        |            | Figure                                           | Note  |

|-------------------------------------|----------------------------|------|-------|------|-------|--------------------------------------------------------------------|------------|--------------------------------------------------|-------|

| Logic Low Output Voltage            | Vol                        |      |       | 0.5  | Volts |                                                                    |            | 1                                                | itote |

| Logic High Output Voltage           | Voн                        | 2.4  |       |      | Voits | I <sub>OH</sub> = -4.0 mA                                          |            | 2                                                |       |

| Output Leakage Gurrent              | Іонн                       |      |       | 100  | μА    | Vo = 5,25 V                                                        | Vr=0.8 V   | <del>                                     </del> |       |

| Logic High Enable Voltage           | VEH                        | 2.0  |       |      | Volts |                                                                    | 1 -1 000   |                                                  |       |

| Logic Low Enable Voltage            | VEL                        |      |       | 8.0  | Volts |                                                                    |            |                                                  |       |

| Logic High Enable Current           | lEH .                      |      |       | 20   | μА    | VE = 2.4 V                                                         |            |                                                  |       |

|                                     |                            |      |       | 100  | μА    | VE = 5.25 V                                                        |            | 1                                                |       |

| Logic Low Enable Current            | leL                        |      | -0.28 | -0.4 | mA    | VE = 0.4V                                                          |            |                                                  |       |

| Logic Low Supply Current            | Iccl                       |      | 19    | 26   | mA    | Vcc = 5.25 V                                                       |            |                                                  |       |

| Logic High Supply Current           | Іссн                       |      | 17    | 26   | mA    | V <sub>E</sub> =0V                                                 |            | -                                                |       |

| High Impedance State                | Iccz                       |      | 22    | 28   | mA    | Vcc = 5.25 V                                                       |            |                                                  |       |

| Supply Current                      |                            |      |       |      |       | VE = 5.25 V                                                        |            |                                                  |       |

| High Impedance State Output Current | fozu                       |      |       | 20   | μА    | Vo = 0.4V                                                          | VE = 2 V   |                                                  |       |

| Output Corrent                      | lozh                       |      |       | 20   | μА    | Vo = 2.4 V                                                         | VE = 2 V   |                                                  |       |

|                                     | lozн                       |      |       | 100  | μА    | Vo = 5.25 V                                                        |            |                                                  |       |

| Logic Low Short Circuit             | losu                       |      | 52    |      | mA    | Vo = Vcc = 5.25 V                                                  | IF = 8 mA  |                                                  | 1     |

| Output Current                      |                            |      |       |      |       |                                                                    |            |                                                  |       |

| Logic High Short Circuit            | losh                       |      | -45   |      | mA    | Vcc = 5.25 V                                                       | Ir = 0 mA, |                                                  | 1.    |

| Output Current                      |                            |      |       |      |       |                                                                    | Vo = GND   |                                                  |       |

| Input Current Hysteresis            | leys                       |      | 0.25  |      | mA    | Vcc = 5 V                                                          |            | 3                                                |       |

| Input Forward Voltage               | VF                         | 1.1  | 1.3   | 1.5  | Volts | $I_F = 5 \text{ mA, } T_A = 25^{\circ} \text{ C}$                  | 2          | 4                                                |       |

| Input Reverse Breakdown<br>Voltage  | VR                         | 3.0  | 5.0   |      | Volts | $I_{R} = 10 \ \mu A, T_{A} = 25^{\circ}$                           | С          |                                                  |       |

| Input Diode Temperature             | 7/\text{\rm F}             |      | -1.44 |      | mV/°C | l <sub>F</sub> = 5 mA                                              |            | 4                                                |       |

| Coefficient                         | <u></u><br>ΔΤ <sub>A</sub> |      |       |      |       |                                                                    |            | 7                                                |       |

| Input-Output Insulation             | II-a                       |      |       | 1    | μА    | 45% RH, t = 5s,<br>V <sub>I-O</sub> = 3kVdc, T <sub>A</sub> = 25°C |            |                                                  |       |

|                                     |                            |      |       |      | 74    |                                                                    |            |                                                  | 2, 8  |

| Option 010                          | Viso                       | 2500 |       |      | VRMS  | $RH \le 50\%$ , $t = 1 \text{ min}$ .                              |            |                                                  | 10    |

| Input-Output Resistance             | :Ri-o                      |      | 1012  |      | ohms  | V <sub>I-O</sub> = 500 VDC                                         |            |                                                  | 2     |

| Input-Output Capacitance            | Cı-o                       |      | 0.6   |      | pF    | f = 1 MHz, V <sub>I-O</sub> = 0 V dc                               |            |                                                  | 2.    |

| Input Capacitance                   | Cin                        |      | 20    |      | ρF    | f = 1 MHz, V <sub>F</sub> = 0V, Pins 2 and 3                       |            |                                                  | ٠.    |

## **SWITCHING Characteristics**

$_{0^{\circ}}$  C  $\leq$  Ta  $\leq$  70° C, 4.75 V  $\leq$  V<sub>CC</sub>  $\leq$  5.25 V, 0.0 V  $\leq$  V<sub>EN</sub>  $\leq$  0.8 V. 4 mA  $\leq$  I<sub>F</sub>  $\leq$  8.0 mA. All Typicals V<sub>CC</sub> = 5 V, Ta = 25° C, I<sub>F</sub> = 5.0 mA except where noted.

| parameter                                    | Symbol                                 |      | Min. | Typ.   | Max. | Units            | Test Condition                                                        | 19                                        | Figure  | Note |

|----------------------------------------------|----------------------------------------|------|------|--------|------|------------------|-----------------------------------------------------------------------|-------------------------------------------|---------|------|

| Propagation Delay Time to to                 |                                        | tpHL |      |        | 55   | ns               | I <sub>F(ON)</sub> = 7.0 mA                                           |                                           | 5, 6, 7 | 4    |

| Logic Low Output Level                       |                                        |      | 15   | 33     | 60   | ns               | 7 \ hp                                                                |                                           | 5, 6, 7 | 3    |

| Propagation Delay Time to                    | <sup>†</sup> PLH                       |      |      |        | 55   | ns               | I <sub>F(ON)</sub> = 7.0 mA                                           |                                           | 5, 6, 7 | 4    |

| Logic High Output Level                      |                                        |      | 15   | 30     | 60   | ns               | 7                                                                     |                                           | 5, 6, 7 | 3    |

| Pulse Width Distortion                       | Itent-teth                             |      |      | 2      | 15   | ns               | I <sub>F(ON)</sub> = 7.0 mA                                           |                                           | 5, 8    | 4    |

|                                              |                                        |      |      | 3      | 25   | ns               |                                                                       |                                           | 5, 8    |      |

| Channel Distortion                           | Δt <sub>PHL</sub><br>Δt <sub>PLH</sub> |      |      | 8      | 25   | ns               |                                                                       |                                           | 5       | 5    |

|                                              |                                        |      |      | 8      | 25   | ns               |                                                                       |                                           | 5       | 5    |

| Output Rise Time                             | tr.                                    |      |      | 20     |      | пз               |                                                                       |                                           | 5       |      |

| Output Fall Time                             | tę                                     |      |      | 10     |      | ns               |                                                                       |                                           | 5       |      |

| Output Enable Time to Logic High             | tpzH                                   |      |      | 15     |      | ns               |                                                                       |                                           | 9, 10   |      |

| Output Enable Time to<br>Logic Low           | t <sub>PZL</sub>                       |      |      | 30     |      | ns               |                                                                       |                                           | 9, 10   |      |

| Output Disable Time<br>from Logic High       | t <sub>PHZ</sub>                       |      |      | 20     |      | ns               |                                                                       |                                           | 9, 10   |      |

| Output Disable Time from Lagic Low           | tpLZ                                   |      |      | 15     |      | ns               |                                                                       |                                           | 9, 10   |      |

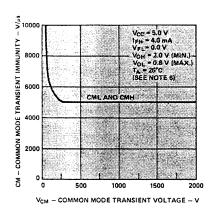

| Logic High Common Mode<br>Transient Immunity | [CM <sub>H</sub> ]                     | 2400 | 1000 | 10,000 |      | V/μs             | V <sub>CM</sub> = 50 V                                                | T <sub>A</sub> = 25°C, I <sub>F</sub> = 0 | 11, 12  | 6    |

|                                              |                                        | 2411 | 1000 |        |      | V/μs             | V <sub>CM</sub> = 300 V                                               |                                           |         |      |

| Logic Low Common Mode<br>Transient Immunity  | [CM <sub>L</sub> ]                     | 2400 | 1000 | 10,000 |      | V/μs             | V <sub>CM</sub> = 50 V                                                |                                           | 11, 12  | 6    |

|                                              |                                        | 2411 | 1000 |        |      | Wµs              | V <sub>CM</sub> = 300 V                                               |                                           | 11, 12  |      |

| Power Supply Noise<br>Immunity               | PSNI                                   |      |      | 0.5    |      | V <sub>p-p</sub> | $V_{CC} = 5.0 \text{ V}, 48 \text{ Hz} \le F_{AC} \le 50 \text{ MHz}$ |                                           |         | 7    |

#### Notes:

- 1. Duration of output short circuit time not to exceed 10 ms.

- 2. Device considered a two terminal device: pins 1-4 shorted together, and pins 5-8 shorted together.

- 3. tpHL propagation delay is measured from the 50% level on the rising edge of the input current pulse to the 1.5 V level on the falling edge of the output pulse. The tpLH propagation delay is measured from the 50% level on the falling edge of the input current pulse to the 1.5 V level on the rising edge of the output pulse.

- 4. This specification simulates the worst case operating conditions of the HCPL-2400/11 over the recommended operating temperature and Vcc range with the suggested applications circuit of Figure 13.

- Channel distortion describes the worst case variation of propagation delay from one part to another at identical operating conditions.

- 6. CM<sub>H</sub> is the maximum slew rate of common mode voltage that can be sustained with the output voltage in the logic high state (V<sub>O(MIN)</sub> > 2.0 V). CM<sub>L</sub> is the maximum slew rate of common mode voltage that can be sustained with the output voltage in the logic low state (V<sub>O(MAX)</sub> < 0.8 V).</p>

- 7. Power Supply Noise Immunity is the peak to peak amplitude of the ac ripple voltage on the Vcc line that the device will withstand and still remain in the desired logic state. For desired logic high state, Voh(MIN) > 2.0 V, and for desired logic low state, Vol(MAX) < 0.8 volts.</p>

- This is a proof test. This rating is equally validated by a 2500 V ac, 1 second test per UL E55 361.

- 9. Peak Forward Input Current pulse width < 50  $\mu s$  at 1 KHz maximum repetition rate.

- 10, See Option 010 data sheet for more information.

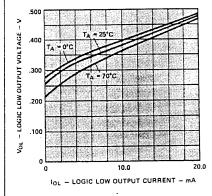

Figure 1. Typical Logic Low Output Voltage vs. Logic Low Output Current

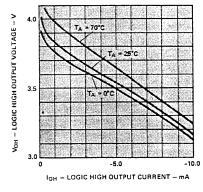

Figure 2. Typical Logic High Output Voltage vs. Logic High Output Current

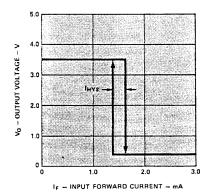

Figure 3. Typical Output Voltage vs. Input Forward Current

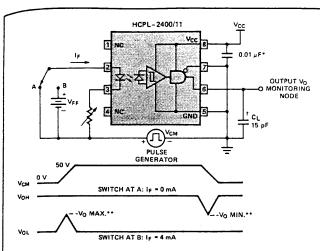

Figure 9. Test Circuit for tpHZ, tpZH, tpLZ and tpZL.

ALL DIODES ARE EC6 519 OR EQUIVALENT C1 = 30 pf INCLUDING PROBE AND JIG CAPACITANCE. Delay vs. Ambient Temperature

-MUST BE LOCATED < 1 cm FROM DEVICE UNDER TEST. -SEE NOTE 6. + CL IS APPROXIMATELY 15 pF, WHICH INCLUDES PROBE AND STRAY WIRING CAPACITANCE.

Figure 11. Test Diagram for Common Mode Transient Immunity and Typical Waveforms

Figure 12. Typical Common Mode Transient Immunity vs. Common Mode Transient Voltage

## **Applications**

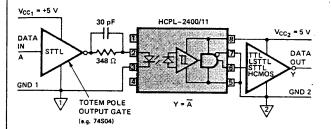

Figure 13. Recommended 20 MBd HCPL-2400/11 Interface Circuit

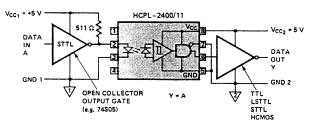

Figure 14. Alternative HCPL-2400/11 Interface Circuit

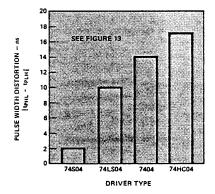

Figure 15. Typical Pulse Width Distortion vs. Input Driver Logic Family

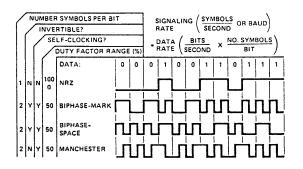

Figure 16. Modulation Code Selections

# Data Rate, Pulse-Width Distortion, and Channel Distortion Definitions

In the world of data communications, a bit is defined as the smallest unit of information a computer operates with. A bit is either a Logic 1 or Logic 0, and is interpreted by a number of coding schemes. For example, a bit can be represented by one symbol through the use of NRZ code, or can contain two symbols in codes such as Biphase or Manchester (see Figure 16). The bit rate capability of a system is expressed in terms of bits/second (b/s) and the symbol rate is expressed in terms of Baud (symbols/second). For NRZ code, the bit rate capability equals the Baud capability because the code contains one symbol per bit of information. For Biphase and Manchester codes, the bit rate capability is equal to one half of the Baud capability, because there are two symbols per bit.

Propagation delay is a figure of merit which describes the finite amount of time required for a system to translate information from input to output when shifting logic levels. Propagation delay from low to high (tpLH) specifies the amount of time required for a system's output to change from a Logic 0 to a Logic 1, when given a stimulus at the input. Propagation delay from high to low (tpHL) specifies the amount of time required for a system's output to change from a Logic 1 to a Logic 0, when given a stimulus at the input (see Figure 5).

When tp\_H and tpHL differ in value, pulse width distortion results. Pulse width distortion is defined as | tpHL-tpLH | and determines the maximum data rate capability of a distortion-limited system. Maximum pulse width distortion on the order of 20–30% is typically used when specifying the maximum data rate capabilities of systems. The exact figure depends on the particular application (RS-232, PCM, T-1, etc.).

Channel distortion, (Δtphl, Δtplh), describes the worst case variation of propagation delay from device to device at identical operating conditions. Propagation delays tend to shift as operating conditions change, and channel distortion specifies the uniformity of that shift. Specifying a maximum value for channel distortion is helpful in parallel data transmission applications where the synchronization of signals on the parallel lines is important.

The HCPL-2400/11 optocouplers offer the advantages of specified propagation delay (tp\_H, tpHL), pulse-width distortion (|tp\_H-tpHL|), and channel distortion ( $\Delta$ tp\_H,  $\Delta$ tpHL) over temperature, input forward current, and power supply voltage ranges.

## **Applications Circuits**

A recommended application circuit for high speed operation is shown in Figure 13. Due to the fast current switching capabilities of Schottky family TTL logic (74STTL), data rates of 20 MBd are achievable from 0 to 70°C. the 74S04 totem-pole driver sources current to series-drive the input of the HCPL-2400/11 optocoupler. The 348 $\Omega$  resistor limits the LED forward current. The 30 pF speed-up capacitor assists in the turn-on and turn-off of the LED, increasing the data rate capability of the circuit. On the output side, the following logic can be directly driven by the output of the HCPL-2400/11 since a pull-up resistor is not required. If desired, a non-inverting buffer may be substituted on either the input or the output side to change the circuit function from Y = A to Y = A. This circuit satisfies all recommended operating conditions.

An alternative circuit is shown in Figure 14, which utilizes a 74S05 open-collector inverter to shunt-drive the HCPL-2400/11 optocoupler. This circuit also satisfies all recommended operating conditions.

The HCPL-2400/11 optocouplers are compatible with other logic familes, such as TTL, LSTTL, and HCMOS. However, the output drive capabilities of Schottky family devices greatly exceed those associated with TTL, LSTTL, and HCMOS logic families, and are recommended in high data rate (20 MBd) applications where fast drive current transitions are required to operate the HCPL-2400/11 with minimum pulse-width distortion.

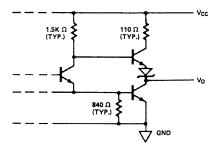

Figure 17. Typical HCPL-2400/11 Output Schematic