# Low Cost, Low Power Mono Audio Codec

# AD74111

# FEATURES

2.5 V Mono Audio Codec with 3.3 V Tolerant **Digital Interface** Supports 8 kHz to 48 kHz Sample Rates Supports 16-/20-/24-Bit Word Lengths Multibit  $\Sigma$ - $\Delta$  Modulators with "Perfect Differential Linearity Restoration" for **Reduced Idle Tones and Noise Floor** Data Directed Scrambling DAC - Least Sensitive to Jitter Performance (20 Hz to 20 kHz) 85 dB ADC Dynamic Range 93 dB DAC Dynamic Range **Programmable ADC Gain On-Chip Volume Control for DAC Channel** Software Controllable Clickless Mute Supports 256  $\times$  f<sub>s</sub>, 512  $\times$  f<sub>s</sub>, and 768  $\times$  f<sub>s</sub> Master Mode Clocks Master Clock Prescaler for Use with DSP Master Clocks **On-Chip Reference 16-Lead TSSOP Package**

# **APPLICATIONS**

Digital Video Camcorders (DVC) Portable Audio Devices (Walkman®, PDAs, and so on) Audio Processing Voice Processing Telematic Systems General-Purpose Analog I/O

### **GENERAL DESCRIPTION**

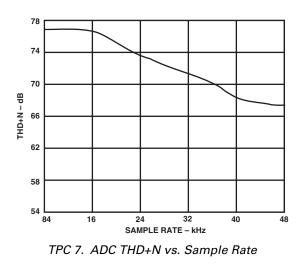

The AD74111 is a front-end processor for general-purpose audio and voice applications. It features a multibit  $\Sigma$ - $\Delta$  A/D conversion channel and a multibit  $\Sigma$ - $\Delta$  D/A conversion channel. The ADC channel provides >67 dB THD+N and the DAC channel provides >88 dB THD+N, both over an audio signal bandwidth.

The AD74111 is particularly suitable for a variety of applications where mono input and output channels are required, including audio sections of digital video camcorders, portable personal audio devices, and telematic applications. Its high quality performance also makes it suitable for speech and telephony applications such as speech recognition and synthesis, and modern feature phones.

An on-chip reference voltage is included but can be powered down and bypassed by an external reference source if required.

The AD74111 offers sampling rates that, depending on MCLK selection and MCLK divider ratio, range from 8 kHz in the voiceband range to 48 kHz in the audio range.

The AD74111 is available in a 16-lead TSSOP package option and is specified for the automotive temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

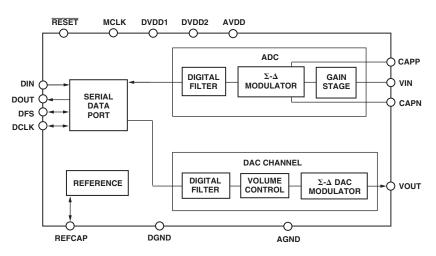

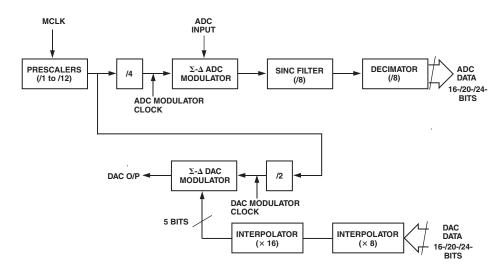

### FUNCTIONAL BLOCK DIAGRAM

# REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

#

| Parameter                              | Conditions                                        | Min  | Тур       | Max  | Unit   |

|----------------------------------------|---------------------------------------------------|------|-----------|------|--------|

| ANALOG-TO-DIGITAL CONVERTERS           |                                                   |      |           |      |        |

| ADC Resolution                         |                                                   |      | 24        |      | Bits   |

| Signal to Noise Ratio (SNR)            | $f_s = 16 \text{ kHz}$                            | 70   | 77        |      | dB     |

| Dynamic Range                          | -                                                 |      |           |      |        |

| (20 Hz to 20 kHz, -60 dB Input)        |                                                   |      |           |      |        |

| No Filter                              | $f_s = 48 \text{ kHz}$                            |      | 85        |      | dB     |

|                                        | $f_s = 16 \text{ kHz}$                            | 78   | 85        |      | dB     |

| With A-Weighted Filter                 | $f_s = 48 \text{ kHz}$                            |      | 87        |      | dB     |

| Total Harmonic Distortion + Noise      | $f_s = 48 \text{ kHz}, \text{PGA} = 0 \text{ dB}$ |      | -67       |      | dB     |

|                                        | $f_s = 16 \text{ kHz}$                            |      | -75       |      | dB     |

| Programmable Input Gain                | -                                                 |      | 12        |      | dB     |

| Gain Step Size                         |                                                   |      | 3         |      | dB     |

| Offset Error                           |                                                   | -55  | +30       | +80  | mV     |

| Full-Scale Input Voltage               |                                                   |      | 0.5       |      | V rms  |

| Input Resistance                       |                                                   |      | 4         |      | kΩ     |

| Input Capacitance                      |                                                   |      |           | 15   | pF     |

| Common-Mode Input Volts                |                                                   |      | 1.125     |      | v      |

| Crosstalk                              | ADC Input Signal = 1.0 kHz,                       |      | 100       |      | dB     |

|                                        | 0 dB; DAC Output = DC                             |      |           |      |        |

| DIGITAL-TO-ANALOG CONVERTERS           |                                                   |      |           |      |        |

| DAC Resolution                         |                                                   |      | 24        |      | Bits   |

| Signal to Noise Ratio (SNR)            | $f_s = 16 \text{ kHz}$                            | 80   | 89        |      | dB     |

| Dynamic Range                          | 5                                                 |      |           |      |        |

| (20 Hz to 20 kHz, -60 dB Input)        |                                                   |      |           |      |        |

| No Filter                              | $f_s = 48 \text{ kHz}$                            |      | 93        |      | dB     |

|                                        | $f_s = 16 \text{ kHz}$                            | 84   | 93        |      | dB     |

| With A-Weighted Filter                 | $f_S = 48 \text{ kHz}$                            |      | 95        |      | dB     |

| Total Harmonic Distortion + Noise      | $f_s = 48 \text{ kHz}$                            |      | -88       |      | dB     |

|                                        | $f_s = 16 \text{ kHz}$                            |      | -88       | -81  | dB     |

|                                        | -3                                                |      |           |      | dB     |

| DC Accuracy                            |                                                   |      |           |      |        |

| Offset Error                           |                                                   | -75  | -10       | +50  | mV     |

| Gain Error<br>Volume Control Step Size |                                                   | -0.9 | +0.175    | +0.8 | dB     |

| (1024 Linear Steps)                    |                                                   |      | 0.098     |      | %      |

| Volume Control Range (Max Attenuation) |                                                   |      | -60       |      | dB     |

| Mute Attenuation                       |                                                   |      | -100      |      | dB     |

| De-emphasis Gain Error                 |                                                   |      | $\pm 0.1$ |      | dB     |

| Full-Scale Output Voltage              |                                                   |      | 0.5       |      | V rms  |

| Output Resistance                      |                                                   |      | 145       |      | Ω      |

| Common Mode Output Volts               |                                                   |      | 1.125     |      | V      |

| Crosstalk                              | Signal Input ADC = AGND;                          |      | 95        |      | dB     |

| Grosstain                              | DAC Output                                        |      | <i></i>   |      |        |

|                                        | Level = $1.0 \text{ kHz}$ , $0 \text{ dB}$        |      |           |      |        |

| REFERENCE (Internal)                   |                                                   |      |           |      |        |

| Absolute Voltage, V <sub>REF</sub>     |                                                   |      | 1.125     |      | V      |

| V <sub>REF</sub> TC                    |                                                   |      | 50        |      | ppm/°C |

| Conditions              | Min                     | Тур                                                                                                                                                                                                                                                                                                                                                                     | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Unit                                                    |

|-------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| f <sub>S</sub> = 48 kHz | 26.5<br>120             | 5<br>910                                                                                                                                                                                                                                                                                                                                                                | 21.5<br>0.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | kHz<br>mdB<br>kHz<br>kHz<br>dB<br>µs                    |

| f <sub>S</sub> = 48 kHz | 26.5<br>75              | 5<br>505<br>55                                                                                                                                                                                                                                                                                                                                                          | 21.5<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | μs<br>kHz<br>mdB<br>kHz<br>kHz<br>dB<br>μs<br>μs<br>μs  |

|                         | DVDD1 -<br>0<br>-10     | - 0.8                                                                                                                                                                                                                                                                                                                                                                   | DVDD1<br>0.8<br>+10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V<br>V<br>μA<br>pF                                      |

|                         | DVDD1 -<br>0<br>-10     | - 0.4                                                                                                                                                                                                                                                                                                                                                                   | DVDD1<br>0.4<br>+10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V<br>V<br>μA                                            |

|                         | 2.375<br>2.375<br>2.375 | 72                                                                                                                                                                                                                                                                                                                                                                      | 2.625<br>2.625<br>3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V<br>V<br>V<br>dB                                       |

|                         | f <sub>S</sub> = 48 kHz | $f_S = 48 \text{ kHz}$ 26.5 $0$ $0$ $0$ $-10$ $0$ $-10$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ | $f_S = 48 \text{ kHz}$ $26.5 \\ 120 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 87 \\ 910 \\ 910 \\ 87 \\ 910 \\ 910 \\ 87 \\ 910 \\ 910 \\ 87 \\ 910 \\ 910 \\ 87 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 910 \\ 91$ | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$ |

\*Guaranteed by design.

Specifications subject to change without notice.

| Conditions                                               | AVDD         | DVDD1                      | DVDD2                      | Total Current |

|----------------------------------------------------------|--------------|----------------------------|----------------------------|---------------|

|                                                          | Current (mA) | Current (mA)               | Current (mA)               | (Max)(mA)     |

| ADC, Reference, Ref-Amp On<br>DAC, Reference, Ref-Amp On |              | 0.15 (0.43)<br>0.15 (0.43) | 0.72 (2.10)<br>0.85 (2.23) |               |

0.15 (0.43)

0.15 (0.43)

0.15 (0.43)

0.27 (0.50)

1.72 (4.80)

0.49 (0.49)

15.35

2.6

0.60 (0.60)

8.60

0.035

NOTES

<sup>1</sup>All values are typical, unless otherwise noted.

Reference, Ref-Amp On

All Sections On

Power-Down Mode

<sup>2</sup>Max values are quoted with DVDD1 = 3.6 V.

<sup>3</sup>Sample rates quoted are for 16 kHz and (48 kHz).

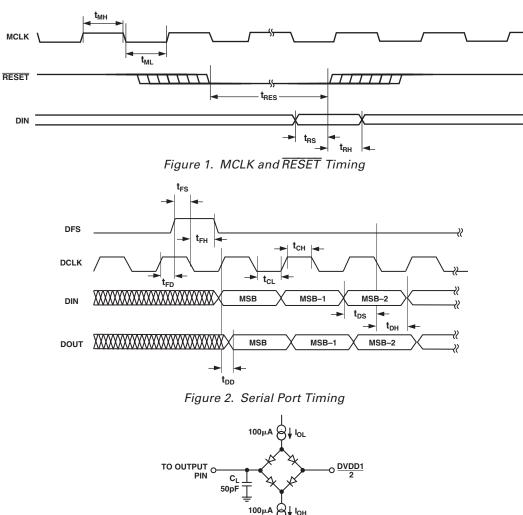

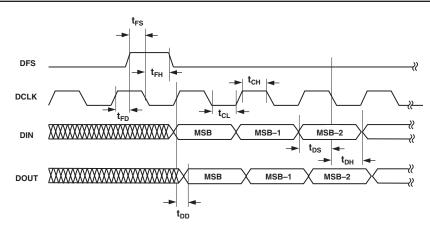

# TIMING CHARACTERISTICS (AVDD = 2.5 V $\pm$ 5%, DVDD2 = 2.5 V $\pm$ 5%, DVDD1 = 3.3 V $\pm$ 10%, f<sub>MCLK</sub> = 12.288 MHz, f<sub>s</sub> = 48 kHz, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| Parameter        |                        | Min | Max | Unit  | Comments                           |

|------------------|------------------------|-----|-----|-------|------------------------------------|

| MASTER           | R CLOCK AND RESET      |     |     |       |                                    |

| t <sub>MH</sub>  | MCLK High              | 25  |     | ns    |                                    |

| t <sub>ML</sub>  | MCLK Low               | 25  |     | ns    |                                    |

| t <sub>RES</sub> | RESET Low              | 10  |     | ns    |                                    |

| t <sub>RS</sub>  | DIN Setup Time         | 5   |     | MCLKS | To RESET Rising Edge <sup>1</sup>  |

| t <sub>RH</sub>  | DIN Setup Time         | 5   |     | MCLKS | To RESET Rising Edge <sup>1</sup>  |

| SERIAL PORT      |                        |     |     |       |                                    |

| t <sub>CH</sub>  | DCLK High <sup>2</sup> | 20  |     | ns    |                                    |

| t <sub>CL</sub>  | DCLK Low <sup>2</sup>  | 20  |     | ns    |                                    |

| t <sub>FD</sub>  | DFS Delay              |     | 5   | ns    | From DCLK Rising Edge <sup>3</sup> |

| t <sub>FS</sub>  | DFS Setup Time         | 5   |     | ns    | To DCLK Falling Edge               |

| t <sub>FH</sub>  | DFS Hold Time          | 15  |     | ns    | From DCLK Falling Edge             |

| t <sub>DD</sub>  | DOUT Delay             |     | 30  | ns    | From DCLK Rising Edge              |

| t <sub>DS</sub>  | DIN Setup Time         | 5   |     | ns    | To DCLK Falling Edge               |

| t <sub>DH</sub>  | DIN Hold Time          | 15  |     | ns    | From DCLK Falling Edge             |

| t <sub>DT</sub>  | DOUT Three-State       |     | 40  | ns    | From DCLK Rising Edge <sup>4</sup> |

NOTES

<sup>1</sup>Determines Master/Slave mode operation.

<sup>2</sup>Applies in Slave mode only.

<sup>3</sup>Applies in Master mode only.

<sup>4</sup>Applies in Multiframe-Sync mode only.

Figure 3. Load Circuit for Digital Output Timing Specifications

IOF

### **ABSOLUTE MAXIMUM RATINGS\***

| $(T_A = 25^{\circ}C, unless otherwise noted.)$                   |

|------------------------------------------------------------------|

| AVDD, DVDD2 to AGND, DGND0.3 V to +3.0 V                         |

| DVDD1 to AGND, DGND0.3 V to +4.5 V                               |

| AGND to DGND                                                     |

| Digital I/O Voltage to DGND0.3 V to DVDD1 + 0.3 V                |

| Operating Temperature Range                                      |

| Automotive (Y Version) $\dots -40^{\circ}$ C to $+105^{\circ}$ C |

| Storage Temperature Range65°C to +150°C                          |

| Junction Temperature 150°C                                       |

| 16-Lead TSSOP, $\theta_{IA}$ Thermal Impedance | W  |

|------------------------------------------------|----|

| Lead Temperature, Soldering                    |    |

| Vapor Phase (60 sec) 215 <sup>o</sup>          | ,C |

| Infrared (15 sec) 220°                         | Ъ  |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **TEMPERATURE RANGE**

| Parameter                 | Min | Max  | Unit |

|---------------------------|-----|------|------|

| Specifications Guaranteed | -40 | +105 | °C   |

| Storage                   | -65 | +150 | °C   |

# **ORDERING GUIDE**

| Model      | Range           | Package |  |

|------------|-----------------|---------|--|

| AD74111YRU | -40°C to +105°C | RU-16   |  |

### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD74111 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

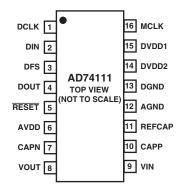

# PIN CONFIGURATION

# PIN FUNCTION DESCRIPTIONS

| Pin No. | Mnemonic | I/O | Description                                                                                                                                                                                 |

|---------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | DCLK     | I/O | Serial Clock                                                                                                                                                                                |

| 2       | DIN      | I   | Serial Data Input. The state of DIN on the rising edge of <b>RESET</b> determines the operating mode of the interface. See the Selecting Master or Slave Mode section for more information. |

| 3       | DFS      | I/O | Frame Synchronization Signal                                                                                                                                                                |

| 4       | DOUT     | 0   | Serial Data Output                                                                                                                                                                          |

| 5       | RESET    | I   | Power-Down/Reset Input                                                                                                                                                                      |

| 6       | AVDD     |     | Analog 2.5 V Power Supply Connection                                                                                                                                                        |

| 7       | CAPN     |     | ADC Filter Capacitor (Negative)                                                                                                                                                             |

| 8       | VOUT     | 0   | DAC Analog Output                                                                                                                                                                           |

| 9       | VIN      | I   | ADC Analog Input                                                                                                                                                                            |

| 10      | CAPP     |     | ADC Filter Capacitor (Positive)                                                                                                                                                             |

| 11      | REFCAP   | I/O | Internal Reference Decoupling Capacitor. Can also be used for connection of an external reference.                                                                                          |

| 12      | AGND     |     | Analog Ground Connection                                                                                                                                                                    |

| 13      | DGND     |     | Digital Ground Connection                                                                                                                                                                   |

| 14      | DVDD2    |     | Digital 2.5 V Power Supply Connection (Core)                                                                                                                                                |

| 15      | DVDD1    |     | Digital Power Supply Connection (Interface)                                                                                                                                                 |

| 16      | MCLK     | I   | External Master Clock Input                                                                                                                                                                 |

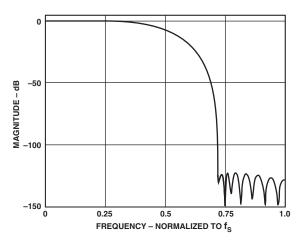

# BP -50 -100 -150 0 0.25 0.5 0.75 1.0 FREQUENCY - NORMALIZED TO f<sub>S</sub>

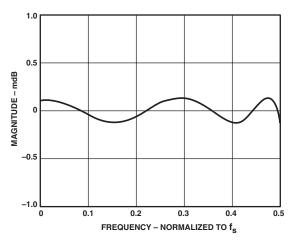

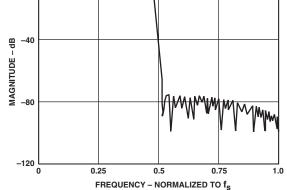

TPC 1. ADC Composite Filter Response

TPC 2. ADC Composite Filter Response Low Group Delay Enabled

TPC 3. ADC Composite Filter Response (Pass-Band Section)

# Typical Performance Characteristics–AD74111

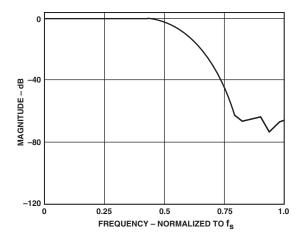

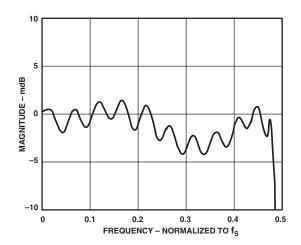

TPC 4. DAC Composite Filter Response

TPC 5. DAC Composite Filter Response Low Group Delay Enabled

TPC 6. DAC Composite Filter Response (Pass-Band Section)

# 90 88 86 眧 THD+N -84 82 80 78 ้ 8 16 24 32 40 48 SAMPLE RATE – kHz

TPC 8. DAC THD+N vs. Sample Rate

# FUNCTIONAL DESCRIPTION General Description

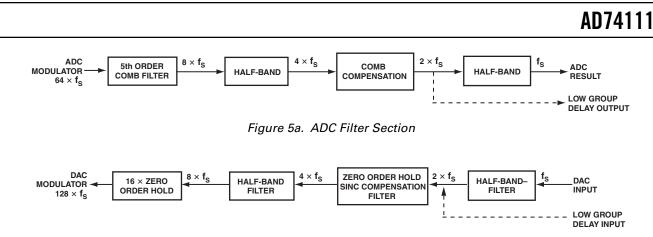

The AD74111 is a 2.5 V mono codec. It comprises an ADC and DAC channel with single-ended input and output. The ADC has a programmable gain stage and the DAC has programmable volume control. Each of these sections is described in further detail below. The AD74111 is controlled by means of a flexible serial port (SPORT) that can be programmed to accommodate many industry standard DSPs and microcontrollers. The AD74111 can be set to operate as a master or slave device. The AD74111 can be set to operate with sample rates of 8 kHz to 48 kHz, depending on the values of MCLK and the MCLK prescalers. On-chip digital filtering is provided as part of the DAC and ADC channels with a low group delay option to reduce the delays through the filters when operating at lower sample rates. Figure 4 shows a block diagram of the DAC and ADC channel in the AD74111. Figures 5a and 5b show block diagrams of the filter arrangements of the ADC and DAC filters.

# ADC Section

The AD74111 contains a multibit sigma-delta ADC. The ADC has a single input pin with additional pins for decoupling/filter capacitors. The ADC channel has an independent input amplifier gain stage that can be programmed in steps of 3 dB, from 0 dB to 12 dB. The input amplifier gain settings are set by programming the appropriate bits in Control Register E. The ADC can also be muted under software control. The AD74111 input channel employs a multibit sigma-delta conversion technique that provides a high resolution output with system filtering implemented on-chip. Sigma-delta converters employ a technique known as oversampling, where the sampling rate is many times the highest frequency of interest. In the case of the AD74111, the oversampling ratio is 64 and a decimation filter is used to reduce the output to standard sample rates. The maximum sample rate is 48 kHz.

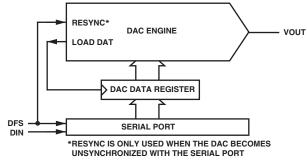

Figure 4. ADC and DAC Engine

Figure 5b. DAC Filter Section

# ADC, CAPP, and CAPN Pins

The ADC channel requires two external capacitors to act as charge reservoirs for the switched capacitor inputs of the sigmadelta modulator. These capacitors isolate the outputs of the PGA stage from glitches generated by the sigma-delta modulator. The capacitor also forms a low-pass filter with the output impedance of the PGA (approximately 124  $\Omega$ ), which helps to isolate noise from the modulator engine. The capacitors should be of good quality, such as NPO or polypropylene film, with values from 100 pF to 1 nF and should be connected to AGND.

# Peak Readback

The AD74111 can store the highest ADC value to facilitate level adjustment of the input signal. Programming the Peak Enable bit in Control Register E with a 1 will enable ADC Peak Level Reading. The peak value is stored as a 6-bit number from 0 dB to -63 dB in 1 dB steps. Reading Control Register F will give the highest ADC value since the bit was set. The ADC peak register is automatically cleared after reading.

# **Decimator Section**

The digital decimation filter has a pass-band ripple of 0.2 mdB and a stop-band attenuation of 120 dB. The filter is an FIR type with a linear phase response. The group delay at 48 kHz is 910  $\mu$ s. Output sample rates up to 48 kHz are supported.

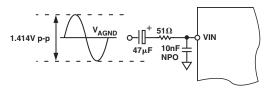

# **Input Signal Swing**

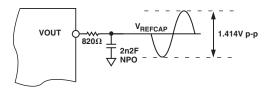

The ADC input has an input range of 0.5 V rms/1.414 V p-p about a bias point equal to  $V_{REFCAP}$ . Figure 6 shows a typical input filter circuit for use with the AD74111.

Figure 6. Typical Input Circuit

# **DAC Section**

The AD74111 DAC channel has a single-ended, analog output. The DAC has independent software controllable Mute and Volume Control functions. Control Register G controls the attenuation factor for the DAC. This register is 10 bits wide, giving 1024 steps of attenuation. The AD74111 output channel employs a multibit sigma-delta conversion technique that provides a high quality output with system filtering implemented on-chip.

# **Output Signal Swing**

The DAC has an output range of 0.5 V rms/1.414 V p-p about a bias point equal to  $V_{REFCAP}$  (see Figure 7).

Figure 7. Typical Output Circuit

# Low Group Delay

It is possible to bypass much of the digital filtering by enabling the Low Group Delay function in Control Register C. By reducing the amount of filtering the AD74111 applies to input and output samples, the time delay between the sampling interval and when the sample is available is greatly reduced. This can be of benefit in applications such as telematics, where minimal time delays are important. When the Low Group Delay function is enabled, the sample rate becomes IMCLK/128.

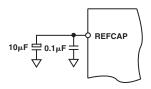

# Reference

The AD74111 features an on-chip reference whose nominal value is 1.125 V. A 100 nF ceramic and 10  $\mu$ F tantalum capacitor applied at the REFCAP pin are necessary to stabilize the reference. (See Figure 8.)

Figure 8. Reference Decoupling

If required, an external reference can be used as the reference source of the ADC and DAC sections. This may be desirable in situations where multiple devices are required to use the same value of reference or because of a better temperature coefficient specification. The internal reference can be disabled via Control Register A and the external reference applied at the REFCAP pin (see Figure 9). External references should be of a suitable value such that the voltage swing of the inputs or outputs is not affected by being too close to the power supply rails and should be adequately decoupled.

Figure 9. External Reference

### **Master Clocking Scheme**

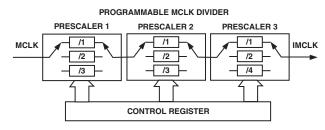

The update rate of the AD74111's ADC and DAC channels requires an internal master clock (IMCLK) that is 256 times the sample update rate (IMCLK =  $256 \times f_s$ ). To provide some flexibility in selecting sample rates, the device has a series of three master clock prescalers that are programmable and allow the user to choose a range of convenient sample rates from a single external master clock. The master clock signal to the AD74111 is applied at the MCLK pin. The MCLK signal is passed through a series of three programmable MCLK prescaler (divider) circuits that can be selected to reduce the resulting Internal MCLK (IMCLK) frequency if required. The first and second MCLK prescalers provide divider ratios of  $\div 1$  (pass through),  $\div 2$ ,  $\div 3$ ; while the third prescaler provides divider ratios of  $\div 1$  (pass through),  $\div 2$ ,  $\div 4$ .

# Figure 10. MCLK Divider

The divider ratios allow a more convenient sample rate selection from a common MCLK, which may be required in many voice related applications. Control Register B should be programmed to achieve the desired divider ratios.

### **Selecting Sample Rates**

The sample rate at which the converter runs is always 256 times the IMCLK rate. IMCLK is the Internal Master Clock and is the output from the Master Clock Prescaler. The default sample rate is 48 kHz (based on an external MCLK of 12.288 MHz). In this mode, the ADC modulator is clocked at 3.072 MHz and the DAC modulator is clocked at 6.144 MHz. Sample rates that are lower than MCLK/256 can be achieved by using the MCLK prescaler.

# Example 1: f<sub>SAMP</sub> = 48 kHz and 8 kHz Required

MCLK = 48 kHz  $\times$  256 = 12.288 MHz to provide 48 kHz f<sub>SAMP</sub>.

For  $f_{SAMP} = 8$  kHz, it is necessary to use the  $\div 3$  setting in Prescaler 1, the  $\div 2$  setting in Prescaler 2, and pass through in Prescaler 3. This results in an IMCLK = 8 kHz  $\times 256 =$ 2.048 MHz (= 12.288 MHz/6).

# Example 2: f<sub>SAMP</sub> = 44.1 kHz and 11.025 kHz Required

MCLK = 44.1 kHz  $\times$  256 = 11.2896 MHz to provide 44.1 kHz f<sub>SAMP</sub>.

For  $f_{SAMP}$  = 11.025 kHz, it is necessary to use the ÷1 setting in Prescaler 1 and the ÷4 setting in Prescaler 2, and pass through in Prescaler 3. This results in an IMCLK = 11.025 kHz × 256 = 2.8224 MHz (= 11.2896 MHz/4).

### Resetting the AD74111

The AD74111 can be reset by bringing the **RESET** pin low. Following a reset, the internal circuitry of the AD74111 ensures that the internal registers are reset to their default settings and the on-chip RAM is purged of previous data samples. The DIN pin is sampled to determine if the AD74111 is required to operate in Master or Slave mode. The reset process takes 3072 MCLK periods, and the user should not attempt to program the AD74111 during this time.

# **Power Supplies and Grounds**

The AD74111 features three separate supplies: AVDD, DVDD1, and DVDD2.

AVDD is the supply to the analog section of the device and must be of sufficient quality to preserve the AD74111's performance characteristics. It is nominally a 2.5 V supply.

DVDD1 is the supply for the digital interface section of the device. It is fed from the digital supply voltage of the DSP or controller to which the device is interfaced and allows the AD74111 to interface with devices operating at supplies of between 2.5 V - 5% to 3.3 V + 10%.

DVDD2 is the supply for the digital core of the AD74111. It is nominally a 2.5 V supply.

# Accessing the Internal Registers

The AD74111 has seven registers that can be programmed to control the functions of the AD74111. Each register is 10 bits wide and is written to or read from using a 16-bit write or read operation, with the exception of Control Register F, which is read-only. Table V shows the format of the data transfer operation. The Control Word is made up of a Read/Write bit, the register address, and the data to be written to the device. Note that in a read operation the data field is ignored by the device. Access to the control registers is via the serial port through one of the operating modes described below.

# Serial Port

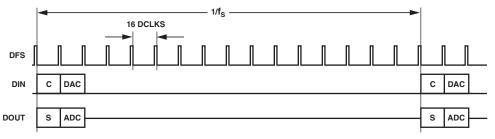

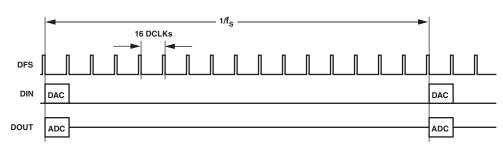

The AD74111 contains a flexible serial interface port that is used to program and read the control registers and to send and receive DAC and ADC audio data. The serial port is compatible with many popular DSPs and can be programmed to operate in a variety of modes, depending on which one best suits the DSP being used. The serial port can be set to operate as a Master or Slave device, as discussed below. Figure 11 shows a timing diagram of the serial port.

Figure 11. Serial Port (SPORT) Timing

# **Serial Port Operating Modes**

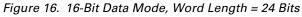

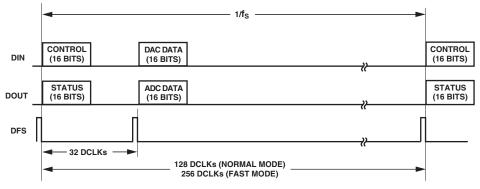

The serial port of the AD74111 can be programmed to operate in a variety of modes depending on the requirements and flexibility of the DSP to which it is connected. The two principal modes of operation are Mixed mode and Data mode.

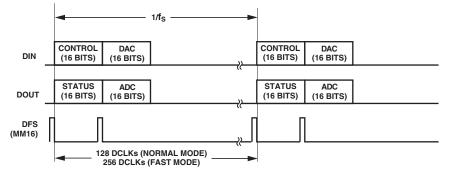

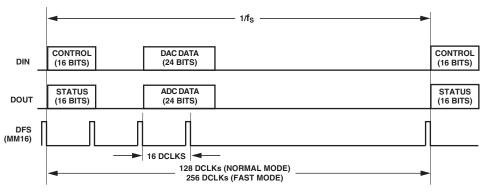

# Mixed Mode

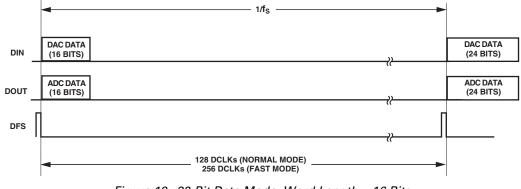

Mixed mode allows the control registers of the AD74111 to be programmed and read back. It also allows data to be sent to the DACs and data to be read from the ADCs. In Mixed mode, there are separate data slots, each with its own frame synchronization signal (DFS) for control and DAC or ADC information. The AD74111 powers up in Mixed mode by default to allow the control registers to be programmed. Figure 13 shows the default setting for Mixed mode.

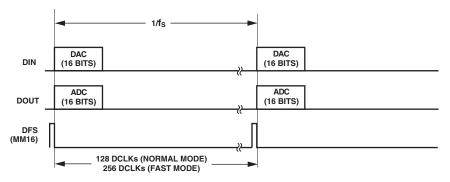

# Data Mode

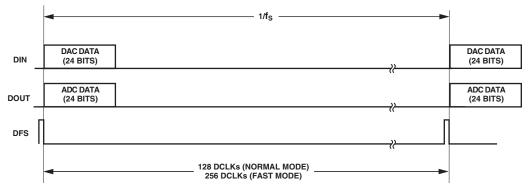

Data mode can be used when programming or reading the control registers is no longer required. Data mode provides a frame synchronization (DFS) pulse for each sample of data. Once the part has been programmed into Data mode, the only way to change the control registers is to perform a hardware reset to put the AD74111 back into Mixed mode. Figure 15 shows the default setting for Data mode.

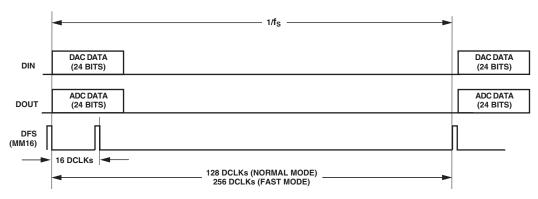

# Data-Word Length

The AD74111 can be programmed to send DAC audio data and receive ADC audio data in different word length formats of 16, 20, or 24 bits. The default mode is 16 bits, but this can be changed by programming Control Register C for the appropriate word length.

# Selecting Master or Slave Mode

The initial operating mode of the AD74111 is determined by the state of the DIN pin following a reset. If the DIN pin is high during this time, Slave mode is selected. In Slave mode, the DFS and DCLK pins are inputs and the control signals for these pins must be provided by the DSP or other controller. If the DIN pin is low immediately following a reset, the AD74111 will operate in Master mode.

# **Master Mode Operation**

In Master mode, the DFS and DCLK pins are outputs from the AD74111. This is the easiest mode in which to use the AD74111 because the correct timing relationship between sample rate, DCLK, and DFS is controlled by the AD74111.

# **Slave Mode Operation**

In Slave mode, the DFS and DCLK pins are inputs to the AD74111. Care needs to be exercised when designing a system to operate the AD74111 in this mode as the relationship between the sample rate, DCLK, and DFS needs to be controlled by the DSP or other controller and must be compatible with the internal DAC/ADC engine of the AD74111. Figure 12 shows a block diagram of the DAC engine and the AD74111's serial port. The sample rate for the DAC engine is determined by the MCLK and MCLK prescalers. The DAC engine will read data from the DAC Data register at this rate. It is therefore important that the serial port is updated at the same rate, as any error between the two will accumulate and eventually cause the DAC engine to have to resynchronize with the serial port, which will cause erroneous values on the DAC output pins.

# Figure 12. DAC Engine

In most cases, it is easy to keep a DSP in synchronization with the AD74111 if they are both run from the same clock or the DSP clock is a multiple of the AD74111's MCLK. In this case,

there will be a fixed relationship between the instruction cycle time of the DSP program and the AD74111, so a timer could be used to accurately control the DAC updates. If a timer is not available, the Multiframe-Sync (MFS) mode could be used to generate a DFS pulse every 16 or 32 DCLKs, allowing the DSP to accurately control the number of DCLKs between updates using an autobuffering or DMA type technique. In all cases for Slave mode operation, there should be 128 DCLKs (Normal mode) or 256 DCLKs (Fast mode) between DAC updates. The ADC operates in a similar manner; however, if the DSP does not read an ADC result, this will appear only as a missed sample and will not be audible. Slave mode is most suited to state-machine type applications where the number of DCLKs and their relationships to the other interface signals can be controlled.

| CRD:3<br>DM/MM | CRD:2<br>DSP<br>Mode | CRC:5, 4<br>Word<br>Width | Operating<br>Mode | Figure |

|----------------|----------------------|---------------------------|-------------------|--------|

| 0              | 0                    | 16                        | 16-Bit Data Mode  | 15     |

| 0              | 1                    | 16                        | 32-Bit Data Mode  | 19     |

| 1              | 0                    | 16                        | 16-Bit Mixed Mode | 13     |

| 1              | 1                    | 16                        | 32-Bit Mixed Mode | 17     |

| 0              | 0                    | >16                       | 16-Bit Data Mode  | 16     |

| 0              | 1                    | >16                       | 32-Bit Data Mode  | 20     |

| 1              | 0                    | >16                       | 16-Bit Mixed Mode | 14     |

| 1              | 1                    | >16                       | 32-Bit Mixed Mode | 18     |

Figure 13. 16-Bit Mixed Mode, Word Length = 16 Bits

Figure 14. 16-Bit Mixed Mode, Word Length = 24 Bits

Figure 15. 16-Bit Data Mode, Word Length = 16 Bits

Figure 17. 32-Bit Mixed Mode, Word Length = 16 Bits

Figure 18. 32-Bit Mixed Mode, Word Length = 24 Bits

Figure 19. 32-Bit Data Mode, Word Length = 16 Bits

Figure 20. 32-Bit Data Mode, Word Length = 24 Bits

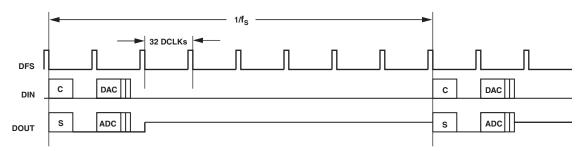

Figure 21. Multiframe Sync 32-Bit Mixed Mode

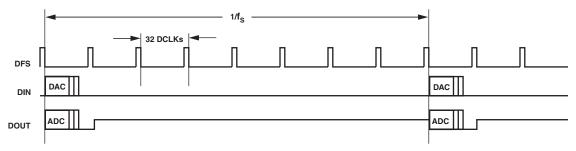

Figure 22. Multiframe Sync 32-Bit Data Mode

Figure 23. Multiframe Sync 16-Bit Mixed Mode

Figure 24. Multiframe Sync 16-Bit Data Mode

| CRD:9<br>MFS | CRD:3<br>DM/MM | CRC:2<br>DSP Mode | Operating Mode    | Figure |

|--------------|----------------|-------------------|-------------------|--------|

| 1            | 0              | 0                 | 16-Bit Data Mode  | 24     |

| 1            | 0              | 1                 | 32-Bit Data Mode  | 22     |

| 1            | 1              | 0                 | 16-Bit Mixed Mode | 23     |

| 1            | 1              | 1                 | 32-Bit Mixed Mode | 21     |

Table IV. Control Register Map

| Address (Binary) | Name | Description        | Туре | Width | Reset Setting |

|------------------|------|--------------------|------|-------|---------------|

| 0000             | CRA  | Control Register A | R/W  | 10    | 00h           |

| 0 0 0 1          | CRB  | Control Register B | R/W  | 10    | 00h           |

| 0010             | CRC  | Control Register C | R/W  | 10    | 00h           |

| 0011             | CRD  | Control Register D | R/W  | 10    | 08h or 09h*   |

| 0100             | CRE  | Control Register E | R/W  | 10    | 00h           |

| 0101             | CRF  | Control Register F | R    | 10    | 00h           |

| 0110             | CRG  | Control Register G | R/W  | 10    | 00h           |

\*09h if DIN is low and 08h if DIN is high.

# Table V. Control Word Descriptions

| Bit     | Field            | Description                                                                                                                                                                                                                                                                           |

|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15      | R/W              | When this bit is high, the contents of the data field will be written to the register specified by the Address Field. When this bit is low, a read of the register specified by the Address Field will occur at the next sample interval; the contents of the Data Field are ignored. |

| 14 - 11 | Register Address | This 4-bit field is used to select one of the seven control registers of the AD74111.                                                                                                                                                                                                 |

| 10      | Reserved         | This bit is reserved and should always be programmed with zero.                                                                                                                                                                                                                       |

| 9–0     | Data Field       | This 10-bit field holds the data that is to be written to or read from the register specified in the Address Field.                                                                                                                                                                   |

| Table VI. | <b>Control Register A</b> |

|-----------|---------------------------|

|-----------|---------------------------|

|     |                |     |          | Function               |                   |                   |                   |                        |          |

|-----|----------------|-----|----------|------------------------|-------------------|-------------------|-------------------|------------------------|----------|

| R/W | ADDRESS        | RES | Reserved | ADC Input<br>Amplifier | ADC               | DAC               | Reference         | Reference<br>Amplifier | Reserved |

| 15  | 14, 13, 12, 11 | 10  | 9, 8, 7  | 6                      | 5                 | 4                 | 3                 | 2                      | 1, 0     |

| 1   | 0000           | 0   | 0        | 0 = Off<br>1 = On      | 0 = Off<br>1 = On | 0 = Off<br>1 = On | 0 = Off<br>1 = On | 0 = Off<br>1 = On      | 0        |

# Table VII. Control Register B

|     |                |     | Function   |                                                                              |                                                                              |                                                                              |

|-----|----------------|-----|------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| R/W | ADDRESS        | RES | Reserved   | Third MCLK<br>Divider                                                        | Second MCLK<br>Divider                                                       | First MCLK<br>Divider                                                        |

| 15  | 14, 13, 12, 11 | 10  | 9, 8, 7, 6 | 5, 4                                                                         | 3, 2                                                                         | 1,0                                                                          |

| 1   | 0001           | 0   | 0          | 00 = Divide by 1<br>01 = Divide by 2<br>10 = Divide by 4<br>11 = Divide by 1 | 00 = Divide by 1<br>01 = Divide by 2<br>10 = Divide by 3<br>11 = Divide by 1 | 00 = Divide by 1<br>01 = Divide by 2<br>10 = Divide by 3<br>11 = Divide by 1 |

# Table VIII. Control Register C

|     |                |     | Function   |                                                              |                             |                                                          |                             |

|-----|----------------|-----|------------|--------------------------------------------------------------|-----------------------------|----------------------------------------------------------|-----------------------------|

| R/W | ADDRESS        | RES | Reserved   | DAC and ADC<br>Word Width                                    | Low Group<br>Delay          | DAC<br>De-emphasis                                       | ADC High-<br>Pass Filter    |

| 15  | 14, 13, 12, 11 | 10  | 9, 8, 7, 6 | 5, 4                                                         | 3                           | 2, 1                                                     | 0                           |

| 1   | 0010           | 0   | 0          | 00 = 16 Bits<br>01 = 20 Bits<br>10 = 24 Bits<br>11 = 24 Bits | 0 = Disabled<br>1 = Enabled | 00 = None<br>01 = 44.1 kHz<br>10 = 32 kHz<br>11 = 48 kHz | 0 = Disabled<br>1 = Enabled |

# Table IX. Control Register D

|     |                |     |                                 | Function      |                                 |          |                                                                         |                  |

|-----|----------------|-----|---------------------------------|---------------|---------------------------------|----------|-------------------------------------------------------------------------|------------------|

| R/W | ADDRESS        | RES | Multiframe Sync                 | Reserved      | DM/MM                           | DSP Mode | Fast DCLK                                                               | Master/<br>Slave |

| 15  | 14, 13, 12, 11 | 10  | 9                               | 8, 7, 6, 5, 4 | 3                               | 2        | 1                                                                       | 0                |

| 1   | 0011           | 0   | 0 = Normal Mode<br>1 = MFS Mode | 0             | 0 = Data Mode<br>1 = Mixed Mode |          | $\begin{array}{c} 0 = 128 \times f_S \\ 1 = 256 \times f_S \end{array}$ |                  |

Table X. Control Register E

|     |                |     | Function   |                                 |                                                                     |                        |                        |  |

|-----|----------------|-----|------------|---------------------------------|---------------------------------------------------------------------|------------------------|------------------------|--|

| R/W | ADDRESS        | RES | Reserved   | ADCL Peak<br>Enable             | ADC Gain                                                            | ADC<br>Mute            | DAC<br>Mute            |  |

| 15  | 14, 13, 12, 11 | 10  | 9, 8, 7, 6 | 5                               | 4, 3, 2                                                             | 1                      | 0                      |  |

| 1   | 0100           | 0   | 0          | 0 = Disabled<br>1 = Peak Enable | 000 = 0 dB<br>001 = 3 dB<br>010 = 6 dB<br>011 = 9 dB<br>1XX = 12 dB | 0 = Normal<br>1 = Mute | 0 = Normal<br>1 = Mute |  |

Table XI. Control Register F

|     |                |     | Function   |                                                                                                   |

|-----|----------------|-----|------------|---------------------------------------------------------------------------------------------------|

| R/W | ADDRESS        | RES | Reserved   | ADC Input Peak Level                                                                              |

| 15  | 14, 13, 12, 11 | 10  | 9, 8, 7, 6 | 5, 4, 3, 2, 1, 0                                                                                  |

| 0   | 0101           | 0   | 0          | 000000 = 0 dBFS<br>000001 = -1 dBFS<br>000010 = -2 dBFS<br>111110 = -62 dBFS<br>111111 = -63 dBFS |

Table XII. Control Register G

|     |                |     | Function                                                                                                                                 |

|-----|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| R/W | ADDRESS        | RES | DAC Volume                                                                                                                               |

| 15  | 14, 13, 12, 11 | 10  | 9, 8, 7, 6, 5, 4, 3, 2, 1, 0                                                                                                             |

| 1   | 0110           | 0   | 0000000000 = 0 dBFS<br>0000000001 = (1023/1024) dBFS<br>0000000010 = (1022/1024) dBFS<br>1111111110 = (2/1024) dBFS<br>1111111111 = Mute |

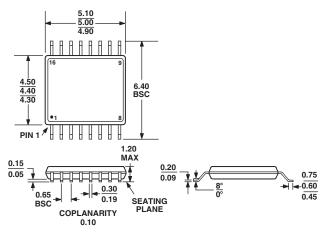

# **OUTLINE DIMENSIONS**

# 16-Lead Thin Shrink Small Outline Package [TSSOP]

(RU-16)

Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MO-153AB

C03069-0-2/03(0)