Wired Communications

Never stop thinking.

Edition 2001-07-16

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 7/16/01. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# DFE-Q V2.1 Quad ISDN 2B1Q Echocanceller Digital Front End

PEF 24911 Version 2.1

Wired Communications

## PEF 24911

| Revision H                     | listory: 2001-07-16                                                                                                                        | DS 3           |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| Previous Ve                    | ersion: Data Sheet 11.00                                                                                                                   | DS 2           |  |

| Page                           | Subjects (major changes since last revision)                                                                                               |                |  |

| Page 13                        | New function: Disable Super Frame Marker introduced on                                                                                     | pin 16: DSFM   |  |

| Page 13<br>Page 13,<br>Page 39 | Refined description of pin 49: CRCON Especially, CRCON = '1' selects MFILT= 0011 0xxx (erroneously, MFILT= 000010xx was documented in DS2) |                |  |

| Page 28                        | Added note: MON-12 read access is impossible in state 'E                                                                                   | Deactivated'   |  |

| Page 43                        | Restriction: PACA/PACE must not be used during local local                                                                                 | opback active  |  |

| Page 54                        | C/I-command LTD added (function as in V1.x)                                                                                                |                |  |

| Page 63                        | AR0 and ARX set UOA = '1' (before: AR0 and ARX set U0 value as the received SAI bit)                                                       | OA to the same |  |

| Page 95<br>Page 130            | Refined description 'Framer / Deframer Loopback': - always transparent - prerequisite is transparent state                                 |                |  |

| Page 97                        | Bit Error Rate Counter: refined operational description                                                                                    |                |  |

| Page 103                       | Data Through is only test mode, C/I-command = ARL must not be applied when pin DT = '1'                                                    |                |  |

| Page 113                       | Refined description of 'Control via MON-2'                                                                                                 |                |  |

| Page 119                       | Removed 'Propagation Delay Measurement': function not                                                                                      | supported      |  |

| Page 120                       | Refined description of mode register evaluation timing                                                                                     |                |  |

| Page 121                       | Removed description OPMODE.MODE1,0: no settings po                                                                                         | ssible         |  |

| Page 125<br>Page 127           | , ,                                                                                                                                        |                |  |

| Page 129                       | Changed TEST.bit6 = '1' (not '0')                                                                                                          |                |  |

| Page 130                       | Statemachine is put into transparent state by TRANS='0' (                                                                                  | (not '1')      |  |

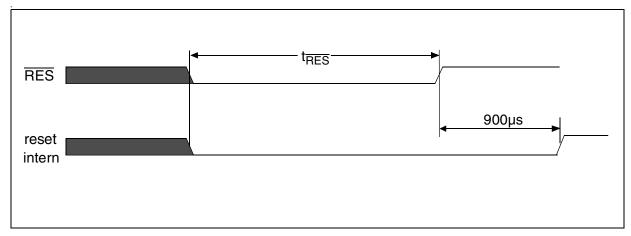

| Page 135                       | Refined reset timing description; added 900µs internal del                                                                                 | ay to figure   |  |

| Page 136                       | Refined description of FSC / Superframe-FSC-timing                                                                                         |                |  |

| Page 137                       | Table 21: Max. connection resistance specified                                                                                             |                |  |

| Page 139                       | Removed input capacitance of pin XIN (pin XIN is not sup                                                                                   | ported)        |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

| Table of                                                                                                                                                                                                                       | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4                                                                                                                                                                                                  | Introduction Features Logic Symbol System Integration Operational Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2<br>4<br>5                                                                                                                                                                                                                                                                                                                    |

| 2<br>2.1<br>2.2<br>2.3                                                                                                                                                                                                         | Pin Descriptions          Pin Diagram          Pin Definitions and Functions          Pinning Changes from DFE-Q V1.3 to DFE-Q V2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 11<br>. 12                                                                                                                                                                                                                                                                                                                   |

| 3<br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.8.1<br>3.8.2<br>3.8.3<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.16.1<br>3.16.2<br>3.16.3 | Functional Description Functional Overview IOM®-2 Interface IOM®-2 Interface IOM®-2 Interface Frame Structure Superframe Marker Function IOM®-2 Command/ Indicate Channel IOM®-2 Monitor Channel MON-12 Protocol Interface to the Analog Front End General Purpose I/Os Clock Generation U-Transceiver Functions 2B1Q Frame Structure Maintenance Channel M4 Bit Reporting to State Machine M4, M5, M6 Bit Control Mechanisms Start of Maintenance Bit Evaluation Embedded Operations Channel (EOC) EOC Processor Cyclic Redundancy Check Scrambling/ Descrambling Encoding/ Decoding (2B1Q) C/I Codes (2B1Q) State Machine Notation LT Mode State Diagram Inputs to the U-Transceiver in LT-Mode Outputs of the U-Transceiver in LT-Mode | <ul> <li>. 20</li> <li>. 21</li> <li>. 23</li> <li>. 24</li> <li>. 28</li> <li>. 30</li> <li>. 34</li> <li>. 34</li> <li>. 36</li> <li>. 41</li> <li>. 43</li> <li>. 45</li> <li>. 46</li> <li>. 47</li> <li>. 50</li> <li>. 52</li> <li>. 53</li> <li>. 54</li> <li>. 55</li> <li>. 57</li> <li>. 58</li> <li>. 62</li> </ul> |

| <b>4</b> 4.1 4.2 4.3                                                                                                                                                                                                           | Operational Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 69<br>. 69                                                                                                                                                                                                                                                                                                                   |

| Table of | Contents                                                    | Page  |

|----------|-------------------------------------------------------------|-------|

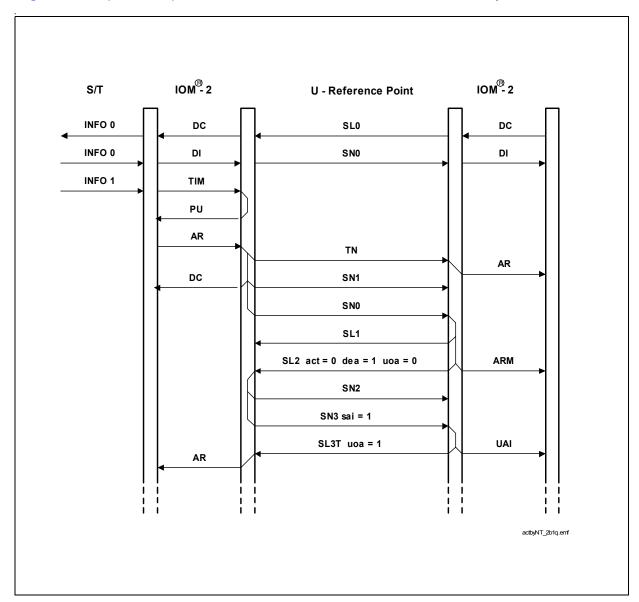

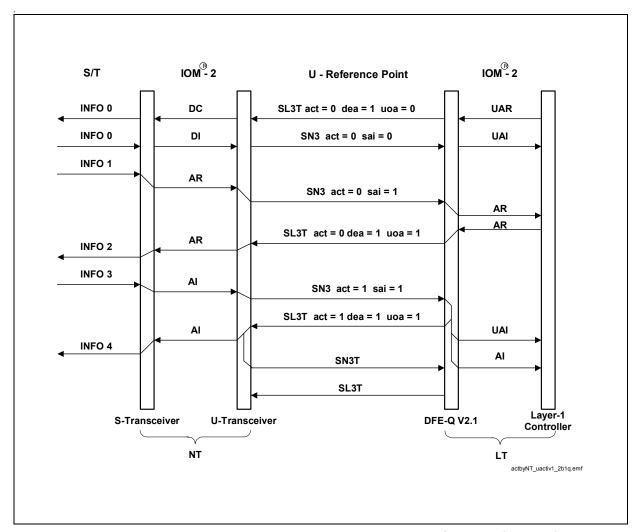

| 4.3.1    | Complete Activation Initiated by LT                         | 73    |

| 4.3.2    | Activation with ACT-Bit Status Ignored by the Exchange Side |       |

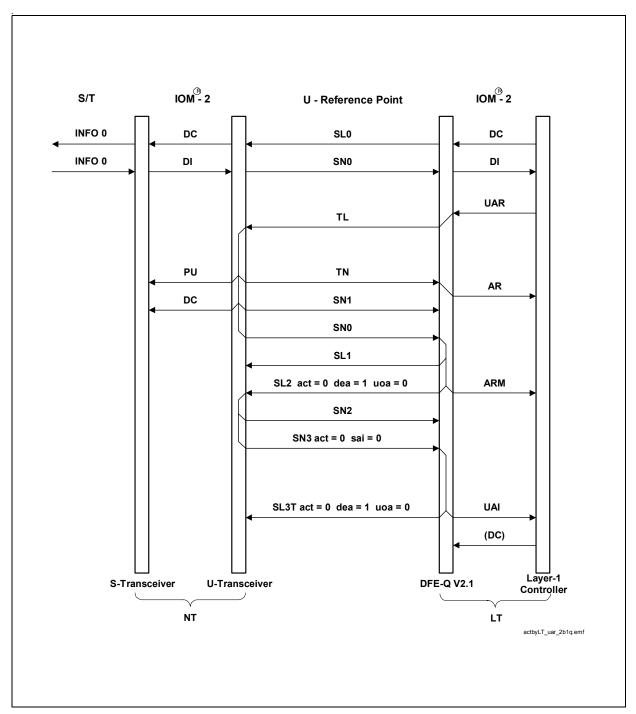

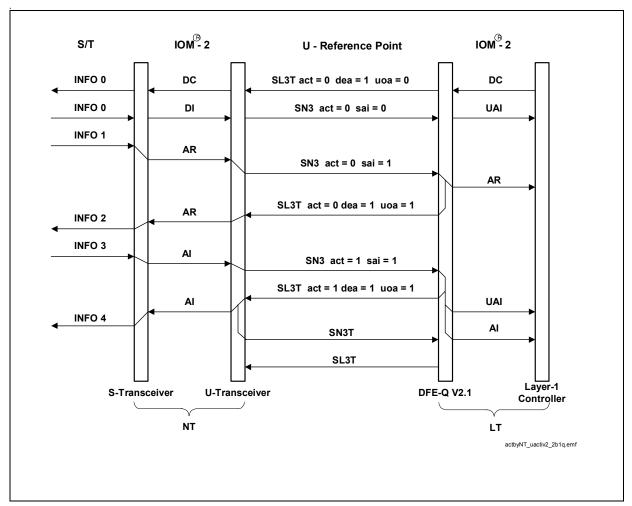

| 4.3.3    | Complete Activation Initiated by TE                         |       |

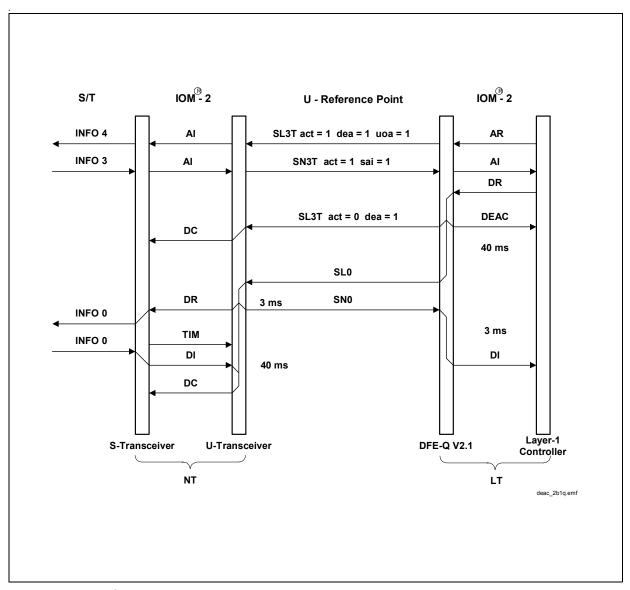

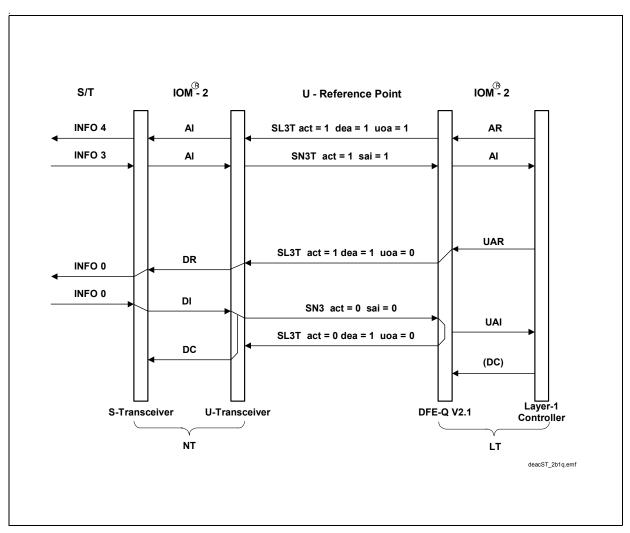

| 4.3.4    | Complete Deactivation                                       | 79    |

| 4.3.5    | Partial Activation (U Only)                                 | 80    |

| 4.3.6    | Activation Initiated by LT with U Active                    |       |

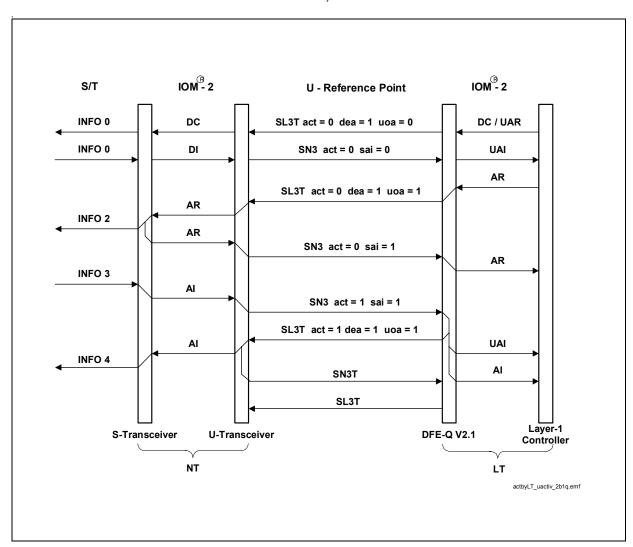

| 4.3.7    | Activation Initiated by TE with U Active                    | 84    |

| 4.3.8    | Deactivating S/T-Interface Only                             |       |

| 4.4      | Maintenance and Test Functions                              | 88    |

| 4.4.1    | Test Loopbacks                                              | 88    |

| 4.4.1.1  | Analog Loopback (No.1)                                      | 89    |

| 4.4.1.2  | Loopback No.2 - Overview                                    | 90    |

| 4.4.1.3  | Loopback No.2 - Complete Loopback                           | 91    |

| 4.4.1.4  | Loopback No.2 - Single Channel Loopbacks                    | 93    |

| 4.4.1.5  | Local Loopbacks Featured By Register LOOP                   |       |

| 4.4.2    | Bit Error Rate Counter                                      |       |

| 4.4.3    | Block Error Counters                                        |       |

| 4.4.3.1  | Near-End and Far-End Block Error Counter                    | 97    |

| 4.4.3.2  | Testing Block Error Counters                                | . 100 |

| 4.4.4    | System Measurements                                         | . 103 |

| 4.4.4.1  | Single-Pulses Test Mode (SSP)                               | . 103 |

| 4.4.4.2  | Data Through Test Mode (DT)                                 | . 103 |

| 4.4.4.3  | Reset Mode                                                  | . 103 |

| 4.4.4.4  | Pulse Mask Measurement                                      | . 104 |

| 4.4.4.5  | Power Spectral-Density Measurement                          | . 104 |

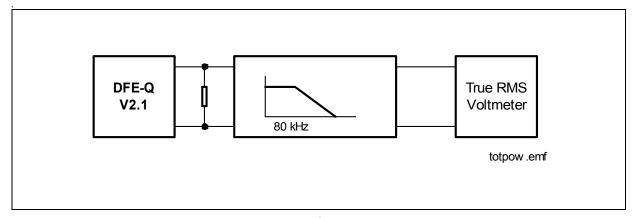

| 4.4.4.6  | Total Power Measurement                                     | . 104 |

| 4.4.4.7  | Return-Loss Measurement                                     | . 105 |

| 4.4.4.8  | Quiet Mode Measurement                                      | . 105 |

| 4.4.4.9  | Insertion Loss Measurement                                  | . 105 |

| 4.4.5    | Boundary Scan                                               | . 105 |

| 5        | Monitor Commands                                            | 110   |

| 5.1      | MON-0 - Exchanging EOC Information                          |       |

| 5.2      | MON-2 - Exchanging Overhead Bits                            |       |

| 5.2      | MON-8 - Local Functions                                     |       |

| 5.5      | WON-0 - Local Fullotions                                    |       |

| 6        | Register Description                                        | . 117 |

| 6.1      | Register Summary                                            |       |

|          | 118                                                         |       |

| 6.2      | Reset of U-Transceiver Functions in State 'Deactivated'     |       |

| 6.3      | Mode Register Evaluation Timing                             |       |

| 6.4      | Detailed Register Description                               |       |

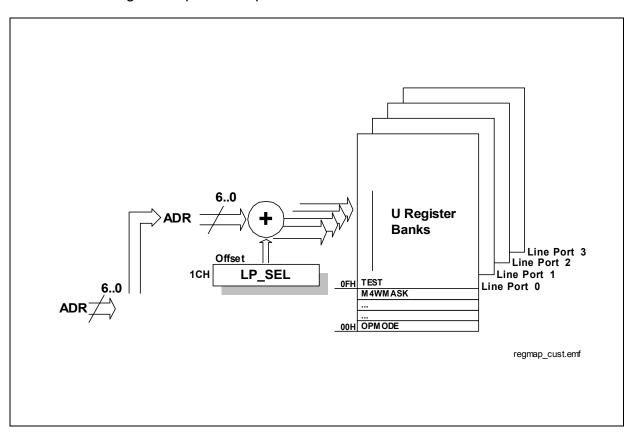

| 6.4.1    | LP_SEL - Line Port Selection Register                       | . 121 |

# **PEF 24911**

| Table of                                                                       | Contents                                                                                                                                                                                                                                                                                                      | Page                                                        |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8<br>6.4.9<br>6.4.10 | OPMODE - Operation Mode Register MFILT - M-Bit Filter Options M4RMASK - M4 Read Mask Register M4WMASK - M4 Write Mask Register TEST - Test Register LOOP - Loop Back Register FEBE - Far End Block Error Counter Register NEBE - Near End Block Error Counter Register BERC - Bit Error Rate Counter Register | . 122<br>. 125<br>. 127<br>. 129<br>. 130<br>. 132          |

| 7 7.1 7.2 7.3 7.4 7.4.1 7.4.2 7.4.3 7.4.4 7.5 7.6 7.6.1 7.6.2                  | Electrical Characteristics Absolute Maximum Ratings Operating Range DC Characteristics AC Characteristics Reset Timing IOM®-2 Interface Timing Interface to the Analog Front End Boundary Scan Timing Capacitances Power Supply Supply Voltage Power Consumption                                              | 133<br>134<br>134<br>135<br>136<br>137<br>138<br>139<br>139 |

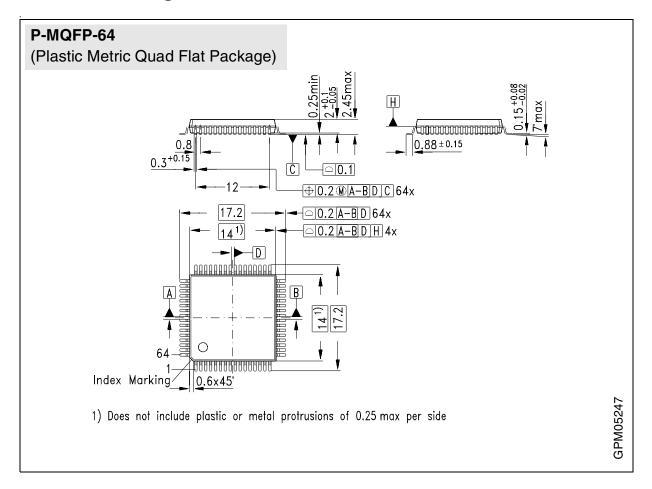

| 8                                                                              | Package Outlines                                                                                                                                                                                                                                                                                              | . 140                                                       |

| 9                                                                              | Appendix A: Standards and Specifications                                                                                                                                                                                                                                                                      | . 141                                                       |

| 10                                                                             | Glossary                                                                                                                                                                                                                                                                                                      | . 142                                                       |

| List of Figur | es                                                           | Page |

|---------------|--------------------------------------------------------------|------|

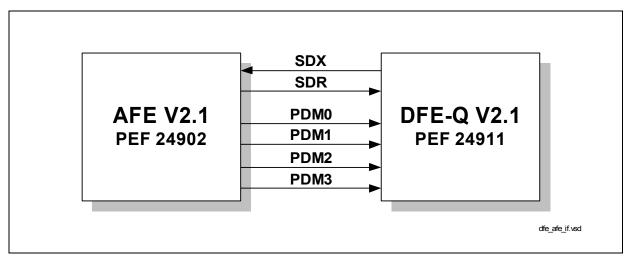

| Figure 1      | DFE-Q/ AFE 2nd Generation Chip Set                           | 1    |

| Figure 2      | Logic Symbol                                                 |      |

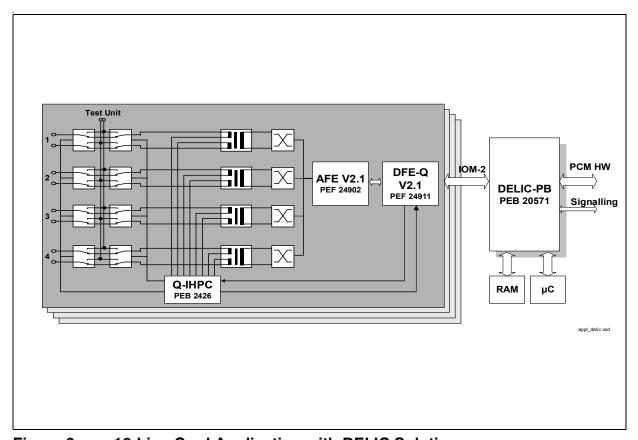

| Figure 3      | 16-Line Card Application with DELIC Solution                 | 5    |

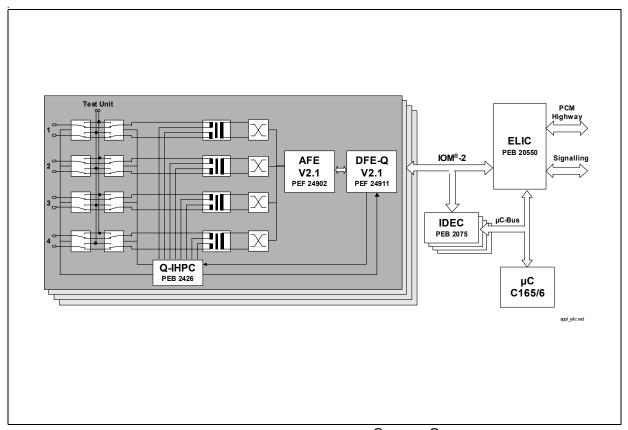

| Figure 4      | 16-Line Card Application with ELIC®/ IDEC® Solution          | 6    |

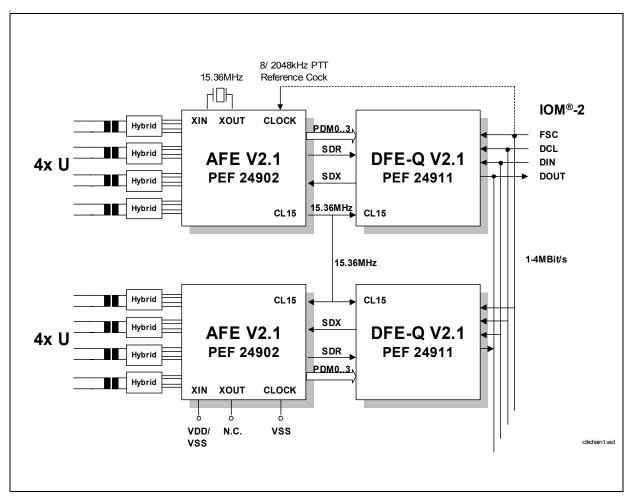

| Figure 5      | Connecting Two AFE/DFE-Q Chip Sets                           | 7    |

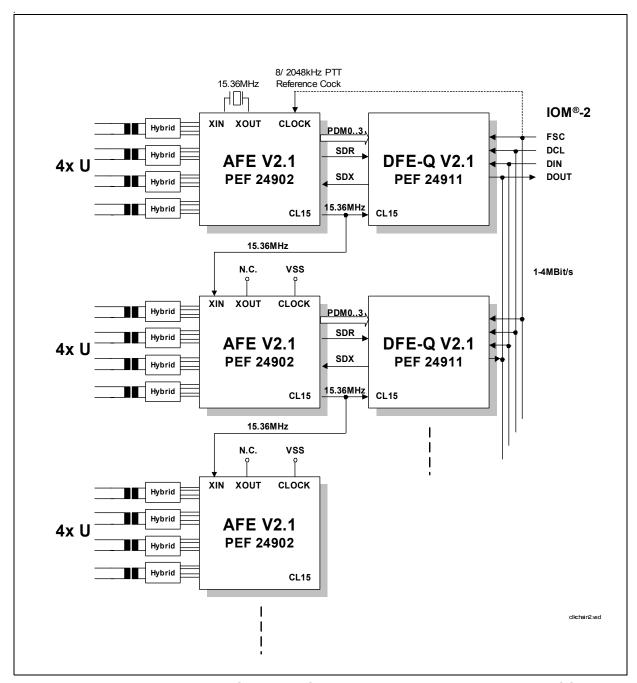

| Figure 6      | Recommended Clocking Scheme for More Than Two DFE-Q/AFE      | Chip |

| S             | ets 8                                                        |      |

| Figure 7      | Pin Configuration (63 of 64 used)                            | 11   |

| Figure 8      | Block Diagram and Data Flow (DFE-Q V2.1 + AFE V2.1)          | 20   |

| Figure 9      | Clock Supply and Data Exchange between Master and Slave      | 21   |

| Figure 10     | Multiplexed Frame Structure of the IOM®-2 Interface          | 23   |

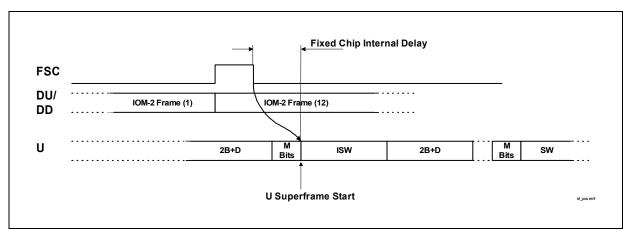

| Figure 11     | Superframe Marker                                            | 24   |

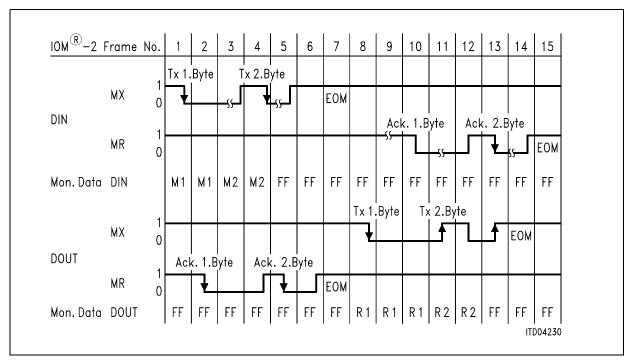

| Figure 12     | Handshake Protocol with a 2-Byte Monitor Message/Response    | 26   |

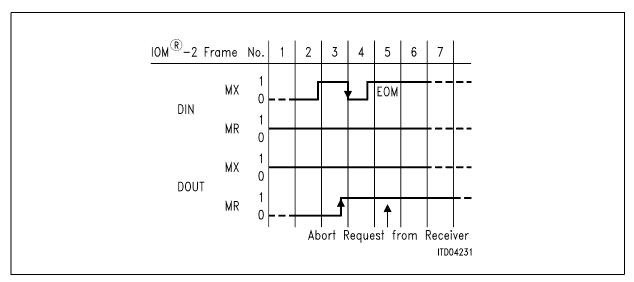

| Figure 13     | Abortion of Monitor Channel Transmission                     | 28   |

| Figure 14     | Interface to the Analog Front End                            | 30   |

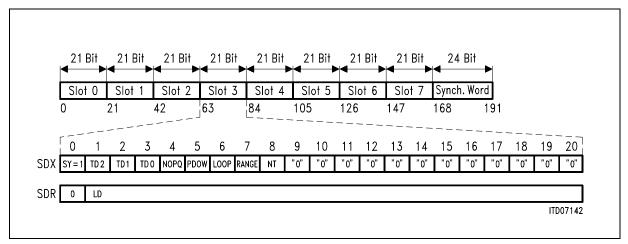

| Figure 15     | Frame Structure on SDX/SDR                                   | 31   |

| Figure 16     | U-Superframe Structure                                       | 34   |

| Figure 17     | U-Basic Frame Structure                                      | 35   |

| Figure 18     | MON-0/2 - M-Bit Correspondence                               | 37   |

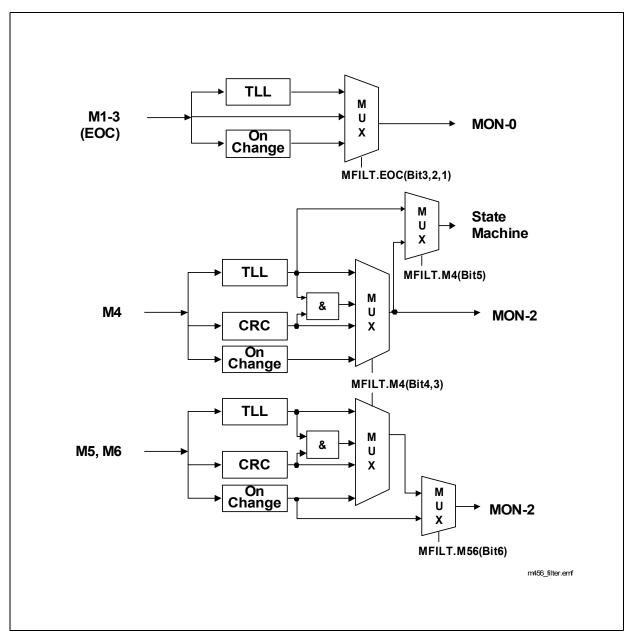

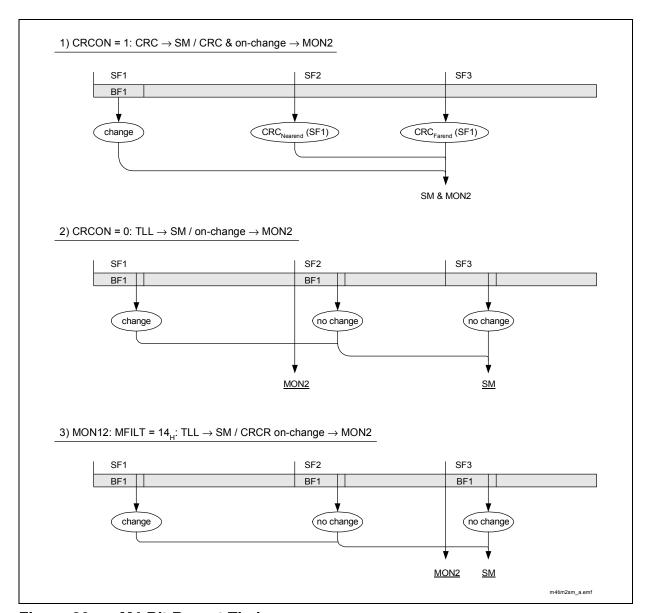

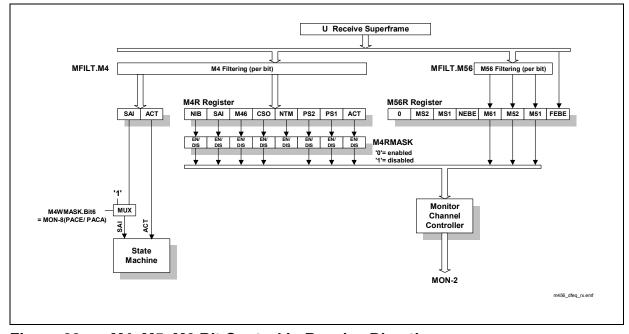

| Figure 19     | Maintenance Channel Filtering Options                        | 40   |

| Figure 20     | M4 Bit Report Timing                                         | 41   |

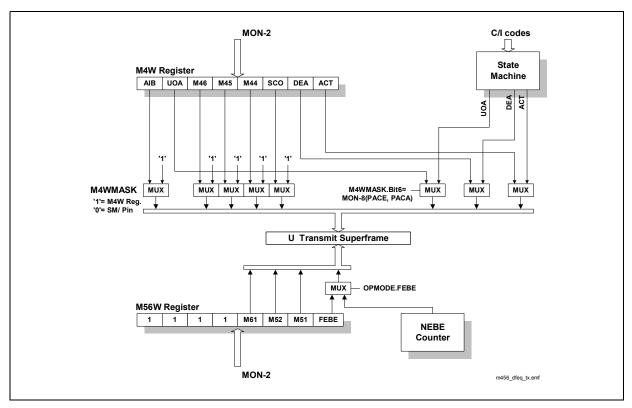

| Figure 21     | M4, M5, M6 Bit Control in Transmit Direction                 | 44   |

| Figure 22     | M4, M5, M6 Bit Control in Receive Direction                  | 44   |

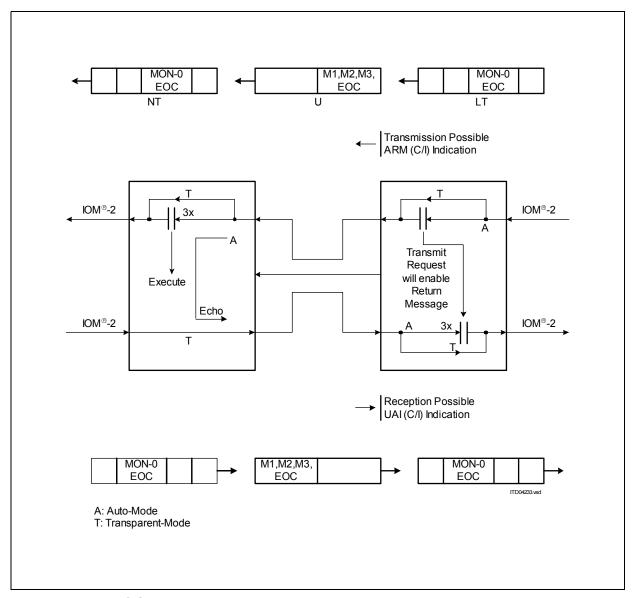

| Figure 23     | EOC-Procedure in Auto- and Transparent Mode                  | 49   |

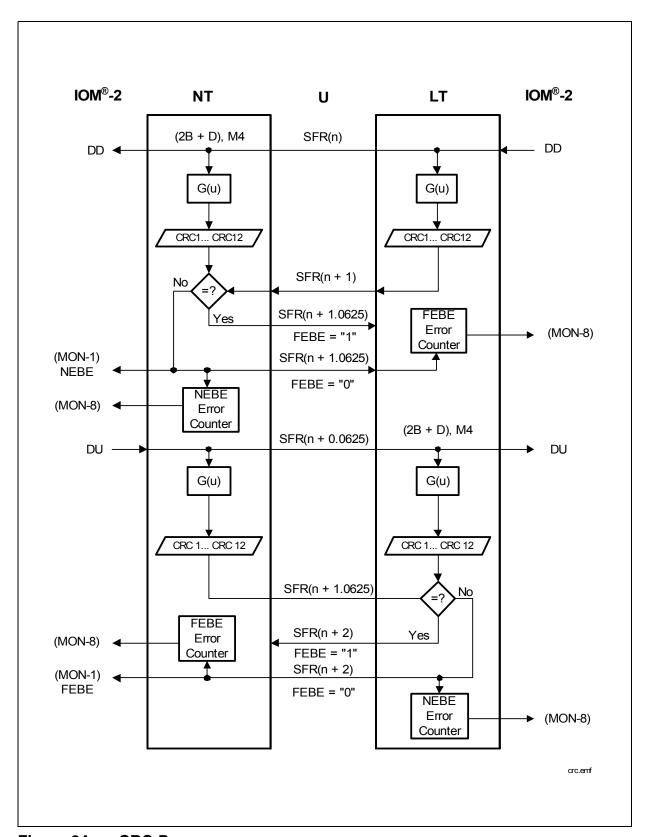

| Figure 24     | CRC-Process                                                  | 51   |

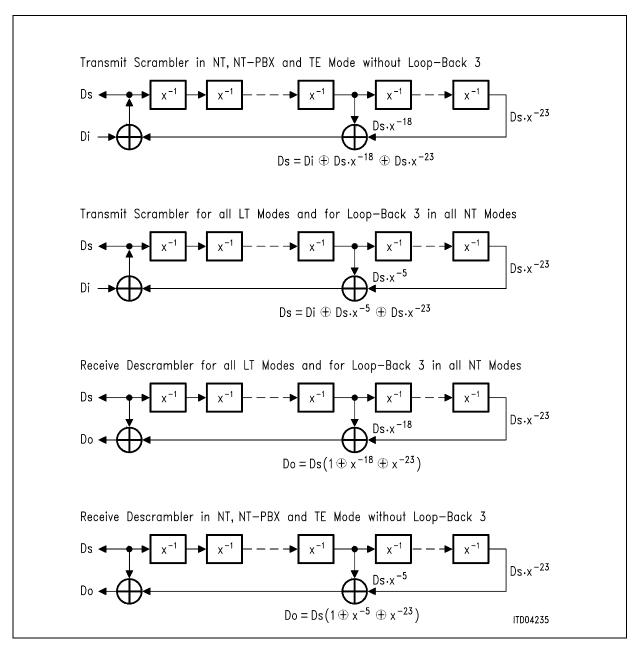

| Figure 25     | Scrambler/ Descrambler Algorithms                            | 52   |

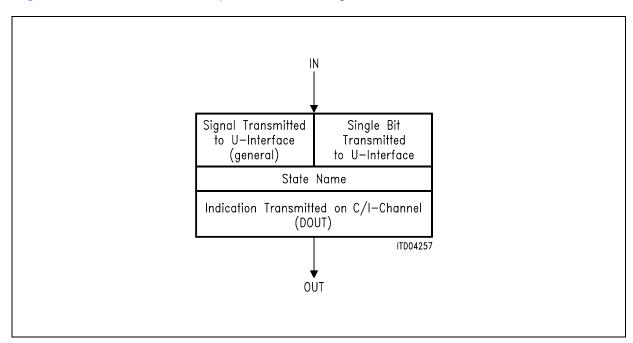

| Figure 26     | Explanation of the State Diagram                             | 55   |

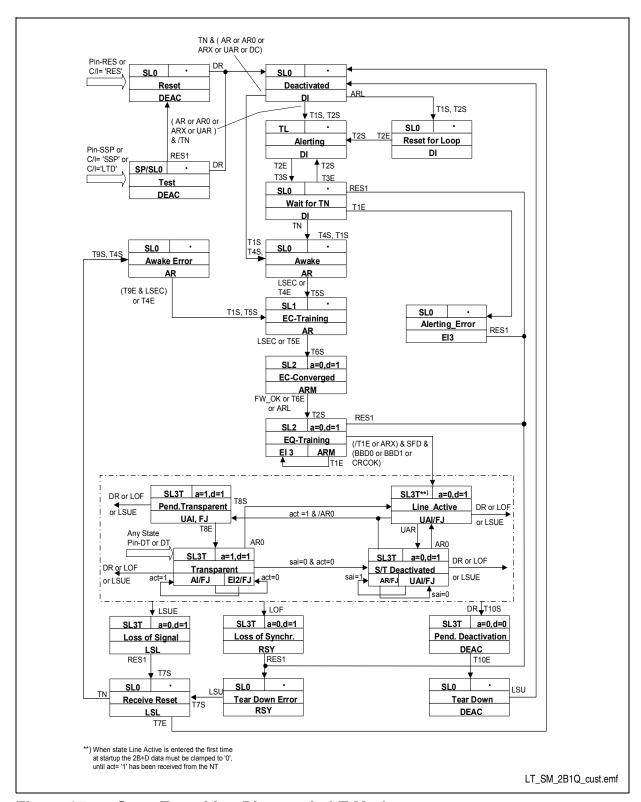

| Figure 27     | State Transition Diagram in LT-Mode                          | 57   |

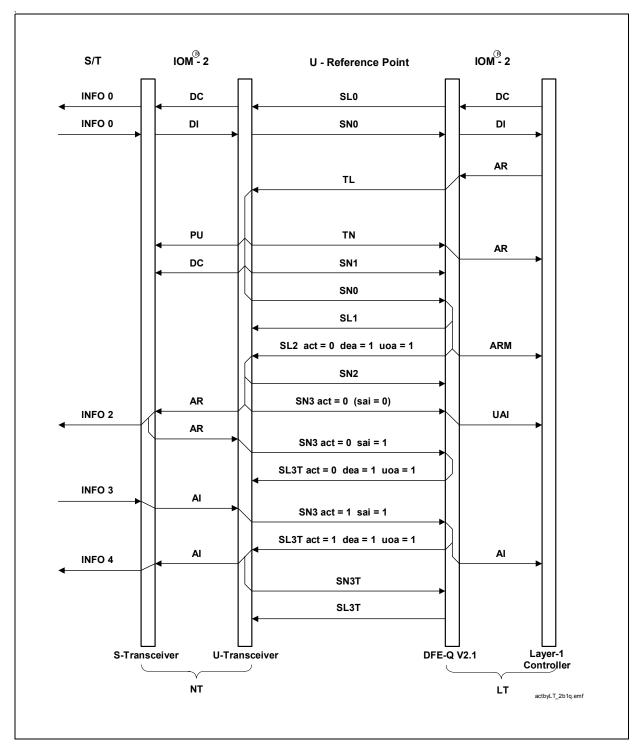

| Figure 28     | Complete Activation Initiated by LT                          | 73   |

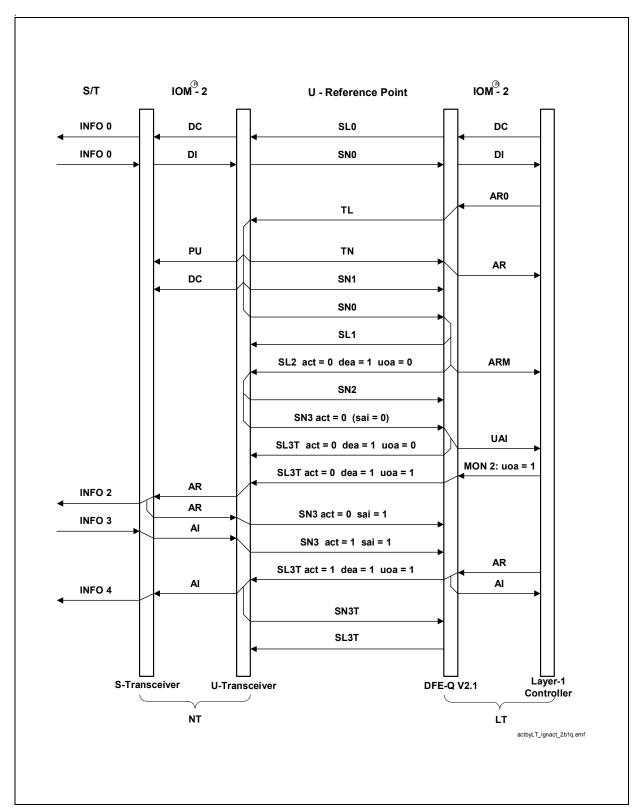

| Figure 29     | Activation with ACT-Bit Status Ignored by the Exchange       | 75   |

| Figure 30     | Complete Activation Initiated by TE                          | 77   |

| Figure 31     | Complete Deactivation                                        | 79   |

| Figure 32     | U Only Activation                                            | 81   |

| Figure 33     | LT Initiated Activation with U-Interface Active              | 82   |

| Figure 34     | TE-Activation with U Active and Exchange Control (case 1)    | 84   |

| Figure 35     | TE-Activation with U Active and no Exchange Control (case 2) | 86   |

| Figure 36     | Deactivation of S/T Only                                     | 87   |

| Figure 37     | Test Loopbacks                                               | 88   |

| Figure 38     | Complete Loopback Options in the NT                          | 91   |

| Figure 39     | Loopbacks Featured by Register LOOP                          | 96   |

| Figure 40     | Block Error Counter Test                                     |      |

| Figure 41     | Total Power Measurement Set-Up                               | 104  |

# **PEF 24911**

| List of Figures |                                    | Page  |  |

|-----------------|------------------------------------|-------|--|

| Figure 42       | DFE-Q V2.1 Register Map            | . 117 |  |

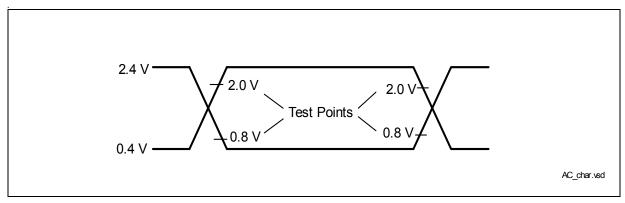

| Figure 43       | Input/Output Waveform for AC Tests | . 135 |  |

| Figure 44       | Reset Timing                       | . 135 |  |

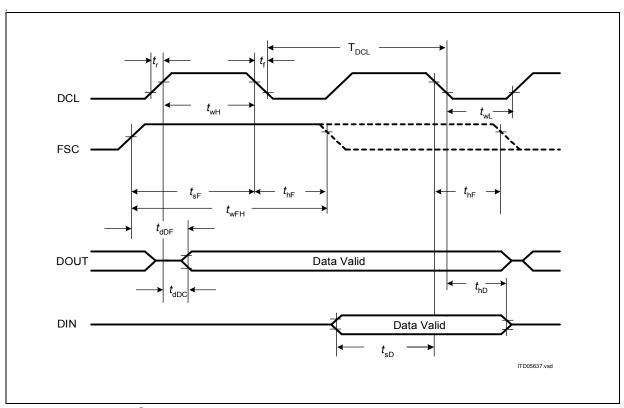

| Figure 45       | IOM®-2 Interface Timing            | . 136 |  |

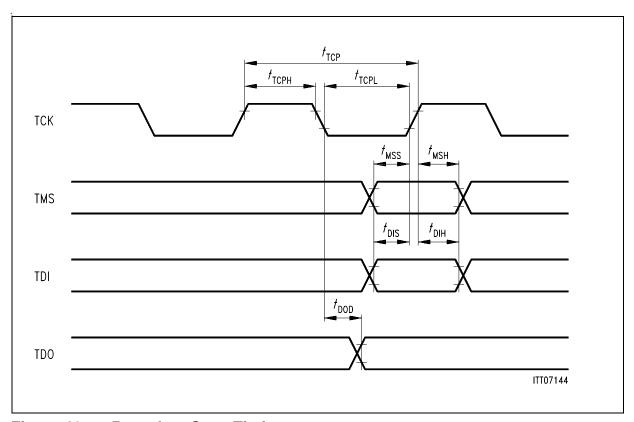

| Figure 46       | Boundary Scan Timing               | . 138 |  |

# **PEF 24911**

| List of Tab | les                                                  | Page           |

|-------------|------------------------------------------------------|----------------|

| Table 1     | Pin Definitions and Functions                        | 12             |

| Table 2     | Pinning Changes                                      | 19             |

| Table 3     | IOM®-2 Data Rates                                    | 22             |

| Table 4     | Assignments of IOM® Channels to Time-Slots No. on SE | X/SDR and Line |

|             | Ports No. 30                                         |                |

| Table 5     | 2B1Q Coding Table                                    | 32             |

| Table 6     | 2B1Q U-Frame Structure                               |                |

| Table 7     | Overhead Bits Filter Setting by CRCON Pin            | 40             |

| Table 8     | Supported EOC-Commands                               | 46             |

| Table 9     | 2B1Q Coding Table                                    | 53             |

| Table 10    | Command / Indicate Codes (2B1Q)                      |                |

| Table 11    | Timers Used in LT-Modes                              | 61             |

| Table 12    | U-Interface Signals                                  |                |

| Table 13    | Boundary Scan Cells                                  |                |

| Table 14    | TAP Controller Instructions:                         |                |

| Table 15    | MON-0 Functions                                      |                |

| Table 16    | MON-2 and Overhead Bits                              |                |

| Table 17    | MON-8-Local Function Commands                        |                |

| Table 18    | Register Map Reference Table                         |                |

| Table 19    | IOM®-2 Dynamic Input Characteristics                 |                |

| Table 20    | IOM®-2 Dynamic Output Characteristics                |                |

| Table 21    | Interface Signals of AFE and DFE-Q                   |                |

| Table 22    | Boundary Scan Dynamic Timing Requirements            |                |

| Table 23    | Power Consumption                                    | 139            |

## 1 Introduction

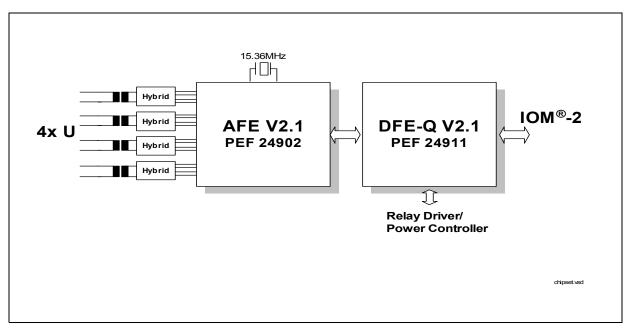

The Quad ISDN 2B1Q Echocanceller Digital Front End (DFE-Q) is the digital part of an optimized two-chip solution featuring 4x ISDN basic rate access and IDSL access at 144 kbit/s. The PEF 24911 is designed to provide in conjunction with the Quad ISDN Echocanceller Analog Front End (PEF 24902 V2.1) full duplex data transmission at the U-reference point according to ANSI T1.601 (1998), ETSI TS 102 080 (1998) and ITU-T G.961 standards.

The DFE-Q 2nd generation has been completely reengineered to guarantee the availability of the well proved DFE-Q/AFE solution over the year 2000. The PEF 24911 V2.1 is downwards pin compatible and functionally equivalent to the DFE-Q V1.x. Thus, line card manufacturers can make use of the most advanced process technology without the need to change their current design (besides the changeover to 3.3 V power supply).

No software changes are required if the DFE-Q V2.1 is deployed in existing DFE-Q V1.x solutions. Some new features are provided such as free programmable filtering options for the maintenance bits (M1-6) and enhanced monitoring and test functions. The data rate is programmable from 1 Mbit/s to 4 Mbit/s.

Figure 1 DFE-Q/ AFE 2nd Generation Chip Set

The output and input pins are throughout 5 V TTL compatible although the PEF 24911 is processed in advanced 3.3 V CMOS technology. A power down state with very low power consumption is featured.

The PEF 24911 comes in a P-MQFP-64 package.

# Quad ISDN 2B1Q Echocanceller Digital Front End DFE-Q V2.1

PEF 24911

#### Version 2.1

#### 1.1 Features

#### **U-Interface**

- Digital part of a two-chip solution featuring full duplex data transmission and reception over two-wire metallic subscriber loops providing 4x ISDN basic rate access or IDSL access at 144 kbit/s

- Conforms to:

- ANSI T1.601-1998

- ETSI TS 102 080 (1998)

- Recommendation ITU-T G.961

- 2B1Q-block code (2 binary, 1 quaternary) at 80-kHz symbol rate

- LT mode

- Data rate of the system interface programmable

- Activation/ deactivation controller

- 15 s start-up guard timer (T1) can be disabled for use in repeater applications

- Adaptive echo cancellation and equalization

- Automatic gain control and polarity adaptation

- Clock recovery (frame and bit synchronization) in all applications

- Built-in wake-up unit for activation from power-down state.

#### **System Interface**

- IOM®-2 interface with programmable data rates (1 Mbit/s to 4 Mbit/s)

- SW controlled I/O ports for relay driver and power feeder control

- 4 relay driver pins per port

- 2 status pins per port

| Туре      | Package   |

|-----------|-----------|

| PEF 24911 | P-MQFP-64 |

#### **Others**

- Software compatible to PEF 24911 V1.3 (Quad IEC DFE-Q)

- Inputs and outputs 5 V TTL compatible

- DOUT (open drain) accepts pull-up to 3.3 V or 5 V

- +3.3 V ±0.3 V Power Supply

- Advanced low power CMOS technology

- Extended temperature range (– 40...to 85 °C)

- Boundary-Scan, JTAG IEEE 1149.1

## Add-On Features and Differences with Respect to DFE-Q V1.3/V1.2/V1.1

- Max. IOM<sup>®</sup>-2 data rate 4 Mbit/s (DCL= 8 MHz)

- +3.3 V instead of +5 V power supply

- Dedicated pins for SSP and DT test modes

- DOUT configurable either as open drain or push-pull (tristate) output

- New MON-12 class features internal register access

- Coefficients retrievable by MON-12 commands instead of MON-8 commands

- Advanced filter options for MON-0 and MON-2 messages

- Bit Error Rate measurement per port

- Additional digital local loops

- C/I codes 'LTD' and 'HI' are no more supported

- Optimized LT-state machine

- JTAG Boundary-Scan with dedicated reset line TRST (replaces power-on reset functionality)

#### **Addressed Applications**

- ISDN Line Cards for Central Office

- ISDN Line Cards for Access Networks

- ISDN Line Cards in PBX Systems

- IDSL Line Cards

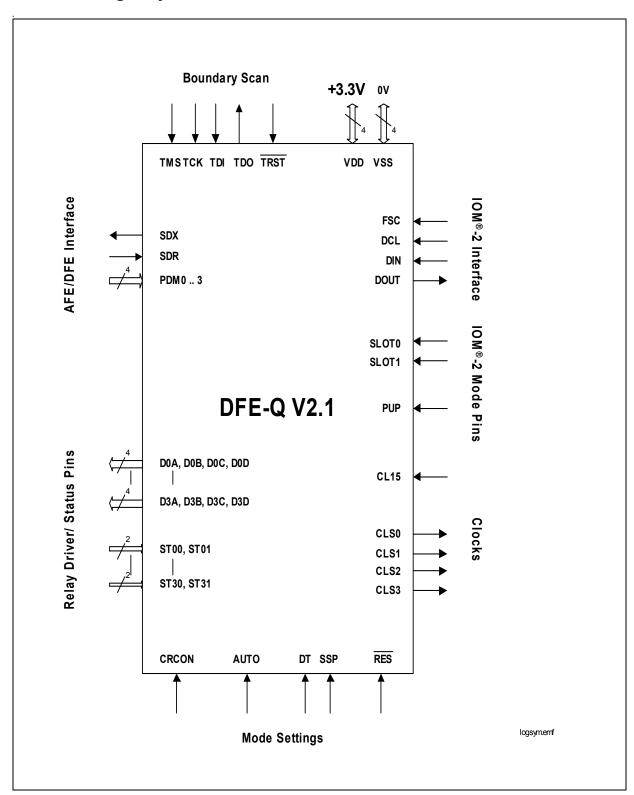

# 1.2 Logic Symbol

Figure 2 Logic Symbol

## 1.3 System Integration

This paragraph shows how the DFE-Q V2.1 may be integrated in systems using other Infineon ISDN devices. The PEF 24911 DFE-Q is optimized for use in the following applications:

- Digital Line Cards for Central Office

- Digital Line Cards for Access Networks (LT mode only)

- PBX applications (LT mode only)

**Figure 3** and **Figure 4** illustrate line card solutions with various Infineon line card controllers. The DELIC-PB (PEB 20571) supersedes the ELIC<sup>®</sup> (PEB 20550) and will feature up to 32 HDLC controllers on-chip.The DELIC controls up to 4 devices of DFE-Q V2.1 on a single IOM<sup>®</sup>-2 interface. In this application an additional clock doubler is necessary to generate the 8.192 MHz DCL clock for the DFE-Q derived from the 4.096 MHz BCL clock of the DELIC.

Figure 3 16-Line Card Application with DELIC Solution

Figure 4 16-Line Card Application with ELIC®/ IDEC® Solution

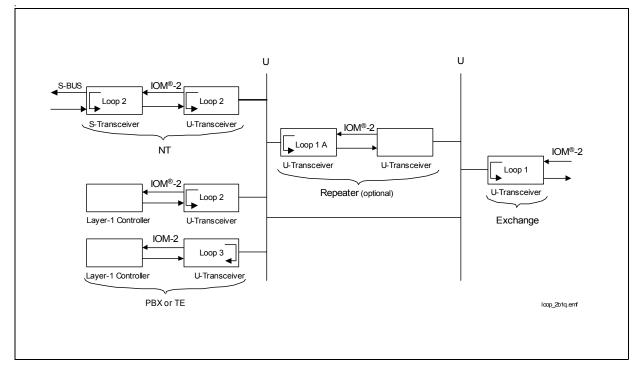

**Figure 5** shows how an 8 channel line card application is realized by use of two AFE/DFE-Q chip sets:

One AFE-PLL generates the synchronized 15.36 MHz clock and provides the master clock at pin CL15 for the other 3 devices. The internal PLL of the first AFE synchronizes the 15.36 MHz master clock onto a PTT reference clock of either 8 kHz or 2048 kHz. Infineon recommends to feed the FSC clock input of the DFE-Q V2.1 and the PLL reference clock input (pin CLOCK) of the AFE from the same clock source.

The PLL of the second AFE is deactivated. The 15.36 MHz master clock is applied at pin CL15. CL15 is configured as input if XIN is clamped either to VDD or to VSS. Pin XOUT has to be left open and CLOCK shall be tied to GND.

Figure 5 Connecting Two AFE/DFE-Q Chip Sets

The DFE-Q devices are supplied by the first AFE at pin CL15 with the synchronized 15.36 MHz clock. The IOM<sup>®</sup>-2 channels the DFE-Q devices are assigned to can be programmed by the two slot pins. Starting from channel no. 0/4/8/12 always four subsequent channels are occupied.

Alternatively the clocking scheme as shown in **Figure 6** may be applied if more than 3 devices are to be clocked (e.g. in a 16-channel line card application). Instead to supply the 2nd AFE with the master clock at pin CL15, here the 15.36 MHz master clock is input at pin XIN. Thereby pin CL15 is configured as output and passes the 15.36 MHz clock on to the attached DFE-Q. If the clock chain is extended in the same way by another two AFE/DFE-Q chip sets a 16-channel line card application can be realized with just one single crystal. Note that the 15.36 MHz clock is inverted once by the AFE if it is input at XIN and output at CL15. This way the duty cycle is recovered again.

Figure 6 Recommended Clocking Scheme for More Than Two DFE-Q/AFE Chip Sets

## 1.4 Operational Overview

The DFE-Q V2.1 operates always in LT mode. Other operating modes known from former versions of the DFE-Q are not further supported.

## **System Interface Configurations**

The following parameters of the system interface are configurable:

- Open Drain/ Push-Pull Mode

Configured as open drain the output pin DOUT is floating and a pull-up resistor is required. In push-pull mode the output pin is high impedance outside the active time slots.

- IOM®-2 Channel Assignment

- IOM<sup>®</sup>-2 channels are always assigned in blocks of four.

| SLOT1 | SLOT0 | Assigned IOM®-2 Channels |

|-------|-------|--------------------------|

| 0     | 0     | 03                       |

| 0     | 1     | 4 7                      |

| 1     | 0     | 8 11                     |

| 1     | 1     | 12 15                    |

# IOM<sup>®</sup>-2 Data Rates

| DCL Frequency<br>[kHz] | Data Rate<br>[kBit/s] | IOM <sup>®</sup> -2 Channels |

|------------------------|-----------------------|------------------------------|

| 2048                   | 1024                  | 4                            |

| 3072                   | 1536                  | 6                            |

| 4096                   | 2048                  | 8                            |

| 6144                   | 3072                  | 12                           |

| 8192                   | 4096                  | 16                           |

## **Send Single Pulses Test Mode**

In test mode 'Send Single Pulses' +/-3 pulses spaced by 1.5 ms are transmitted on all U lines. The test mode is activated by pin SSP= set to '1'. The SSP test function can be as well stimulated by C/I= SSP besides the fact that the HW selection impacts all line ports while the SW selection impacts only the chosen line.

## **Data Through Mode**

In test mode 'Data Through' the U-transceiver is forced to enter the 'Transparent' state and to issue SL3T (see **Table 12**) independently of the wake-up protocol. The DT test mode is activated by pin DT= set to '1'. The DT test function can be as well stimulated by C/I= DT besides the fact that the HW selection impacts all line ports while the SW selection impacts only the chosen line.

# 2 Pin Descriptions

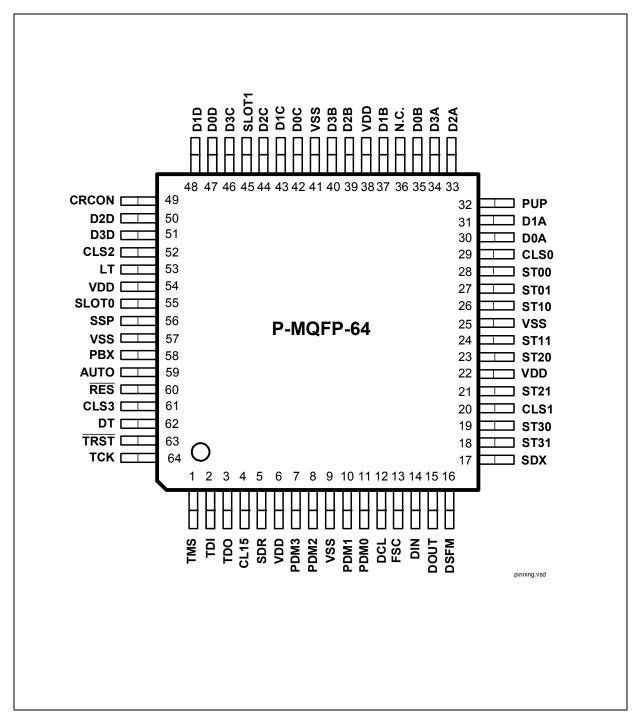

# 2.1 Pin Diagram

(top view)

Figure 7 Pin Configuration (63 of 64 used)

# 2.2 Pin Definitions and Functions

| Table 1 | Pin Definitions and Functions |

|---------|-------------------------------|

| Iabici  |                               |

| Pin No. | Symbol | Input (I)<br>Output (O) | Function |

|---------|--------|-------------------------|----------|

|         |        |                         |          |

# IOM®-2 Interface

| iOivi°-2 inter | OM 2 Interrace |                   |                                                                                                                                                        |  |  |

|----------------|----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 13             | FSC            | 1                 | Frame Synchronization Clock (8kHz) the start of the first B1-channel in time-slot 0 is marked, FSC is expected to be '1' for at least two DCL periods. |  |  |

| 12             | DCL            | 1                 | Data Clock<br>clock rate ranges from 2048 to 8192 kHz<br>(1024 to 4096 kBit/s)                                                                         |  |  |

| 14             | DIN            | 1                 | Data In input of IOM®-2 data synchronous to DCL clock                                                                                                  |  |  |

| 15             | DOUT           | O<br>(OD/<br>PuP) | Data Out output of IOM®-2 data synchronous to DCL clock                                                                                                |  |  |

## **Mode Selection Pins**

| 60 | RES   | I    | Reset triggers asynchronous HW reset, Schmitt trigger input '1'= inactive '0'= active                                                                                                                    |

|----|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55 | SLOT0 | I    | IOM®-2 Channel Slot Selection 0 assigns IOM®-2 channels in blocks of 4  SLOT1, 0: '00'= IOM®-2 channels 0 to 3 '01'= IOM®-2 channels 4 to 7 '10'= IOM®-2 channels 8 to 11 '11'= IOM®-2 channels 12 to 15 |

| 45 | SLOT1 | (PD) | IOM <sup>®</sup> -2 Channel Slot Selection 1 assigns IOM <sup>®</sup> -2 channels in blocks of 4                                                                                                         |

Table 1

Pin Definitions and Functions (cont'd)

| marker on FSC. I.e the transmitted super- frame is not affected by an FSC pulse shorter than 2 DCL clock periods. '0' = The position of the transmitted superframe is synchronized to short FSC pulses.  32 PUP I Push Pull Mode in push pull mode '0' and '1' is actively driver during an occupied time slot, outside the active time slots DOUT is high impedance (tristate) '1'= configures DOUT as push/pull output '0'= configures DOUT as open drain output  49 CRCON I (PD) CRC Check On/Off defines the condition on which MON-2 messages and M4 bit will be passed on, the setting has effect on all ports (see Table 7). Pin CRCON is evaluated only after hardware reset. '1'= CRC Check On MON-2 messages are not issued and M4-bit are not forwarded to the statemachine if the CRC-check of the U-superframe containing M4-bit changes is not ok. (MFILT= 0011 0xxx) '0'= CRC Check Off MON-2 messages are issued every time a change in at least one of the overhead bits (M4,5,6) of the U-interface is detected, regardless of the CRC checksum status. | Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| in push pull mode '0' and '1' is actively driver during an occupied time slot, outside the active time slots DOUT is high impedance (tristate) '1'= configures DOUT as push/pull output '0'= configures DOUT as open drain output  49  CRCON  CRC Check On/Off defines the condition on which MON-2 messages and M4 bit will be passed on, the setting has effect on all ports (see Table 7). Pin CRCON is evaluated only after hardware reset. '1'= CRC Check On MON-2 messages are not issued and M4-bit are not forwarded to the statemachine if the CRC-check of the U-superframe containing M4-bit changes is not ok. (MFILT= 0011 0xxx) '0'= CRC Check Off MON-2 messages are issued every time a change in at least one of the overhead bits (M4,5,6) of the U-interface is detected, regardless of the CRC checksum status. M4-bit are forwarded to the statemachine with triple-last-look filtering (TLL). (MFILT= 0000 0xxx)                                                                                                                                    | 16      | DSFM   | I<br>(PD)               | '1' = Inhibits the evaluation of the super frame marker on FSC. I.e the transmitted super-frame is not affected by an FSC pulse shorter than 2 DCL clock periods. '0' = The position of the transmitted superframe is synchronized to short FSC                                                                                                                                                                                                                                                                                                                                                                                                          |

| defines the condition on which MON-2 messages and M4 bit will be passed on, the setting has effect on all ports (see Table 7). Pin CRCON is evaluated only after hardware reset. '1'= CRC Check On MON-2 messages are not issued and M4-bit are not forwarded to the statemachine if the CRC-check of the U-superframe containing M4-bit changes is not ok. (MFILT= 0011 0xxx) '0'= CRC Check Off MON-2 messages are issued every time a change in at least one of the overhead bits (M4,5,6) of the U-interface is detected, regardless of the CRC checksum status. M4-bit are forwarded to the statemachine with triple-last-look filtering (TLL). (MFILT= 0000 0xxx)                                                                                                                                                                                                                                                                                                                                                                                                   | 32      | PUP    | -                       | in push pull mode '0' and '1' is actively driven during an occupied time slot, outside the active time slots DOUT is high impedance (tristate) '1'= configures DOUT as push/pull output                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 53 LT I reserved, clamp to high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 49      | CRCON  | I<br>(PD)               | defines the condition on which MON-2 messages and M4 bit will be passed on, the setting has effect on all ports (see Table 7).  Pin CRCON is evaluated only after hardware reset.  '1'= CRC Check On MON-2 messages are not issued and M4-bit are not forwarded to the statemachine if the CRC-check of the U-superframe containing M4-bit changes is not ok.  (MFILT= 0011 0xxx)  '0'= CRC Check Off MON-2 messages are issued every time a change in at least one of the overhead bits (M4,5,6) of the U-interface is detected, regardless of the CRC checksum status. M4-bit are forwarded to the statemachine with triple-last-look filtering (TLL). |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53      | LT     | I                       | reserved, clamp to high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 1

Pin Definitions and Functions (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                      |

|---------|--------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 58      | PBX    | I                       | reserved, clamp to low                                                                                                                                                                                                                                                                                                                                                        |

| 59      | AUTO   |                         | EOC Auto Mode selects auto or transparent mode for EOC channel processing, the setting has effect on all ports '1'= EOC auto mode (MFILT= xxxx x100) '0'= EOC transparent mode (MFILT= xxxx x001)                                                                                                                                                                             |

| 56      | SSP    |                         | Send Single Pulses (SSP) Test Mode '1'= alternating +/-3 pulses are issued at all line ports in 1.5 ms intervals '0'= deactivated, clamp to GND if not used This pin function corresponds to the SW selection by C/I= SSP besides the fact that the HW selection impacts all line ports while the SW selection impacts only the chosen line                                   |

| 62      | DT     |                         | Data Through (DT) Test Mode enables/disables DT test mode '1'= DT test mode enabled, the U-transceiver is forced on all line ports to enter the 'Transparent' state '0'= DT test mode disabled This pin function corresponds to the SW selection by C/I= DT besides the fact that the HW selection impacts all line ports while the SW selection impacts only the chosen line |

# Interface to the Analog Front End

| 4  | CL15 | I | 15.36 MHz Master Clock Input                                                                                                                                                        |

|----|------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | PDM0 | I | Pulse Density Modulated Receive Data of Line<br>Port 0<br>pulse density modulated bit stream from the<br>PEF 24902 Quad AFE that is output from the<br>second-order sigma-delta ADC |

Table 1

Pin Definitions and Functions (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                 |

|---------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10      | PDM1   | I                       | Pulse Density Modulated Receive Data of Line<br>Port 1<br>pulse density modulated bit stream from the<br>PEF 24902 Quad AFE that is output from the<br>second-order sigma-delta ADC                                                                                                                                                      |

| 8       | PDM2   | I                       | Pulse Density Modulated Receive Data of Line<br>Port 2<br>pulse density modulated bit stream from the<br>PEF 24902 Quad AFE that is output from the<br>second-order sigma-delta ADC                                                                                                                                                      |

| 7       | PDM3   | I                       | Pulse Density Modulated Receive Data of Line<br>Port 3<br>pulse density modulated bit stream from the<br>PEF 24902 Quad AFE that is output from the<br>second-order sigma-delta ADC                                                                                                                                                      |

| 5       | SDR    | I                       | Serial Data Receive Line interface signal from the PEF 24902 Quad AFE that transports level detect information for the wake-up recognition of all 4 lines by use of TDM                                                                                                                                                                  |

| 17      | SDX    | 0                       | Serial Data Transmit Line interface to the PEF 24902 Quad AFE for the transmit and control data. Transmission is based on clock CL15 (15.36 Mbit/s). For each line port the following bits are exchanged: TD0, TD1: Transmit data RANGE: Range select LOOP: Analog loopback switch PDOW: Power down/power up Synchronization information |

| Table 1         Pin Definitions and Functions (cont'd) |                          |                         |                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------|--------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                                                | Symbol                   | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                  |

| Relay Driver                                           | / Status Pii             | ns                      |                                                                                                                                                                                                                                                                                                           |

| 30,<br>35,<br>42,<br>47                                | DOA<br>DOB<br>DOC<br>DOD | O                       | Relay Driver Pins of Line Port 0 addressable via MON-8 command in IOM®-2 channel 0/4/8/12. The logic values of the bit positions A,B,C, D of the MON-8 command 'SETD' determine the output setting. Default value after pin-reset is low. C/I-code reset does not affect the current status.              |

| 31,<br>37,<br>43,<br>48                                | D1A<br>D1B<br>D1C<br>D1D | O                       | Relay Driver Pins of Line Port 1 addressable via MON-8 command in IOM <sup>®</sup> -2 channel 1/5/9/13. The logic values of the bit positions A,B,C, D of the MON-8 command 'SETD' determine the output setting. Default value after pin-reset is low. C/I-code reset does not affect the current status. |

| 33,<br>39,<br>44,<br>50                                | D2A<br>D2B<br>D2C<br>D2D | 0                       | Relay Driver Pins of Line Port 2 addressable via MON-8 command in IOM®-2 channel 2/6/10/14.  The logic values of the bit positions A,B,C, D of the MON-8 command 'SETD' determine the output setting.  Default value after pin-reset is low. C/I-code reset does not affect the current status.           |

| 34,<br>40,<br>46,<br>51                                | D3A<br>D3B<br>D3C<br>D3D | 0                       | Relay Driver Pins of Line Port 3 addressable via MON-8 command in IOM®-2 channel 3/7/11/15.  The logic values of the bit positions A,B,C, D of the MON-8 command 'SETD' determine the output setting.  Default value after pin-reset is low. C/I-code reset does not affect the current status.           |

| 28,<br>27                                              | ST00<br>ST01             | I                       | Status Pin of Line Port 0 change of status is passed to $IOM^{\mathbb{R}}$ -2 channel $0/4/8/12$ via MON-8 message 'AST' at bit positions $S_{0}$ , $S_{1}$ . Connect to either VDD or VSS if not used.                                                                                                   |

Table 1

Pin Definitions and Functions (cont'd)

| Pin No.   | Symbol       | Input (I)<br>Output (O) | Function                                                                                                                                                                                           |

|-----------|--------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26,<br>24 | ST10<br>ST11 | I                       | Status Pin of Line Port 1 change of status is passed to $IOM^{@}$ -2 channel 1/5/9/13 via MON-8 message 'AST' at bit positions $S_{0}$ , $S_{1}$ . Connect to either VDD or VSS if not used.       |

| 23,<br>21 | ST20<br>ST21 | I                       | Status Pin of Line Port 2 change of status is passed to $IOM^{\oplus}$ -2 channel 2/6/10/14 via MON-8 message 'AST' at bit positions $S_{0,}$ $S_{1}$ . Connect to either VDD or VSS if not used.  |

| 19,<br>18 | ST30<br>ST31 | I                       | Status Pin of Line Port3 change of status is passed to $IOM^{\otimes}$ -2 channel 3/7/11/15 via MON-8 message 'AST' at bit positions $S_{0}$ , $S_{1}$ . Connect to either VDD or VSS if not used. |

# **Test Pins**

| 29 | CLS0 | 0 | 12 msec clock synchronized to the received<br>Superframe of Port 0<br>can be used for monitoring and test purposes<br>Note: The delay between both signals may |

|----|------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |      |   | vary from activation to activation.                                                                                                                            |

| 20 | CLS1 | 0 | 12 msec clock synchronized to the received Superframe of Port 1 can be used for monitoring and test purposes                                                   |

|    |      |   | Note: The delay between both signals may vary from activation to activation.                                                                                   |

| 52 | CLS2 | 0 | 12 msec clock synchronized to the received<br>Superframe of Port 2<br>can be used for monitoring and test purposes                                             |

|    |      |   | Note: The delay between both signals may vary from activation to activation.                                                                                   |

Table 1Pin Definitions and Functions (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                     |

|---------|--------|-------------------------|--------------------------------------------------------------------------------------------------------------|

| 61      | CLS3   | 0                       | 12 msec clock synchronized to the received Superframe of Port 3 can be used for monitoring and test purposes |

|         |        |                         | Note: The delay between both signals may vary from activation to activation.                                 |

# **JTAG Boundary Scan**

| 64 | TCK  | I         | Test Clock                                                                                                                                                                                                                             |

|----|------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | TMS  | (PU)      | Test Mode Select internal pullup resistor (160 $k\Omega$ )                                                                                                                                                                             |

| 2  | TDI  | (PU)      | Test Data Input internal pullup resistor (160 k $\Omega$ )                                                                                                                                                                             |

| 3  | TDO  | 0         | Test Data Output                                                                                                                                                                                                                       |

| 63 | TRST | I<br>(PU) | JTAG Boundary Scan Disable resets the TAP controller state machine (asynchronous reset), active low, internal pullup (160 k $\Omega$ ). Clamp TRST to GND if the Boundary Scan logic is not used '1'= reset inactive '0'= reset active |

# **Power Supply Pins**

| 6, 22, 38, 54 | VDD | 3.3V ±0.3V supply voltage |

|---------------|-----|---------------------------|

| 9, 25, 41, 57 | VSS | 0V ground                 |

OD: Open Drain

PuP: Push Pull

PD: Internal Pull Down (e.g.. 10 to 20 kOhms)

PU: Internal Pull Up (e.g.. 10 to 20 kOhms)

# 2.3 Pinning Changes from DFE-Q V1.3 to DFE-Q V2.1

Table 2 Pinning Changes

| Table 2 I filling Ghanges |       |       |                                                                   |  |  |  |

|---------------------------|-------|-------|-------------------------------------------------------------------|--|--|--|

| Pin No.                   | V2.1  | V1.3  | Comment                                                           |  |  |  |

| 16                        | DSFM  | TPD   | new function for suppression of short FSC evaluation              |  |  |  |

| 32                        | PUP   | N.C.  | additional push-pull mode for pin DOUT eases interface adaptation |  |  |  |

| 36                        | N.C.  | DSYNC | obsolete                                                          |  |  |  |

| 45                        | SLOT1 | N.C.  | increased max data rate requires additional SLOT pin              |  |  |  |

| 49                        | CRCON | CRCON | see Page 39                                                       |  |  |  |

| 53                        | LT    | LT    | dedicated LT mode pin is obsolete                                 |  |  |  |

| 55                        | SLOT0 | SLOT  | renamed                                                           |  |  |  |

| 56                        | SSP   | TSP   | dedicated pin for 'Send Single<br>Pulses' test mode               |  |  |  |

| 58                        | PBX   | PBX   | function removed                                                  |  |  |  |

| 62                        | DT    | TP    | dedicated pin for 'Data Through' test mode                        |  |  |  |

| 63                        | TRST  | TP1   | BScan power-on-reset is replaced by a dedicated reset line        |  |  |  |

# 3 Functional Description

#### 3.1 Functional Overview

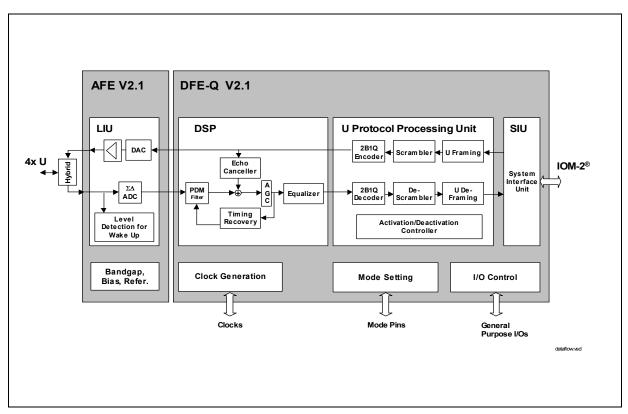

A functional overview of the DFE-Q V2.1 is given in **Figure 8**. Besides the signal processing and frame formatting blocks the PEF 24911 features an on-chip activation/ deactivation controller and programmable general purpose I/O pins for the control of test relays and power feeding circuits. An application specific DSP core services the four U-lines and cuts chip size to a minimum.

Figure 8 Block Diagram and Data Flow (DFE-Q V2.1 + AFE V2.1)

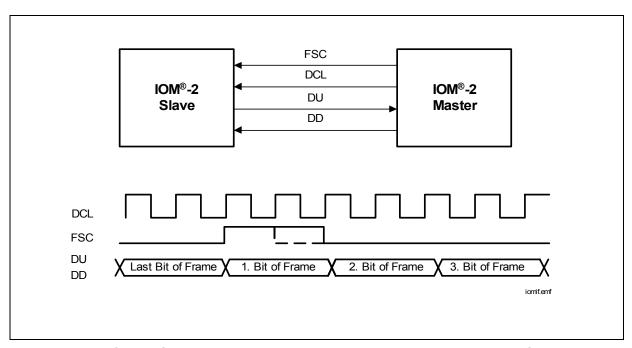

# 3.2 IOM®-2 Interface

The IOM®-2 interface is a four-wire serial interface providing a symmetrical full-duplex communication link to layer-1 and layer-2 backplane devices. It transports user data, control/programming and status information via dedicated time multiplexed channels.

The structure used follows the 2B + 1 D-channel structure of ISDN. The ISDN-user data rate of 144 kbit/s (B1 + B2 + D) on the U-interface is transmitted transparently in both directions (U <=>  $IOM^{(B)}$ ) over the interface.

Figure 9 Clock Supply and Data Exchange between Master and Slave

The **Frame Sync Signal FSC** is a 8 kHz signal delimiting the frames. This signal is used to determine the start of a frame.

The data is clocked by a **Data Clock (DCL)** which operates at twice the data rate. The data clock is a square wave signal with a duty cycle ratio of typically 1:1. Incoming data is sampled on the falling edge of the DCL-clock.

Data is carried over **Data Upstream (DU)** and **Data Downstream (DD)** signals. The upstream and downstream directions are always defined with respect to the exchange: Downstream refers to information flowing from the exchange to the subscriber, upstream is defined vice versa.

The output line is operating either as open drain or push-pull output. Both modes are selected by signal "PUP". In open drain mode an external pull-up resistor is required. The absence of a pull-up resistor is not automatically recognized (i.e. no push-pull detection).

Within one FSC-period, 128 to 512 bit are transmitted, corresponding to DCL-frequencies ranging from 2048 kHz up to 8192 kHz. The following table shows possible operating frequencies of the IOM<sup>®</sup>-2-interface.

Table 3 IOM<sup>®</sup>-2 Data Rates

| DCL Frequency<br>[kHz] | Data Rate<br>[kBit/s] | IOM <sup>®</sup> -2 Channels |

|------------------------|-----------------------|------------------------------|

| 2048                   | 1024                  | 4                            |

| 3072                   | 1536                  | 6                            |

| 4096                   | 2048                  | 8                            |

| 6144                   | 3072                  | 12                           |

| 8192                   | 4096                  | 16                           |

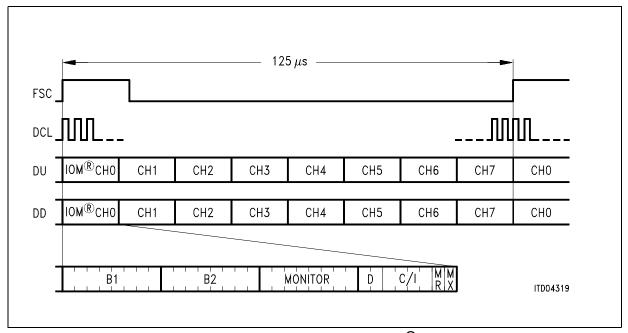

# 3.2.1 IOM®-2 Interface Frame Structure

The typical IOM<sup>®</sup>-2 line card application comprises a DCL-frequency of 4096 kHz with a nominal bit rate of 2048 kbit/s. Therefore eight channels are available, each consisting of the basic frame with a nominal data rate of 256 kbit/s. The downstream data (DD) is transferred on signal DIN, the upstream data (DU) on signal DOUT. The IOM<sup>®</sup>-2 channel assignment is programmable by pin strapping (SLOT1,0).

The basic IOM®-2 frame and clocking structure consists of:

| channel |

|---------|

| bits    |

| B1 | B2 | Monitor | D | Command / Indicate | MR | MX |

|----|----|---------|---|--------------------|----|----|

| 8  | 8  | 8       | 2 | 4                  | 1  | 1  |

- Two 64-kbit/s channels B1 and B2

- The monitor channel for transferring maintenance information between layer-1 and layer-2 devices

- Two bits for the 16-kbit/s D-channel

- Four command / indication (C/I) bits for controlling of layer-1 functions (activation/ deactivation and additional control functions) by the layer-2 controller

- Two bits MR and MX for handling the monitor channel

Figure 10 Multiplexed Frame Structure of the IOM<sup>®</sup>-2 Interface

## 3.2.2 Superframe Marker Function

The start of a new superframe is programmed by a FSC high-phase lasting for one single DCL-period. A FSC high-phase of two (or more) DCL-periods is transmitted for all other IOM<sup>®</sup>-2-frame starts.

It is optional to include superframe markers in every 96th "frame synchronization" signal. The remaining 95 FSC-clocks must be of at least two DCL-periods duration. If no superframe marker is to be used all FSC high-phases need to be of at least two DCL-periods duration.

With the SF function enabled the next outgoing basic frame on U defines the start of the U superframe by an inverted sync word (see **Figure 11**). This way the positions of the  $IOM^{\textcircled{8}}$ -2 and the U superframe are no more arbitrary but definite within a tolerance of 1.5 ms.

Figure 11 Superframe Marker

If no superframe marker is to be used, all FSC high-phases need to be of at least two DCL-periods duration.

The relationship between the IOM<sup>®</sup>-2-superframe on the LT-side, the U-frame and the IOM<sup>®</sup>-2-superframe on the NT-side is fixed after activation of the U-interface. I.e. data inserted on LT-side in the first B1-channel after the IOM<sup>®</sup>-2-slave superframe marker will always appear on NT-side with a fixed offset, e.g. in the 5th B1-channel after the master superframe marker. After a new activation this relationship (offset) may be different.

Note: The evaluation of short FSC by the DFE-Q V2.1 can be suppressed by pin DSFM (see Page 13).

# 3.2.3 IOM<sup>®</sup>-2 Command/ Indicate Channel

The Command/Indication (C/I) channel carries real-time control and status information between the DFE-Q V2.1 and a layer-1 control device. A new C/I code must be applied in six consecutive IOM<sup>®</sup>-2 frames to be considered valid, unconditional commands (i.e. RES, SSP, DT and commands in the states "Test" and "Reset") must be applied up to 2 ms before they are recognized. An indication is issued permanently by the DFE-Q V2.1 on DOUT until a new indication needs to be forwarded.

The C/I code is 4 bit wide and located at bit positions 27–30 in each time-slot. A listing and explanation of the U-transceiver C/I codes can be found on page 3-54.

# 3.2.4 IOM<sup>®</sup>-2 Monitor Channel

The Monitor channel represents a second method of initiating and reading U-transceiver specific information. Features of the monitor channel are supplementary to the command/indicate channel. Unlike the command/indicate channel with an emphasis on status control, the monitor channel provides access to internal bits (maintenance, overhead) and test functions (local loop-backs, block error counter etc.).

Besides the known MON-0/2/8 commands a new MON class, MON-12 is introduced in the DFE-Q V2.1:

#### **New MON-12 Class**

By use of MON-12 commands the DFE-Q V2.1 provides the ability to address parts of the device internal register map and thus to address functions that have been added with version 2.1. MON-12 commands are always prioritized and processed first if other Monitor commands are outstanding. See **Chapter 3.2.5** for the details.

This means that Monitor commands are split into four categories. Each category derives its name from the first nibble (4 bits) of the two byte long message. These are:

- MON-12(Internal Register Map)

- MON-0(Transparent Channel)

- MON-2(Overhead Bits)

- MON-8(Local Functions)

The order of the list above corresponds to the priority attributed to each category. MON-12 commands are always processed first. MON-0 messages will be transmitted before MON-2 messages in case several messages are initiated simultaneously. The various MON-0, MON-2 and MON-8-commands are discussed in detail in **Chapter 5**, "Monitor Commands" on Page 110.

#### **Structure**

The structure of the Monitor channel is 8 bit wide, located at bit position 17 - 24 in every time-slot. Monitor commands/messages sent to/from the U-transceiver are always 2 bytes long.

Transmission of multiple monitor bytes is specified by IOM<sup>®</sup>-2 (see next section "Handshake Procedure" for details). For handshake control in multiple byte transfers, bit 31, monitor read "MR", and bit 32, monitor transmit "MX", of every time-slot are used.

#### Verification

A double last-look criterion is implemented for the monitor channel. If the monitor message that was received consecutively after a change has been detected is not identical to the message that was received before the message will be aborted.

#### **Handshake Procedure**

IOM<sup>®</sup>-2 provides a sophisticated handshake procedure for the transfer of monitor messages. For handshake control two bits, MX and MR, are assigned to each IOM<sup>®</sup>-2 frame (on DIN and DOUT). The monitor transmit bit (MX) indicates when a new byte has been issued in the monitor channel (active low). The transmitter postpones transmitting the next information until the correct reception has been confirmed. A correct reception will be confirmed by setting the monitor read bit (MR) to low.

The monitor channel is full duplex and operates on a pseudo-asynchronous base, i.e. while data transfer on the bus takes place synchronized to frame synchronization, the flow of monitor data is controlled by the MR- and MX-bits. Monitor data will be transmitted repeatedly until its reception is acknowledged.

**Figure 12** illustrates a monitor transfer at maximum speed. The transmission of a 2-byte monitor command followed by a 2-byte response requires a minimum of 15  $IOM^{@}$ -2 frames (reception 7 frames + transmission 8 frames = 1.875 ms). In case the controller is able to confirm the receipt of first response byte in the frame immediately following the MX-transition on DOUT from high to low (i.e. in frame No. 9), 1 byte may be saved (7 frames + 7 frames).

Transmission and reception of monitor messages can be performed simultaneously by the U-transceiver. In the procedure depicted in **Figure 12** it would be possible for the U-transceiver to transmit monitor data in frames 1–5 (excluding EOM-indication) and receive monitor data from frame 8 onwards.

M 1/2:Monitor message 1. and 2. byte R 1/2:Monitor response 1. and 2. byte

Figure 12 Handshake Protocol with a 2-Byte Monitor Message/Response

#### Idle State

After the bits MR and MX have been held inactive (i.e. high) for two or more successive IOM<sup>®</sup>-frames, the channel is considered idle in this direction.

#### **Standard Transmission Procedure**

- 1. The first byte of monitor data is placed by the external controller on the DIN line of the DFE-Q V2.1 and MX is activated (low; frame No. 1).

- 2. The DFE-Q V2.1 reads the data of the monitor channel and acknowledges by setting the MR-bit of DOUT active if the transmitted bytes are identical in two received frames (frame No. 2 because data are already read and compared while the MX-bit is not activated).

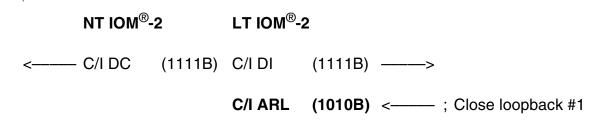

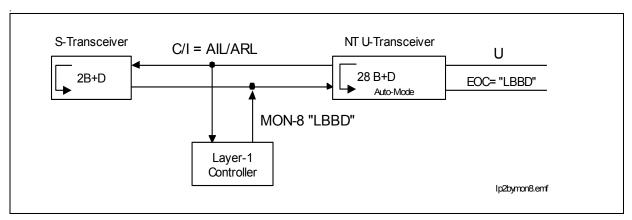

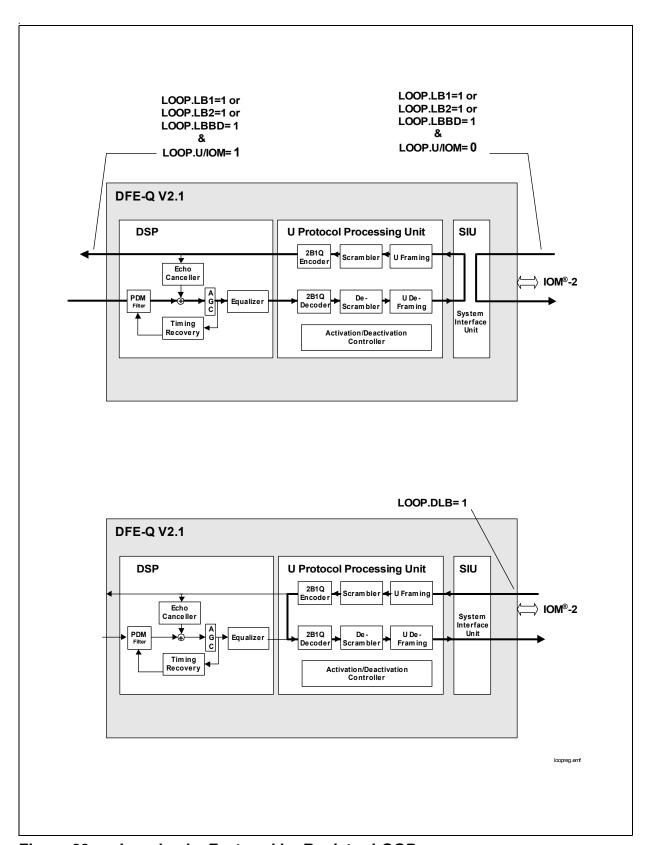

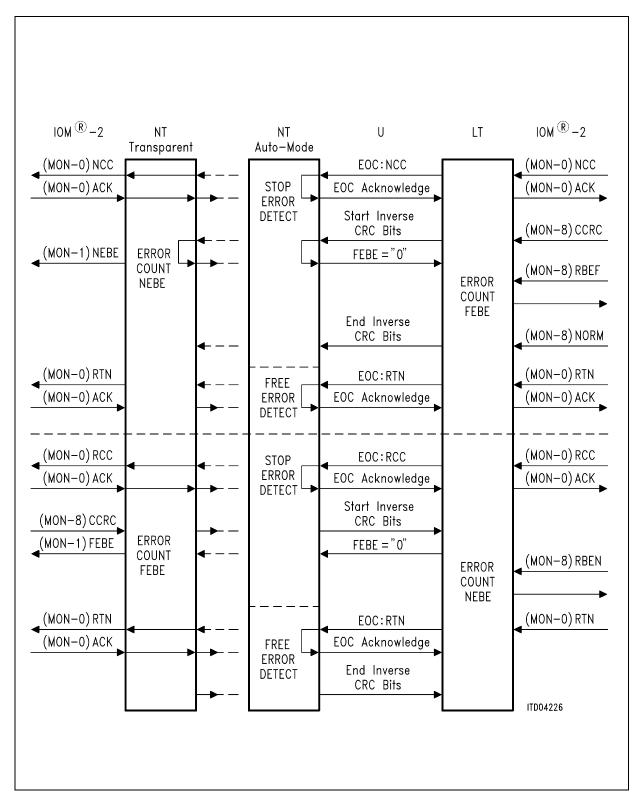

- 3. The second byte of monitor data is placed by the controller on DIN and the MX-bit is set inactive for one single IOM<sup>®</sup>-frame. This is performed at a time convenient to the controller.