#### **General Description**

The DS2431 is a 1024-bit, 1-Wire® EEPROM chip organized as four memory pages of 256 bits each. Data is written to an 8-byte scratchpad, verified, and then copied to the EEPROM memory. As a special feature, the four memory pages can individually be write protected or put in EPROM-emulation mode, where bits can only be changed from a 1 to a 0 state. The DS2431 communicates over the single-conductor 1-Wire bus. The communication follows the standard 1-Wire protocol. Each device has its own unalterable and unique 64-bit ROM registration number that is factory lasered into the chip. The registration number is used to address the device in a multidrop, 1-Wire net environment.

### **Applications**

Accessory/PCB Identification Medical Sensor Calibration Data Storage Analog Sensor Calibration Including IEEE P1451.4 Smart Sensors

Ink and Toner Print Cartridge Identification After-Market Management of Consumables

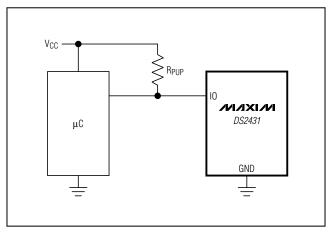

### **Typical Operating Circuit**

#### **Features**

- **♦ 1024 Bits of EEPROM Memory Partitioned Into** Four Pages of 256 Bits

- ♦ Individual Memory Pages Can Be Permanently Write Protected or Put in EPROM-Emulation Mode ("Write to 0")

- ♦ Switchpoint Hysteresis and Filtering to Optimize Performance in the Presence of Noise

- ♦ IEC 1000-4-2 Level 4 ESD Protection (8kV Contact, 15kV Air, Typical)

- ♦ Reads and Writes Over a Wide Voltage Range from 2.8V to 5.25V from -40°C to +85°C

- ♦ Communicates to Host with a Single Digital Signal at 15.4kbps or 125kbps Using 1-Wire **Protocol**

- ◆ Also Available as Automotive Version Meeting **AEC-Q100 Grade 1 Qualification Requirements** (DS2431-A1)

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE            |

|-------------|----------------|------------------------|

| DS2431+     | -40°C to +85°C | 3 TO-92                |

| DS2431+T&R  | -40°C to +85°C | 3 TO-92                |

| DS2431P+    | -40°C to +85°C | 6 TSOC                 |

| DS2431P+T&R | -40°C to +85°C | 6 TSOC                 |

| DS2431G+    | -40°C to +85°C | 2 SFN                  |

| DS2431G+T&R | -40°C to +85°C | 2 SFN                  |

| DS2431Q+T&R | -40°C to +85°C | 6 TDFN-EP* (2.5k pcs)  |

| DS2431X+S   | -40°C to +85°C | 3x3 UCSPR** (2.5k pcs) |

| DS2431X+    | -40°C to +85°C | 3x3 UCSPR** (10k pcs)  |

Note: The leads of TO-92 packages on tape and reel are formed to approximately 100-mil (2.54mm) spacing. For details, refer to the package outline drawing.

+ Denotes a lead-free/RoHS-compliant package.

T&R = Tape and reel.

\*EP = Exposed pad.

\*\*Contact factory for availability and guidelines on qualified usage conditions of the lead-free UCSPR.

Pin Configurations appear at end of data sheet.

1-Wire is a registered trademark of Maxim Integrated Products, Inc.

#### **ABSOLUTE MAXIMUM RATINGS**

| IO Voltage Range to GND     | 0.5V to +6V   | Junction Temperature      | +150°C                   |

|-----------------------------|---------------|---------------------------|--------------------------|

| IO Sink Current             | 20mA          | Storage Temperature Range | 55°C to +125°C           |

| Operating Temperature Range | 40°C to +85°C | Soldering Temperature     |                          |

|                             |               |                           | J-STD-020 Specification. |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C.) \text{ (Note 1)}$

| PARAMETER                       | SYMBOL           | CONDITIONS                                                             | MIN                | TYP MAX                   | UNITS |  |  |  |

|---------------------------------|------------------|------------------------------------------------------------------------|--------------------|---------------------------|-------|--|--|--|

| IO PIN: GENERAL DATA            | •                |                                                                        | •                  |                           | •     |  |  |  |

| 1-Wire Pullup Voltage           | V <sub>PUP</sub> | (Note 2)                                                               | 2.8                | 5.25                      | V     |  |  |  |

| 1-Wire Pullup Resistance        | Rpup             | (Notes 2, 3)                                                           | 0.3                | 2.2                       | kΩ    |  |  |  |

| Input Capacitance               | CIO              | (Notes 4, 5)                                                           |                    | 1000                      | pF    |  |  |  |

| Input Load Current              | ΙL               | IO pin at V <sub>PUP</sub>                                             | 0.05               | 6.7                       | μΑ    |  |  |  |

| High-to-Low Switching Threshold | V <sub>TL</sub>  | (Notes 5, 6, 7)                                                        | 0.5                | V <sub>PUP</sub> -<br>1.8 | V     |  |  |  |

| Input Low Voltage               | VIL              | (Notes 2, 8)                                                           |                    | 0.5                       | V     |  |  |  |

| Low-to-High Switching Threshold | V <sub>TH</sub>  | (Notes 5, 6, 9)                                                        | 1.0                | V <sub>PUP</sub> -<br>1.0 | V     |  |  |  |

| Switching Hysteresis            | V <sub>H</sub> Y | (Notes 5, 6, 10)                                                       | 0.21               | 1.70                      | V     |  |  |  |

| Output Low Voltage              | V <sub>OL</sub>  | At 4mA (Note 11)                                                       |                    | 0.4                       | V     |  |  |  |

| Recovery Time<br>(Notes 2,12)   | trec             | Standard speed, $R_{PUP} = 2.2 k\Omega$                                | 5                  |                           |       |  |  |  |

|                                 |                  | Overdrive speed, R <sub>PUP</sub> = $2.2k\Omega$                       | 2                  |                           |       |  |  |  |

|                                 |                  | Overdrive speed, directly prior to reset pulse; $R_{PUP} = 2.2k\Omega$ | 5                  |                           | - µs  |  |  |  |

| Rising-Edge Hold-Off Time       |                  | Standard speed                                                         | 0.5                | 0.5 5.0                   |       |  |  |  |

| (Notes 5, 13)                   | t <sub>REH</sub> | Overdrive speed                                                        | Not applicable (0) |                           | μs    |  |  |  |

| Time Slot Duration              | to: 0=           | Standard speed                                                         | 65                 |                           | μs    |  |  |  |

| (Notes 2, 14)                   | tslot            | Overdrive speed                                                        | 8                  | 8                         |       |  |  |  |

| IO PIN: 1-Wire RESET, PRESEN    | CE-DETECT        | CYCLE                                                                  |                    |                           |       |  |  |  |

| Popot Low Time (Note 2)         | trstl            | Standard speed                                                         | 480                | 640                       |       |  |  |  |

| Reset Low Time (Note 2)         |                  | Overdrive speed                                                        | 48                 | 80                        | - μs  |  |  |  |

| Presence-Detect High Time       | t <sub>PDH</sub> | Standard speed                                                         | 15 60              |                           | μs    |  |  |  |

|                                 |                  | Overdrive speed                                                        | 2                  | 6                         | ] µs  |  |  |  |

| Presence-Detect Low Time        | tPDL             | Standard speed                                                         | 60                 | 240                       | 110   |  |  |  |

| Treserice-Detect Low Tillle     |                  | Overdrive speed                                                        | 8                  | 24                        | μs    |  |  |  |

| Presence-Detect Sample Time     | twon             | Standard speed                                                         | 60                 | 75                        | 110   |  |  |  |

| (Notes 2, 15)                   | tMSP             | Overdrive speed                                                        | 6                  | 10                        | μs    |  |  |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C.) \text{ (Note 1)}$

| PARAMETER                                        | SYMBOL           | CONDITIONS                               | MIN TY              | P MAX  | UNITS |  |

|--------------------------------------------------|------------------|------------------------------------------|---------------------|--------|-------|--|

| IO PIN: 1-Wire WRITE                             | •                |                                          | ·                   |        |       |  |

| Write-Zero Low Time<br>(Notes 2, 16, 17)         |                  | Standard speed                           | 60                  | 120    | μs    |  |

|                                                  | twoL             | Overdrive speed, V <sub>PUP</sub> > 4.5V | 5                   | 15.5   |       |  |

|                                                  |                  | Overdrive speed                          | 6                   | 15.5   |       |  |

| Write-One Low Time<br>(Notes 2, 17)              |                  | Standard speed                           | 1                   | 15     | μs    |  |

|                                                  | t <sub>W1L</sub> | Overdrive speed                          | 1                   | 2      |       |  |

| IO PIN: 1-Wire READ                              | •                |                                          |                     |        |       |  |

| Read Low Time<br>(Notes 2, 18)                   | t <sub>RL</sub>  | Standard speed                           | 5                   | 15 - δ |       |  |

|                                                  |                  | Overdrive speed                          | 1                   | 2 - δ  | - µs  |  |

| Read Sample Time                                 | tmsr             | Standard speed                           | $t_{RL} + \delta$   | 15     |       |  |

| (Notes 2, 18)                                    |                  | Overdrive speed                          | t <sub>RL</sub> + δ | 2      | μs    |  |

| EEPROM                                           |                  |                                          |                     |        |       |  |

| Programming Current                              | IPROG            | (Notes 5, 19)                            |                     | 0.8    | mA    |  |

| Programming Time                                 | tprog            | (Notes 20, 21)                           |                     | 10     | ms    |  |

| Write/Erase Cycles (Endurance)<br>(Notes 22, 23) | N <sub>CY</sub>  | At +25°C                                 | 200k                |        |       |  |

|                                                  |                  | At +85°C (worst case)                    | 50k                 |        |       |  |

| Data Retention<br>(Notes 24, 25, 26)             | t <sub>DR</sub>  | At +85°C (worst case)                    | 40                  |        | Years |  |

- **Note 1:** Specifications at T<sub>A</sub> = -40°C are guaranteed by design only and not production tested.

- Note 2: System requirement

- **Note 3:** Maximum allowable pullup resistance is a function of the number of 1-Wire devices in the system and 1-Wire recovery times. The specified value here applies to systems with only one device and with the minimum 1-Wire recovery times. For more heavily loaded systems, an active pullup such as that found in the DS2482-x00, DS2480B, or DS2490 may be required.

- **Note 4:** Maximum value represents the internal parasite capacitance when V<sub>PUP</sub> is first applied. If a 2.2kΩ resistor is used to pull up the data line, 2.5μs after V<sub>PUP</sub> has been applied, the parasite capacitance does not affect normal communications.

- Note 5: Guaranteed by design, characterization, and/or simulation only. Not production tested.

- **Note 6:** V<sub>TL</sub>, V<sub>TH</sub>, and V<sub>HY</sub> are a function of the internal supply voltage, which is a function of V<sub>PUP</sub>, R<sub>PUP</sub>, 1-Wire timing, and capacitive loading on IO. Lower V<sub>PUP</sub>, higher R<sub>PUP</sub>, shorter t<sub>REC</sub>, and heavier capacitive loading all lead to lower values of V<sub>TL</sub>, V<sub>TH</sub>, and V<sub>HY</sub>.

- Note 7: Voltage below which, during a falling edge on IO, a logic 0 is detected.

- Note 8: The voltage on IO must be less than or equal to V<sub>ILMAX</sub> at all times the master is driving IO to a logic 0 level.

- **Note 9:** Voltage above which, during a rising edge on IO, a logic 1 is detected.

- Note 10: After V<sub>TH</sub> is crossed during a rising edge on IO, the voltage on IO must drop by at least V<sub>HY</sub> to be detected as logic 0.

- Note 11: The I-V characteristic is linear for voltages less than 1V.

- Note 12: Applies to a single device attached to a 1-Wire line.

- Note 13: The earliest recognition of a negative edge is possible at t<sub>RFH</sub> after V<sub>TH</sub> has been reached on the preceding rising edge.

- **Note 14:** Defines maximum possible bit rate. Equal to twoLMIN + trecmin.

- **Note 15:** Interval after t<sub>RSTL</sub> during which a bus master is guaranteed to sample a logic 0 on IO if there is a DS2431 present. Minimum limit is t<sub>PDHMIN</sub>; maximum limit is t<sub>PDHMIN</sub> + t<sub>PDLMIN</sub>.

- Note 16: Numbers in **bold** are **not** in compliance with legacy 1-Wire product standards. See the *Comparison Table*.

- **Note 17:**  $\epsilon$  in Figure 11 represents the time required for the pullup circuitry to pull the voltage on IO up from V<sub>IL</sub> to V<sub>TH</sub>. The actual maximum duration for the master to pull the line low is  $t_{W1LMAX} + t_F \epsilon$  and  $t_{W0LMAX} + t_F \epsilon$ , respectively.

- **Note 18:** δ in Figure 11 represents the time required for the pullup circuitry to pull the voltage on IO up from V<sub>IL</sub> to the input-high threshold of the bus master. The actual maximum duration for the master to pull the line low is the MAX + tF.

- **Note 19:** Current drawn from IO during the EEPROM programming interval. The pullup circuit on IO during the programming interval should be such that the voltage at IO is greater than or equal to V<sub>PUPMIN</sub>. If V<sub>PUP</sub> in the system is close to V<sub>PUPMIN</sub>, a low-impedance bypass of R<sub>PUP</sub>, which can be activated during programming, may need to be added.

- Note 20: Interval begins t<sub>REHMAX</sub> after the trailing rising edge on IO for the last time slot of the E/S byte for a valid Copy Scratchpad sequence. Interval ends once the device's self-timed EEPROM programming cycle is complete and the current drawn by the device has returned from I<sub>PROG</sub> to I<sub>L</sub>.

- Note 21: tpROG for units branded version "A1" is 12.5ms. tpROG for units branded version "A2" and later is 10ms.

- Note 22: Write-cycle endurance is degraded as TA increases.

- Note 23: Not 100% production tested; guaranteed by reliability monitor sampling.

- Note 24: Data retention is degraded as TA increases.

- **Note 25:** Guaranteed by 100% production test at elevated temperature for a shorter time; equivalence of this production test to the data sheet limit at operating temperature range is established by reliability testing.

- **Note 26:** EEPROM writes can become nonfunctional after the data-retention time is exceeded. Long-term storage at elevated temperatures is not recommended; the device can lose its write capability after 10 years at +125°C or 40 years at +85°C.

#### **COMPARISON TABLE**

| PARAMETER              | LEGACY VALUES       |             |                         |             | DS2431 VALUES          |             |                         |             |

|------------------------|---------------------|-------------|-------------------------|-------------|------------------------|-------------|-------------------------|-------------|

|                        | STANDARD SPEED (µs) |             | OVERDRIVE SPEED<br>(µs) |             | STANDARD SPEED<br>(µs) |             | OVERDRIVE SPEED<br>(µs) |             |

|                        | MIN                 | MAX         | MIN                     | MAX         | MIN                    | MAX         | MIN                     | MAX         |

| tslot (including trec) | 61                  | (undefined) | 7                       | (undefined) | 65*                    | (undefined) | 8*                      | (undefined) |

| trstl                  | 480                 | (undefined) | 48                      | 80          | 480                    | 640         | 48                      | 80          |

| tpdH                   | 15                  | 60          | 2                       | 6           | 15                     | 60          | 2                       | 6           |

| tpDL                   | 60                  | 240         | 8                       | 24          | 60                     | 240         | 8                       | 24          |

| twoL                   | 60                  | 120         | 6                       | 16          | 60                     | 120         | 6                       | 15.5        |

<sup>\*</sup>Intentional change; longer recovery time requirement due to modified 1-Wire front-end.

Note: Numbers in bold are not in compliance with legacy 1-Wire product standards.