# DS1220AB/AD 16k Nonvolatile SRAM

#### **FEATURES**

- 10 years minimum data retention in the absence of external power

- Data is automatically protected during power loss

- Directly replaces 2k x 8 volatile static RAM or EEPROM

- Unlimited write cycles

- Low-power CMOS

- JEDEC standard 24-pin DIP package

- Read and write access times as fast as 100 ns

- Lithium energy source is electrically disconnected to retain freshness until power is applied for the first time

- Full ±10% V<sub>CC</sub> operating range (DS1220AD)

- Optional ±5% V<sub>CC</sub> operating range (DS1220AB)

- Optional industrial temperature range of -40°C to +85°C, designated IND

### PIN ASSIGNMENT

| A7  | <b>1</b> 1  | 24 🔳            | VCC |

|-----|-------------|-----------------|-----|

| A6  |             | 23              | A8  |

| A5  | 3           | 22              | A9  |

| A4  | 4           | 21              | WE  |

| A3  | <b>■</b> 5  | 20 ■            | ŌE  |

| A2  | <b>6</b>    | 19 🛮            | A10 |

| A1  | <b>□</b> 7  | 18              | CE  |

| A0  | <b>■</b> 8  | 17              | DQ7 |

| DQ0 | <b>1</b> 9  | <sub>16</sub> 🛮 | DQ6 |

| DQ1 | <b>1</b> 0  | 15              | DQ5 |

| DQ2 | <b>1</b> 11 | 14 🗖            | DQ4 |

| GND | <b>1</b> 2  | 13              | DQ3 |

|     | 1           |                 |     |

24-Pin ENCAPSULATED PACKAGE 720-mil EXTENDED

### PIN DESCRIPTION

| A0-A10                 | - Address Inputs   |

|------------------------|--------------------|

| DQ0-DQ7                | - Data In/Data Out |

| $\overline{\text{CE}}$ | - Chip Enable      |

| $\overline{	ext{WE}}$  | - Write Enable     |

| $\overline{OE}$        | - Output Enable    |

| $V_{CC}$               | - Power (+5V)      |

| GND                    | - Ground           |

## **DESCRIPTION**

The DS1220AB and DS1220AD 16k Nonvolatile SRAMs are 16,384-bit, fully static, nonvolatile SRAMs organized as 2048 words by 8 bits. Each NV SRAM has a self-contained lithium energy source and control circuitry which constantly monitors  $V_{\rm CC}$  for an out-of-tolerance condition. When such a condition occurs, the lithium energy source is automatically switched on and write protection is unconditionally enabled to prevent data corruption. The NV SRAMs can be used in place of existing  $2k \times 8$  SRAMs directly conforming to the popular bytewide 24-pin DIP standard. The devices also match the pinout of the 2716 EPROM and the 2816 EEPROM, allowing direct substitution while enhancing performance. There is no limit on the number of write cycles that can be executed and no additional support circuitry is required for microprocessor interfacing.

### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on Any Pin Relative to Ground -0.3V to +6.0V

Operating Temperature

0°C to 70°C; -40°C to +85°C for IND parts

Storage Temperature

-40°C to +70°C; -40°C to +85°C for IND parts

Soldering Temperature +260°C for 10 seconds Caution: Do Not Reflow (Wave or Hand Solder Only)

# RECOMMENDED DC OPERATING CONDITIONS

(T<sub>A</sub>: See Note 10)

| PARAMETER                     | SYMBOL            | MIN  | TYP | MAX      | UNITS | NOTES |

|-------------------------------|-------------------|------|-----|----------|-------|-------|

| DS1220AB Power Supply Voltage | $V_{CC}$          | 4.75 | 5.0 | 5.25     | V     |       |

| DS1220AD Power Supply Voltage | $V_{CC}$          | 4.50 | 5.0 | 5.50     | V     |       |

| Logic 1                       | $V_{\mathrm{IH}}$ | 2.2  |     | $V_{CC}$ | V     |       |

| Logic 0                       | $V_{\rm IL}$      | 0.0  |     | +0.8     | V     |       |

(T<sub>A</sub>: See Note 10)

( $V_{CC}$  =5V  $\pm$  5% for DS1220AB)

## DC ELECTRICAL CHARACTERISTICS

( $V_{CC}$  =5V  $\pm$  10% for DS1220AD)

| PARAMETER                                                 | SYMBOL            | MIN  | TYP  | MAX  | UNITS | NOTES |

|-----------------------------------------------------------|-------------------|------|------|------|-------|-------|

| Input Leakage Current                                     | $I_{IL}$          | -1.0 |      | +1.0 | μΑ    |       |

| I/O Leakage Current $\overline{CE} \ge V_{IH} \le V_{CC}$ | $I_{IO}$          | -1.0 |      | +1.0 | μΑ    |       |

| Output Current @ 2.4V                                     | $I_{OH}$          | -1.0 |      |      | mA    |       |

| Output Current @ 0.4V                                     | $I_{OL}$          | 2.0  |      |      | mA    |       |

| Standby Current $\overline{CE} = 2.2V$                    | $I_{CCS1}$        |      | 5.0  | 10.0 | mA    |       |

| Standby Current $\overline{CE} = V_{CC}-0.5V$             | $I_{CCS2}$        |      | 3.0  | 5.0  | mA    |       |

| Operating Current (Commercial)                            | $I_{CC01}$        |      |      | 75   | mA    |       |

| Operating Current (Industrial)                            | I <sub>CCO1</sub> |      |      | 85   | mA    |       |

| Write Protection Voltage (DS1220AB)                       | $V_{TP}$          | 4.5  | 4.62 | 4.75 | V     |       |

| Write Protection Voltage (DS1220AD)                       | $V_{TP}$          | 4.25 | 4.37 | 4.5  | V     |       |

# CAPACITANCE

$(T_{\Delta} = 25^{\circ}C)$

| PARAMETER                | SYMBOL          | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------|-----------------|-----|-----|-----|-------|-------|

| Input Capacitance        | C <sub>IN</sub> |     | 5   | 10  | pF    |       |

| Input/Output Capacitance | $C_{I/O}$       |     | 5   | 12  | pF    |       |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

(T<sub>A:</sub> See Note 10)

(V<sub>CC</sub> =5.0V  $\pm$  5% for DS1220AB)

# **AC ELECTRICAL CHARACTERISTICS**

|                                                                   |                    | DS1220AB-100 |     | DS1220       | OAB-120 |       |       |

|-------------------------------------------------------------------|--------------------|--------------|-----|--------------|---------|-------|-------|

| PARAMETER                                                         | SYMBOL             | DS1220AD-100 |     | DS1220AD-120 |         | UNITS | NOTES |

|                                                                   |                    | MIN          | MAX | MIN          | MAX     |       |       |

| Read Cycle Time                                                   | $t_{RC}$           | 100          |     | 120          |         | ns    |       |

| Access Time                                                       | $t_{ACC}$          |              | 100 |              | 120     | ns    |       |

| OE to Output Valid                                                | $t_{OE}$           |              | 50  |              | 60      | ns    |       |

| CE to Output Valid                                                | $t_{CO}$           |              | 100 |              | 120     | ns    |       |

| $\overline{\text{OE}}$ or $\overline{\text{CE}}$ to Output Active | $t_{COE}$          | 5            |     | 5            |         | ns    | 5     |

| Output High Z from                                                | t <sub>OD</sub>    |              | 35  |              | 35      | ns    | 5     |

| Deselection                                                       | UD                 |              |     |              | 33      | 113   |       |

| Output Hold from Address                                          | t <sub>OH</sub>    | 5            |     | 5            |         | ns    |       |

| Change                                                            | чон                |              |     | 3            |         | 113   |       |

| Write Cycle Time                                                  | $t_{ m WC}$        | 100          |     | 120          |         | ns    |       |

| Write Pulse Width                                                 | $t_{\mathrm{WP}}$  | 75           |     | 90           |         | ns    | 3     |

| Address Setup Time                                                | $t_{AW}$           | 0            |     | 0            |         | ns    |       |

| Write Recovery Time                                               | $t_{\mathrm{WR1}}$ | 0            |     | 0            |         | ns    | 12    |

|                                                                   | $t_{\mathrm{WR2}}$ | 10           |     | 10           |         | ns    | 13    |

| Output High from WE                                               | $t_{ODW}$          |              | 35  |              | 35      | ns    | 5     |

| Output Active from WE                                             | t <sub>OEW</sub>   | 5            |     | 5            |         | ns    | 4     |

| Data Setup Time                                                   | $t_{\mathrm{DS}}$  | 40           |     | 50           |         | ns    | 4     |

| Data Hold Time                                                    | $t_{ m DH1}$       | 0            |     | 0            |         | ns    | 12    |

|                                                                   | t <sub>DH2</sub>   | 10           |     | 10           |         | ns    | 13    |

# **AC ELECTRICAL CHARACTERISTICS**

(cont'd)

| PARAMETER                                                         | SYMBOL             |     |     |     | 0AB-200<br>0AD-200 | UNITS  | NOTES  |

|-------------------------------------------------------------------|--------------------|-----|-----|-----|--------------------|--------|--------|

|                                                                   |                    | MIN | MAX | MIN | MAX                | 011110 | 110125 |

| Read Cycle Time                                                   | $t_{RC}$           | 150 |     | 200 |                    | ns     |        |

| Access Time                                                       | $t_{ACC}$          |     | 150 |     | 200                | ns     |        |

| OE to Output Valid                                                | $t_{OE}$           |     | 70  |     | 100                | ns     |        |

| CE to Output Valid                                                | $t_{CO}$           |     | 150 |     | 200                | ns     |        |

| $\overline{\text{OE}}$ or $\overline{\text{CE}}$ to Output Active | $t_{COE}$          | 5   |     | 5   |                    | ns     | 5      |

| Output High Z from Deselection                                    | t <sub>OD</sub>    |     | 35  |     | 35                 | ns     | 5      |

| Output Hold from Address<br>Change                                | t <sub>OH</sub>    | 5   |     | 5   |                    | ns     |        |

| Write Cycle Time                                                  | $t_{ m WC}$        | 150 |     | 200 |                    | ns     |        |

| Write Pulse Width                                                 | $t_{\mathrm{WP}}$  | 100 |     | 150 |                    | ns     | 3      |

| Address Setup Time                                                | $t_{AW}$           | 0   |     | 0   |                    | ns     |        |

| Write Recovery Time                                               | $t_{\mathrm{WR1}}$ | 0   |     | 0   |                    | ns     | 12     |

|                                                                   | $t_{\mathrm{WR2}}$ | 10  |     | 10  |                    | ns     | 13     |

| Output High Z from WE                                             | $t_{\mathrm{ODW}}$ |     | 35  |     | 35                 | ns     | 5      |

| Output Active from WE                                             | t <sub>OEW</sub>   | 5   |     | 5   |                    | ns     | 4      |

| Data Setup Time                                                   | $t_{ m DS}$        | 60  |     | 50  |                    | ns     | 4      |

| Data Hold Time                                                    | t <sub>DH1</sub>   | 0   |     | 0   |                    | ns     | 12     |

|                                                                   | t <sub>DH2</sub>   | 10  |     | 10  |                    | ns     | 13     |

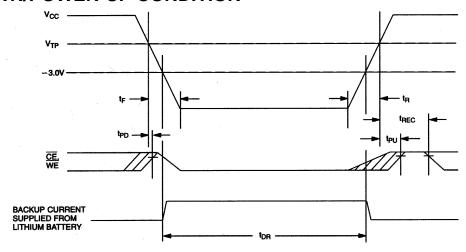

### POWER-DOWN/POWER-UP CONDITION

SEE NOTE 11

## POWER-DOWN/POWER-UP TIMING

(T<sub>A</sub>: See Note 10)

|                                                                                     |                   | - Д | 1010 |     |       |       |

|-------------------------------------------------------------------------------------|-------------------|-----|------|-----|-------|-------|

| PARAMETER                                                                           | SYMBOL            | MIN | TYP  | MAX | UNITS | NOTES |

| $V_{CC}$ Fail Detect to $\overline{CE}$ and $\overline{WE}$ Inactive                | $t_{\mathrm{PD}}$ |     |      | 1.5 | μs    | 11    |

| V <sub>CC</sub> slew from V <sub>TP</sub> to 0V                                     | $t_{\mathrm{F}}$  | 300 |      |     | μs    |       |

| V <sub>CC</sub> slew from 0V to V <sub>TP</sub>                                     | $t_{R}$           | 300 |      |     | μs    |       |

| V <sub>CC</sub> Valid to $\overline{\text{CE}}$ and $\overline{\text{WE}}$ Inactive | $t_{\mathrm{PU}}$ |     |      | 2   | ms    |       |

| V <sub>CC</sub> Valid to End of Write Protection                                    | $t_{REC}$         |     |      | 125 | ms    |       |

$(T_A = 25^{\circ}C)$

| PARAMETER                    | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

|------------------------------|-------------------|-----|-----|-----|-------|-------|

| Expected Data Retention Time | $t_{\mathrm{DR}}$ | 10  |     |     | years | 9     |

#### **WARNING:**

Under no circumstances are negative undershoots, of any amplitude, allowed when device is in the battery backup mode.

# NOTES:

- 1. WE is high for a read cycle.

- 2.  $\overline{OE} = V_{IH}$  or  $V_{IL}$ . If  $\overline{OE} = V_{IH}$  during write cycle, the output buffers remain in a high-impedance state.

- 3.  $t_{WP}$  is specified as the logical AND of  $\overline{CE}$  and  $\overline{WE}$ .  $t_{WP}$  is measured from the latter of  $\overline{CE}$  or  $\overline{CE}$  going low to the earlier of  $\overline{CE}$  or  $\overline{WE}$  going high.

- 4.  $t_{DS}$  is measured from the earlier of  $\overline{CE}$  or  $\overline{WE}$  going high.

- 5. These parameters are sampled with a 5 pF load and are not 100% tested.

- 6. If the  $\overline{\text{CE}}$  low transition occurs simultaneously with or later than the  $\overline{\text{WE}}$  low transition, the output buffers remain in a high-impedance state during this period.

- 7. If the  $\overline{\text{CE}}$  high transition occurs prior to or simultaneously with the  $\overline{\text{WE}}$  high transition, the output buffers remain in a high-impedance state during this period.

- 8. If WE is low or the WE low transition occurs prior to or simultaneously with the CE low transition, the output buffers remain in a high-impedance state during this period.

- 9. Each DS1220AB and each DS1220AD has a built-in switch that disconnects the lithium source until  $V_{CC}$  is first applied by the user. The expected  $t_{DR}$  is defined as accumulative time in the absence of  $V_{CC}$  starting from the time power is first applied by the user. This parameter is guaranteed by design and is not 100% tested.

- 10. All AC and DC electrical characteristics are valid over the full operating temperature range. For commercial products, this range is 0°C to 70°C. For industrial products (IND), this range is -40°C to +85°C.

- 11. In a power down condition the voltage on any pin may not exceed the voltage on  $V_{CC}$ .

- 12.  $t_{WR1}$ ,  $t_{DH1}$  are measured from  $\overline{WE}$  going high.

- 13. t<sub>WR2</sub>, t<sub>DH2</sub> are measured from CE going high.

- 14. DS1220 modules are recognized by Underwriters Laboratory (U.L.®) under file E99151.

#### DC TEST CONDITIONS

Outputs Open Cycle = 200ns for Operating Current All Voltages Are Referenced to Ground

### **AC TEST CONDITIONS**

Output Load: 100 pF + 1TTL Gate Input Pulse Levels: 0 - 3.0V

Timing Measurement Reference Levels

Input: 1.5V Output: 1.5V

Input Pulse Rise and Fall Times: 5ns

### ORDERING INFORMATION

| PART NUMBER      | TEMPERATURE<br>RANGE | SUPPLY<br>TOLERANCE | PIN/PACKAGE   | SPEED<br>GRADE |

|------------------|----------------------|---------------------|---------------|----------------|

| DS1220AB-100     | 0°C to +70°C         | 5V ± 5%             | 24 / 720 EMOD | 100ns          |

| DS1220AB-100+    | 0°C to +70°C         | 5V ± 5%             | 24 / 720 EMOD | 100ns          |

| DS1220AB-100IND  | -40°C to +85°C       | 5V ± 5%             | 24 / 720 EMOD | 100ns          |

| DS1220AB-100IND+ | -40°C to +85°C       | 5V ± 5%             | 24 / 720 EMOD | 100ns          |

| DS1220AB-120     | 0°C to +70°C         | 5V ± 5%             | 24 / 720 EMOD | 120ns          |

| DS1220AB-120+    | 0°C to +70°C         | 5V ± 5%             | 24 / 720 EMOD | 120ns          |

| DS1220AB-150     | 0°C to +70°C         | 5V ± 5%             | 24 / 720 EMOD | 150ns          |

| DS1220AB-150+    | 0°C to +70°C         | 5V ± 5%             | 24 / 720 EMOD | 150ns          |

| DS1220AB-200     | 0°C to +70°C         | 5V ± 5%             | 24 / 720 EMOD | 200ns          |

| DS1220AB-200+    | 0°C to +70°C         | 5V ± 5%             | 24 / 720 EMOD | 200ns          |

| DS1220AB-200IND  | -40°C to +85°C       | 5V ± 5%             | 24 / 720 EMOD | 200ns          |

| DS1220AB-200IND+ | -40°C to +85°C       | 5V ± 5%             | 24 / 720 EMOD | 200ns          |

| DS1220AD-100     | 0°C to +70°C         | 5V ± 10%            | 24 / 720 EMOD | 100ns          |

| DS1220AD-100+    | 0°C to +70°C         | 5V ± 10%            | 24 / 720 EMOD | 100ns          |

| DS1220AD-100IND  | -40°C to +85°C       | 5V ± 10%            | 24 / 720 EMOD | 100ns          |

| DS1220AD-100IND+ | -40°C to +85°C       | 5V ± 10%            | 24 / 720 EMOD | 100ns          |

| DS1220AD-120     | 0°C to +70°C         | 5V ± 10%            | 24 / 720 EMOD | 120ns          |

| DS1220AD-120+    | 0°C to +70°C         | 5V ± 10%            | 24 / 720 EMOD | 120ns          |

| DS1220AD-150     | 0°C to +70°C         | 5V ± 10%            | 24 / 720 EMOD | 150ns          |

| DS1220AD-150+    | 0°C to +70°C         | 5V ± 10%            | 24 / 720 EMOD | 150ns          |

| DS1220AD-200     | 0°C to +70°C         | 5V ± 10%            | 24 / 720 EMOD | 200ns          |

| DS1220AD-200+    | 0°C to +70°C         | 5V ± 10%            | 24 / 720 EMOD | 200ns          |

| DS1220AD-200IND  | -40°C to +85°C       | 5V ± 10%            | 24 / 720 EMOD | 200ns          |

| DS1220AD-200IND+ | -40°C to +85°C       | 5V ± 10%            | 24 / 720 EMOD | 200ns          |

<sup>+</sup> Denotes lead-free/RoHS-compliant product.