# 24AA65/24LC65/24C65

# 64K I<sup>2</sup>C<sup>™</sup> Smart Serial<sup>™</sup> EEPROM

#### **Device Selection Table**

| Part Number | Vcc Range | Page Size | Temp. Ranges | Packages |

|-------------|-----------|-----------|--------------|----------|

| 24AA65      | 1.8-6.0V  | 64 Bytes  | С            | P, SM    |

| 24LC65      | 2.5-6.0V  | 64 Bytes  | C, I         | P, SM    |

| 24C65       | 4.5-6.0V  | 64 Bytes  | C, I, E      | P, SM    |

#### Features:

- Voltage Operating Range: 1.8V to 6.0V

- Peak write current 3 mA at 6.0V

- Maximum read current 150  $\mu A$  at 6.0V

- Standby current 1 μA, typical

- Industry Standard Two-Wire Bus Protocol I<sup>2</sup>C™ Compatible

- 8-Byte Page, or Byte modes Available

- 2 ms Typical Write Cycle Time, Byte or Page

- 64-Byte Input Cache for Fast Write Loads

- Up to 8 devices may be connected to the same bus for up to 512K bits total memory

- Including 100 kHz (1.8V ≤ Vcc < 4.5V) and 400 kHz (4.5V ≤ Vcc ≤ 6.0V) Compatibility

- Programmable Block Security Options

- Programmable Endurance Options

- Schmitt Trigger, Filtered Inputs for Noise Suppression

- · Output Slope Control to Eliminate Ground Bounce

- Self-Timed Erase and Write Cycles

- · Power-on/off Data Protection Circuitry

- · Endurance:

- 10,000,000 E/W cycles for a High Endurance Block

- 1,000,000 E/W cycles for a Standard Endurance Block

- Electrostatic Discharge Protection > 4000V

- Data Retention > 200 years

- · 8-pin PDIP/SOIJ Packages

- Temperature Ranges

- Industrial (I) -40°C to +85°C - Automotive (E) -40°C to +125°C

- · Pb-Free and RoHS Compliant

\*24XX65 is used in this document as a generic part number for the 24AA65/24LC65/24C65 devices.

### **Description:**

The Microchip Technology Inc. 24AA65/24LC65/ 24C65 (24XX65)\* is a "smart" 8K x 8 Serial Electrically Erasable PROM. This device has been developed for advanced, low-power applications such as personal communications, and provides the systems designer with flexibility through the use of many new user-programmable features. The 24XX65 offers a relocatable 4K bit block of ultra-high-endurance memory for data that changes frequently. The remainder of the array, or 60K bits, is rated at 1,000,000 erase/write (E/W) cycles ensured. The 24XX65 features an input cache for fast write loads with a capacity of eight pages, or 64 bytes. This device also features programmable security options for E/W protection of critical data and/or code of up to fifteen 4K blocks. Functional address lines allow the connection of up to eight 24XX65's on the same bus for up to 512K bits contiguous EEPROM memory. Advanced CMOS technology makes this device ideal for low-power nonvolatile code and data applications. The 24XX65 is available in the standard 8-pin plastic DIP and 8-pin surface mount SOIJ package.

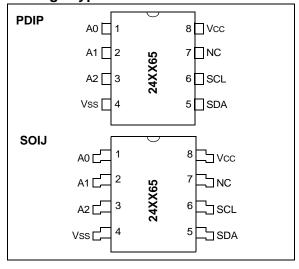

#### **Package Types**

# 24AA65/24LC65/24C65

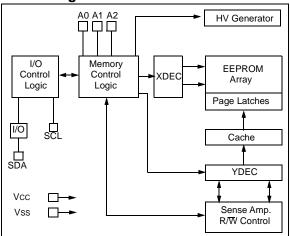

## **Block Diagram**

### **Pin Function Table**

| Name       | Function                       |  |  |

|------------|--------------------------------|--|--|

| A0, A1, A2 | User Configurable Chip Selects |  |  |

| Vss        | Ground                         |  |  |

| SDA        | Serial Address/Data/I/O        |  |  |

| SCL        | Serial Clock                   |  |  |

| Vcc        | +1.8V to 6.0V Power Supply     |  |  |

| NC         | No Internal Connection         |  |  |

#### 1.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings(†)

| Vcc                                    | 7.0V              |

|----------------------------------------|-------------------|

| All inputs and outputs w.r.t. Vss      | 0.6V to Vcc +1.0V |

| Storage temperature                    | 65°C to +150°C    |

| Ambient temperature with power applied | 40°C to +125°C    |

| ESD protection on all pins             | ≥ 4 kV            |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for an extended period of time may affect device reliability.

TABLE 1-1: DC CHARACTERISTICS

| DC CHARACTERISTICS                                                                                                                           | VCC = +1.8<br>Commercia<br>Industrial<br>Automotive | I (C): TA<br>(I): TA        | = -40°   | to +70°<br>°C to +85<br>°C to +12 | 5°C                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------|----------|-----------------------------------|--------------------------------------------------------|

| Parameter                                                                                                                                    | Sym                                                 | Min                         | Max      | Units                             | Conditions                                             |

| A0, A1, A2, SCL and SDA pins: High-level input voltage Low-level input voltage Hysteresis of Schmitt Trigger inputs Low-level output voltage | VIH<br>VIL<br>VHYS<br>VOL                           | .7 Vcc<br>—<br>.05 Vcc<br>— |          | V<br>V<br>V                       | (Note 1)<br>IOL = 3.0 mA                               |

| Input leakage current                                                                                                                        | lu                                                  | 1                           | ±1       | μΑ                                | VIN = .1V to VCC                                       |

| Output leakage current                                                                                                                       | ILO                                                 | 1                           | ±1       | μΑ                                | VOUT = .1V to VCC                                      |

| Pin capacitance (all inputs/outputs)                                                                                                         | CIN, COUT                                           |                             | 10       | pF                                | VCC = 5.0V (Note 1)<br>TA = 25°C, FCLK = 1 MHz         |

| Operating current                                                                                                                            | Icc Write<br>Icc Read                               |                             | 3<br>150 | mA<br>μA                          | VCC = 6.0V, SCL = 400 kHz<br>VCC = 6.0V, SCL = 400 kHz |

| Standby current                                                                                                                              | Iccs                                                |                             | 5        | μΑ                                | Vcc = 5.0V, SCL = SDA = Vcc<br>A0, A1, A2 = Vss        |

Note 1: This parameter is periodically sampled and not 100% tested.

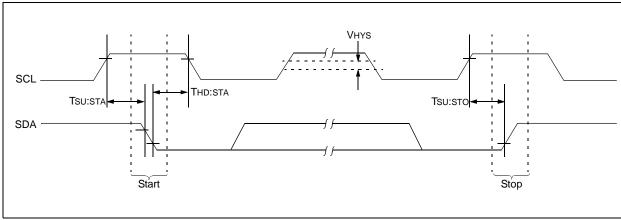

### FIGURE 1-1: BUS TIMING START/STOP

## 24AA65/24LC65/24C65

TABLE 1-2: AC CHARACTERISTICS

| Parameter                                          | Symbol  | Vcc = 1.8V-6.0V<br>STD. Mode |        | Vcc = 4.5-6.0V<br>FAST Mode |     | Units   | Remarks                                                       |  |

|----------------------------------------------------|---------|------------------------------|--------|-----------------------------|-----|---------|---------------------------------------------------------------|--|

|                                                    |         | Min                          | Max    | Min                         | Max |         |                                                               |  |

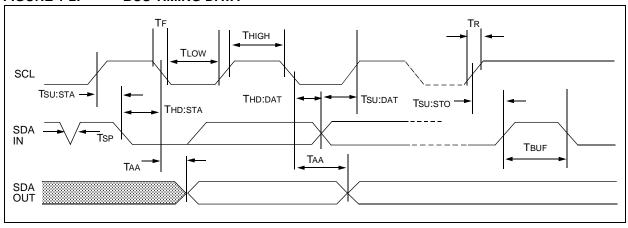

| Clock frequency                                    | FCLK    | _                            | 100    | _                           | 400 | kHz     |                                                               |  |

| Clock high time                                    | THIGH   | 4000                         | _      | 600                         |     | ns      |                                                               |  |

| Clock low time                                     | TLOW    | 4700                         | _      | 1300                        |     | ns      |                                                               |  |

| SDA and SCL rise time                              | TR      | _                            | 1000   | _                           | 300 | ns      | (Note 1)                                                      |  |

| SDA and SCL fall time                              | TF      | _                            | 300    | _                           | 300 | ns      | (Note 1)                                                      |  |

| Start condition setup time                         | THD:STA | 4000                         | _      | 600                         |     | ns      | After this period the first clock pulse is generated          |  |

| Start condition setup time                         | Tsu:sta | 4700                         | _      | 600                         | _   | ns      | Only relevant for repeated Start condition                    |  |

| Data input hold time                               | THD:DAT | 0                            | _      | 0                           | _   | ns      |                                                               |  |

| Data input setup time                              | TSU:DAT | 250                          | _      | 100                         | _   | ns      |                                                               |  |

| Stop condition setup time                          | Tsu:sto | 4000                         | _      | 600                         |     | ns      |                                                               |  |

| Output valid from clock                            | TAA     | _                            | 3500   | _                           | 900 | ns      | (Note 2)                                                      |  |

| Bus free time                                      | TBUF    | 4700                         |        | 1300                        | _   | ns      | Time the bus must be free before a new transmission can start |  |

| Output fall time from VIH min to VIL max           | Tof     | _                            | 250    | 20 + 0.1<br>Св              | 250 | ns      | (Note 1), CB ≤ 100 pF                                         |  |

| Input filter spike suppression (SDA and SCL pins)  | TSP     | 50                           | _      | 50                          | _   | ns      | (Note 3)                                                      |  |

| Write cycle time                                   | Twr     | _                            | 5      | _                           | 5   | ms/page | (Note 4)                                                      |  |

| Endurance<br>High Endurance Block<br>Rest of Array |         | 10M<br>1M                    | _<br>_ | 10M<br>1M                   |     | cycles  | 25°C, (Note 5)                                                |  |

- **Note 1:** Not 100 percent tested. CB = total capacitance of one bus line in pF.

- 2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

- **3:** The combined TsP and VHYS specifications are due to new Schmitt Trigger inputs which provide improved noise and spike suppression. This eliminates the need for a Ti specification for standard operation.

- **4:** The times shown are for a single page of 8 bytes. Multiply by the number of pages loaded into the write cache for total time.

- 5: This parameter is not tested but ensured by characterization. For endurance estimates in a specific application, please consult the Total Endurance™ Model

FIGURE 1-2: BUS TIMING DATA

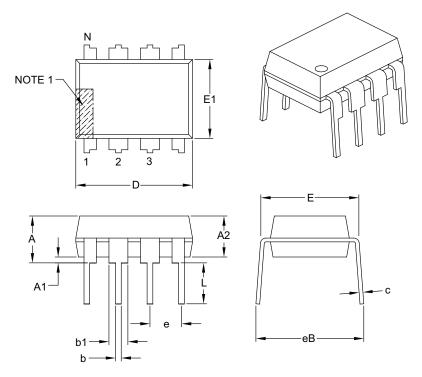

## 8-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

|                            | Units            |            |      | INCHES |  |  |

|----------------------------|------------------|------------|------|--------|--|--|

|                            | Dimension Limits |            |      | MAX    |  |  |

| Number of Pins             | N                |            | 8    |        |  |  |

| Pitch                      | е                | e .100 BSC |      |        |  |  |

| Top to Seating Plane       | A                | 210        |      |        |  |  |

| Molded Package Thickness   | A2               | .115       | .130 | .195   |  |  |

| Base to Seating Plane      | A1               | .015       | _    | _      |  |  |

| Shoulder to Shoulder Width | E                | .290       | .310 | .325   |  |  |

| Molded Package Width       | E1               | .240       | .250 | .280   |  |  |

| Overall Length             | D                | .348       | .365 | .400   |  |  |

| Tip to Seating Plane       | L                | .115       | .130 | .150   |  |  |

| Lead Thickness             | С                | .008       | .010 | .015   |  |  |

| Upper Lead Width           | b1               | .040       | .060 | .070   |  |  |

| Lower Lead Width b         |                  | .014       | .018 | .022   |  |  |

| Overall Row Spacing § eB   |                  | -          | _    | .430   |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-018B

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.              | X /XX XXX                                                                                                                                                                                                                                                                                                                                                                                                      | Examples:                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device  Device:       | Temperature Range Pattern Range  24AA65 - 64K I <sup>2</sup> C 1.8V Serial EEPROM (100 kHz) 24AA65T - 64K I <sup>2</sup> C 1.8V Serial EEPROM (100 kHz) 24LC65 - 64K I <sup>2</sup> C Serial EEPROM (100 kHz/400 kHz) 24LC65T - 64K I <sup>2</sup> C Serial EEPROM (Tape and Reel) 24C65T - 64K I <sup>2</sup> C 4.5V Serial EEPROM (400 kHz) 24C65T - 64K I <sup>2</sup> C 4.5V Serial EEPROM (Tape and Reel) | <ul> <li>a) 24LC65T-I/SM: 64 Kbit Smart Serial,<br/>Tape and Reel, 5.28 mm SOIJ package,<br/>Industrial temperature, 2.5V</li> <li>b) 24LC65-I/P: 64 Kbit Smart Serial,<br/>Industrial temperature, PDIP package,<br/>2.5V</li> <li>c) 24AA65T-/SM: 64 Kbit Smart Serial,<br/>Tape and Reel, 5.28 mm SOIJ package,<br/>Commercial temperature, 1.8V</li> </ul> |

| Temperature<br>Range: | I = -40°C to +85°C<br>E = -40°C to +125°C                                                                                                                                                                                                                                                                                                                                                                      | d) 24C65-E/P: 64 Kbit Smart Serial,<br>Automotive temperature, PDIP, 5V                                                                                                                                                                                                                                                                                        |

| Package:              | P = Plastic DIP (300 mil Body) SM = Plastic SOIJ (5.28 mm Body, EIAJ standard)                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                |