## 0A

# Video Equalizer (3D+C) for DVI, HDMI Source/Repeater/ Sink Applications

# **General Description**

The DS16EV5110A is a multi-channel equalizer optimized for video cable extension Source/Repeater/Sink Applications. It operates between 250Mbps and 2.25Gbps with common applications at 1.65Gbps and 2.25Gbps (per data channel). It contains three Transition-Minimized Differential Signaling (TMDS) data channels and one clock channel as specified for DVI and HDMI interfaces. It provides compensation for skineffect and dielectric losses, a common phenomenon when transmitting video on commercially available high definition video cables.

The inputs conform to DVI and HDMI requirements and features programmable levels of input equalization. The programmable levels of equalization provide optimal signal boost and reduces inter-symbol interference. Eight levels of boost are selectable via a pin interface or by the optional System Management Bus.

The clock channel is optimized for clock rates of up to 225 MHz and features a signal detect circuit. To maximize noise immunity, the DS16EV5110A features a signal detector with programmable thresholds. The threshold is adjustable through a System Management Bus (SMBus) interface.

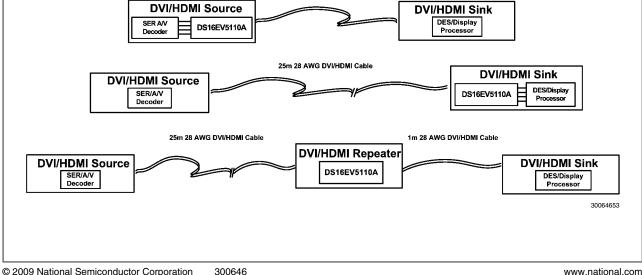

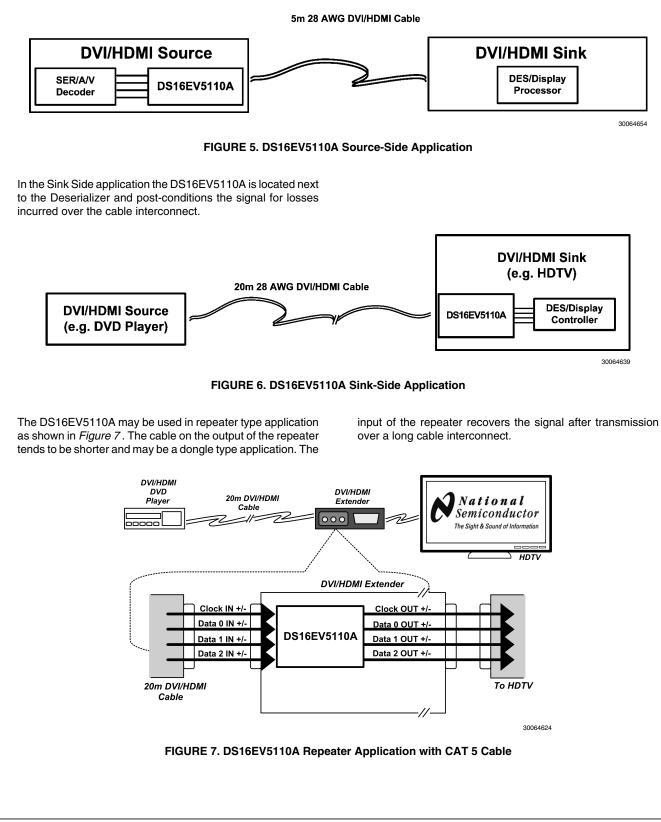

The DS16EV5110A may be used in Source Applications, Sink Applications, or as a Repeater.

The DS16EV5110A also provides support for system power management via output enable controls. Additional controls are provided via the SMBus enabling customization and optimization for specific applications requirements. These controls include programmable features such as output amplitude and boost controls as well as system level diagnostics.

The DS16EV5110A is a pin-for-pin replacement to the DS16EV5110. It features an enhanced CML output that presents a high impedance when powered down.

## **Features**

- 8 levels of equalization settable by 3 pins or through the SMBus interface

- DC-Coupled inputs and outputs

- Optimized for operation from 250 Mbps to 2.25 Gbps in support of UXGA, 480 I/P, 720 I/P, 1080 I, and 1080 P with 8, 10, and 12–bit Color Depth Resolutions

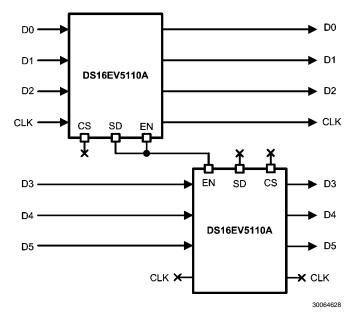

- Two DS16EV5110A devices support DVI/HDMI Dual Link

- DVI 1.0, and HDMI 1.3a Compatible TMDS Interface

- Clock channel signal detect (LOS)

- Enable for power savings standby mode

- System Management Bus (SMBus) provides control of boost, output amplitude, enable, and clock channel signal detect threshold

- Low power consumption: 475mW (Typical)

- 0.13 UI total jitter at 1.65 Gbps including cable

- Single 3.3V power supply

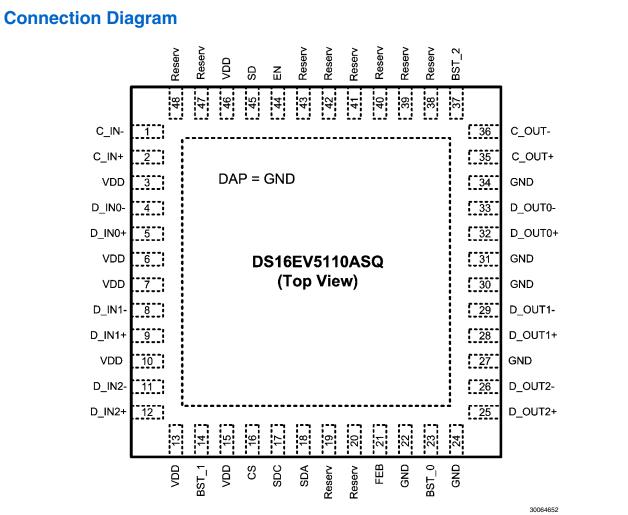

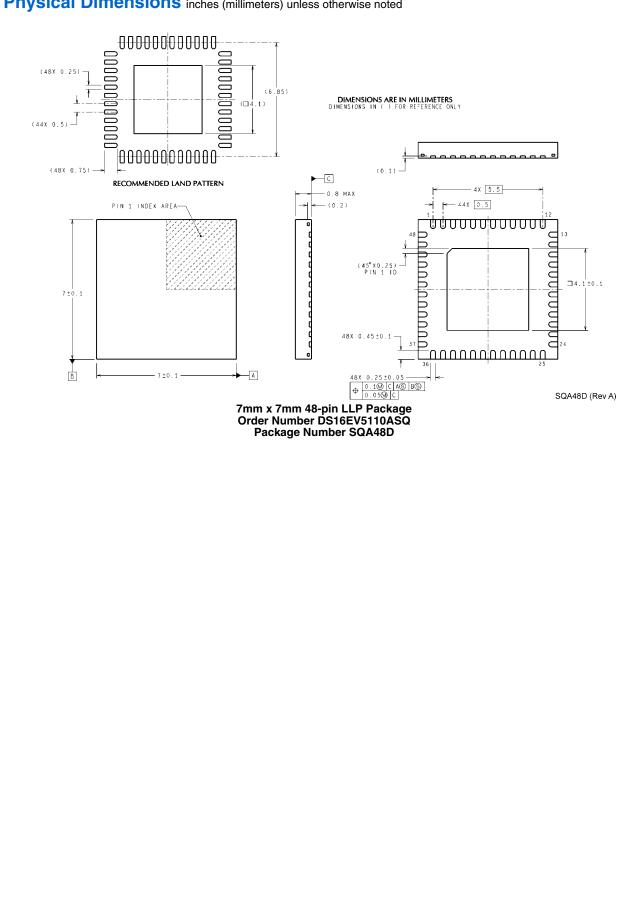

- Small 7mm x 7mm, 48-pin leadless LLP package

- -40°C to +85°C operating temperature range

- Extends TMDS cable reach over:

- 1. > 40 meters 24 AWG DVI Cable (1.65Gbps)

- 2. > 20 meters 28 AWG DVI Cable (1.65Gbps)

- 3. > 20 meters Cat5/Cat5e/Cat6 cables (1.65Gbps)

- 4. > 20 meters 28 AWG HDMI cables (2.25Gbps)

## **Applications**

- HDMI / DVI Cable Extenders

- HDMI / DVI Switches

- Projectors

- High Definition Displays

**Typical Application**

5m 28 AWG DVI/HDMI Cable

April 6, 2009

# **Pin Descriptions**

| Pin Name        | Pin Number                               | I/O, Type     | Description                                                                                                                                                                                                                                        |

|-----------------|------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HIGH SPEED      | DIFFERENT                                | AL I/O        |                                                                                                                                                                                                                                                    |

| C_IN-           | 1                                        | I, CML        | Inverting and non-inverting TMDS Clock inputs to the equalizer. An on-chip 50 $\Omega$ terminating                                                                                                                                                 |

| C_IN+           | 2                                        |               | resistor connects C_IN+ to VDD and C_IN- to VDD.                                                                                                                                                                                                   |

| D_IN0-          | 4                                        | I, CML        | Inverting and non-inverting TMDS Data inputs to the equalizer. An on-chip 50 $\Omega$ terminating                                                                                                                                                  |

| D_IN0+          | 5                                        | i, chil       | resistor connects D_IN0+ to VDD and D_IN0- to VDD.                                                                                                                                                                                                 |

| D_IN1-          | 8                                        | I, CML        |                                                                                                                                                                                                                                                    |

| D_IN1+          | 9                                        | I, ONL        | Inverting and non-inverting TMDS Data inputs to the equalizer. An on-chip $50\Omega$ terminating resistor connects D_IN1+ to VDD and D_IN1- to VDD.                                                                                                |

| D_IN2-          | 11                                       | I, CML        | Inverting and non-inverting TMDS Data inputs to the equalizer. An on-chip 50 $\Omega$ terminating                                                                                                                                                  |

| D_IN2+          | 12                                       | .,            | resistor connects D_IN2+ to VDD and D_IN2- to VDD.                                                                                                                                                                                                 |

| C_OUT-          | 36                                       | O, CML        | Inverting and non-inverting TMDS outputs from the equalizer. Open collector.                                                                                                                                                                       |

| C_OUT+          | 35                                       | -,-           |                                                                                                                                                                                                                                                    |

| D_OUT0-         | 33                                       | O, CML        | Inverting and non-inverting TMDS outputs from the equalizer. Open collector.                                                                                                                                                                       |

| D_OUT0+         | 32                                       | -, -          |                                                                                                                                                                                                                                                    |

| D_OUT1-         | 29                                       | O, CML        | Inverting and non-inverting TMDS outputs from the equalizer. Open collector.                                                                                                                                                                       |

| D_OUT1+         | 28                                       |               |                                                                                                                                                                                                                                                    |

| D_OUT2-         | 26                                       | O, CML        | Inverting and non-inverting TMDS outputs from the equalizer. Open collector.                                                                                                                                                                       |

| D_OUT2+         | 25                                       |               |                                                                                                                                                                                                                                                    |

| Equalization    | Control                                  |               |                                                                                                                                                                                                                                                    |

| BST_0           | 23                                       | I, LVCMOS     | BST_0, BST_1, and BST_2 select the equalizer boost level for EQ channels. BST_0,                                                                                                                                                                   |

| BST_1           | 14                                       | .,            | BST_1, and BST_2 are internally pulled Low. See <i>Table 2</i> .                                                                                                                                                                                   |

| BST_2           | 37                                       |               |                                                                                                                                                                                                                                                    |

| Device Contr    | ol                                       |               |                                                                                                                                                                                                                                                    |

| EN              | 44                                       | I, LVCMOS     | Enable Equalizer input. When held High, normal operation is selected. When held Low, standby mode is selected. EN is internally pulled High. Signal is global to all Data and Cloc channels.                                                       |

| FEB             | 21                                       | I, LVCMOS     | Force External Boost. When held High, the equalizer boost setting is controlled by the BST [0:2] pins. When held Low, the equalizer boost level is controlled through the SMBus (see <i>Table 1</i> ) control pins. FEB is internally pulled High. |

| SD              | 45                                       | O, LVCMOS     |                                                                                                                                                                                                                                                    |

| POWER           |                                          |               |                                                                                                                                                                                                                                                    |

| V <sub>DD</sub> | 3, 6, 7,<br>10, 13,<br>15, 46            | Power         | $V_{DD}$ pins should be tied to the $V_{DD}$ plane through a low inductance path. A 0.1µF bypass capacitor should be connected between each $V_{DD}$ pin to the GND planes.                                                                        |

| GND             | 22, 24,<br>27, 30,<br>31, 34             | GND           | Ground reference. GND should be tied to a solid ground plane through a low impedance path.                                                                                                                                                         |

| Exposed<br>Pad  | DAP                                      | GND           | The exposed pad at the center of the package must be connected to the ground plane.                                                                                                                                                                |

| System Mana     | agement Bus                              | (SMBus) Inte  | rface Control Pins                                                                                                                                                                                                                                 |

| SDA             | 18                                       | IO,<br>LVCMOS | SMBus Data Input / Output. Internally pulled High to 3.3V with High-Z pull up.                                                                                                                                                                     |

| SDC             | 17                                       | I, LVCMOS     | SMBus Clock Input. Internally pulled High to 3.3V with High-Z pull up.                                                                                                                                                                             |

| CS              | 16                                       | I, LVCMOS     | SMBus Chip select. When held High, the equalizer SMBus register is enabled. When held                                                                                                                                                              |

|                 |                                          | .,            | Low, the equalizer SMBus register is disabled. CS is internally pulled Low. CS is internally gated with SDC.                                                                                                                                       |

| Other           |                                          |               |                                                                                                                                                                                                                                                    |

| Reserv          | 19, 20, 38,<br>39, 40,41,<br>42, 43, 47, |               | Reserved. Do not connect.                                                                                                                                                                                                                          |

TOP VIEW - Not to Scale

#### **Ordering Information**

| NSID           | Tape & Reel Quantity | Package |

|----------------|----------------------|---------|

| DS16EV5110ASQ  | 250                  | SQA48D  |

| DS16EV5110ASQX | 2,500                | SQA48D  |

3

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>DD</sub> ) | -0.5V to +4.0V  |

|-----------------------------------|-----------------|

| LVCMOS Input Voltage              | -0.5V + 4.0V    |

| LVCMOS Output Voltage             | -0.5V to 4.0V   |

| CML Input/Output Voltage          | -0.5V to 4.0V   |

| Junction Temperature              | +150°C          |

| Storage Temperature               | -65°C to +150°C |

| Lead Temp. (Soldering, 5 sec.)    | +260°C          |

|                                   |                 |

| ESD Rating                   |        |

|------------------------------|--------|

| HBM, 1.5 kΩ, 100 pF          | >6 kV  |

| Thermal Resistance           |        |

| θ <sub>JA</sub> , No Airflow | 30°C/W |

## **Recommended Operating**

### **Conditions** (Notes 2, 3)

|                                            | Min | Тур | Max | Units |

|--------------------------------------------|-----|-----|-----|-------|

| Supply Voltage<br>(V <sub>DD</sub> to GND) | 3.0 | 3.3 | 3.6 | V     |

| Ambient Temperature                        | -40 | 25  | +85 | °C    |

# **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless other specified. (Notes 2, 3)

| Symbol                          | Parameter                                 | Conditions                                                                      | Min                  | Тур | Max                  | Units             |

|---------------------------------|-------------------------------------------|---------------------------------------------------------------------------------|----------------------|-----|----------------------|-------------------|

| LVCMOS DC                       | SPECIFICATIONS                            |                                                                                 |                      |     |                      |                   |

| I <sub>IH-PU</sub>              | High Level Input Leakage Current          | LVCMOS pins with internal pull-up resistors                                     | -10                  |     | +10                  | μA                |

| I <sub>IH-PD</sub>              | High Level Input Leakage Current          | LVCMOS pins with internal pull-<br>down resistors                               | 80                   |     | 105                  | μA                |

| I <sub>IL-PU</sub>              | Low Level Input Leakage Current           | LVCMOS pins with internal pull-up resistors                                     | -20                  |     | -10                  | μA                |

| IL-PD                           | Low Level Input Leakage Current           | LVCMOS pins with internal pull-<br>down resistors                               | -10                  |     | +10                  | μA                |

| V <sub>IH</sub>                 | High Level Input Voltage                  |                                                                                 | 2.0                  |     | VDD                  | V                 |

| V <sub>IL</sub>                 | Low Level Input Voltage                   |                                                                                 | 0                    |     | 0.8                  | V                 |

| V <sub>он</sub>                 | High Level Output Voltage                 | SD Pin, I <sub>OH</sub> = -3mA                                                  | 2.4                  |     |                      | V                 |

| V <sub>OL</sub>                 | Low Level Output Voltage                  | SD Pin, I <sub>OL</sub> = 3mA                                                   |                      |     | 0.4                  | V                 |

| POWER                           | -                                         | •                                                                               |                      |     | •                    |                   |

| PD                              | Power Dissipation                         | EN = High, Device Enabled                                                       |                      | 475 | 700                  | mW                |

|                                 |                                           | EN = Low, Power Down Mode                                                       |                      |     | 70                   | mW                |

| N                               | Supply Noise Tolerance (Note 4)           | DC to 50MHz                                                                     |                      | 100 |                      | mV <sub>P-F</sub> |

| CML INPUTS                      | 5                                         | •                                                                               |                      |     | •                    |                   |

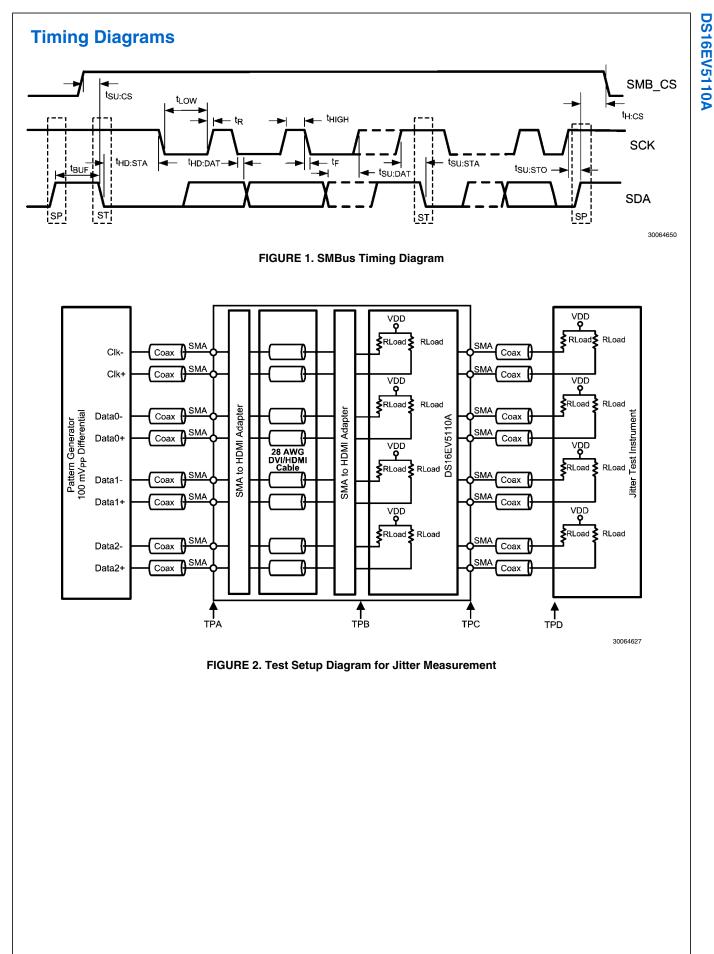

| V <sub>TX</sub>                 | Input Voltage Swing (Launch<br>Amplitude) | Measured differentially at TPA ( <i>Figure 2</i> )                              | 800                  |     | 1200                 | mV <sub>P-F</sub> |

| VICMDC                          | Input Common-Mode Voltage                 | DC-Coupled Requirement<br>Measured at TPA ( <i>Figure 2</i> )                   | V <sub>DD</sub> -0.3 |     | V <sub>DD</sub> -0.2 | V                 |

| V <sub>IN</sub>                 | Input Voltage Swing                       | Measured differentially at TPB ( <i>Figure 2</i> )                              |                      | 120 |                      | mV <sub>P-P</sub> |

| R <sub>LI</sub>                 | Differential Input Return Loss            | 100 MHz– 825 MHz, with fixture's effect de-embedded                             |                      | 10  |                      | dB                |

| R <sub>IN</sub>                 | Input Resistance                          | IN+ to VDD and IN- to VDD                                                       | 45                   | 50  | 55                   | Ω                 |

| CML OUTPU                       | ITS                                       | •                                                                               |                      |     | •                    |                   |

| V <sub>o</sub>                  | Output Voltage Swing                      | Measured differentially with OUT+ and OUT- terminated by $50\Omega$ to VDD      | 800                  |     | 1200                 | mV <sub>P-F</sub> |

| V <sub>OCM</sub>                | Output common-mode Voltage                | Measured Single-ended                                                           | V <sub>DD</sub> -0.3 |     | V <sub>DD</sub> -0.2 | V                 |

| OFF                             | Output Leakage Current                    | $V_{OUT} = 3.6V, V_{DD} = open or 0V$                                           |                      | ±1  |                      | μA                |

| t <sub>R</sub> , t <sub>F</sub> | Transition Time                           | 20% to 80% of differential output voltage, measured within 1" from output pins. | 75                   |     | 240                  | ps                |

| Symbol            | Parameter                                              | Conditions                                                                         | Min  | Тур   | Max   | Units             |

|-------------------|--------------------------------------------------------|------------------------------------------------------------------------------------|------|-------|-------|-------------------|

| t <sub>ccsк</sub> | Inter Pair Channel-to-Channel<br>Skew (all 4 Channels) | Difference in 50% crossing<br>between shortest and longest<br>channels             |      | 25    |       | ps                |

| t <sub>D</sub>    | Latency                                                |                                                                                    |      | 350   |       | ps                |

| OUTPUT JIT        | TER                                                    |                                                                                    |      |       |       |                   |

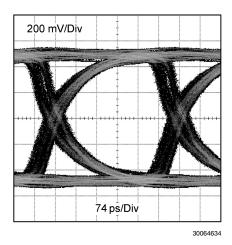

| TJ1               | Total Jitter at 1.65 Gbps                              | 20m 28 AWG STP DVI Cable<br>Data Paths<br>EQ Setting 0x04 PRBS7<br>(Notes 5, 6, 7) |      | 0.13  | 0.17  | UI <sub>P-P</sub> |

| TJ2               | Total Jitter at 2.25 Gbps                              | 20m 28 AWG STP DVI Cable<br>Data Paths<br>EQ Setting 0x04 PRBS7<br>(Notes 5, 6, 7) |      | 0.2   |       | UI <sub>P-F</sub> |

| TJ3               | Total Jitter at 165 MHz                                | Clock Paths<br>Clock Pattern<br>(Notes 5, 6, 7)                                    |      |       | 0.165 | UI <sub>P-F</sub> |

| TJ4               | Total Jitter at 225 MHz                                | Clock Paths<br>Clock Pattern<br>(Notes 5, 6, 7)                                    |      | 0.165 |       | UI <sub>P-F</sub> |

| RJ                | Random Jitter                                          | (Notes 7, 8)                                                                       |      | 3     |       | ps <sub>rms</sub> |

| BIT RATE          |                                                        | · ·                                                                                |      |       | 2     |                   |

| F <sub>CLK</sub>  | Clock Frequency                                        | Clock Path<br>(Note 5)                                                             | 25   |       | 225   | MHz               |

| BR                | Bit Rate                                               | Data Path<br>(Note 5)                                                              | 0.25 |       | 2.25  | Gbps              |

**Note 1:** "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. Absolute Maximum Numbers are guaranteed for a junction temperature range of -40°C to +125°C. Models are validated to Maximum Operating Voltages only.

Note 2: Typical values represent most likely parametric norms at  $V_{DD} = 3.3V$ ,  $T_A = 25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

Note 3: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes.

Note 4: Allowed supply noise (mV  $_{\rm P-P}$  sine wave) under typical conditions.

Note 5: Specification is guaranteed by characterization and is not tested in production.

Note 6: Deterministic jitter is measured at the differential outputs (TPC of *Figure 2*), minus the deterministic jitter before the test channel (TPA of *Figure 2*). Random jitter is removed through the use of averaging or similar means.

Note 7: Total Jitter is defined as peak-to-peak deterministic jitter from (Note 8) + 14.2 times random jitter in psrms.

**Note 8:** Random jitter contributed by the equalizer is defined as sq rt ( $J_{OUT}^2 - J_{IN}^2$ ).  $J_{OUT}$  is the random jitter at equalizer outputs in ps<sub>rms</sub>, see TPC of *Figure 2*;  $J_{IN}$  is the random jitter at the input of the equalizer in ps<sub>rms</sub>, see TPA of *Figure 2*.

# Electrical Characteristics — System Management Bus Interface (Notes 2, 3)

Over recommended operating supply and temperature ranges unless other specified.

| Symbol                 | Parameter                                                                                | Conditions                             | Min  | Тур  | Max             | Units |

|------------------------|------------------------------------------------------------------------------------------|----------------------------------------|------|------|-----------------|-------|

| System Bus             | Interface — DC Specifications                                                            |                                        |      |      |                 |       |

| V <sub>IL</sub>        | Data, Clock Input Low Voltage                                                            |                                        |      |      | 0.8             | V     |

| V <sub>IH</sub>        | Data, Clock Input High Voltage                                                           |                                        | 2.8  |      | V <sub>DD</sub> | V     |

| I <sub>PULLUP</sub>    | Current through pull-up resistor or current source                                       | VOL = 0.4V                             |      | 10   |                 | mA    |

| V <sub>DD</sub>        | Nominal Bus Voltage                                                                      |                                        | 3.0  |      | 3.6             | V     |

| LEAK-Bus               | Input Leakage per bus segment                                                            | (Note 9)                               | —200 |      | +200            | μA    |

| LEAK-Pin               | Input Leakage per device pin                                                             |                                        |      | —15  |                 | μA    |

| CI                     | Capacitance for SDA and SDC                                                              | (Notes 9, 10)                          |      |      | 10              | pF    |

| R <sub>TERM</sub>      | Termination Resistance                                                                   | V <sub>DD3.3</sub> , (Notes 9, 10, 11) |      | 1000 |                 | Ω     |

|                        | Interface Timing Specification                                                           |                                        |      |      |                 |       |

| FSMB                   | Bus Operating Frequency                                                                  | (Note 12)                              | 10   |      | 100             | kHz   |

| TBUF                   | Bus Free Time Between Stop and Start Condition                                           |                                        | 4.7  |      |                 | μs    |

| TSU:CS                 | Minimum time between SMB_CS being active and start condition                             | (Note 5)                               | 30   |      |                 | ns    |

| TH:CS                  | Minimum time between stop condition and releasing SMB_CS                                 | (Note 5)                               | 100  |      |                 | ns    |

| THD:STA                | Hold Time After (Repeated) Start<br>Condition. First CLK generated<br>after this period. | At I <sub>PULLUP</sub> , Max           | 4.0  |      |                 | μs    |

| TSU:STA                | Repeated Start Condition Setup<br>Time                                                   |                                        | 4.7  |      |                 | μs    |

| TSU:STO                | Stop Condition Setup Time                                                                |                                        | 4.0  |      |                 | μs    |

| THD:DAT                | Data Hold Time                                                                           |                                        | 300  |      |                 | ns    |

| TSU:DAT                | Data Setup Time                                                                          |                                        | 250  |      |                 | ns    |

| T <sub>TIMEOUT</sub>   | Detect Clock Low Timeout                                                                 | (Note 12)                              | 25   |      | 35              | ms    |

| T <sub>LOW</sub>       | Clock Low Period                                                                         |                                        | 4.7  |      |                 | μs    |

| T <sub>HIGH</sub>      | Clock High Period                                                                        | (Note 12)                              | 4.0  |      | 50              | μs    |

| Γ <sub>LOW</sub> :SEXT | Cumulative Clock Low Extend<br>Time (Slave Device)                                       | (Note 12)                              |      |      | 2               | ms    |

| F                      | Clock/Data Fall Time                                                                     | (Note 12)                              |      |      | 300             | ns    |

| R                      | Clock/Data Rise Time                                                                     | (Note 12)                              |      |      | 1000            | ns    |

| POR                    | Time in which a device must be operational after power-on reset                          | (Note 12)                              |      |      | 500             | ms    |

Note 9: Recommended value. Parameter not tested in production.

Note 10: Recommended maximum capacitance load per bus segment is 400pF.

Note 11: Maximum termination voltage should be identical to the device supply voltage.

Note 12: Compliant to SMBus 2.0 physical layer specification. See System Management Bus (SMBus) Specification Version 2.0, section 3.1.1 SMBus common AC specifications for details.

7

# System Management Bus (SMBus) and Configuration Registers

The System Management Bus interface is compatible to SM-Bus 2.0 physical layer specification. The use of the Chip Select signal is **required**. Holding the CS pin High enables the SMBus port allowing access to the configuration registers. Holding the CS pin Low disables the device's SMBus allowing communication from the host to other slave devices on the bus. In the STANDBY state, the System Management Bus remains active. When communication to other devices on the SMBus is active, the CS signal for the DS16EV5110As must be driven Low.

The address byte for all DS16EV5110As is AC'h. Based on the SMBus 2.0 specification, the DS16EV5110A has a 7-bit slave address of 1010110'b. The LSB is set to 0'b (for a WRITE), thus the 8-bit value is 1010 1100 'b or AC'h.

The SDC and SDA pins are 3.3V LVCMOS signaling and include high-Z internal pull up resistors. External low impedance pull up resistors maybe required depending upon SMBus loading and speed. Note, these pins are not 5V tolerant.

#### Transfer of Data via the SMBus

During normal operation the data on SDA must be stable during the time when SDC is High.

There are three unique states for the SMBus:

**START:** A High-to-Low transition on SDA while SDC is High indicates a message START condition.

**STOP:** A Low-to-High transition on SDA while SDC is High indicates a message STOP condition.

**IDLE:** If SDC and SDA are both High for a time exceeding  $t_{\rm BUF}$  from the last detected STOP condition or if they are High for a total exceeding the maximum specification for  $t_{\rm HIGH}$  then the bus will transfer to the IDLE state.

#### **SMBus Transactions**

The device supports WRITE and READ transactions. See Register Description table for register address, type (Read/ Write, Read Only), default value and function information.

#### Writing a Register

To write a register, the following protocol is used (see SMBus 2.0 specification).

- 1. The Host (Master) selects the device by driving its SMBus Chip Select (CS) signal High.

- 2. The Host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 3. The Device (Slave) drives the ACK bit ("0").

- 4. The Host drives the 8-bit Register Address.

- 5. The Device drives an ACK bit ("0").

- 6. The Host drive the 8-bit data byte.

- 7. The Device drives an ACK bit ("0").

- 8. The Host drives a STOP condition.

- 9. The Host de-selects the device by driving its SMBus CS signal Low.

The WRITE transaction is completed, the bus goes IDLE and communication with other SMBus devices may now occur.

#### **Reading a Register**

To read a register, the following protocol is used (see SMBus 2.0 specification).

- 1. The Host (Master) selects the device by driving its SMBus Chip Select (CS) signal High.

- 2. The Host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 3. The Device (Slave) drives the ACK bit ("0").

- 4. The Host drives the 8-bit Register Address.

- 5. The Device drives an ACK bit ("0").

- 6. The Host drives a START condition.

- 7. The Host drives the 7-bit SMBus Address, and a "1" indicating a READ.

- 8. The Device drives an ACK bit "0".

- 9. The Device drives the 8-bit data value (register contents).

- 10. The Host drives a NACK bit "1" indicating end of the READ transfer.

- 11. The Host drives a STOP condition.

- 12. The Host de-selects the device by driving its SMBus CS signal Low.

The READ transaction is completed, the bus goes IDLE and communication with other SMBus devices may now occur. Please see *Table 1* for more information.

|                  |         |         |      |            | I. SMBus Register I | bescription  |            |            |                 |

|------------------|---------|---------|------|------------|---------------------|--------------|------------|------------|-----------------|

| Name             | Address | Default | Туре | Bit 7      | Bit 6 Bit 5 Bit 4   | Bit 3        | Bit 2      | Bit 1      | Bit 0           |

| Status           | 0x00    | 0x00    | RO   | ID Revisio | n                   | Reserved     | Reserved   | Reserved   | SD              |

| Status           | 0x01    | 0x00    | RO   | Reserved   | Boost 1             | EN           | Reserved   |            | 2               |

| Status           | 0x02    | 0x00    | RO   | Reserved   | Boost 3             | Reserved     | Boost 2    |            |                 |

| Internal         | 0x03    | 0x77    | RW   | EN (Int.)  | Boost Control       | EN (Int.)    | Reserved   |            |                 |

| Enable/          |         |         |      | 0:Enable   | (BC for CH0)        | 0:Enable     |            |            |                 |

| Individual       |         |         |      | 1:Disable  | 000 (Min Boost)     | 1:Disable    |            |            |                 |

| Channel          |         |         |      | (D_IN0±)   | 001                 | (C_IN±)      |            |            |                 |

| Boost            |         |         |      |            | 010                 |              |            |            |                 |

| Control          |         |         |      |            | 011                 |              |            |            |                 |

| for              |         |         |      |            | 100                 |              |            |            |                 |

| C_IN±,           |         |         |      |            | 101<br>110          |              |            |            |                 |

| D_IN0±           |         |         |      |            | 111 (Max Boost)     |              |            |            |                 |

| Individual       | 0x04    | 0x77    | RW   | EN (Int.)  | Boost Control       | EN (Int.)    | Boost Con  | trol       |                 |

| Channel          | 0X04    |         |      | 0:Enable   | (BC for CH2)        | 0:Enable     | (BC for CF |            |                 |

| Boost            |         |         |      | 1:Disable  | 000 (Min Boost)     | 1:Disable    | 000 (Min E | ,          |                 |

| Control          |         |         |      | (D_IN2±)   | 001                 | $(D_IN1\pm)$ | 001        | ,0001)     |                 |

| for              |         |         |      | (,         | 010                 | (,           | 010        |            |                 |

| D_IN1±,          |         |         |      |            | 011                 |              | 011        |            |                 |

| D_IN2±           |         |         |      |            | 100                 |              | 100        |            |                 |

|                  |         |         |      |            | 101                 |              | 101        |            |                 |

|                  |         |         |      |            | 110                 |              | 110        |            |                 |

|                  |         |         |      |            | 111 (Max Boost)     |              | 111 (Max I | · · · · ·  |                 |

| Signal           | 0x05    | 0x00    | RW   | Reserved   |                     |              |            | Threshold  | (mV)            |

| Detect ON        |         |         |      |            |                     |              |            | 00: 70 (De | efault)         |

| (SD_ON)          |         |         |      |            |                     |              |            | 01: 55     |                 |

|                  |         |         |      |            |                     |              |            | 10: 90     |                 |

|                  |         |         |      |            |                     |              |            | 11:75      | <i></i>         |

| Signal           | 0x06    | 0x00    | RW   | Reserved   |                     |              |            | Threshold  |                 |

| Detect OFF       |         |         |      |            |                     |              |            | 00: 40 (De | efault)         |

| (SD_OFF)         |         |         |      |            |                     |              |            | 01: 30     |                 |

|                  |         |         |      |            |                     |              |            | 10: 55     |                 |

| SMBus or         | 0.07    | 0x00    | RW   | Deserve-   |                     |              |            | 11: 45     | SMBuo           |

| SMBUS or<br>CMOS | 0x07    |         |      | Reserved   |                     |              |            |            | SMBus<br>Enable |

| Control for      |         |         |      |            |                     |              |            |            | 0: Disable      |

| EN               |         |         |      |            |                     |              |            |            | 1: Enable       |

| Output           | 0x08    | 0x78    | RW   | Reserved   |                     | Output Lev   | /el:       | Reserved   |                 |

| Level            |         |         |      |            |                     | 00: 540 m    |            |            |                 |

|                  |         |         |      |            |                     | 01: 770 m    |            |            |                 |

|                  |         |         |      |            |                     | 10: 1000 n   |            |            |                 |

|                  |         |         |      |            |                     | 11: 1200 n   | nVp-p      |            |                 |

#### **TABLE 1. SMBus Register Descriptions**

Note: RO = Read Only, RW = Read/Write

DS16EV5110A

## **DS16EV5110A Device Description**

The DS16EV5110A video equalizer comprises three data channels, a clock channel, and a control interface including a SystemI Management Bus (SMBus) port.

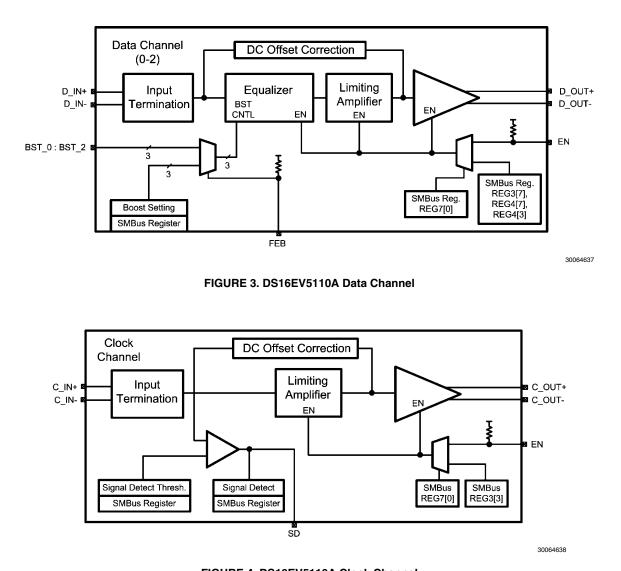

#### **DATA CHANNELS**

The DS16EV5110A provides three data channels. Each data channel consists of an equalizer stage, a limiting amplifier, a DC offset correction block, and a TMDS driver as shown in *Figure 3*.

#### **EQUALIZER BOOST CONTROL**

The data channel equalizers support eight programmable levels of equalization boost. The state of the FEB pin determines how the boost settings are controlled. If the FEB pin is held High, then the equalizer boost setting is controlled by the Boost Set pins (BST\_[0:2]) in accordance with Table 2. If this programming method is chosen, then the boost setting selected on the Boost Set pins is applied to all three data channels. When the FEB pin is held Low, the equalizer boost level is controlled through the SMBus. This programming method is accessed via the appropriate SMBus registers (see Table 1). Using this approach, equalizer boost settings can be programmed for each channel individually. FEB is internally pulled High (default setting); therefore if left unconnected, the boost settings are controlled by the Boost Set pins (BST [0:2]). The range of boost settings provided enables the DS16EV5110A to address a wide range of transmission line path loss scenarios, enabling support for a variety of data rates and formats.

#### TABLE 2. EQ Boost Control Table

| Control Via<br>SMBus | Control Via Pins<br>BST_2, BST_1, | EQ Boost Setting<br>at 825 MHz (dB) |  |  |  |  |

|----------------------|-----------------------------------|-------------------------------------|--|--|--|--|

| BC_2, BC_1,          | BST_0                             | (TYP)                               |  |  |  |  |

| BC_0                 | (FEB = 1)                         |                                     |  |  |  |  |

| (FEB = 0)            |                                   |                                     |  |  |  |  |

| 000                  | 000                               | 9                                   |  |  |  |  |

| 001                  | 001                               | 14                                  |  |  |  |  |

| 010                  | 010                               | 18                                  |  |  |  |  |

| 011                  | 011                               | 21                                  |  |  |  |  |

| 100                  | 100                               | 24                                  |  |  |  |  |

| 101                  | 101                               | 26                                  |  |  |  |  |

| 110                  | 110                               | 28                                  |  |  |  |  |

| 111                  | 111                               | 30                                  |  |  |  |  |

#### **DEVICE STATE AND ENABLE CONTROL**

The DS16EV5110A has an Enable feature which provides the ability to control device power consumption. This feature can

be controlled either via the Enable Pin (EN Pin) or via the Enable Control Bit which is accessed through the SMBus port (see *Table 1* and *Table 3*). If Enable is activated, the data channels and clock channel are placed in the ACTIVE state and all device blocks function as described. The DS16EV5110A can also be placed in STANDBY mode to save power. In this mode only the control interface including the SMBus port as well as the clock channel signal detection circuit remain active.

| Register 07[0]<br>(SMBus) | EN Pin<br>(CMOS) | Register 03[3]<br>(EN Control)<br>(SMBus) | Device State |

|---------------------------|------------------|-------------------------------------------|--------------|

| 0 : Disable               | 1                | Х                                         | ACTIVE       |

| 0 : Disable               | 0                | Х                                         | STANDBY      |

| 1 : Enable                | Х                | 0                                         | ACTIVE       |

| 1 : Enable                | Х                | 1                                         | STANDBY      |

#### **CLOCK CHANNEL**

The clock channel incorporates a limiting amplifier, a DC offset correction, and a TMDS driver as shown in *Figure 4*.

#### **CLOCK CHANNEL SIGNAL DETECT**

The DS16EV5110A features a signal detect circuit on the clock channel. The status of the clock signal can be determined by either reading the Signal Detect bit (SD) in the SMBus registers (see *Table 1*) or by the state of the SD pin. A logic High indicates the presence of a signal that has exceeded a specified threshold value (called SD\_ON). A logic Low means that the clock signal has fallen below a threshold value (called SD\_OFF). These values are programmed via the SMBus (*Table 1*). If not programmed via the SMBus, the thresholds take on the default values for the SD\_OFF and SD\_ON values can be changed through the SMBus. All threshold values specified are DC peak-to-peak differential signals (positive signal minus negative signal) at the input of the device.

#### **TABLE 4. Clock Channel Signal Detect Threshold Values**

| Bit 1 | Bit 0 | Bit 0 SD_OFF Threshold SD_ON Thresh<br>Register 06 (mV) Register 05 (m |              |

|-------|-------|------------------------------------------------------------------------|--------------|

| 0     | 0     | 40 (Default)                                                           | 70 (Default) |

| 0     | 1     | 30                                                                     | 55           |

| 1     | 0     | 55                                                                     | 90           |

| 1     | 1     | 45                                                                     | 75           |

FIGURE 4. DS16EV5110A Clock Channel

#### **OUTPUT LEVEL CONTROL**

The output amplitude of the TMDS drivers for both the data channels and the clock channel can be controlled via the SM-Bus (see *Table 1*). The default output level is 1000mV p-p. The following Table presents the output level values supported:

#### TABLE 5. Output Level Control Settings - REG 0x08[3:2]

|             |                    | <b>0</b>          |  |

|-------------|--------------------|-------------------|--|

| Bit 3 Bit 2 |                    | Output Level (mV) |  |

| 0 0 540     |                    | 540               |  |

| 0 1         |                    | 770               |  |

| 1           | 1 0 1000 (default) |                   |  |

| 1 1 1200    |                    | 1200              |  |

#### **AUTOMATIC ENABLE FEATURE**

It may be desired for the DS16EV5110A to be configured to automatically enter STANDBY mode if no clock signal is present. STANDBY mode can be implemented by connecting the Signal Detect (SD) pin to the external (LVCMOS) Enable (EN) pin. In order for this option to function properly, REG07[0] should be set to a "0" (default value). If the clock signal applied to the clock channel input swings above the SD\_ON threshold specified in the threshold register via the SMBus, then the SD pin is asserted High. If the SD pin is connected to the EN pin, this will enable the equalizer, limiting amplifier, and output buffer on the data channels and the limiting amplifier and output buffer on the clock channel; thus the DS16EV5110A will automatically enter the ACTIVE state. If the clock signal present falls below SD\_OFF threshold specified in the threshold register, then the SD pin will be asserted Low, causing the aforementioned blocks to be placed in the STANDBY state.

### **Application Information**

The DS16EV5110A is used to recondition DVI/HDMI video signals or differential signals with similar characteristics for signal loss and degradation due to transmission through a length of shielded or unshielded cable. The DS16EV5110A maybe used on the Source or Sink side of the application or as a Repeater (Sink and Source).

In the Source Side application the DS16EV5110A is located near the Serializer and conditions the signal for losses due to internal cabling or FR4 losses (backplane). The signal is then re-driven at full amplitude and reduced jitter over the external cable interconnect.

www.national.com

In general, the use of multiple equalizers is not recommended due to accumulation of random jitter.

#### **DVI 1.0 AND HDMI V1.2a APPLICATIONS**

A single DS16EV5110A can be used to implement cable extension solutions with various resolutions and screen refresh rates. The range of digital serial rates supported is between 250 Mbps and 1.65 Gbps. For applications requiring ultrahigh resolution for DVI applications (e.g., QXGA and WQX-GA), a "dual link" TMDS interface is required. This is easily configured by using two DS16EV5110A devices as shown in *Figure 8*.

Note the recommended connections between LVCMOS control pins. This provides the Automatic Enable feature for both devices based on the one active clock channel. In many applications the SMBus is not required (device is pin controlled), for this application simply leave the three SMBus pins open. SDC and SDA are internally pulled High, and CS is internally pulled Low, thus the SMBus is in the disabled state.

FIGURE 8. Connection in Dual Link Application

#### **HDMI V1.3 APPLICATION**

The DS16EV5110A can reliably extend operation to distances greater than 20 meters of 28 AWG HDMI cable at 2.25 Gbps, thereby supporting HDMI v1.3 for 1080p HDTV resolution with 12-bit color depth. Please note that the Electrical Characteristics specified in this document have not been tested for and are not guaranteed for 2.25 Gbps operation.

#### DC COUPLED DATA PATHS AND DVI/HDMI COMPLIANCE

The DS16EV5110A is designed to support TMDS differential pairs with DC coupled transmission lines. It contains integrated termination resistors (50 $\Omega$ ), pulled up to VDD at the input stage, and open collector outputs for DVI / HDMI for signal swing.

#### **CABLE SELECTION**

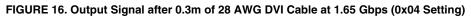

At higher frequencies, longer cable lengths produce greater losses due to the skin effect. The quality of the cable with respect to conductor wire gauge and shielding heavily influences performance. Thicker conductors have lower signal degradation per unit length. In nearly all applications, the DS16EV5110A equalization can be set to 0x04, and equalize up to 22 dB skin effect loss for all input cable configurations at all data rates, without degrading signal integrity.

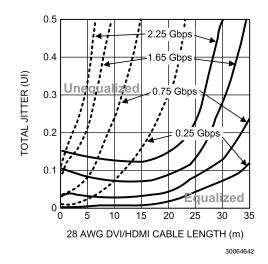

# 28 AWG STP DVI / HDMI CABLES RECOMMENDED BOOST SETTINGS

The following table presents the recommended boost control settings for various data rates and cable lengths for 28 AWG DVI/HDMI compliant configurations. Boost setting maybe done via the three BST[2:0] pins or via the respective register values.

#### TABLE 6. Boost Control Setting for STP Cables

| Setting | Data Rate                         | 28 AWG DVI / HDMI |  |  |  |

|---------|-----------------------------------|-------------------|--|--|--|

| 0x04    | 750 Mbps                          | 0–25m             |  |  |  |

| 0x04    | 1.65 Gbps                         | 1.65 Gbps 0–20m   |  |  |  |

| 0x06    | 750 Mbps                          |                   |  |  |  |

| 0x06    | 1.65 Gbps                         |                   |  |  |  |

| 0x03    | 2.25 Gbps                         | 0–15m             |  |  |  |

| 0x06    | 2.25 Gbps 15m to greater than 20m |                   |  |  |  |

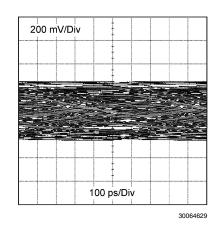

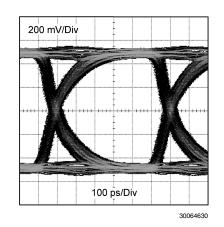

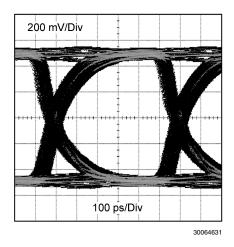

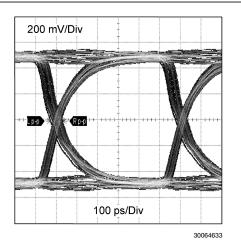

*Figure 9* shows the cable extension and jitter reduction obtained with the use of the equalizer. *Table 6* lists the various gain settings used versus cable length recommendations.

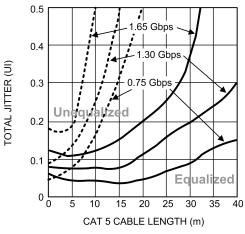

#### UTP (UNSHIELDED TWIST PAIRS) CABLES

The DS16EV5110A can be used to extend the length of UTP cables, such as Cat5, Cat5e and Cat6 to distances greater than 20 meters at 1.65 Gbps with < 0.13 UI of jitter. Please note that for non-standard DVI/HDMI cables, the user must ensure the clock-to-data channel skew requirements are met. Table 7 presents the recommended boost control settings for various data rates and cable lengths for UTP configurations:

| Setting Data Rate |                            | Cat5 Cable     |  |

|-------------------|----------------------------|----------------|--|

| 0x03              | 03 750 Mbps 0–25m          |                |  |

| 0x06              | 750 Mbps                   | 50 Mbps 25–45m |  |

| 0x03              | 1.65 Gbps Greater than 20m |                |  |

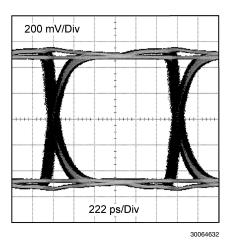

*Figure 10* shows the cable extension and jitter reduction obtained with the use of the equalizer. *Table 7* lists the various gain settings used versus cable length recommendations.

30064643

#### FIGURE 10. Equalized vs. Unequalized Jitter Performance Over Cat5 Cable

DS16EV5110A

## **General Recommendations**

The DS16EV5110A is a high performance circuit capable of delivering excellent performance. Careful attention must be paid to the details associated with high-speed design as well as providing a clean power supply. Refer to the LVDS Owner's Manual for more detailed information on high-speed design tips as well as many other available resources available addressing signal integrity design issues.

# PCB LAYOUT CONSIDERATIONS FOR DIFFERENTIAL PAIRS

The TMDS differential inputs and outputs must have a controlled differential impedance of  $100\Omega$ . It is preferable to route TMDS lines exclusively on one layer of the board, particularly for the input traces. The use of vias should be avoided if possible. If vias must be used, they should be used sparingly and must be placed symmetrically for each side of a given differential pair. Route the TMDS signals away from other signals and noise sources on the printed circuit board. All traces of TMDS differential inputs and outputs must be equal in length to minimize intra-pair skew.

#### LLP FOOTPRINT RECOMMENDATIONS

See National application note: AN-1187 for additional information on LLP packages footprint and soldering information.

#### POWER SUPPLY BYPASSING

Two approaches are recommended to ensure that the DS16EV5110A is provided with an adequate power supply. First, the supply (VDD) and ground (GND) pins should be connected to power planes routed on adjacent layers of the printed circuit board. The layer thickness of the dielectric should be minimized so that the VDD and GND planes create a low inductance supply with distributed capacitance. Second, careful attention to supply bypassing through the proper use of bypass capacitors is required. A 0.1µF bypass capacitor should be connected to each VDD pin such that the capacitor is placed as close as possible to the DS16EV5110A. Smaller body size capacitors can help facilitate proper component placement. Additionally, three capacitors with capacitance in the range of 2.2µF to 10µF should be incorporated in the power supply bypassing design as well. These capacitors can be either tantalum or an ultra-low ESR ceramic and should be placed as close as possible to the DS16EV5110A.

#### **EQUIVALENT I/O STRUCTURES**

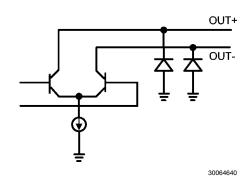

*Figure 11* shows the DS16EV5110A CML output structure and ESD protection circuitry.

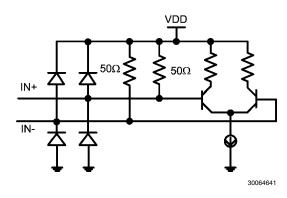

*Figure 12* shows the DS16EV5110A CML input structure and ESD protection circuitry.

FIGURE 11. Equivalent CML Output Structure

FIGURE 12. Equivalent CML Input Structure

# **Typical Performance Characteristics**

FIGURE 14. Output Signal after 20m of Cat5 Cable at 1.65 Gbps (0x06 Setting)

FIGURE 15. Output Signal after 30m of 28 AWG DVI Cable at 750 Mbps (0x06 Setting)

FIGURE 17. Output Signal after 20m of 28 AWG HDMI Cable at 2.25 Gbps (0x06 Setting)

# Physical Dimensions inches (millimeters) unless otherwise noted

**DS16EV5110A**

# Notes

DS16EV5110A

# Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Products                       |                              | Design Support          |                                |

|--------------------------------|------------------------------|-------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools          | www.national.com/webench       |

| Audio                          | www.national.com/audio       | App Notes               | www.national.com/appnotes      |

| Clock and Timing               | www.national.com/timing      | Reference Designs       | www.national.com/refdesigns    |

| Data Converters                | www.national.com/adc         | Samples                 | www.national.com/samples       |

| Interface                      | www.national.com/interface   | Eval Boards             | www.national.com/evalboards    |

| LVDS                           | www.national.com/lvds        | Packaging               | www.national.com/packaging     |

| Power Management               | www.national.com/power       | Green Compliance        | www.national.com/quality/green |

| Switching Regulators           | www.national.com/switchers   | Distributors            | www.national.com/contacts      |

| LDOs                           | www.national.com/ldo         | Quality and Reliability | www.national.com/quality       |

| LED Lighting                   | www.national.com/led         | Feedback/Support        | www.national.com/feedback      |

| Voltage Reference              | www.national.com/vref        | Design Made Easy        | www.national.com/easy          |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions               | www.national.com/solutions     |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                | www.national.com/milaero       |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™             | www.national.com/solarmagic    |

| Wireless (PLL/VCO)             | www.national.com/wireless    | Analog University®      | www.national.com/AU            |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2009 National Semiconductor Corporation

For the most current product information visit us at www.national.com

R

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com