# AMD Geode™ SC2200 Processor Data Book

*March 2006* Publication ID: 32580B

AMD Geode™ SC2200 Processor Data Book

#### © 2006 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Contacts

www.amd.com

#### Trademarks

AMD, the AMD Arrow logo, and combinations thereof, and Geode and Virtual System Architecture are trademarks of Advanced Micro Devices, Inc.

Microsoft and Windows are registered trademarks of Microsoft Corporation in the United States and/or other jurisdictions.

MMX is a registered trademark of Intel Corporation in the United States and/or other jurisdictions.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# Contents

| List o | of Figu                                       | ures5                                                                                                                                                                                                                     |

|--------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List o | of Tab                                        | les9                                                                                                                                                                                                                      |

| 1.0    | 1.1                                           | view         13           General Description         13           Features         14                                                                                                                                    |

| 2.0    | 2.1<br>2.2<br>2.3<br>2.4                      | itecture Overview17GX1 Module17Video Processor Module22Core Logic Module23Superl/O Module23Clock, Timers, and Reset Logic24                                                                                               |

| 3.0    | 3.1<br>3.2<br>3.3<br>3.4                      | al Definitions25Ball Assignments27Strap Options45Multiplexing Configuration46Signal Descriptions52eral Configuration Block75                                                                                              |

| -      | 4.1<br>4.2<br>4.3<br>4.4                      | Configuration Block Addresses75Multiplexing, Interrupt Selection, and Base Address Registers76WATCHDOG83High-Resolution Timer85Clock Generators and PLLs87                                                                |

| 5.0    | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | PerI/O Module95Features96Module Architecture97Configuration Structure/Access98Standard Configuration Registers100Real-Time Clock (RTC)111System Wakeup Control (SWC)123ACCESS.bus Interface128Legacy Functional Blocks136 |

| 6.0  | Core  | e Logic Module                            | 149 |

|------|-------|-------------------------------------------|-----|

|      | 6.1   | Feature List                              | 149 |

|      | 6.2   | Module Architecture                       | 150 |

|      | 6.3   | Register Descriptions                     | 183 |

|      | 6.4   | Chipset Register Space                    | 198 |

| 7.0  | Vide  | eo Processor Module                       | 319 |

|      | 7.1   | Module Architecture                       | 320 |

|      | 7.2   | Functional Description                    |     |

|      | 7.3   | Register Descriptions                     | 338 |

| 8.0  | Deb   | bugging and Monitoring                    | 365 |

|      | 8.1   | Testability (JTAG)                        | 365 |

|      | 8.2   | Engineering Note: Carmel Rev B1 - DFT ACP |     |

| 9.0  | Elec  | ctrical Specifications                    | 369 |

|      | 9.1   | General Specifications                    |     |

|      | 9.2   | DC Characteristics                        |     |

|      | 9.3   | AC Characteristics                        |     |

| 10.0 | Pacl  | kage Specifications                       | 443 |

|      | 10.1  | Thermal Characteristics                   |     |

|      | 10.2  |                                           |     |

| Арре | endix | A Support Documentation                   | 447 |

|      | A.1   | Order Information                         | 447 |

|      | A.2   | Data Book Revision History                | 448 |

# List of Figures

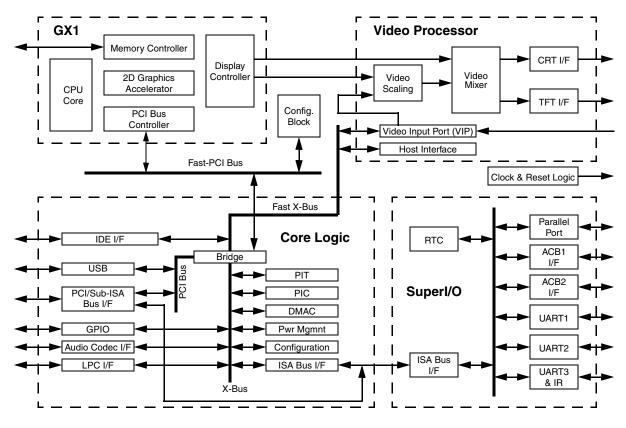

| Figure 1-1.  | Block Diagram                                                              | 13  |

|--------------|----------------------------------------------------------------------------|-----|

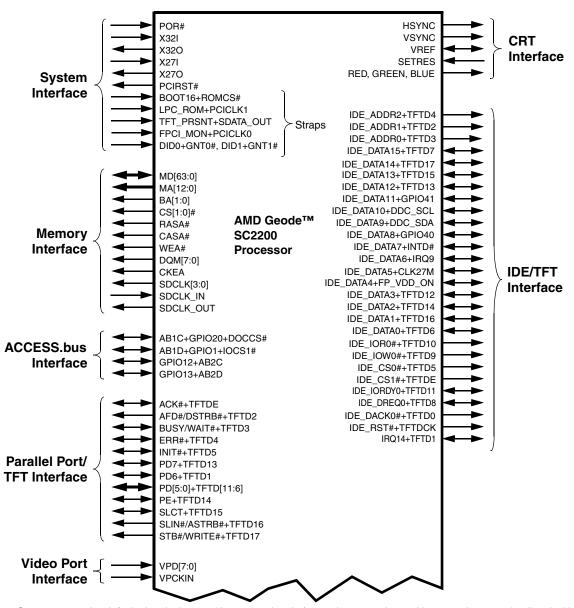

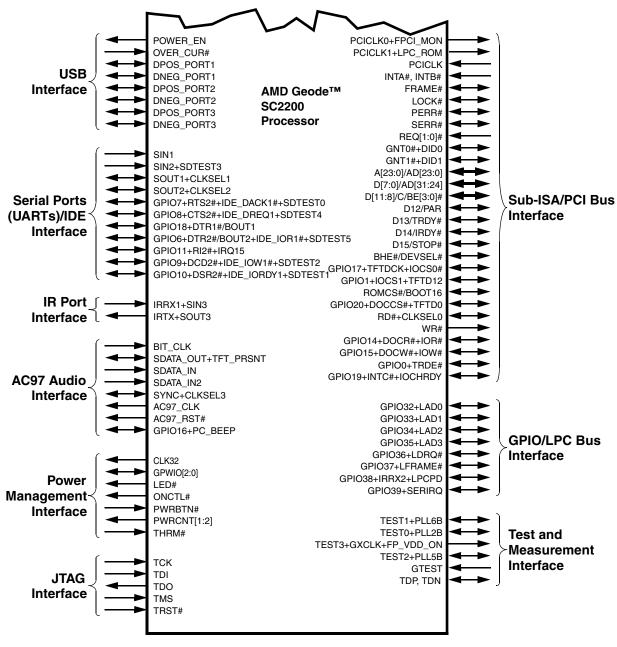

| Figure 3-1.  | Signal Groups                                                              | 25  |

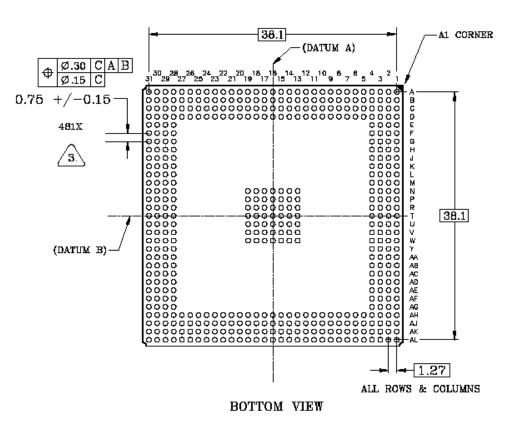

| Figure 3-2.  | BGU481 Ball Assignment Diagram                                             | 28  |

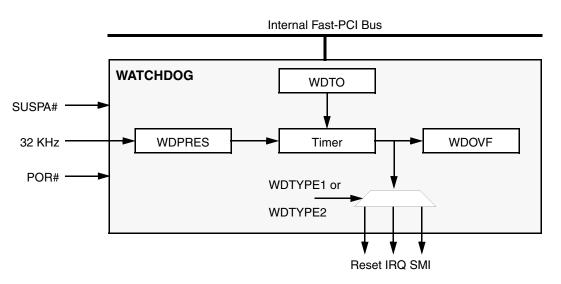

| Figure 4-1.  | WATCHDOG Block Diagram                                                     | 83  |

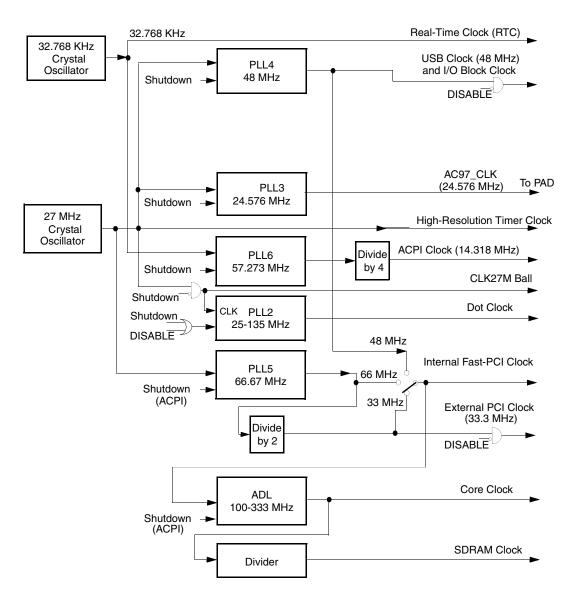

| Figure 4-2.  | Clock Generation Block Diagram                                             | 87  |

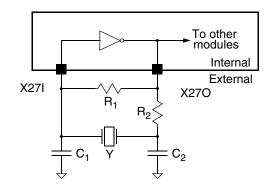

| Figure 4-3.  | Recommended Oscillator External Circuitry                                  | 88  |

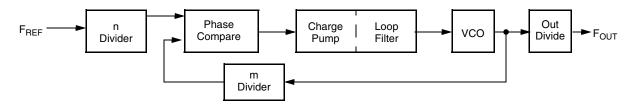

| Figure 4-4.  | PLL3 and Dividers Block Diagram                                            | 91  |

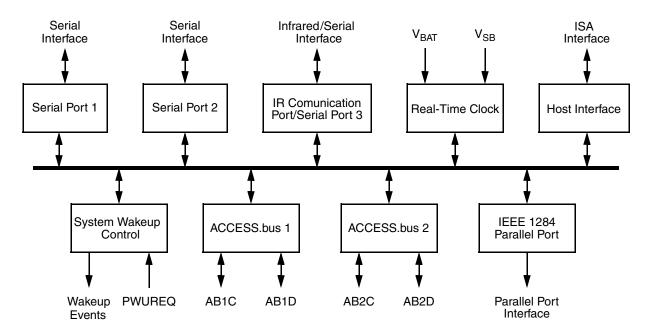

| Figure 5-1.  | SIO Block Diagram                                                          | 95  |

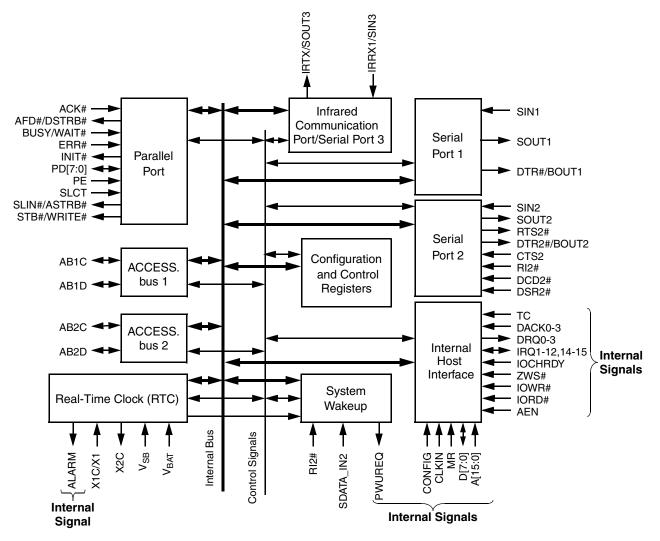

| Figure 5-2.  | Detailed SIO Block Diagram                                                 | 97  |

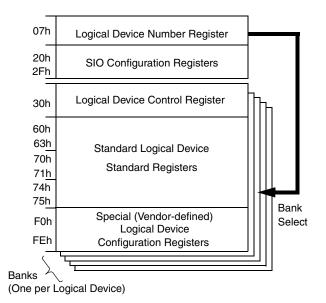

| Figure 5-3.  | Structure of the Standard Configuration Register File                      | 98  |

| Figure 5-4.  | Standard Configuration Registers Map                                       | 100 |

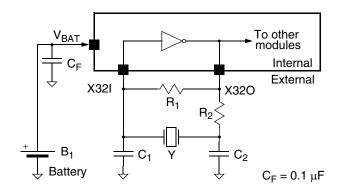

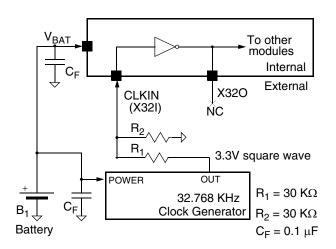

| Figure 5-5.  | Recommended Oscillator External Circuitry                                  |     |

| Figure 5-6.  | External Oscillator Connections                                            |     |

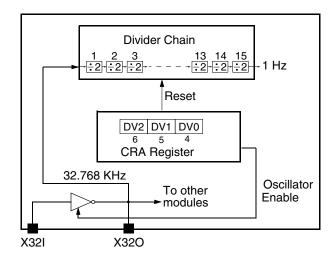

| Figure 5-7.  | Divider Chain Control                                                      | 112 |

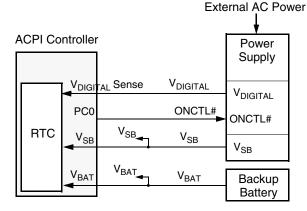

| Figure 5-8.  | Power Supply Connections                                                   | 114 |

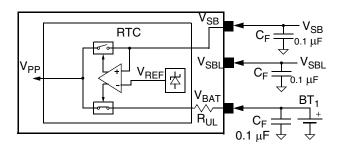

| Figure 5-9.  | Typical Battery Configuration                                              |     |

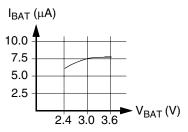

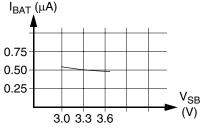

| Figure 5-10. | Typical Battery Current: Battery Backed Power Mode @ T <sub>C</sub> = 25°C |     |

| Figure 5-11. | Typical Battery Current: Normal Operation Mode                             |     |

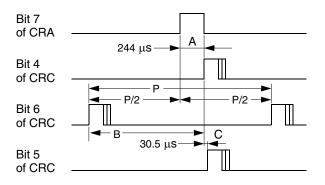

| Figure 5-12. | Interrupt/Status Timing                                                    |     |

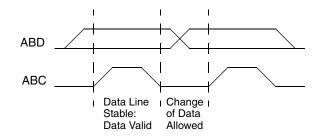

| Figure 5-13. | Bit Transfer                                                               |     |

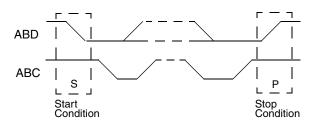

| Figure 5-14. | Start and Stop Conditions                                                  | 128 |

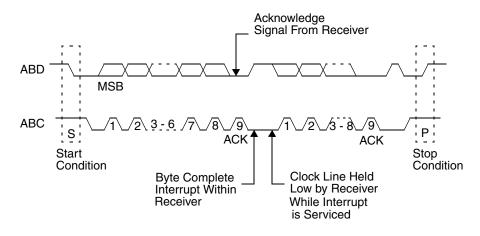

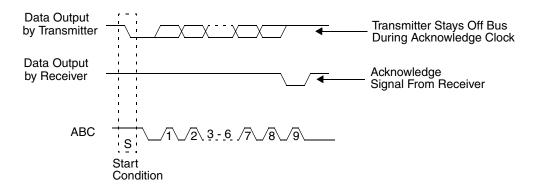

| Figure 5-15. | ACCESS.bus Data Transaction                                                |     |

| Figure 5-16. | ACCESS.bus Acknowledge Cycle                                               | 129 |

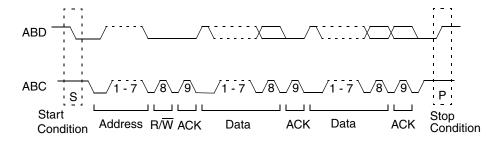

| Figure 5-17. | A Complete ACCESS.bus Data Transaction                                     |     |

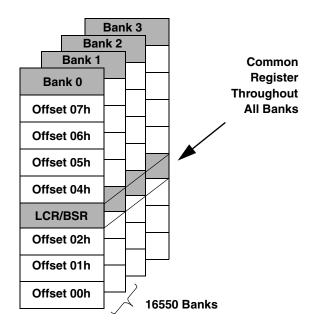

| Figure 5-18. | UART Mode Register Bank Architecture                                       |     |

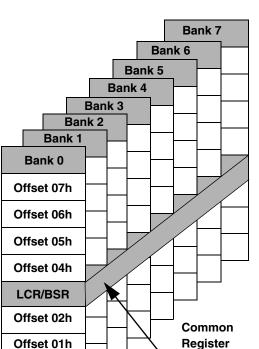

| Figure 5-19. | IRCP/SP3 Register Bank Architecture                                        |     |

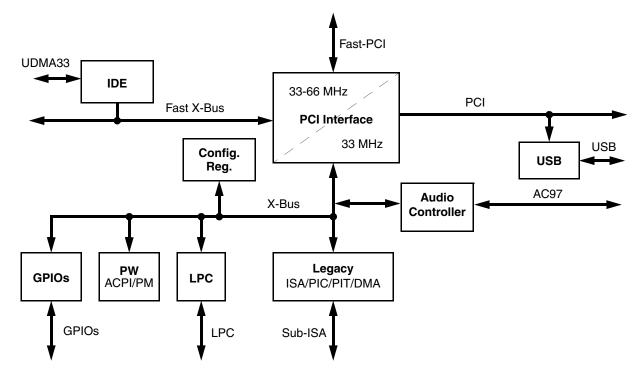

| Figure 6-1.  | Core Logic Module Block Diagram                                            |     |

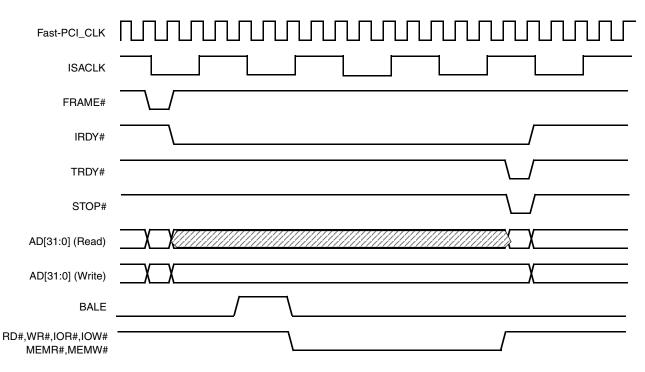

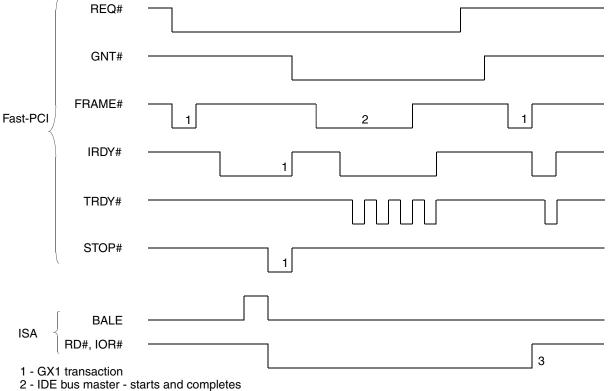

| Figure 6-2.  | Non-Posted Fast-PCI to ISA Access                                          |     |

| Figure 6-3.  | PCI to ISA Cycles with Delayed Transaction Enabled                         |     |

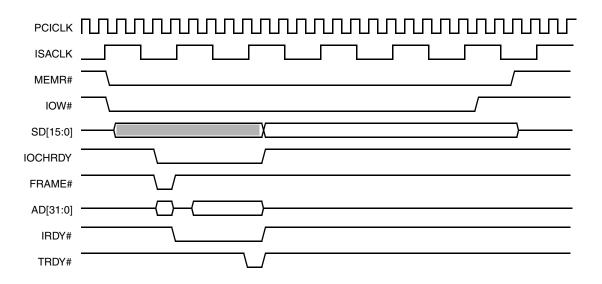

| Figure 6-4.  | ISA DMA Read from PCI Memory                                               |     |

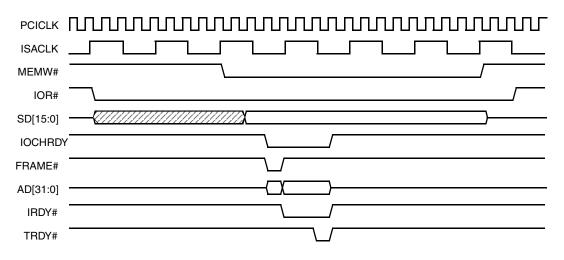

| Figure 6-5.  | ISA DMA Write to PCI Memory                                                |     |

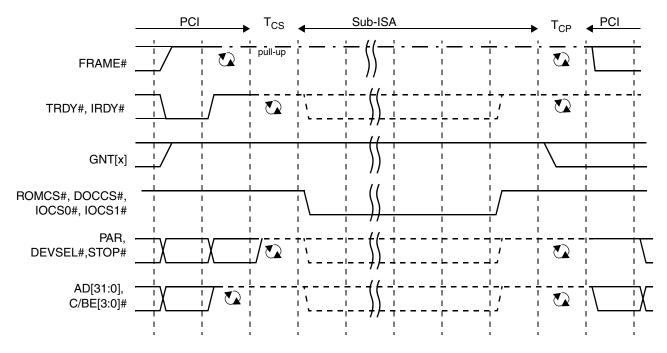

| Figure 6-6.  | PCI Change to Sub-ISA and Back                                             |     |

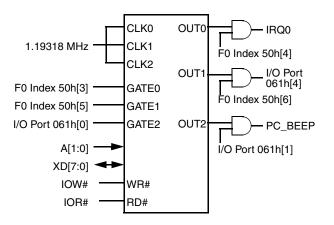

| Figure 6-7.  | PIT Timer                                                                  |     |

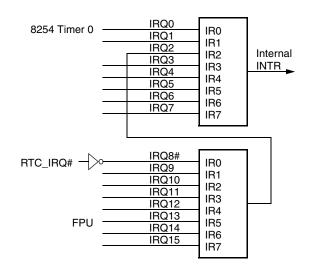

| Figure 6-8.  | PIC Interrupt Controllers                                                  | 163 |

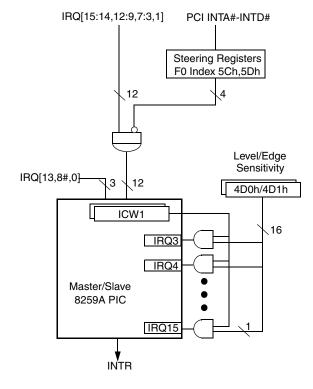

| Figure 6-9.  | PCI and IRQ Interrupt Mapping                                              |     |

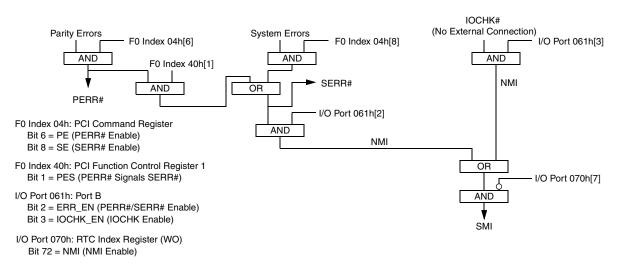

| Figure 6-10. | SMI Generation for NMI                                                     |     |

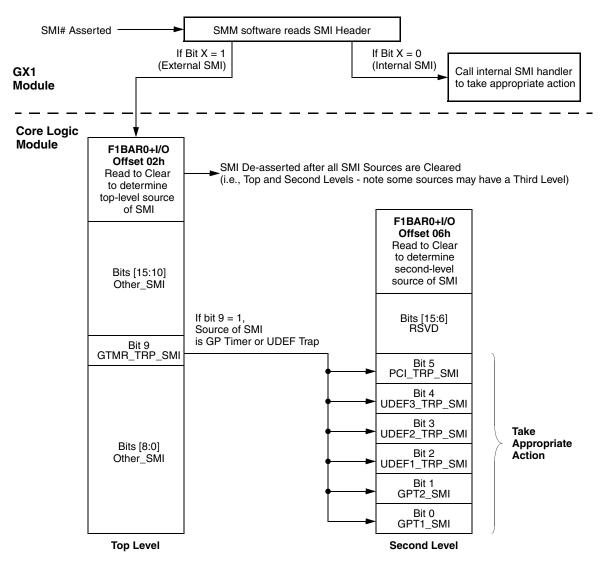

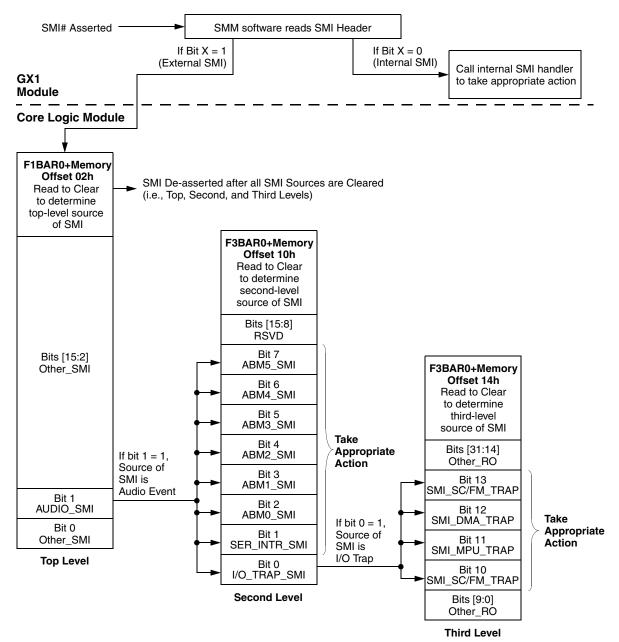

| Figure 6-11. | General Purpose Timer and UDEF Trap SMI Tree Example                       | 173 |

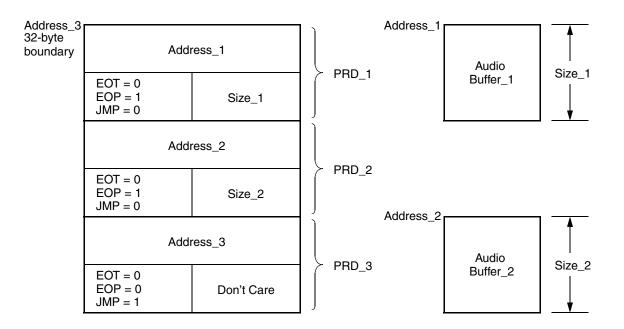

| Figure 6-12. | PRD Table Example                                                          | 177 |

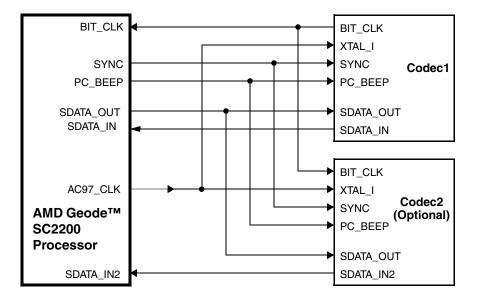

| Figure 6-13. | AC97 V2.0 Codec Signal Connections                                         | 178 |

| Figure 6-14. | Audio SMI Tree Example                                                     | 180 |

| Figure 6-15. | Typical Setup                                                              | 181 |

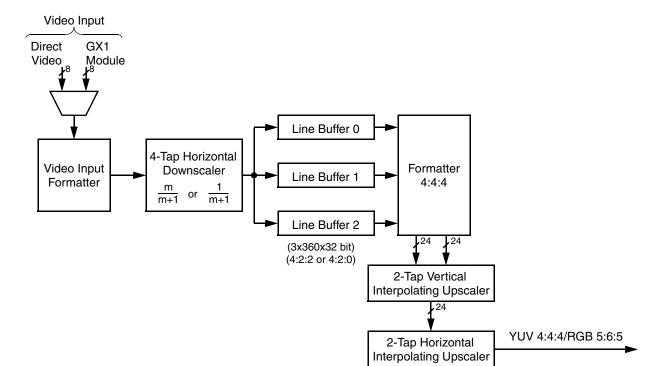

| Figure 7-1.  | Video Processor Block Diagram                                              |     |

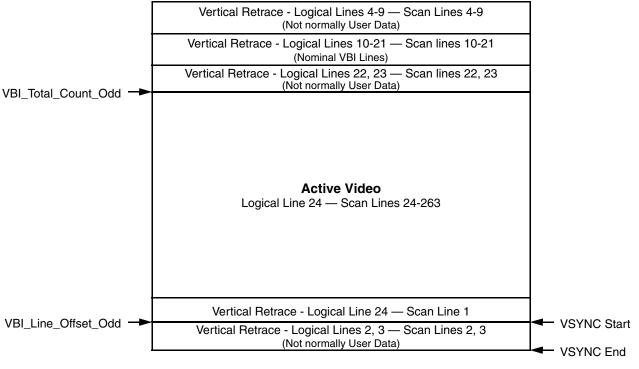

| Figure 7-2.  | NTSC 525 Lines, 60 Hz, Odd Field                                           |     |

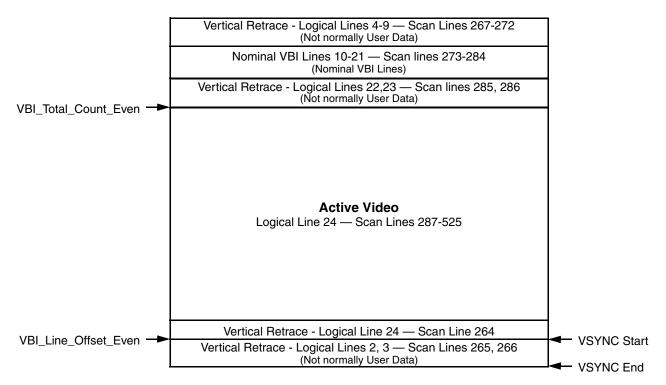

| Figure 7-3.  | NTSC 525 Lines, 60 Hz, Even Field                                          |     |

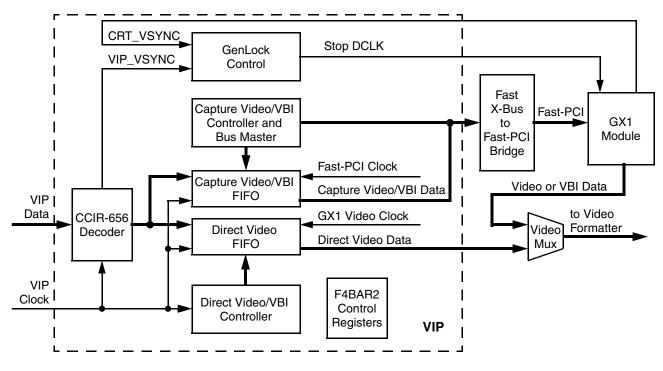

| Figure 7-4.  | VIP Block Diagram                                                          | 323 |

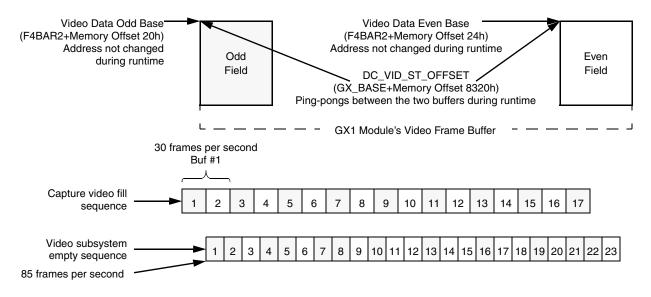

| Figure 7-5.  | Capture Video Mode Bob Example Using One Video Frame Buffer     |     |

|--------------|-----------------------------------------------------------------|-----|

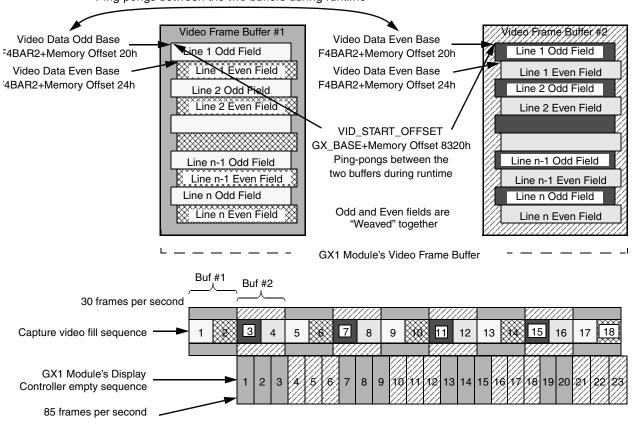

| Figure 7-6.  | Capture Video Mode Weave Example Using Two Video Frame Buffers  |     |

| Figure 7-7.  | Video Block Diagram                                             |     |

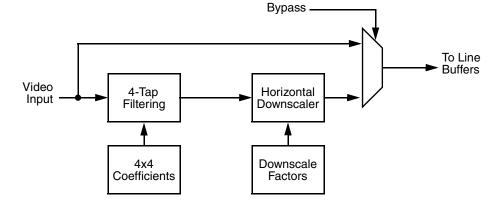

| Figure 7-8.  | Horizontal Downscaler Block Diagram                             | 328 |

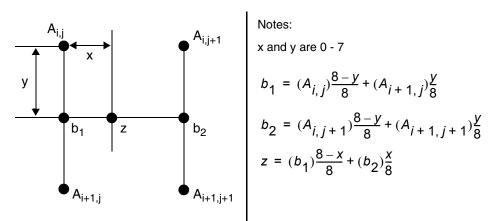

| Figure 7-9.  | Linear Interpolation Calculation                                | 329 |

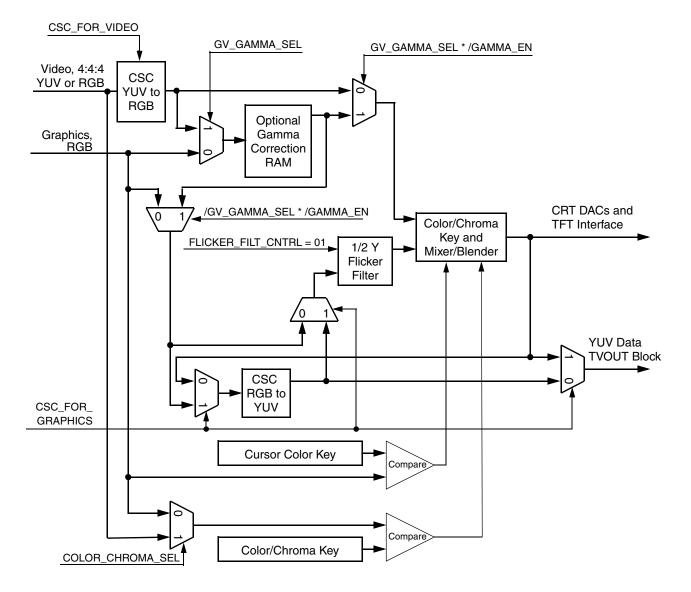

| Figure 7-10. | Mixer/Blender Block Diagram                                     | 330 |

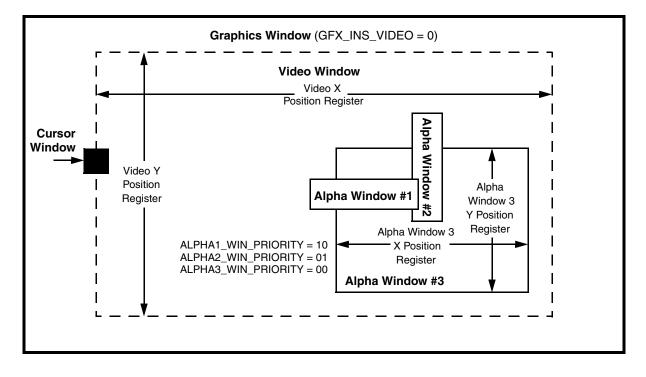

| Figure 7-11. | Graphics/Video Frame with Alpha Windows                         | 332 |

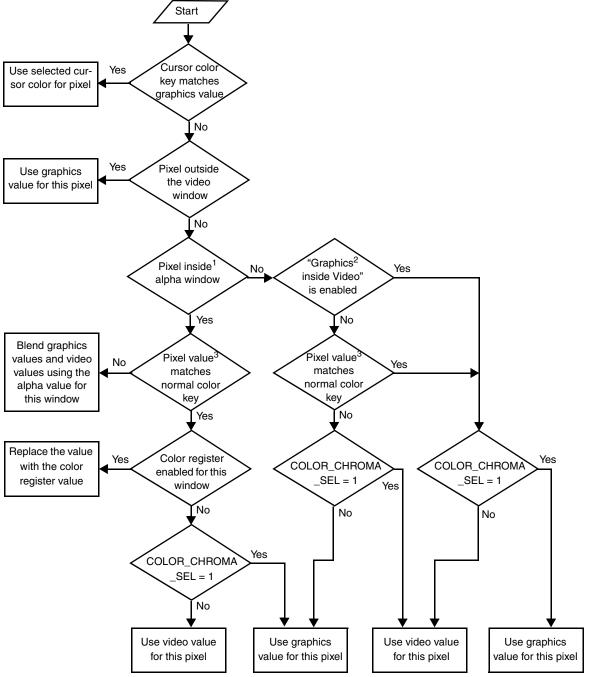

| Figure 7-12. | Color Key and Alpha Blending Logic                              |     |

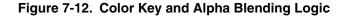

| Figure 7-13. | DAC Voltage Levels                                              |     |

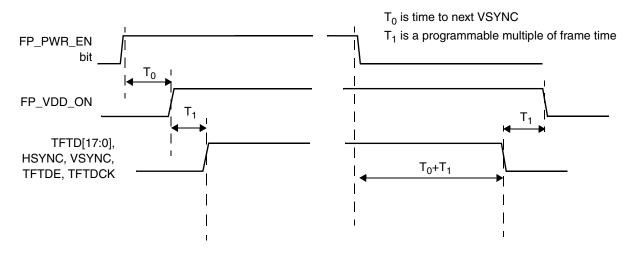

| Figure 7-14. | TFT Power Sequence                                              |     |

| Figure 7-15. | PLL Block Diagram                                               |     |

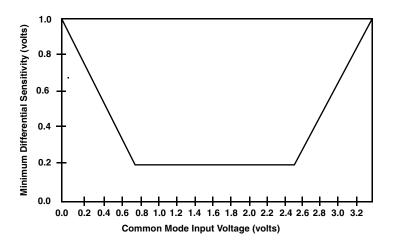

| Figure 9-1.  | Differential Input Sensitivity for Common Mode Range            |     |

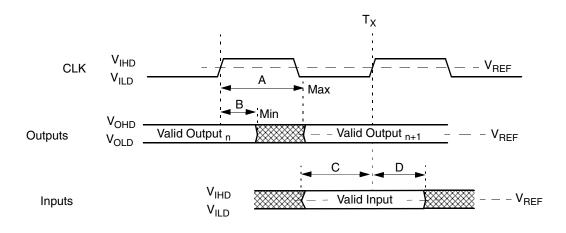

| Figure 9-2.  | General Drive level and Measurement Points                      |     |

| Figure 9-3.  | Drive Level and Measurement Points                              |     |

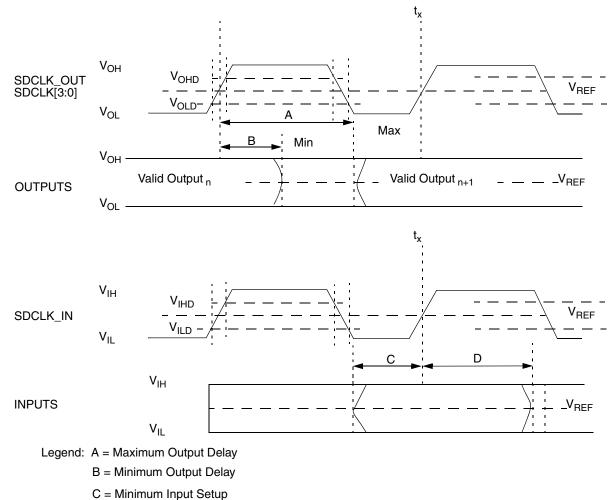

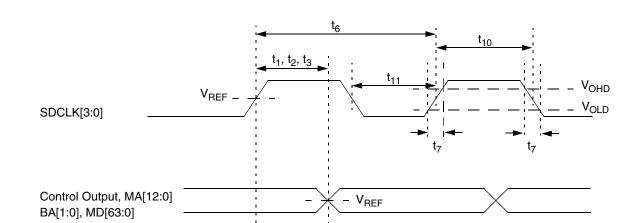

| Figure 9-4.  | Memory Controller Output Valid Timing Diagram                   |     |

| -            |                                                                 |     |

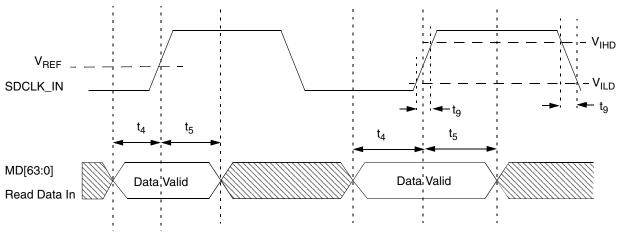

| Figure 9-5.  | Read Data In Setup and Hold Timing Diagram                      |     |

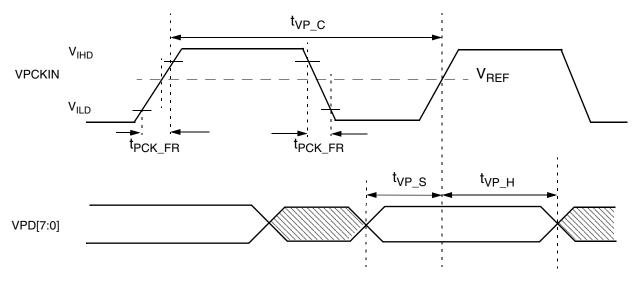

| Figure 9-6.  | Video Input Port Timing Diagram                                 |     |

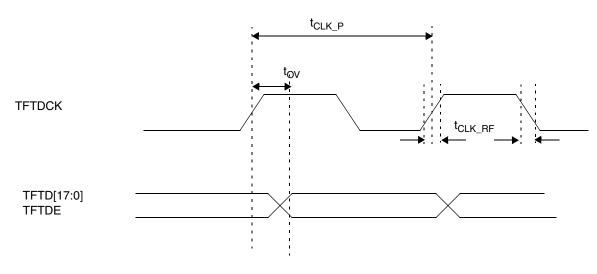

| Figure 9-7.  | TFT Timing Diagram                                              |     |

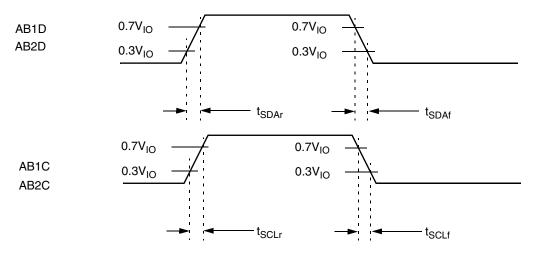

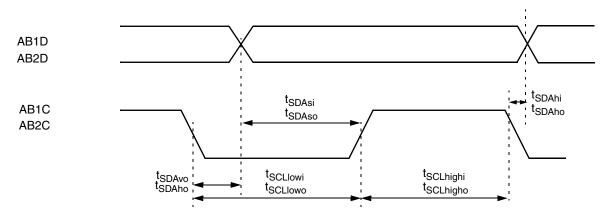

| Figure 9-8.  | ACB Signals: Rising Time and Falling Timing Diagram             |     |

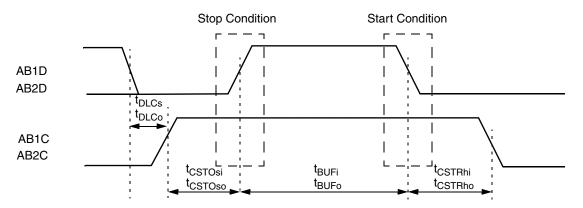

| Figure 9-9.  | ACB Start and Stop Condition Timing Diagram                     |     |

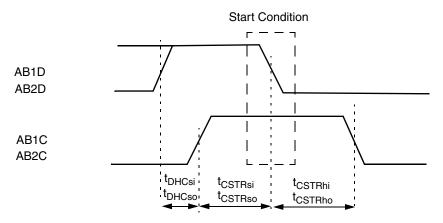

| Figure 9-10. | ACB Start Condition Timing Diagram                              |     |

| Figure 9-11. | ACB Data Bit Timing Diagram                                     |     |

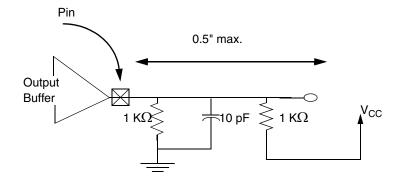

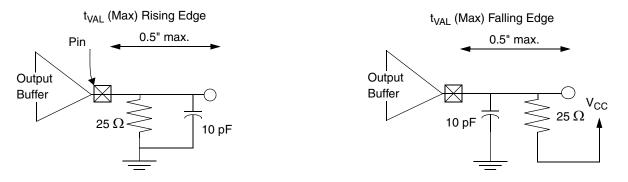

| Figure 9-12. | Testing Setup for Slew Rate and Minimum Timing                  | 394 |

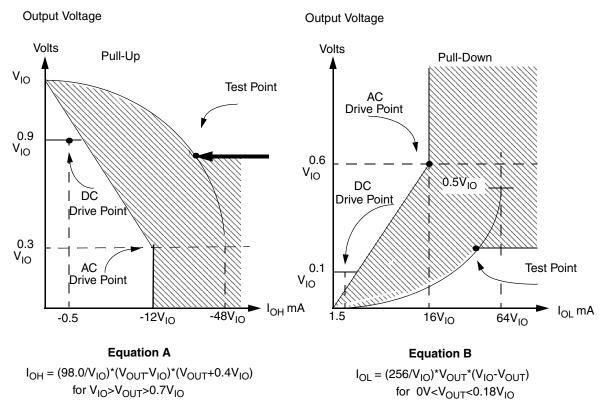

| Figure 9-13. | V/I Curves for PCI Output Signals                               | 395 |

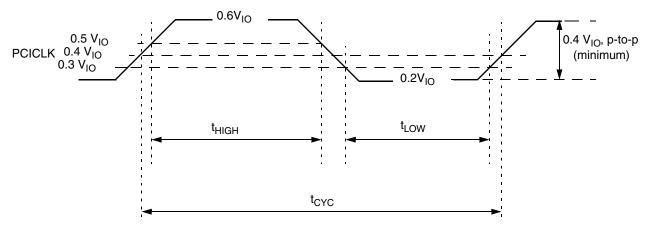

| Figure 9-14. | PCICLK Timing and Measurement Points                            | 396 |

| Figure 9-15. | Load Circuits for Maximum Time Measurements                     | 397 |

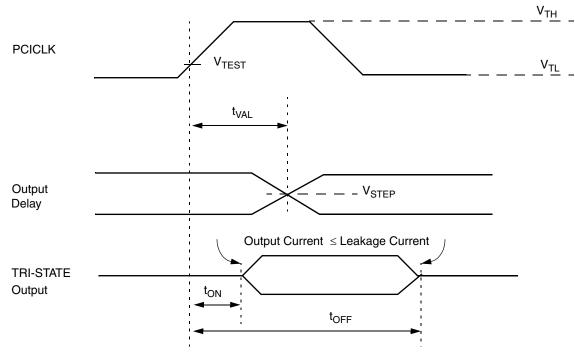

| Figure 9-16. | Output Timing Measurement Conditions                            | 398 |

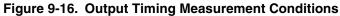

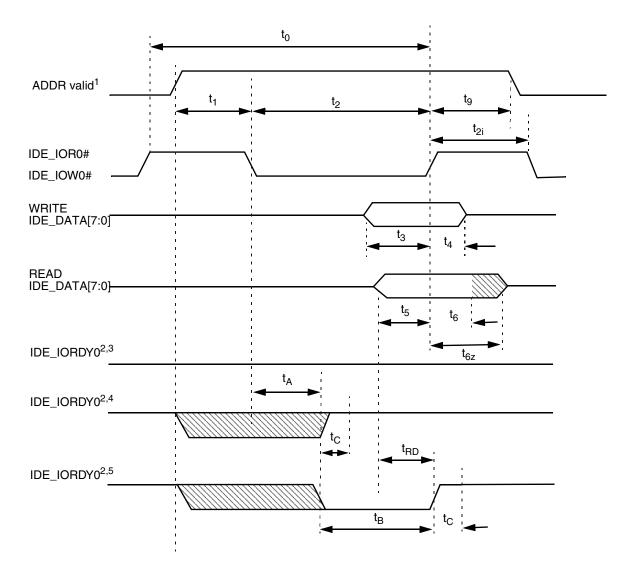

| Figure 9-17. | Input Timing Measurement Conditions                             |     |

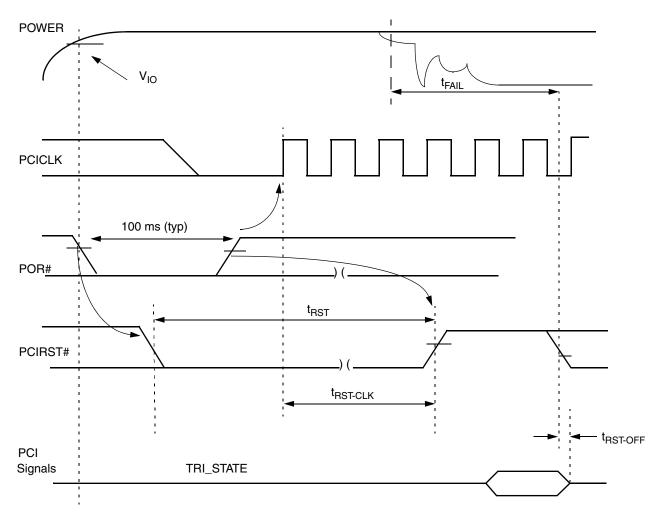

| Figure 9-18. | PCI Reset Timing                                                |     |

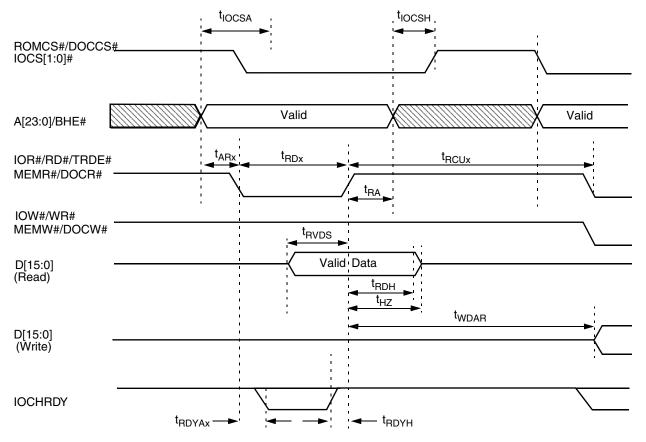

| Figure 9-19. | Sub-ISA Read Operation Timing Diagram                           |     |

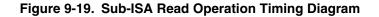

| Figure 9-20. | Sub-ISA Write Operation Timing Diagram                          |     |

| Figure 9-21. |                                                                 |     |

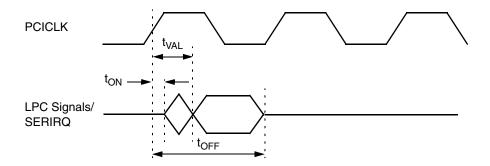

| Figure 9-22. | LPC Input Timing Diagram                                        |     |

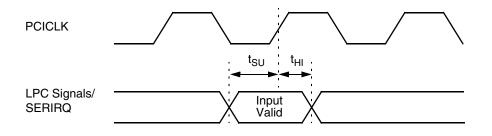

| Figure 9-23. | IDE Reset Timing Diagram                                        |     |

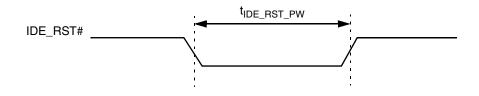

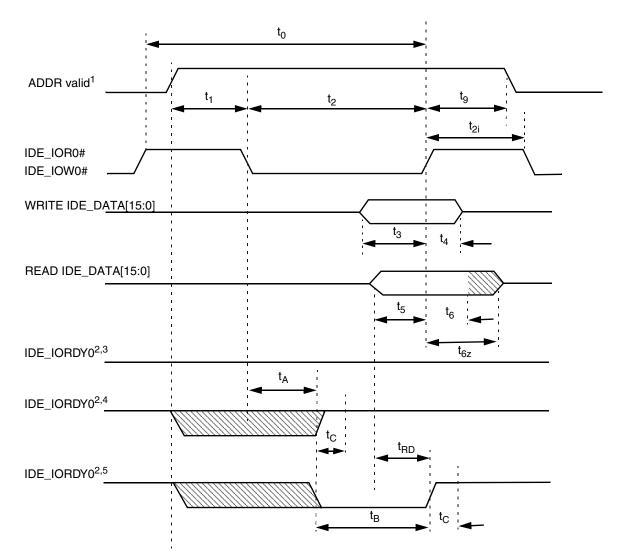

| Figure 9-24. | Register Transfer to/from Device Timing Diagram                 |     |

| -            | • • •                                                           |     |

| Figure 9-25. | PIO Data Transfer to/from Device Timing Diagram                 |     |

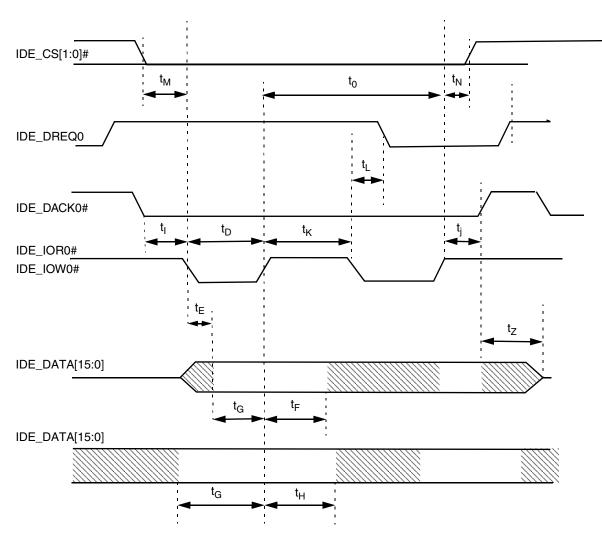

| Figure 9-26. | Multiword DMA Data Transfer Timing Diagram                      |     |

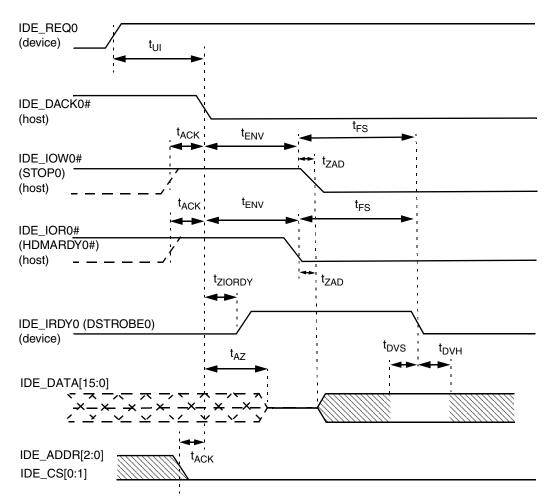

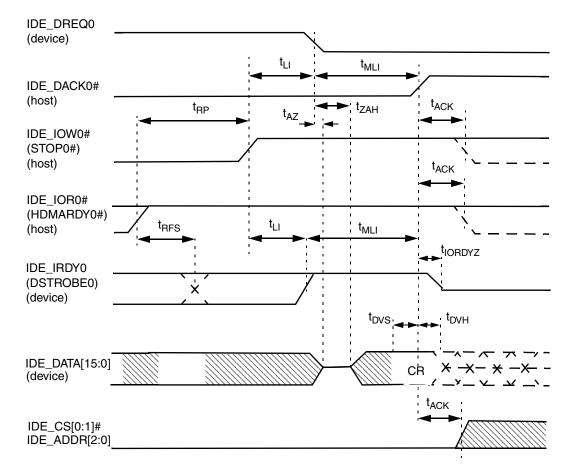

| Figure 9-27. | Initiating an UltraDMA Data in Burst Timing Diagram             |     |

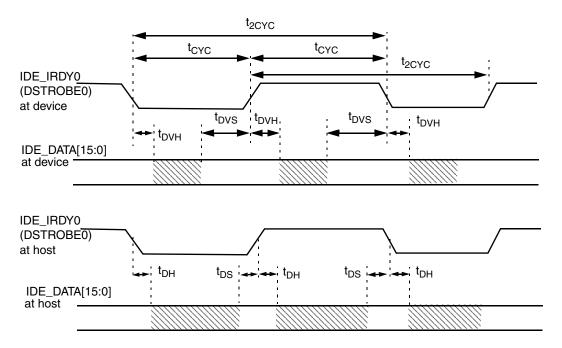

| Figure 9-28. | Sustained UltraDMA Data In Burst Timing Diagram                 |     |

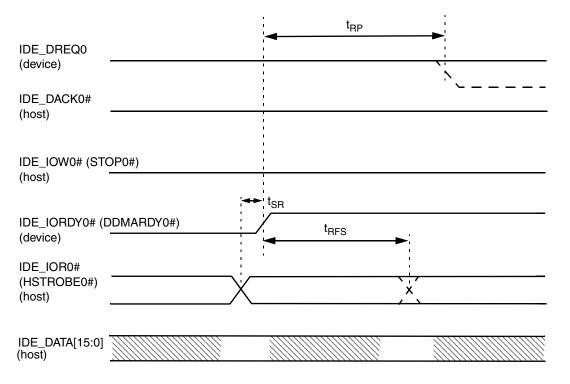

| Figure 9-29. | Host Pausing an UltraDMA Data In Burst Timing Diagram           |     |

| Figure 9-30. | Device Terminating an UltraDMA Data In Burst Timing Diagram     |     |

| Figure 9-31. | Host Terminating an UltraDMA Data In Burst Timing Diagram       |     |

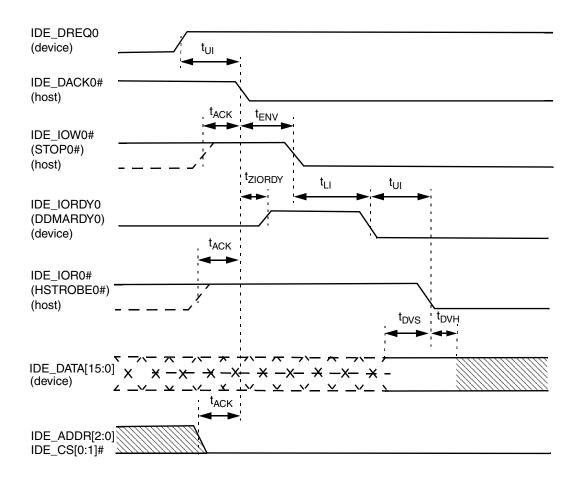

| Figure 9-32. | Initiating an UltraDMA Data Out Burst Timing Diagram            |     |

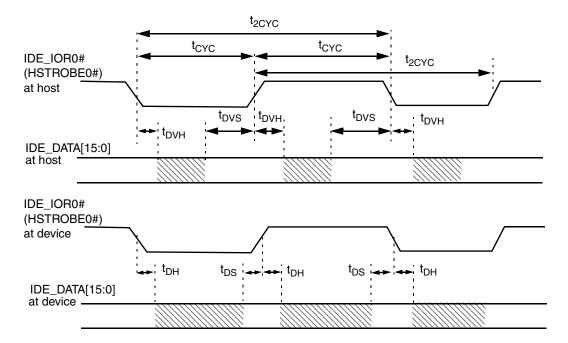

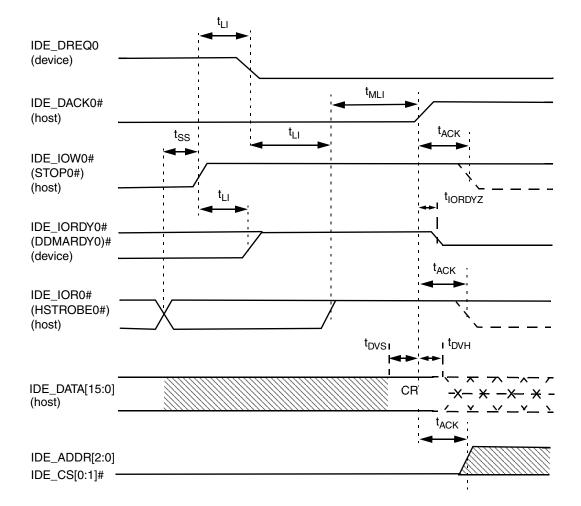

| Figure 9-33. | Sustained UltraDMA Data Out Burst Timing Diagram                | 419 |

| Figure 9-34. | Device Pausing an UltraDMA Data Out Burst Timing Diagram        | 420 |

| Figure 9-35. | Host Terminating an UltraDMA Data Out Burst Timing Diagram      | 421 |

| Figure 9-36. | Device Terminating an UltraDMA Data Out Burst Timing Diagram    | 422 |

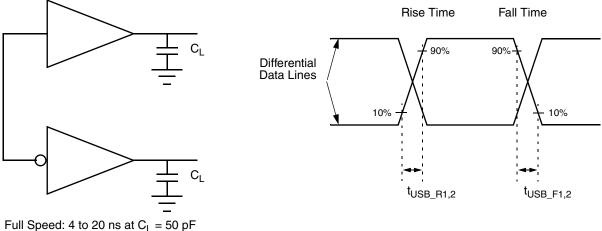

| Figure 9-37. | Data Signal Rise and Fall Timing Diagram                        | 425 |

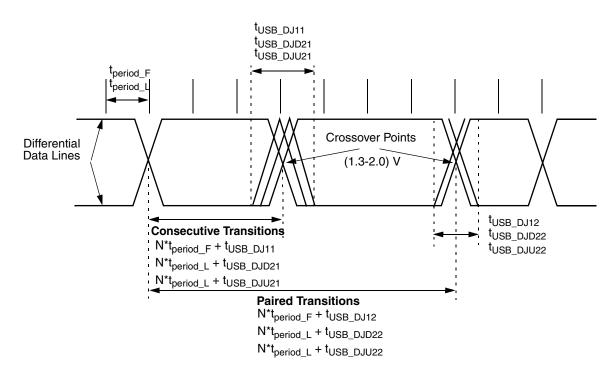

| Figure 9-38. | Source Differential Data Jitter Timing Diagram                  |     |

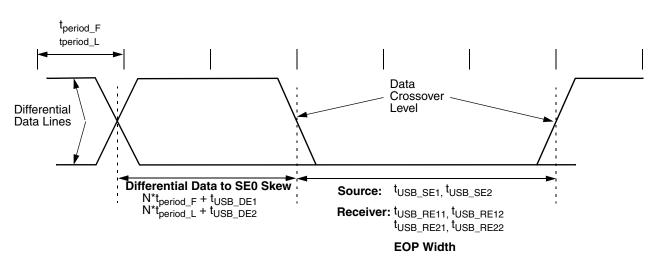

| Figure 9-39. | EOP Width Timing Diagram                                        |     |

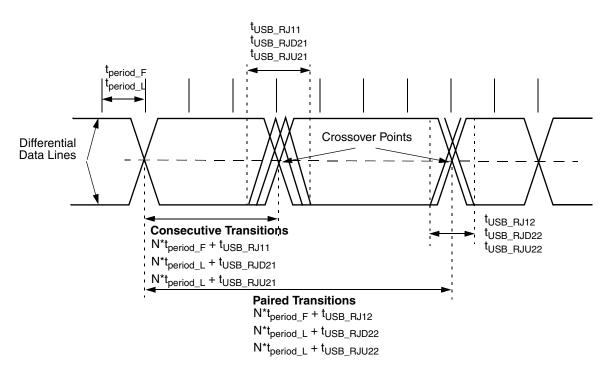

| Figure 9-40. | Receiver Jitter Tolerance Timing Diagram                        |     |

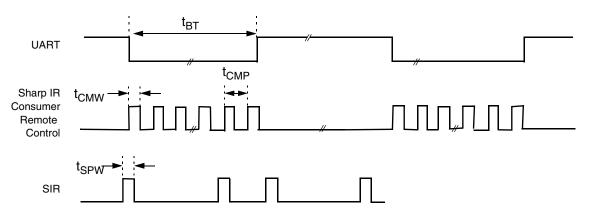

| Figure 9-41. | UART, Sharp-IR, SIR, and Consumer Remote Control Timing Diagram |     |

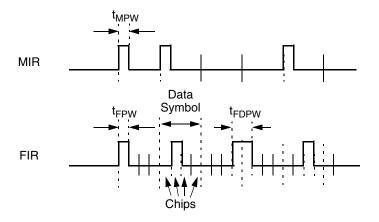

| Figure 9-42. | Fast IR (MIR and FIR) Timing Diagram                            |     |

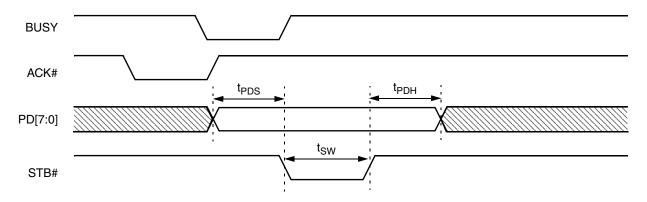

| Figure 9-43. | Standard Parallel Port Typical Data Exchange Timing Diagram     |     |

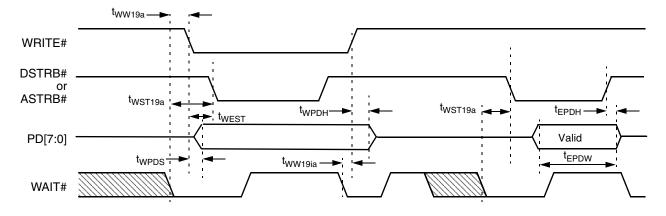

| Figure 9-44. | Enhanced Parallel Port Timing Diagram                           |     |

|              |                                                                 |     |

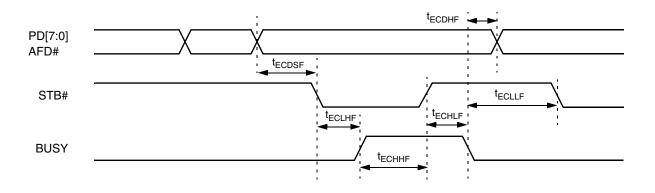

| ECP Forward Mode Timing Diagram           | 431                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

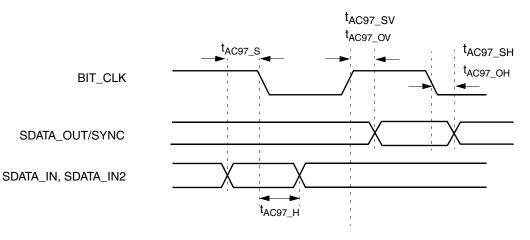

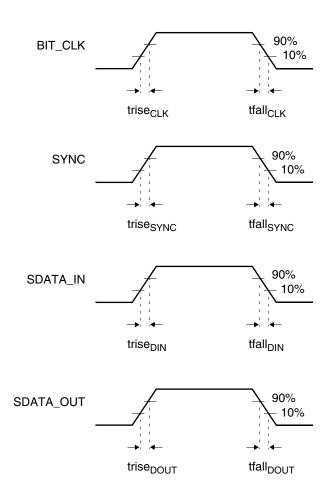

| AC97 Sync Timing Diagram                  | 433                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

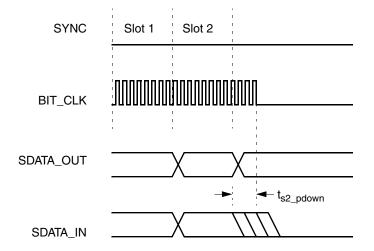

| AC97 Low Power Mode Timing Diagram        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

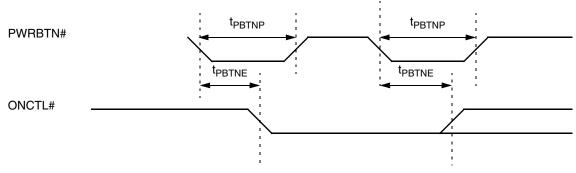

| PWRBTN# Trigger and ONCTL# Timing Diagram | 438                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

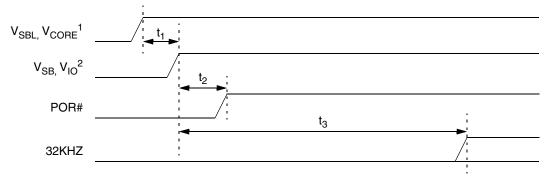

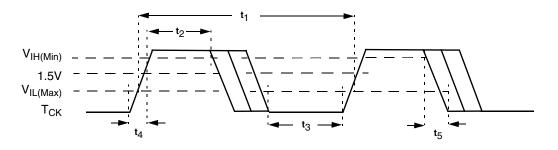

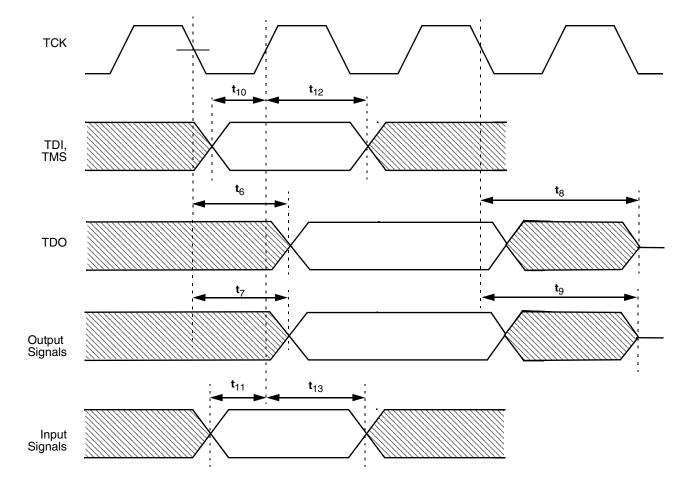

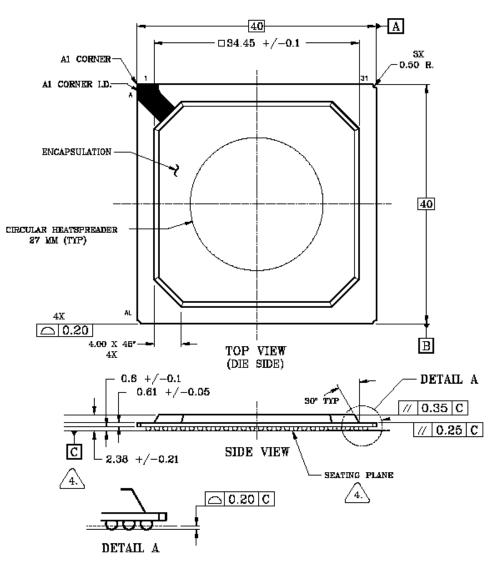

|                                           | ECP Forward Mode Timing Diagram<br>ECP Reverse Mode Timing Diagram<br>AC97 Reset Timing Diagram<br>AC97 Sync Timing Diagram<br>AC97 Clocks Diagram<br>AC97 Data TIming Diagram<br>AC97 Data TIming Diagram<br>AC97 Low Power Mode Timing Diagram<br>PWRBTN# Trigger and ONCTL# Timing Diagram<br>GPWIO and ONCTL# Timing Diagram<br>Power-Up Sequencing With PWRBTN# Timing Diagram<br>Power-Up Sequencing Without PWRBTN# Timing Diagram<br>TCK Measurement Points and Timing Diagram<br>JTAG Test Timing Diagram<br>Heatsink Example<br>BGU481 Package - Top View<br>BGU481 Package - Bottom View |

# List of Tables

| Table 2-1.  | SC2200 Memory Controller Register Summary                     |      |

|-------------|---------------------------------------------------------------|------|

| Table 2-2.  | SC2200 Memory Controller Registers                            |      |

| Table 3-1.  | Signal Definitions Legend                                     |      |

| Table 3-2.  | BGU481 Ball Assignment - Sorted by Ball Number                |      |

| Table 3-3.  | BGU481 Ball Assignment - Sorted Alphabetically by Signal Name |      |

| Table 3-4.  | Strap Options                                                 |      |

| Table 3-5.  | Two-Signal/Group Multiplexing                                 |      |

| Table 3-6.  | Three-Signal/Group Multiplexing                               |      |

| Table 3-7.  | Four-Signal/Group Multiplexing                                |      |

| Table 4-1.  | General Configuration Block Register Summary                  |      |

| Table 4-2.  | Multiplexing, Interrupt Selection, and Base Address Registers |      |

| Table 4-3.  | WATCHDOG Registers                                            |      |

| Table 4-4.  | High-Resolution Timer Registers                               | . 86 |

| Table 4-5.  | Crystal Oscillator Circuit Components                         | . 88 |

| Table 4-6.  | Core Clock Frequency                                          | . 89 |

| Table 4-7.  | Strapped Core Clock Frequency                                 | . 89 |

| Table 4-8.  | PLL3 Clock Frequency                                          | . 90 |

| Table 4-9.  | Clock Generator Configuration                                 | . 92 |

| Table 5-1.  | SIO Configuration Options                                     | . 98 |

| Table 5-2.  | LDN Assignments                                               | . 98 |

| Table 5-3.  | Standard Configuration Registers                              | 101  |

| Table 5-4.  | SIO Control and Configuration Register Map                    | 103  |

| Table 5-5.  | SIO Control and Configuration Registers                       |      |

| Table 5-6.  | Relevant RTC Configuration Registers                          | 104  |

| Table 5-7.  | RTC Configuration Registers                                   |      |

| Table 5-8.  | Relevant SWC Registers                                        |      |

| Table 5-9.  | Relevant IRCP/SP3 Registers                                   |      |

| Table 5-10. | IRCP/SP3 Configuration Register                               |      |

| Table 5-11. | Relevant Serial Ports 1 and 2 Registers                       |      |

| Table 5-12. | Serial Ports 1 and 2 Configuration Register                   |      |

| Table 5-13. | Relevant ACB1 and ACB2 Registers                              |      |

| Table 5-14. | ACB1 and ACB2 Configuration Register                          |      |

| Table 5-15. | Relevant Parallel Port Registers                              |      |

| Table 5-16. | Parallel Port Configuration Register                          |      |

| Table 5-17. | Crystal Oscillator Circuit Components                         |      |

| Table 5-18. | System Power States                                           |      |

| Table 5-19. | RTC Register Map                                              |      |

| Table 5-20. | RTC Registers                                                 |      |

| Table 5-21. | Divider Chain Control / Test Selection                        |      |

| Table 5-22. | Periodic Interrupt Rate Encoding                              |      |

| Table 5-23. | BCD and Binary Formats                                        |      |

| Table 5-24. | Standard RAM Map                                              |      |

| Table 5-25. | Extended RAM Map                                              |      |

| Table 5-26. | Time Range Limits for CEIR Protocols                          |      |

| Table 5-27. | Banks 0 and 1 - Common Control and Status Register Map        |      |

|             |                                                               | /    |

| Table 5-28.  | Bank 1 - CEIR Wakeup Configuration and Control Register Map                    |     |

|--------------|--------------------------------------------------------------------------------|-----|

| Table 5-29.  | Banks 0 and 1 - Common Control and Status Registers                            |     |

| Table 5-30.  | Bank 1 - CEIR Wakeup Configuration and Control Registers                       |     |

| Table 5-31.  | ACB Register Map                                                               |     |

| Table 5-32.  | ACB Registers                                                                  |     |

| Table 5-33.  | Parallel Port Register Map for First Level Offset                              |     |

| Table 5-34.  | Parallel Port Register Map for Second Level Offset                             |     |

| Table 5-35.  | Parallel Port Bit Map for First Level Offset                                   |     |

| Table 5-36.  | Parallel Port Bit Map for Second Level Offset                                  |     |

| Table 5-37.  | Bank 0 Register Map                                                            |     |

| Table 5-38.  | Bank Selection Encoding                                                        | 139 |

| Table 5-39.  | Bank 1 Register Map                                                            |     |

| Table 5-40.  | Bank 2 Register Map                                                            | 139 |

| Table 5-41.  | Bank 3 Register Map                                                            | 140 |

| Table 5-42.  | Bank 0 Bit Map                                                                 | 140 |

| Table 5-43.  | Bank 1 Bit Map                                                                 | 141 |

| Table 5-44.  | Bank 2 Bit Map                                                                 | 141 |

| Table 5-45.  | Bank 3 Bit Map                                                                 | 141 |

| Table 5-46.  | Bank 0 Register Map                                                            | 142 |

| Table 5-47.  | Bank Selection Encoding                                                        | 143 |

| Table 5-48.  | Bank 1 Register Map                                                            | 143 |

| Table 5-49.  | Bank 2 Register Map                                                            |     |

| Table 5-50.  | Bank 3 Register Map                                                            |     |

| Table 5-51.  | Bank 4 Register Map                                                            |     |

| Table 5-52.  | Bank 5 Register Map                                                            |     |

| Table 5-53.  | Bank 6 Register Map                                                            |     |

| Table 5-54.  | Bank 7 Register Map                                                            |     |

| Table 5-55.  | Bank 0 Bit Map                                                                 |     |

| Table 5-56.  | Bank 1 Bit Map                                                                 |     |

| Table 5-57.  | Bank 2 Bit Map                                                                 |     |

| Table 5-58.  | Bank 3 Bit Map                                                                 |     |

| Table 5-59.  | Bank 4 Bit Map                                                                 |     |

| Table 5-60.  | Bank 5 Bit Map                                                                 |     |

| Table 5-61.  | Bank 6 Bit Map                                                                 |     |

| Table 5-62.  | Bank 7 Bit Map                                                                 |     |

| Table 6-1.   | Physical Region Descriptor Format                                              |     |

| Table 6-2.   | UltraDMA/33 Signal Definitions                                                 |     |

| Table 6-3.   | Cycle Multiplexed PCI / Sub-ISA Balls                                          |     |

| Table 6-4.   | PIC Interrupt Mapping                                                          |     |

| Table 6-5.   | Wakeup Events Capability                                                       |     |

| Table 6-6.   | Power Planes Control Signals vs. Sleep States                                  |     |

| Table 6-7.   | Power Planes vs. Sleep/Global States                                           |     |

| Table 6-8.   | Power Management Events                                                        |     |

| Table 6-9.   | Device Power Management Programming Summary                                    |     |

| Table 6-10.  | Bus Masters That Drive Specific Slots of the AC97 Interface                    |     |

| Table 6-11.  | Physical Region Descriptor Format                                              |     |

| Table 6-12.  | Cycle Types                                                                    |     |

| Table 6-13.  | PCI Configuration Address Register (0CF8h)                                     |     |

| Table 6-14.  | F0: PCI Header/Bridge Configuration Registers for GPIO and LPC Support Summary |     |

| Table 6-15.  | F0BAR0: GPIO Support Registers Summary                                         |     |

| Table 6-16.  | F0BAR1: LPC Support Registers Summary                                          |     |

| Table 6-17.  | F1: PCI Header Registers for SMI Status and ACPI Support Summary               |     |

| Table 6-18.  | F1BAR0: SMI Status Registers Summary                                           |     |

| Table 6-19.  | F1BAR1: ACPI Support Registers Summary                                         |     |

| Table 6-20.  | F2: PCI Header Registers for IDE Controller Support Summary                    |     |

| 1 abie 0-20. | I Z.I OTHEAUEL REGISTERS TO THE OUTLIONEL SUPPORT SUPPORT STATE                | 100 |

| Table 6-21. | F2BAR4: IDE Controller Support Registers Summary                           | . 191 |

|-------------|----------------------------------------------------------------------------|-------|

| Table 6-22. | F3: PCI Header Registers for Audio Support Summary                         | . 191 |

| Table 6-23. | F3BAR0: Audio Support Registers Summary                                    |       |

| Table 6-24. | F5: PCI Header Registers for X-Bus Expansion Support Summary               |       |

| Table 6-25. | F5BAR0: I/O Control Support Registers Summary                              |       |

| Table 6-26. | PCIUSB: USB PCI Configuration Register Summary                             | . 194 |

| Table 6-27. | USB_BAR: USB Controller Registers Summary                                  | . 195 |

| Table 6-28. | ISA Legacy I/O Register Summary                                            | . 196 |

| Table 6-29. | F0: PCI Header/Bridge Configuration Registers for GPIO and LPC Support     | . 198 |

| Table 6-30. | F0BAR0+I/O Offset: GPIO Configuration Registers                            |       |

| Table 6-31. | F0BAR1+I/O Offset: LPC Interface Configuration Registers                   | . 237 |

| Table 6-32. | F1: PCI Header Registers for SMI Status and ACPI Support                   | . 245 |

| Table 6-33. | F1BAR0+I/O Offset: SMI Status Registers                                    |       |

| Table 6-34. | F1BAR1+I/O Offset: ACPI Support Registers                                  | . 255 |

| Table 6-35. | F2: PCI Header/Channels 0 and 1 Registers for IDE Controller Configuration | . 266 |

| Table 6-36. | F2BAR4+I/O Offset: IDE Controller Configuration Registers                  | . 270 |

| Table 6-37. | F3: PCI Header Registers for Audio Configuration                           | . 272 |

| Table 6-38. | F3BAR0+Memory Offset: Audio Configuration Registers                        | . 273 |

| Table 6-39. | F5: PCI Header Registers for X-Bus Expansion                               | . 287 |

| Table 6-40. | F5BAR0+I/O Offset: X-Bus Expansion Registers                               | . 290 |

| Table 6-41. | PCIUSB: USB PCI Configuration Registers                                    | . 292 |

| Table 6-42. | USB_BAR+Memory Offset: USB Controller Registers                            | . 295 |

| Table 6-43. | DMA Channel Control Registers                                              | . 305 |

| Table 6-44. | DMA Page Registers                                                         | . 310 |

| Table 6-45. | Programmable Interval Timer Registers                                      |       |

| Table 6-46. | Programmable Interrupt Controller Registers                                |       |

| Table 6-47. | Keyboard Controller Registers                                              |       |

| Table 6-48. | Real-Time Clock Registers                                                  | . 317 |

| Table 6-49. | Miscellaneous Registers                                                    |       |

| Table 7-1.  | Valid Mixing/Blending Configurations                                       |       |

| Table 7-2.  | Truth Table for Alpha Blending                                             |       |

| Table 7-3.  | F4: PCI Header Registers for Video Processor Support Summary               |       |

| Table 7-4.  | F4BAR0: Video Processor Configuration Registers Summary                    |       |

| Table 7-5.  | F4BAR2: VIP Support Registers Summary                                      |       |

| Table 7-6.  | F4: PCI Header Registers for Video Processor Support Registers             |       |

| Table 7-7.  | F4BAR0+Memory Offset: Video Processor Configuration Registers              |       |

| Table 7-8.  | F4BAR2+Memory Offset: VIP Configuration Registers                          |       |

| Table 8-1.  | JTAG Mode Instruction Support                                              |       |

| Table 8-2.  | Test Modes                                                                 |       |

| Table 8-3.  | Observe Clocks Mode                                                        | . 366 |

| Table 8-4.  | Bypass Clocks Mode                                                         | . 366 |

| Table 8-5.  | Vodka_C Scan Clocks                                                        | . 367 |

| Table 8-6.  | Vodka Scan Chains                                                          | . 367 |

| Table 8-7.  | BhargavaB Scan Clocks                                                      | . 367 |

| Table 8-8.  | BhargavaB Scan Chains                                                      | . 367 |

| Table 8-9.  | Vodka Internal Test Modes                                                  |       |

| Table 8-10. | BhargavaB Internal Test Modes                                              | . 368 |

| Table 9-1.  | Electro Static Discharge (ESD)                                             | . 369 |

| Table 9-2.  | Absolute Maximum Ratings                                                   |       |

| Table 9-3.  | Operating Conditions                                                       |       |

| Table 9-4.  | Power Planes of External Interface Signals                                 |       |

| Table 9-5.  | System Conditions Used to Measure SC2200 Current During the On State       |       |

| Table 9-6.  | DC Characteristics for On State                                            |       |

| Table 9-7.  | DC Characteristics for Active Idle, Sleep, and Off States                  |       |

| Table 9-8.  | Ball Capacitance and Inductance                                            |       |

| Table 9-9.  | Balls with PU/PD Resistors                                         | . 375 |

|-------------|--------------------------------------------------------------------|-------|

| Table 9-10. | PLL4 (48 MHz)                                                      |       |

| Table 9-11. | PLL3                                                               |       |

| Table 9-12. | PLL6 (57.273 MHz)                                                  |       |

| Table 9-13. | PLL2 Characteristics                                               |       |

| Table 9-14. | PLL5 (66.67 MHz)                                                   |       |

| Table 9-15. | Buffer Types                                                       |       |

| Table 9-16. | Default Levels for Measurement of Switching Parameters             |       |

| Table 9-17. | Memory Controller Timing Parameters                                |       |

| Table 9-18. | Video Input Port Timing Parameters                                 |       |

| Table 9-19. | TFT Timing Parameters                                              |       |

| Table 9-20. | CRT VESA Compatible DAC (RED, GREEN, and BLUE Outputs)             |       |

| Table 9-21. | ACCESS.bus Input Timing Parameters                                 |       |

| Table 9-22. | ACCESS.bus Output Timing Parameters                                |       |

| Table 9-23. | PCI AC Specifications                                              |       |

| Table 9-24. | PCI Clock Parameters                                               | . 396 |

| Table 9-25. | PCI Timing Parameters                                              |       |

| Table 9-26. | Measurement Condition Parameters                                   | . 398 |

| Table 9-27. | Sub-ISA Timing Parameters                                          |       |

| Table 9-28. | LPC and SERIRQ Timing Parameters                                   | . 404 |

| Table 9-29. | IDE General Timing Parameters                                      | . 405 |

| Table 9-30. | IDE Register Transfer to/from Device Timing Parameters             | . 406 |

| Table 9-31. | IDE PIO Data Transfer to/from Device Timing Parameters             | . 408 |

| Table 9-32. | IDE Multiword DMA Data Transfer Timing Parameters                  | .410  |

| Table 9-33. | IDE UltraDMA Data Burst Timing Parameters                          | .412  |

| Table 9-34. | USB Timing Parameters                                              |       |

| Table 9-35. | UART, Sharp-IR, SIR, and Consumer Remote Control Timing Parameters | . 427 |

| Table 9-36. | Fast IR Port Timing Parameters                                     |       |

| Table 9-37. | Standard Parallel Port Timing Parameters                           | . 429 |

| Table 9-39. | ECP Forward Mode Timing Parameters                                 |       |

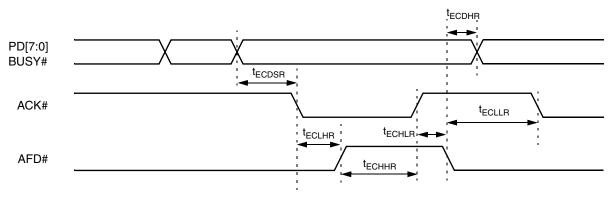

| Table 9-40. | ECP Reverse Mode Timing Parameters                                 | . 432 |

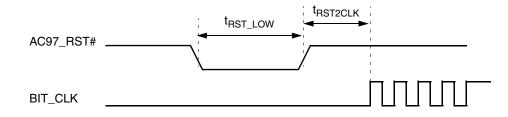

| Table 9-41. | AC Reset Timing Parameters                                         |       |

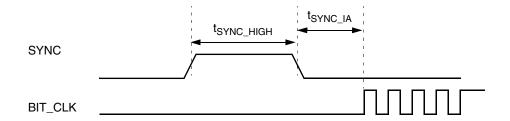

| Table 9-42. | AC97 Sync Timing Parameters                                        |       |

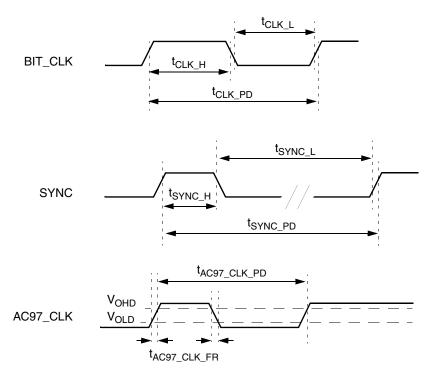

| Table 9-43. | AC97 Clocks Parameters                                             |       |

| Table 9-44. | AC97 I/O Timing Parameters                                         | . 435 |

| Table 9-45. | AC97 Signal Rise and Fall Timing Parameters                        | . 436 |

| Table 9-46. | AC97 Low Power Mode Timing Parameters                              |       |

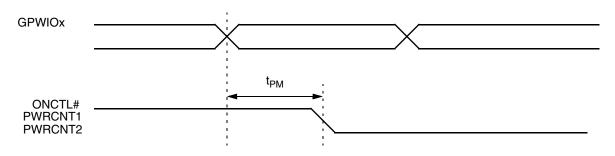

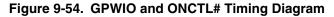

| Table 9-47. | PWRBTN# Timing Parameters                                          |       |

| Table 9-48. | Power Management Event (GPWIO) and ONCTL# Timing Parameters        |       |

| Table 9-49. | Power-Up Sequence Using the Power Button Timing Parameters         |       |

| Table 9-50. | Power-Up Sequence Not Using the Power Button Timing Parameters     |       |

| Table 9-51. | JTAG Timing Parameters                                             |       |

| Table 10-1. | q <sub>.IC</sub> (×C/W)                                            |       |

| Table 10-2. | Case-to-Ambient Thermal Resistance Example @ 85×C                  |       |

| Table A-1.  | Revision History                                                   |       |

| Table A-2.  | Edits to Current Revision                                          |       |

|             |                                                                    | 0     |

### 1.1 General Description

The AMD Geode<sup>™</sup> SC2200 processor is a member of the AMD Geode processor family of fully integrated x86 system chips. The SC2200 processor includes:

- The Geode GX1 processor module combines advanced CPU performance with MMX<sup>™</sup> support, fully accelerated 2D graphics, a 64-bit synchronous DRAM (SDRAM) interface, a PCI bus controller, and a display controller.

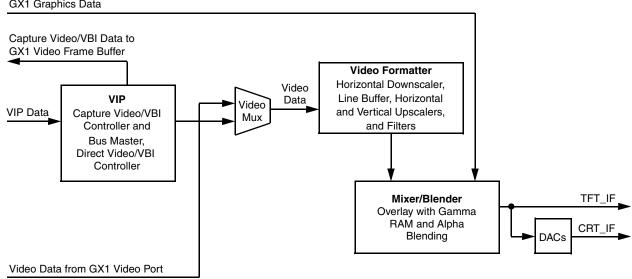

- A low-power CRT and TFT Video Processor module with a Video Input Port (VIP), and a hardware video accelerator for scaling, filtering, and color space conversion.

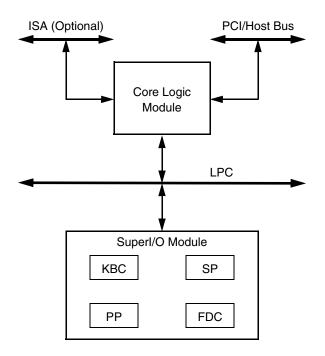

- The Core Logic module includes: PC/AT functionality, a USB interface, an IDE interface, a PCI bus interface, an LPC bus interface, Advanced Configuration Power Interface (ACPI) version 1.0 compliant power management, and an audio codec interface.

- The SuperI/O module has: three Serial Ports (UART1, UART2, and UART3 with fast infrared), a Parallel Port, two ACCESS.bus (ACB) interfaces, and a Real-Time Clock (RTC).

These features, combined with the device's low power consumption, enable a small form factor design making it ideal as the core for a thin client application.

Figure 1-1 shows the relationships between the modules.

Figure 1-1. Block Diagram

AMD Geode™ SC2200 Processor Data Book

### 1.2 Features

#### **General Features**

- 32-Bit x86 processor, up to 300 MHz, with MMX instruction set support

- Memory controller with 64-bit SDRAM interface

- 2D graphics accelerator

- CRT controller with hardware video accelerator

- CCIR-656 video input port with direct video for full screen display

- PC/AT functionality

- PCI bus controller

- IDE interface, two channels

- USB, three ports, OHCI (OpenHost Controller Interface) version 1.0 compliant

- Audio, AC97/AMC97 version 2.0 compliant

- Virtual System Architecture<sup>™</sup> (VSA) technology support

- Power management, ACPI (Advanced Configuration Power Interface) version 1.0 compliant

- Package:

BGU481 (481-Terminal Ball Grid Array Cavity Up)

#### **GX1 Processor Module**

- CPU Core:

- 32-Bit x86, 300 MHz, with MMX compatible instruction set support

- 16 KB unified L1 cache

- Integrated FPU (Floating Point Unit)

- Re-entrant SMM (System Management Mode) enhanced for VSA

- 2D Graphics Accelerator:

- Accelerates BitBLTs, line draw and text

- Supports all 256 raster operations

- Supports transparent BLTs

- Runs at core clock frequency

- Memory Controller:

- 64-Bit SDRAM interface

- 66 MHz to 100 MHz frequency range

- Direct interface with CPU/cache, display controller and 2D graphic accelerator

- Supports clock suspend and power-down/ self-refresh

- Up to two banks of SDRAM (8 devices total) or one SODIMM

- Display Controller:

- Hardware graphics frame buffer compress/ decompress

- Hardware cursor, 32x32 pixels

#### **Video Processor Module**

- Video Accelerator:

- Flexible video scaling support of up to 8x (horizontally and vertically)

- Bilinear interpolation filters (with two taps, and eight phases) to smooth output video

- Video/Graphics Mixer:

- 8-bit value alpha blending

- Three blending windows with constant alpha value

- Color key

- Video Input Port (VIP):

- Video capture or display

- CCIR-656 and VESA Video Interface Port v1.1 compliant

- Lock display timing to video input timing (GenLock)

- Able to transfer video data into main memory

- Direct video transfer for full screen display

- Separate memory location for VBI

- CRT Interface:

- Uses three 8-bit DACs

- Supports up to 135 MHz

- 1280x1024 non-interlaced CRT @ 8 bpp, up to 75 Hz

- 1024x768 non-interlaced CRT @ 16 bpp, up to 85 Hz

- TFT Interface:

- Direct connection to TFT panels

- 800x600 non-interlaced TFT @ 16 bpp graphics, up to 85 Hz

- 1024x768 non-interlaced TFT @ 16 bpp graphics, up to 75 Hz

- TFT on IDE: FPCLK max is 40 MHz

- TFT on Parallel Port: FPCLK max is 80 MHz

#### **Core Logic Module**

- Audio Codec Interface:

- AC97/AMC97 (Rev. 2.0) codec interface

- Six DMA channels

- PC/AT Functionality:

- Programmable Interrupt Controller (PIC), 8259A-equivalent

- Programmable Interval Timer (PIT), 8254-equivalent

- DMA Controller (DMAC), 8237-equivalent

- Power Management:

- ACPI v1.0 compliant

- Sx state control of three power planes

- Cx/Sx state control of clocks and PLLs

- Thermal event input

- Wakeup event support:

- Three general-purpose events

- AC97 codec event

- UART2 RI# signal

- Infrared (IR) event

#### Overview

- General Purpose I/Os (GPIOs):

27 multiplexed GPIO signals

- Low Pin Count (LPC) Bus Interface:

Specification v1.0 compatible

- PCI Bus Interface:

- PCI v2.1 compliant with wakeup capability

- 32-Bit data path, up to 33 MHz

- Glueless interface for an external PCI device

- Fixed priority

- 3.3V signal support only

#### Sub-ISA Bus Interface:

- Up to 16 MB addressing

- Supports a chip select for ROM or Flash EPROM boot device

- Supports either:

- M-Systems DiskOnChip DOC2000 Flash file system

- NAND EEPROM

- Supports up to two chip selects for external I/O devices

- 8-Bit (optional 16-bit) data bus width

- Shares balls with PCI signals

- Is not a subtractive agent

- IDE Interface:

- Two IDE channels for up to four external IDE devices

- Supports ATA-33 synchronous DMA mode transfers, up to 33 MB/s

- Universal Serial Bus (USB):

- USB OpenHCI v1.0 compliant

- Three ports

#### SuperI/O Module

- Real-Time Clock (RTC):

- DS1287, MC146818 and PC87911 compatible

- Multi-century calendar

- ACCESS.bus (ACB) Interface:

- Two ACB interface ports

- Parallel Port:

- EPP 1.9 compliant

- IEEE 1284 ECP compliant, including level 2

- Serial Port (UART):

- UART1, 16550A compatible (SIN, SOUT, BOUT pins), used for SmartCard interface

- UART2, 16550A compatible

- Enhanced UART with fast Infrared (IR)

#### **Other Features**

- High-Resolution Timer:

- 32-Bit counter with 1  $\mu s$  count interval

- WATCHDOG Timer:

Interfaces to INTR, SMI, Reset

- Clocks:

- Input (external crystals):

- 32.768 KHz (internal clock oscillator)

- 27 MHz (internal clock oscillator)

- Output:

- AC97 clock (24.576 MHz)

- Memory controller clock (66 MHz to 100 MHz)

32580B

- PCI clock (33 MHz)

- JTAG Testability:

- Bypass, Extest, Sample/Preload, IDcode, Clamp, HiZ

- Voltages:

- Internal logic:

- 233 MHz @ 1.8V

- 266 MHz @ 1.8V

300 MHz @ 2.1V

- Standby logic:

- 233 MHz @ 1.8V

- 266 MHz @ 1.8V

- 300 MHz @ 2.1V

- I/O: 3.3V

- Standby I/O: 3.3V

- Battery (if used): 3.0V

# Architecture Overview

As illustrated in Figure 1-1 on page 13, the SC2200 processor contains the following modules in one integrated device:

- GX1 Module:

- Combines advanced CPU performance with MMX support, fully accelerated 2D graphics, a 64-bit synchronous DRAM (SDRAM) interface and a PCI bus controller. Integrates GX1 silicon revision 8.1.1.

- Video Processor Module:

- A low-power CRT and TFT support module with a video input port, and a hardware video accelerator for scaling, filtering and color space conversion.

- Core Logic Module:

- Includes PC/AT functionality, an IDE interface, a Universal Serial Bus (USB) interface, ACPI 1.0 compliant power management, and an audio codec interface.

- SuperI/O Module:

- Includes two Serial Ports, an Infrared (IR) Port, a Parallel Port, two ACCESS.bus interfaces, and a Real-Time Clock (RTC).

### 2.1 GX1 Module

The GX1 processor (silicon revision 8.1.1) is the central module of the SC2200. For detailed information regarding the GX1 module, refer to the AMD Geode<sup>TM</sup> GX1 Processor Data Book and the AMD Geode<sup>TM</sup> GX1 Processor Silicon Revision 8.1.1 Specification Update document.

The device ID of the SC2200 processor is contained in the GX1 module. Software can detect the revision by reading the DIR0 and DIR1 Configuration registers (see Configuration registers in the AMD Geode<sup>TM</sup> GX1 Processor Data Book). The AMD Geode<sup>TM</sup> SC2200 Processor Specification Update document contains the specific values.

#### 2.1.1 Memory Controller

The GX1 module is connected to external SDRAM devices. For more information see Section 3.4.2 "Memory Interface Signals" on page 54, and the "Memory Controller" chapter in the AMD Geode<sup>TM</sup> GX1 Processor Data Book.

There are some differences in the memory controller of the SC2200 processor and the standalone GX1 processor's memory controller:

- There is drive strength/slew control in the SC2200 that is not in the GX1. The bits that control this function are in the MC\_MEM\_CNTRL1 and MC\_MEM\_CNTRL2 registers. In the GX1 processor, these bits are marked as reserved.

- 2) The SC2200 supports two banks of memory. The GX1 supports four banks of memory. In addition, the SC2200 supports a maximum of eight devices and the GX1 supports up to 32 devices. With this difference, the MC\_BANK\_CFG register is different.

Table 2-1 summarizes the 32-bit registers contained in the SC2200's memory controller. Table 2-2 gives detailed register/bit formats.

| GX_BASE+<br>Memory Offset | Width<br>(Bits) | Туре | Name/Function                                                     | Reset Value |

|---------------------------|-----------------|------|-------------------------------------------------------------------|-------------|

| 8400h-8403h               | 32              | R/W  | MC_MEM_CNTRL1. Memory Controller Control Register 1               | 248C0040h   |

| 8404h-8407h               | 32              | R/W  | MC_MEM_CNTRL2. Memory Controller Control Register 2               | 00000801h   |

| 8408h-840Bh               | 32              | R/W  | MC_BANK_CFG. Memory Controller Bank Configuration                 | 41104110h   |

| 840Ch-840Fh               | 32              | R/W  | MC_SYNC_TIM1. Memory Controller Synchronous Timing<br>Register 1  | 2A733225h   |

| 8414h-8417h               | 32              | R/W  | MC_GBASE_ADD. Memory Controller Graphics Base<br>Address Register | 00000000h   |

| 8418h-841Bh               | 32              | R/W  | MC_DR_ADD. Memory Controller Dirty RAM Address<br>Register        | 00000000h   |

| 841Ch-841Fh               | 32              | R/W  | MC_DR_ACC. Memory Controller Dirty RAM Access<br>Register         | 0000000xh   |

# Table 2-1. SC2200 Memory Controller Register Summary

# Table 2-2. SC2200 Memory Controller Registers

| Bit      | Description                                                                                                                                                                                                                   |                                                                    |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|

| GX_BASE+ | + 8400h-8403h MC_MEM_CNTRL1                                                                                                                                                                                                   | (R/W) Reset Value: 248C0040h                                       |  |  |  |  |

| 31:30    | MDCTL (MD[63:0] Drive Strength). 11 is strongest, 00 is weakest.                                                                                                                                                              |                                                                    |  |  |  |  |

| 29       | RSVD (Reserved) Write as 0.                                                                                                                                                                                                   |                                                                    |  |  |  |  |

| 28:27    | MABACTL (MA[12:0] and BA[1:0] Drive Strength). 11 is stron                                                                                                                                                                    | ngest, 00 is weakest.                                              |  |  |  |  |

| 26       | RSVD (Reserved). Write as 0.                                                                                                                                                                                                  |                                                                    |  |  |  |  |

| 25:24    | MEMCTL (RASA#, CASA#, WEA#, CS[1:0]#, CKEA, DQM[7:                                                                                                                                                                            | :0] Drive Strength). 11 is strongest, 00 is weakest.               |  |  |  |  |

| 23:22    | RSVD (Reserved). Write as 0.                                                                                                                                                                                                  |                                                                    |  |  |  |  |

| 21       | RSVD (Reserved). Must be written as 0. Wait state on the X-                                                                                                                                                                   | -Bus x_data during read cycles - for debug only.                   |  |  |  |  |

| 20:18    | SDCLKRATE (SDRAM Clock Ratio). Selects SDRAM clock                                                                                                                                                                            | ratio.                                                             |  |  |  |  |

|          | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                          |                                                                    |  |  |  |  |

|          | Ratio does not take effect until the SDCLKSTRT bit (bit 17 of this register) transitions from 0 to 1.                                                                                                                         |                                                                    |  |  |  |  |

| 17       | <ul> <li>SDCLKSTRT (Start SDCLK). Start operating SDCLK using the new ratio and shift value (selected in bits [20:18] of this register).</li> <li>0: Clear.</li> <li>1: Enable.</li> </ul>                                    |                                                                    |  |  |  |  |

|          | This bit must transition from zero (written to zero) to one (writt                                                                                                                                                            | ten to one) in order to start SDCLK or to change the shift value.  |  |  |  |  |

| 16:8     | <b>RFSHRATE (Refresh Interval).</b> This field determines the number of processor core clocks multiplied by 64 between refresh cycles to the DRAM. By default, the refresh interval is 00h. Refresh is turned off by default. |                                                                    |  |  |  |  |

| 7:6      | <b>RFSHSTAG (Refresh Staggering).</b> This field determines nur four banks during refresh cycles:                                                                                                                             | mber of clocks between the RFSH commands to each of the            |  |  |  |  |

|          | 00: 0 SDRAM clocks<br>01: 1 SDRAM clocks (Default)<br>10: 2 SDRAM clocks<br>11: 4 SDRAM clocks                                                                                                                                |                                                                    |  |  |  |  |

|          | Staggering is used to help reduce power spikes during refresh<br>this field must be written as 00.                                                                                                                            | n by refreshing one bank at a time. If only one bank is installed, |  |  |  |  |

| Bit     | Description                                                      |                                                                                                                                                    |                                             |

|---------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 5       | 2CLKADDR (Two Clock Address S                                    | Setup). Assert memory address for one extra c                                                                                                      | clock before CS# is asserted.               |

|         | 0: Disable.                                                      |                                                                                                                                                    |                                             |

|         | 1: Enable.                                                       |                                                                                                                                                    |                                             |

|         |                                                                  | address setup at high frequencies and/or high                                                                                                      |                                             |

| 4       |                                                                  | when set high, generates a refresh request. Th                                                                                                     |                                             |

| 3       | troller requests are arbitrated at the                           | When round robin is enabled, processor, graph<br>same priority level. When disabled, processor r<br>requests always have the highest arbitration p | equests are arbitrated at a higher priority |

|         | 0: Disable.<br>1: Enable round robin.                            |                                                                                                                                                    |                                             |

| 2       | SMM_MAP (SMM Region Mapping<br>BFFFF in SDRAM.                   | i). Maps the SMM memory region at GX_BASI                                                                                                          | E+400000 to physical address A0000 to       |

|         | 0: Disable.                                                      |                                                                                                                                                    |                                             |

|         | 1: Enable.                                                       |                                                                                                                                                    |                                             |

| 1       | RSVD (Reserved). Write as 0.                                     |                                                                                                                                                    |                                             |

| 0       | LTMODE in MC_SYNC_TIM1.                                          | /hen this bit is set, the memory controller will p                                                                                                 |                                             |

|         | This bit must transition from zero (w                            | ritten to zero) to one (written to one) in order to                                                                                                | program the SDRAM devices.                  |

| GX_BASE | E+8404h-8407h                                                    | MC_MEM_CNTRL2 (R/W)                                                                                                                                | Reset Value: 00000801h                      |

| 31:14   | RSVD (Reserved). Write as 0.                                     |                                                                                                                                                    |                                             |

| 13:12   | SDCLKCTL (SDCLK High Drive/SI<br>11 is strongest, 00 is weakest. | ew Control). Controls the high drive and slew                                                                                                      | rate of SDCLK[3:0] and SDCLK_OUT.           |

| 11      | RSVD (Reserved). Write as 0.                                     |                                                                                                                                                    |                                             |

| 10      | SDCLKOMSK# (Enable SDCLK_O                                       | UT). Turns on the output.                                                                                                                          |                                             |

|         | 0: Enable.<br>1: Disable.                                        |                                                                                                                                                    |                                             |

| 9       | SDCLK3MSK# (Enable SDCLK3).                                      | Turns on the output.                                                                                                                               |                                             |

|         | 0: Enable.<br>1: Disable.                                        |                                                                                                                                                    |                                             |

| 8       | SDCLK2MSK# (Enable SDCLK2).                                      | Turns on the output.                                                                                                                               |                                             |

|         | 0: Enable.<br>1: Disable.                                        |                                                                                                                                                    |                                             |

| 7       | SDCLK1MSK# (Enable SDCLK1).                                      | Turns on the output.                                                                                                                               |                                             |

|         | 0: Enable.                                                       |                                                                                                                                                    |                                             |

|         | 1: Disable.                                                      |                                                                                                                                                    |                                             |

| 6       | SDCLK0MSK# (Enable SDCLK0).                                      | Turns on the output.                                                                                                                               |                                             |

|         | 0: Enable.<br>1: Disable.                                        |                                                                                                                                                    |                                             |

| 5:3     | SHFTSDCLK (Shift SDCLK). This f                                  | unction allows shifting SDCLK to meet SDRAM the SDCLKSTRT bit (bit 17 of MC_MEM_CN                                                                 | • •                                         |

|         | 000: No shift                                                    | 100: Shift 2 core clocks                                                                                                                           |                                             |

|         | 001: Shift 0.5 core clock                                        | 101: Shift 2.5 core clocks                                                                                                                         |                                             |

|         | 010: Shift 1 core clock                                          | 110: Shift 3 core clocks                                                                                                                           |                                             |

| -       | 011: Shift 1.5 core clock                                        | 111: Reserved                                                                                                                                      |                                             |

| 2       | RSVD (Reserved). Write as 0.                                     |                                                                                                                                                    |                                             |

| 1       | · · · · · · · · · · · · · · · · · · ·                            | ead data is latched one or two core clock after                                                                                                    | the rising edge of SDCLK.                   |

|         | 0: 1 Core clock.<br>1: 2 Core clocks.                            |                                                                                                                                                    |                                             |

| 0       | FSTRDMSK (Fast Read Mask). Do                                    | not allow core reads to bypass the request FIF                                                                                                     | =0.                                         |

|         | 0: Disable.<br>1: Enable.                                        |                                                                                                                                                    |                                             |

# Table 2-2. SC2200 Memory Controller Registers (Continued)

# Table 2-2. SC2200 Memory Controller Registers (Continued)