# FSDH565 Fairchild Power Switch(FPS)

#### Features

- Single Chip 650V 0.5A SenseFET Power Switch

- Precision Fixed Operating Frequency (100kHz)

- Internal Start up Switch

- UVLO with Hysteresis (6.7V/8.7V)

- Over Load Protection

- Over Current Protection (0.3A)

- Internal Thermal Shutdown Function

- Secondary Side Regulation

- Auto-restart mode

- No load consumption <250mW at 265VAC input

### Applications

- Charger & Adaptor for Mobile Phone, PDA & MP3

- Auxiliary Power for PC, C-TV, Monitor

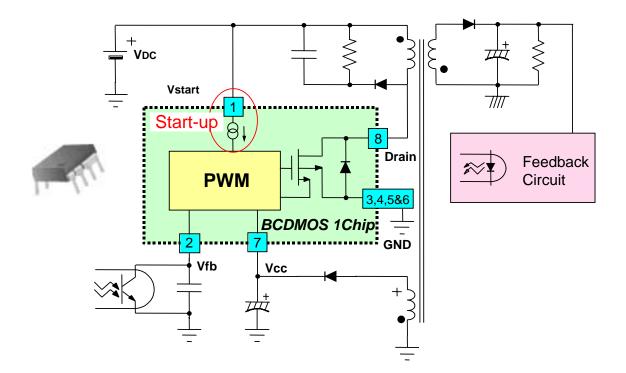

Internal Block Diagram

#### Description

The FSDH565 is specially designed for an off-line SMPS with minimal external components. The FSDH565 is a monolithic high voltage power switching regulator that combine the SenseFET(LDMOS) with voltage mode PWM control block. Included PWM controller features integrated fixed oscillator, under voltage lock out, leading edge blanking, optimized gate turn-on/turn-off driver, thermal shut down protection and temperature compensated precision current sources for loop compensation and fault protection circuitry. compared to discrete MOSFET and controller or RCC switching converter solution, a FSDH565 can reduce total component count, design size, weight and at the same time increase efficiency, productivity, and system reliability. It has a basic platform well suited for cost effective design in a flyback converter.

#### #1 : Vstr UVLO ≤ 6.7V #7 : Vcc UVLO ≥ 8.7V INIO 4 5V #8 : Drain VREE VREG(5.8V) INTERNAL BIAS SFET osc Q L.E.B #2 : Vfb Ş 4.5V #3.#4.#5.#6 GND TSD ÷4

#### Rev.1.0.2

©2001 Fairchild Semiconductor Corporation

### **Absolute Maximum Ratings**

(Ta=25°C unless otherwise specified)

| Parameter                          | Symbol  | Value       | Unit |

|------------------------------------|---------|-------------|------|

| Maximum Drain Voltage              | Vd,max  | 650         | V    |

| Continuous Drain Current (TC=25°C) | ID      | 0.3         | ADC  |

| Maximum Supply Voltage             | VCC,MAX | 21          | V    |

| Input Voltage Range                | VFB     | -0.3 to VSD | V    |

| Operating Ambient Temperature      | TA      | -25 to +85  | °C   |

| Storage Temperature Range          | TSTG    | -55 to +150 | °C   |

### **PIN Definitions**

| Pin Number | Pin Name | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1          | Vstr     | This pin connects directly to the rectified AC line voltage source. At start up the internal switch supplies internal bias and charges an external capacitor that connects from the Vcc pin to ground. once this reaches 8.7V, Vstr is isolated internally.                                                                                                                                                                                                                                   |  |  |

| 2          | Vfb      | This pin is the inverting input of the PWM comparator, and it operates normally between 0.5V and 2.5V. It has a 0.45mA current source connected internally and a capacitor and opto coupler connected externally. A feedback voltage of 3.5V to 4.5V triggers overload protection (OLP). There is a time delay due to the 5uA current source, which prevents false triggering under transient conditions but still allows the protection mechanism to operate under true overload conditions. |  |  |

| 3, 4, 5, 6 | GND      | These pins are the control ground and the SenseFET Source.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 7          | Vcc      | This is the positive supply voltage input. During start up, power is supplied to this input from Pin 1. When Vcc reaches the UVLO upper threshold (8.7V), the start up Internal Switch (Vstr) turns off and power is supplied from auxiliary transformer winding.                                                                                                                                                                                                                             |  |  |

| 8          | Drain    | This pin is designed to directly drive the converter transformer and is capable of switching a maximum of 650V and 1A.                                                                                                                                                                                                                                                                                                                                                                        |  |  |

#### **Electrical Characteristics**

(Ta=25°C unless otherwise specified)

| Parameter                                        | Symbol  | Condition                                      | Min. | Тур. | Max. | Unit |

|--------------------------------------------------|---------|------------------------------------------------|------|------|------|------|

| SENSEFET SECTION                                 |         |                                                |      |      |      |      |

| Drain-Source Breakdown Voltage                   | BVDSS   | $V_{GS} = 0V, I_{D} = 100 \mu A$               | 650  | -    | -    | V    |

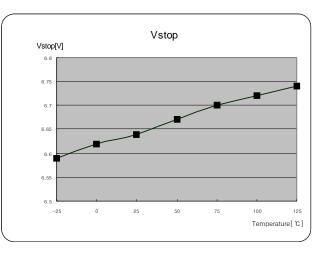

| Zero gate voltage drain current                  | IDSS    | V <sub>DS</sub> = 520V                         | -    | -    | 100  | μΑ   |

| Static drain-source on Resistance                | RDS(ON) | ID = 50mA Tj = 25°C                            | -    | 36   | 39   | Ω    |

|                                                  |         | I <sub>D</sub> = 50mA Tj = 100°C               | -    | 51   | 59   | Ω    |

| Rise Time                                        | TR      | V <sub>DS</sub> = 325V, I <sub>D</sub> = 300mA | -    | 100  | -    | nS   |

| Fall Time                                        | TF      | V <sub>DS</sub> = 325V, I <sub>D</sub> = 50mA  | -    | 50   | -    | nS   |

| START UP SECTION                                 |         |                                                |      |      |      |      |

| VSTR Supply Voltage                              | Vst     | -                                              | 17   | -    | -    | V    |

| UVLO SECTION                                     |         |                                                |      |      |      |      |

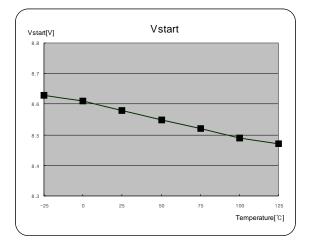

| Start Threshold Voltage                          | Vstart  | -                                              | 8.0  | 8.7  | 9.4  | V    |

| Stop Threshold Voltage                           | Vstop   | After turn on                                  | 6.0  | 6.7  | 7.4  | V    |

| OSCILLATOR SECTION                               |         |                                                |      |      |      |      |

| Initial accuracy                                 | Fosc    | Tj = 25°C                                      | 90   | 100  | 110  | kHz  |

| Maximum Duty Cycle                               | DMAX    | Vfb = 3V                                       | 64   | 67   | 70   | %    |

| Minimum Duty Cycle                               | DMIN    | Vfb = 0V                                       | -    | 0    | 0    | %    |

| FEEDBACK SECTION                                 |         |                                                |      |      |      |      |

| Feedback Source Current                          | IFB     | Vfb = 0V                                       | 0.40 | 0.45 | 0.50 | mA   |

| Shutdown feedback Voltage                        | VSD     | -                                              | 4.0  | 4.5  | 5.0  | V    |

| CURRENT LIMIT(SELF-PROTECTION                    | SECTION |                                                |      |      |      |      |

| Peak Current Limit                               | IOVER   | peak inductor current                          | 0.25 | 0.3  | 0.35 | А    |

| PROTECTION SECTION                               |         |                                                |      |      |      |      |

| Thermal Shutdown Temperature (Tj) <sup>(1)</sup> | TSD     | -                                              | 125  | 145  | -    | °C   |

| TOTAL DEVICE SECTION                             |         |                                                |      | •    |      |      |

| Operating Supply Current                         | IOP     | Vcc = 9.5V (Max)                               | -    | -    | 3.5  | mA   |

Note:

1. These parameters, although guaranteed, are not 100% tested in production

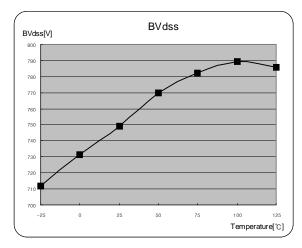

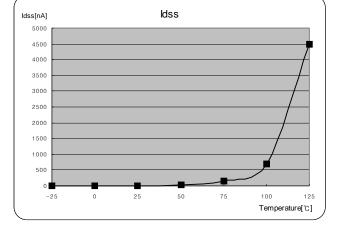

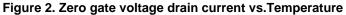

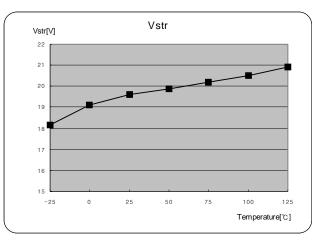

#### **Typical Performance Characteristics**

(These characteristic graphs are normalized at Ta=25°C)

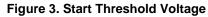

Figure 5. Operating Supply Current

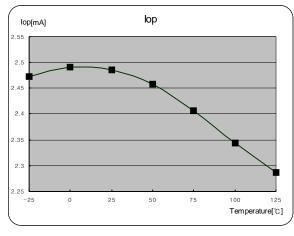

Figure 4. Stop Threshold Voltage

Figure 6.Vstr Supply Voltage

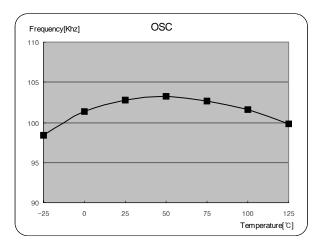

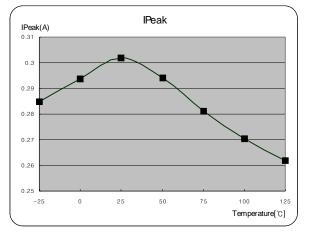

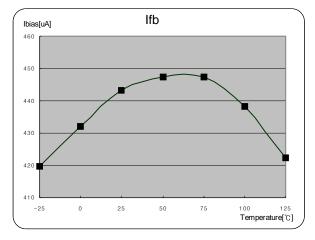

### Typical Performance Characteristics (Continued)

(These characteristic graphs are normalized at Ta=25°C)

Figure 7. Output Frequency

Figure 9. Peak Current Limit

Figure 8. Feedback Source Current

# **Typical Circuit**

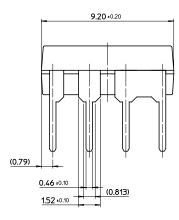

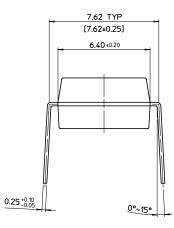

# Package Dimensions

#### **Ordering Information**

| Product Number | Package | Rating     | Topr (°C)      |

|----------------|---------|------------|----------------|

| FSDH565        | 8-DIPH  | 650V, 0.5A | –25°C to +85°C |

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com