## **High-Side N-Channel Switch with Current Limit**

#### **FEATURES**

- User Set Over Current Limit From 400 mA to 2.4 A

- Low  $r_{\mbox{DS(on)}}$  45 m $\Omega$  (max) at 25  $^{\circ}\mbox{C}$

- Fault Indicator

- Under Voltage Lockout

#### **APPLICATIONS**

- · Notebook Computers Power Management

- USB Power Distribution

- · Hot Plug In Power Supplies

- Power Supply/Load Protection

- · Battery-Charger Circuits

RoHS\*

#### **DESCRIPTION**

The Si4779CY n-channel high-side switch combines a low  $r_{DS(on)}$  MOSFET switch with a user set, pulse gate control (PGC) based current limit. This switch is designed to protect the system power supply from overloads and short circuit conditions in applications such as USB. The PGC based approach to the current limiter provides the additional benefit of keeping the

thereby eliminating the need for thermal shutdown. The low quiescent current makes the Si4779CY ideal for use in battery powered devices. The Si4779CY operates on both 3 V and 5 V busses, and is packaged in the LITTLE FOOT® SO-8 package.

MOSFET junction temperature within specification,

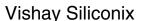

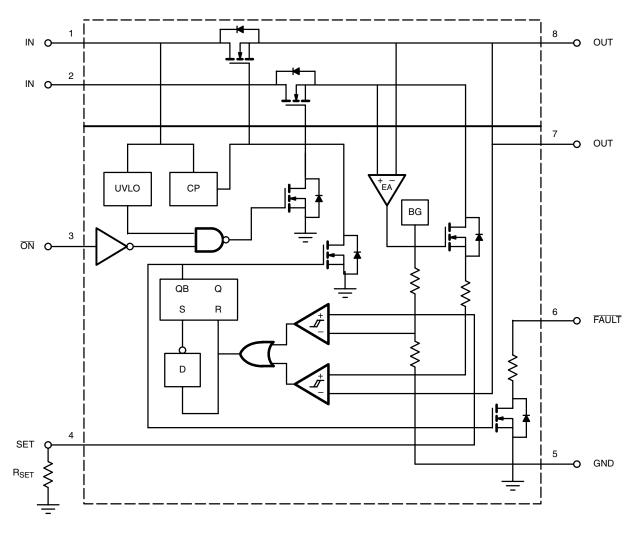

#### **FUNCTIONAL BLOCK DIAGRAM**

FIGURE 1.

<sup>\*</sup> Pb containing terminations are not RoHS compliant, exemptions may apply.

| ABSOLUTE MAXIMUM RATINGS T <sub>A</sub> = 25 °C, unless otherwise noted |                        |                                   |             |      |  |

|-------------------------------------------------------------------------|------------------------|-----------------------------------|-------------|------|--|

| Parameter                                                               |                        | Symbol                            | Limit       | Unit |  |

| Voltage, IN to GND                                                      | V <sub>IN</sub>        | - 0.3 to 7                        | v           |      |  |

| Voltage, ON                                                             | V <sub>ON</sub>        | - 0.3 to 7                        |             |      |  |

| Continuous Drain Current /T 150 °C)8                                    | T <sub>A</sub> = 25 °C | l <sub>D</sub>                    | 2.4         | Α    |  |

| Continuous Drain Current (T <sub>J</sub> = 150 °C) <sup>a</sup>         | T <sub>A</sub> = 85 °C |                                   | 2.4         |      |  |

| Maximum Power Dissipation <sup>a</sup> T <sub>A</sub> = 70 °C           |                        | $P_{D}$                           | 0.65        | W    |  |

| Operating Junction and Storage Temperature Range                        |                        | T <sub>J</sub> , T <sub>stg</sub> | - 65 to 125 | °C   |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING CONDITIONS |                                      |            |      |  |  |

|----------------------------------|--------------------------------------|------------|------|--|--|

| Parameter                        | Symbol                               | Typical    | Unit |  |  |

| Voltage, IN to GND               | V <sub>IN</sub>                      | 3.0 to 5.0 |      |  |  |

| Voltage, ON or FAULT to GND      | V <sub>ON</sub> , V <sub>FAULT</sub> | 0 to 5.0   | V    |  |  |

| Operating Temperature Range      | T <sub>A</sub>                       | 0 to 85    | °C   |  |  |

| THERMAL RESISTANCE RATINGS            |              |                   |         |         |      |  |

|---------------------------------------|--------------|-------------------|---------|---------|------|--|

| Parameter                             |              | Symbol            | Typical | Maximum | Unit |  |

| Junction-to-Ambient <sup>a</sup>      | Steady State | R <sub>thJA</sub> | 98      | 120     | °C/W |  |

| Junction-to-Foot (Drain) <sup>b</sup> | Sieduy Sidie | R <sub>thJF</sub> | 37      | 46      | C/VV |  |

a. Surface mounted on 1" x 1" FR4 board, 0.062" thick, 2-oz copper double sided.

b. Junction-to-foot thermal impedance represents the effective thermal impedance of all heat carrying leads in parallel and is intended for use in conjunction with the thermal impedance of the PC board pads to ambient (R<sub>thJA</sub> = R<sub>thJF</sub> + R<sub>thPCB-A</sub>). It can also be used to estimate chip temperature if power dissipation and the lead temperature of a heat carrying (drain) lead is known.

| SPECIFICATIONS                        |                       |                                                                                      |             |                  |       |      |  |

|---------------------------------------|-----------------------|--------------------------------------------------------------------------------------|-------------|------------------|-------|------|--|

| Parameter                             | Symbol                | Test Conditions Unless Specified                                                     | Limits      |                  |       |      |  |

| Parameter                             |                       | $T_A = 25  ^{\circ}C,  V_{IN} = 5  V$                                                |             | Typ <sup>a</sup> | Max   | Unit |  |

| Basic Operations                      |                       |                                                                                      |             |                  |       |      |  |

| Operating Voltage                     | V <sub>IN</sub>       |                                                                                      | 2.7         |                  | 5.5   | V    |  |

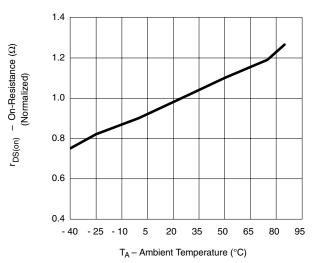

| On-State Resistance                   | r <sub>DS(on)</sub>   | V <sub>IN</sub> = 4.75 V, I <sub>D</sub> = 2 A                                       |             | 0.035            | 0.045 | .0   |  |

| On State Hedicianse                   |                       | V <sub>IN</sub> = 3.0 V, I <sub>D</sub> = 2 A                                        |             | 0.045            | 0.055 | 32   |  |

| Supply Current                        | I <sub>SUP(off)</sub> | $\overline{ON} = IN, V_{IN} = 5.5 V, V_{OUT} = 0 V$                                  |             |                  | 2     | μΑ   |  |

| Supply Suitem                         | I <sub>SUP(on)</sub>  | $\overline{ON} = GND$ , $V_{IN} = V_{OUT} = 5.5 \text{ V}$ , $I_{OUT} = 0 \text{ V}$ |             |                  | 70    |      |  |

| ON Input Low Voltage                  | $V_{ONL}$             | V <sub>IN</sub> = 2.7 V to 5.5 V                                                     |             |                  | 0.8   |      |  |

| ON Input High Voltage                 | V <sub>ONH</sub>      | V <sub>IN</sub> = 2.7 V to 3.6 V                                                     | o 3.6 V 2.0 |                  |       | V    |  |

| ON Input High Voltage                 | VONH                  | V <sub>IN</sub> = 4.5 V to 5.5 V                                                     | 2.4         |                  |       |      |  |

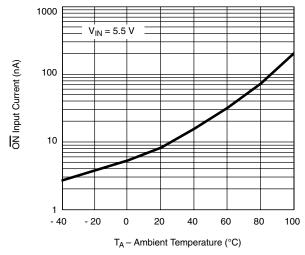

| ON Input Current                      | I <sub>ON</sub>       | V <sub>ON</sub> = 5.5 V                                                              |             | 0.01             | ± 1   | μΑ   |  |

| Protection                            |                       |                                                                                      |             |                  |       |      |  |

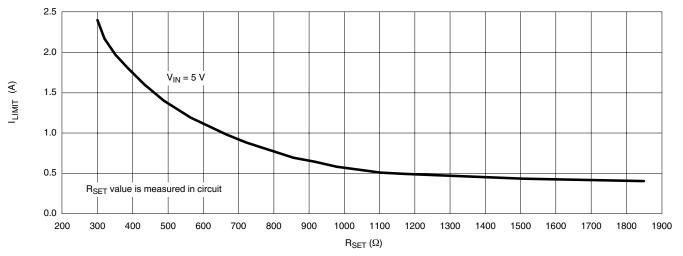

| Over Current Limit Range <sup>b</sup> | I <sub>LIMIT</sub>    | Tolerance = ± 20 %, V <sub>IN</sub> = 5 V                                            | 0.4         |                  | 2.4   | Α    |  |

| Under Voltage Lockout (rising edge)   | UVLO <sub>rise</sub>  |                                                                                      | 2.0         |                  | 4.0   |      |  |

| Under Voltage Lockout (falling edge)  | UVLO <sub>fall</sub>  |                                                                                      | 2.0         | 2.3              | 2.6   | V    |  |

| Under Voltage Hysteresis              | ΔUVLO                 |                                                                                      |             | 0.1              |       | v    |  |

| FAULT Output Voltage Low <sup>b</sup> | V <sub>FAULT</sub>    | I <sub>SINK</sub> = 100 μA                                                           |             |                  | 0.4   |      |  |

| FAULT Logic Output Leakage Current    | I <sub>FL</sub>       | V <sub>IN</sub> = V <sub>FAULT</sub> = 5.5 V                                         |             | 0.01             | 1     | μΑ   |  |

| Dynamic <sup>b</sup>                  |                       |                                                                                      |             |                  |       |      |  |

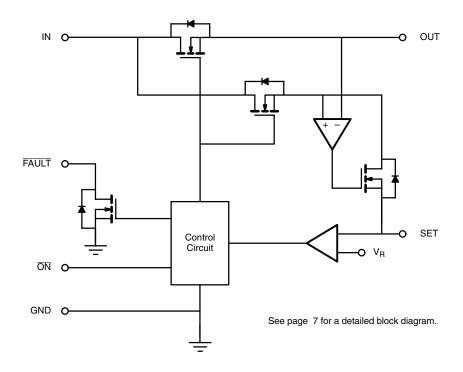

| Turn-On Time                          | t <sub>on</sub>       | $V_{IN} = 5 \text{ V, R}_{I} = 11 \Omega, C_{I} = 40 \mu\text{F}$                    |             | 3                |       | - ms |  |

| Rise Time                             | t <sub>r</sub>        | - ν <sub>IN</sub> – 5 ν, τις – τι 22, Ος – 40 μι                                     |             | 3.5              |       | 1115 |  |

| Turn-Off Time                         | t <sub>off</sub>      | V <sub>IN</sub> = 5 V, I <sub>OUT</sub> = 500 mA                                     |             | 1.5              |       |      |  |

| Fall Time                             | t <sub>f</sub>        |                                                                                      |             | 0.5              |       | μs   |  |

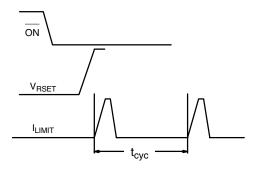

| Cycle Time                            | t <sub>cyc</sub>      | $V_{IN} = 5 \text{ V}, R_{L} = 0.5 \Omega$                                           |             | 8                |       | ms   |  |

#### Notes

- a. Typical values at  $T_A = 25$  °C are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- b. Guaranteed by design. Derived from I<sub>SET</sub> current ratio, current-limit amplifier and external set resistor accuracy.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **TIMING DIAGRAMS**

90 %

OUT 10 %

$t_{rise}$

90 %

OUT

10 %

# VISHAY.

#### **TIMING DIAGRAMS**

FIGURE 4.

### TYPICAL CHARACTERISTICS 25 °C, unless noted

FIGURE 5.  $R_{\rm SET}$  vs.  $I_{\rm LIMIT}$

FIGURE 6. Supply Current, Output Disable vs. Ambient Temperature Over Operating Voltage

FIGURE 7. Normalized On-Resistance vs. Ambient Temperature

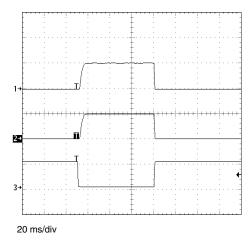

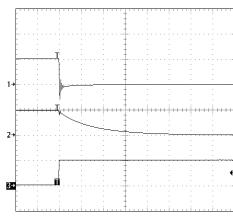

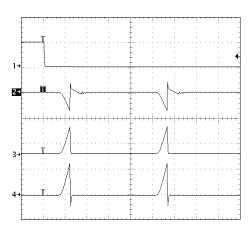

## **TYPICAL WAVEFORMS** $V_{IN} = 5 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$ , unless otherwise noted

CH1:  $I_{OUT}$ , 2 A/div CH2:  $V_{OUT}$ , 5 V/div,  $C_L$  = 47  $\mu$ F CH3:  $\overline{ON}$ , 5 V/div

#### FIGURE 8. Switch Turn-ON/OFF Time

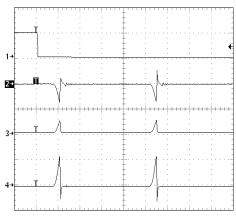

CH1:  $I_{OUT}$ , 0.5 A/div CH2:  $V_{OUT}$ , 5 V/div,  $C_L$  = 10  $\mu$ F CH3:  $\overline{ON}$ , 5 V/div

NOTE: Discharge time based primarily on external R and C

FIGURE 10. Switch Turn-OFF Time

CH1:  $I_{OUT}$ , 0.5 A/div CH2:  $V_{OUT}$ , 5 V/div,  $C_L$  = 10  $\mu$ F CH3:  $\overline{ON}$ , 5 V/div

#### FIGURE 9. Switch Turn-ON Time

200 μs/div

CH1:  $I_{OUT}$ , 0.5 A/div CH2:  $V_{OUT}$ , 5 V/div,  $C_L$  = 150  $\mu$ F CH3:  $\overline{ON}$ , 5 V/div

NOTE: Discharge time based primarily on external R and C

FIGURE 11. Switch Turn-OFF Time

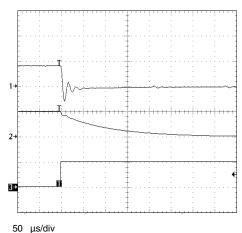

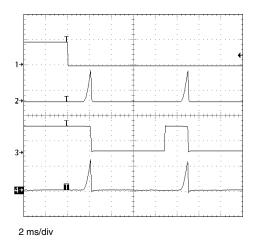

## **TYPICAL WAVEFORMS** $V_{IN} = 5 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$ , unless otherwise noted

CH1:  $\overline{ON}$ , 5 V/div

CH2:  $V_{OUT}$ , 5 V/div,  $R_L$  = 0.5  $\Omega$ ,  $C_L$  = 47  $\mu F$  CH3: FAULT, 5 V/div

CH4: I<sub>OUT</sub>, 1 A/div

### FIGURE 12. FAULT to Short Response (t<sub>cyc</sub>)

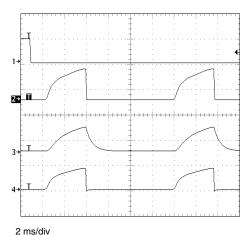

2 ms/div

CH1:  $\overline{ON}$ , 5 V/div CH2: PS Droops, 50 mV/div, Offset = 5 V CH3:  $V_{OUT}$ , 1 V/div,  $R_L$  = 0.5  $\Omega$ ,  $C_L$  = 100  $\mu F$

CH4: I<sub>OUT</sub>, 0.5 A/div

NOTE: Special test with 820- $\mu F$  capacitor at PS and  $R_{\mbox{\footnotesize SET}}$  setup for 0.5 A.

FIGURE 14. Power Supply Droops vs. Short

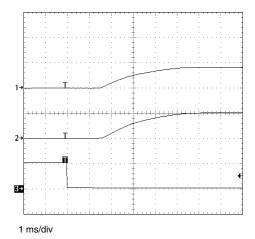

CH1:  $\overline{ON}$ , 5 V/div

CH2:  $V_{RESET}$ , 500 mV/div CH3:  $V_{OUT}$ , 5 V/div,  $R_L$  = 5.6  $\Omega$ ,  $C_L$  = 100  $\mu F$

CH4: I<sub>OUT</sub>, 1 A/div

FIGURE 13. V<sub>RESET</sub> to Over Current Response

2 ms/div

CH1:  $\overline{ON}$ , 5 V/div CH2: PS Droops, 100 mV/div, Offset = 5 V CH3:  $V_{OUT}$ , 1 V/div,  $R_L$  = 0.5  $\Omega$ ,  $C_L$  = 100  $\mu F$

CH4: I<sub>OUT</sub>, 2 A/div

NOTE: Special test with 820- $\mu\text{F}$  capacitor at PS and R\_SET setup for 2.4 A.

FIGURE 15. Power Supply Droops vs. Short

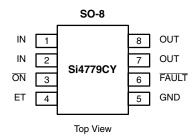

### **PIN CONFIGURATION**

Ordering Information: Si4779CY-T1 Si4779CY-T1-E3 (Lead (Pb)-free)

| PIN  | PIN DESCRIPTION |                                                                                                                                                                                      |  |  |  |  |

|------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin  | Symbol          | Description                                                                                                                                                                          |  |  |  |  |

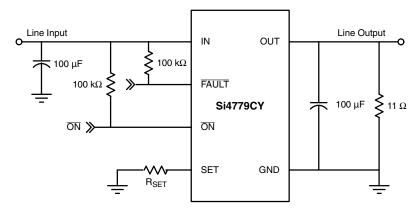

| 1, 2 | IN              | Input. N-channel MOSFET drain, bypass IN with a 100 $\mu\text{F}$ capacitor to GND.                                                                                                  |  |  |  |  |

| 3    | ŌN              | Active-low switch-on input, logic low turns switch on. $\overline{ON}$ needs to be connected to $V_{IN}$ during power up, then connect to GND to activate the switch after power up. |  |  |  |  |

| 4    | SET             | Current-limit input. A resistor from SET to GND sets the current limit for the switch.                                                                                               |  |  |  |  |

| 5    | GND             | Ground                                                                                                                                                                               |  |  |  |  |

| 6    | FAULT           | Fault indicator output. This open drain output goes low when the circuit is in current limit or in short circuit protection mode.                                                    |  |  |  |  |

| 7, 8 | OUT             | Switch output. N-channel MOSFET source.                                                                                                                                              |  |  |  |  |

### **DETAILED BLOCK DIAGRAM**

FIGURE 16.

# VISHAY.

#### **DETAILED DESCRIPTION**

The SI4779CY limits the output current to a user-defined level. When the output current passes through the main switch a fraction of this current passes through a replica switch and  $R_{\rm SFT}$ .

$R_{SET}$  is an external sense resistor used to set the level of the over current limit; the over current limit should be set between 0.4 A and 2.4 A (see graph for  $R_{SET}$  value vs. current limit). The circuit shuts down the switch when the current flowing through the switch exceeds Ilimit. After a short period of time, the circuit will slowly turn on the switch again. The length of time off is based on aver-

age power consumption, which is designed to be kept under 500 mW.

If the output is shorted, the circuit will go into an on-off cycle to protect the switch and to prevent the battery from draining down.

The fault output ( $\overline{\text{FAULT}}$ ) goes low when the circuit is in over current limit or short circuit protection mode. A 100 k $\Omega$  pull-up resistor from  $\overline{\text{FAULT}}$  to IN provides a logic-control signal.

#### **APPLICATIONS DIAGRAM**

FIGURE 17.

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="http://www.vishay.com/ppg?71664">http://www.vishay.com/ppg?71664</a>.

Vishay

## **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Revision: 18-Jul-08

Document Number: 91000 www.vishay.com