# 16 Kbit (2K x 8) AutoStore nvSRAM

### **Features**

- 25 ns and 45 ns access times

- Hands off automatic STORE on power down with external 68 µF capacitor

- STORE to QuantumTrap™ nonvolatile elements is initiated by software, hardware, or AutoStore™ on power down

- RECALL to SRAM initiated by software or power up

- Unlimited Read, Write, and Recall cycles

- 1,000,000 STORE cycles to QuantumTrap

- 100 year data retention to QuantumTrap

- Single 5V±10% operation

- Commercial and industrial temperatures

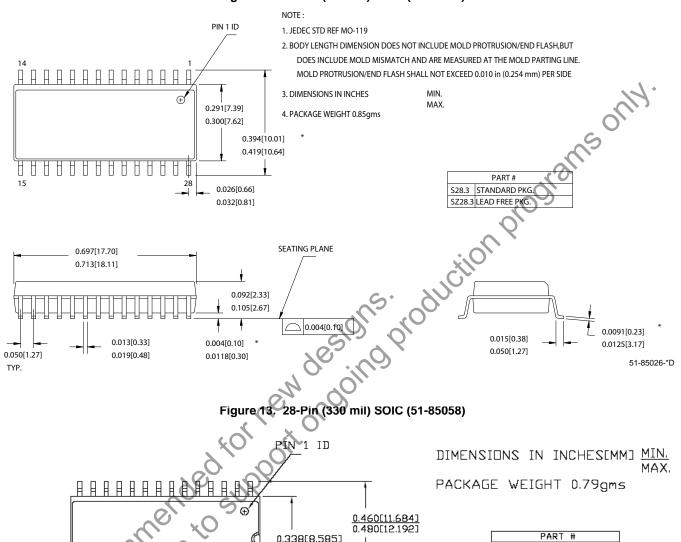

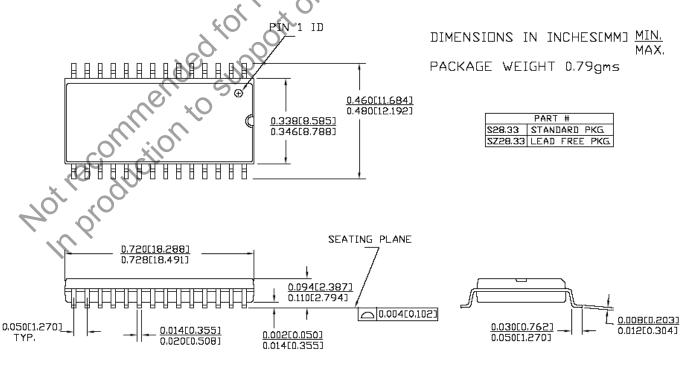

- 28-pin 300 mil and (330 mil) SOIC package

- RoHS compliance

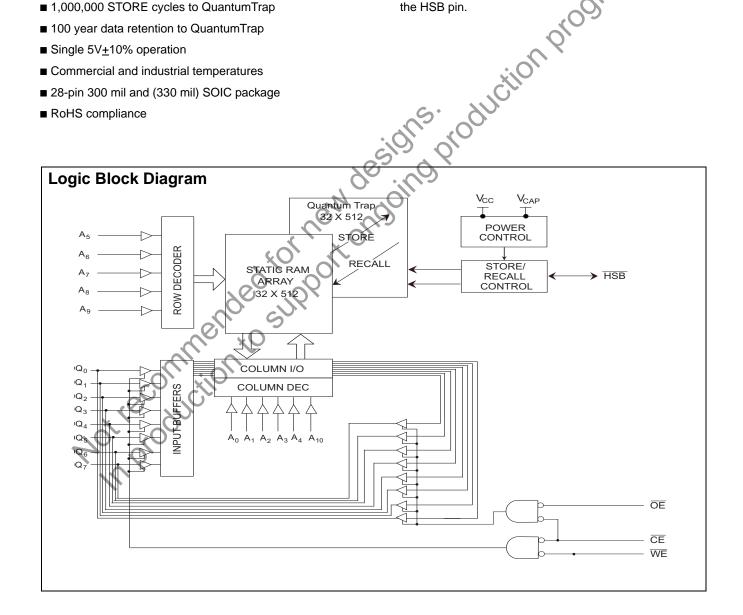

## **Functional Description**

The Cypress STK22C48 is a fast static RAM with a nonvolatile element in each memory cell. The embedded nonvolatile elements incorporate QuantumTrap technology producing the world's most reliable nonvolatile memory. The SRAM provides unlimited read and write cycles, while independent nonvolatile data resides in the highly reliable Quantum rap cell. Data transfers from the SRAM to the nonvolatile elements (the STORE operation) takes place automatically at power down. On power up, data is restored to the SRAM (the RECALL operation) from the nonvolatile memory. A hardware STORE is initiated with the HSB pin.

**Cypress Semiconductor Corporation** Document Number: 001-51000 Rev. \*A

198 Champion Court

San Jose, CA 95134-1709 408-943-2600 Revised December 11, 2009

### **Contents**

| Features                               | 1        | Data Retention a         |

|----------------------------------------|----------|--------------------------|

| Functional Description                 | 1        | Capacitance              |

| Logic Block Diagram                    | 1        | Thermal Resistar         |

| Contents                               | 2        | <b>AC Test Condition</b> |

| Device Operation                       | 3        | <b>AC Switching Ch</b>   |

| SRAM Read                              | 3        | SRAM Read                |

| SRAM Write                             | 3        | Switching Wavef          |

| AutoStore Operation                    | 3        | SRAM Write               |

| AutoStore Inhibit mode                 | 3        | AutoStore or Pov         |

| Hardware STORE (HSB) Operation         | 4        | Switching Wavef          |

| Hardware RECALL (Power Up)             | 4        | Hardware STORE           |

| Data Protection                        | 4        | Switching Wavef          |

| Noise Considerations                   | 4        | Ordering Informa         |

| Hardware Protect                       | 4        | Part Numbering I         |

| Low Average Active Power               | 4        | Package Diagran          |

| Preventing Store                       | 5        | <b>Document Histor</b>   |

| Best Practices                         | 5        | Sales, Solutions,        |

| Maximum Ratings                        | 6        | Worldwide Sa<br>Products |

| Operating Range                        | 6        | Products                 |

| DC Electrical Characteristics          | 6        | 9. 1                     |

|                                        | 65,      | 76                       |

|                                        | <b>\</b> | 700                      |

| . 6                                    |          |                          |

|                                        | 20)      | ,                        |

|                                        | 11,2     |                          |

|                                        |          |                          |

|                                        |          |                          |

| 20 20                                  |          |                          |

| 70 16,                                 |          |                          |

|                                        |          |                          |

| ~°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°° |          |                          |

|                                        |          |                          |

|                                        |          |                          |

| co. His                                |          |                          |

| .00                                    |          |                          |

| * 10 -00.                              |          |                          |

| 10, 10,                                |          |                          |

| 4 0,                                   |          |                          |

| Low Average Active Power               |          |                          |

|                                        |          |                          |

|                                        |          |                          |

|                                        |          |                          |

|                                        |          |                          |

|                                        |          |                          |

| Data Retention and Endurance              | 6  |

|-------------------------------------------|----|

| Capacitance                               | 7  |

| Thermal Resistance                        | 7  |

| AC Test Conditions                        | 7  |

| AC Switching Characteristics              | 8  |

| SRAM Read Cycle                           | 8  |

| Switching Waveforms                       |    |

| SRAM Write Cycle                          | 9  |

| AutoStore or Power Up RECALL 1            | 10 |

| Switching Waveform 1                      | 0  |

| Hardware STORE Cycle 1                    | 11 |

| Switching Waveform 1                      | 11 |

| Ordering Information 1                    |    |

| Part Numbering Nomenclature 1             | 2  |

| Package Diagrams1                         | 13 |

| Document History Page 1                   | 4  |

| Sales, Solutions, and Legal Information 1 | 4  |

| Worldwide Sales and Design Support 1      |    |

| Products                                  | 4  |

## **Device Operation**

The STK22C48 nvSRAM is made up of two functional components paired in the same physical cell. These are an SRAM memory cell and a nonvolatile QuantumTrap cell. The SRAM memory cell operates as a standard fast static RAM. Data in the SRAM is transferred to the nonvolatile cell (the STORE operation) or from the nonvolatile cell to SRAM (the RECALL operation). This unique architecture enables the storage and recall of all cells in parallel. During the STORE and RECALL operations, SRAM Read and Write operations are inhibited. The STK22C48 supports unlimited reads and writes similar to a typical SRAM. In addition, it provides unlimited RECALL operations from the nonvolatile cells and up to one million STORE operations.

## **SRAM Read**

The STK22C48 performs a Read cycle whenever  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  are LOW while  $\overline{\text{WE}}$  and  $\overline{\text{HSB}}$  are HIGH. The address specified on pins  $A_{0-10}$  determines the 2,048 data bytes accessed. When the Read is initiated by an address transition, the outputs are valid after a delay of  $t_{AA}$  (Read cycle 1). If the Read is initiated by  $\overline{\text{CE}}$  or  $\overline{\text{OE}}$ , the outputs are valid at  $t_{ACE}$  or at  $t_{DOE}$ , whichever is later (Read cycle 2). The data outputs repeatedly respond to address changes within the  $t_{AA}$  access time without the need for transitions on any control input pins, and remains valid until another address change or until  $\overline{\text{CE}}$  or  $\overline{\text{OE}}$  is brought HIGH, or  $\overline{\text{WE}}$  or  $\overline{\text{HSB}}$  is brought LOW.

### SRAM Write

<u>A Write cycle</u> is performed whenever  $\overline{CE}$  and  $\overline{WE}$  are LOW and HSB is HIGH. The address inputs must be stable prior to entering the Write cycle and must remain stable until either  $\overline{CE}$  or  $\overline{WE}$  goes HIGH at the end of the cycle. The data on the common I/O pins  $DQ_{0-7}$  are written into the memory if it has valid  $t_{SD}$ , before the end of a  $\overline{WE}$  controlled Write or before the end of an  $\overline{CE}$  controlled Write. Keep  $\overline{OE}$  HIGH during the entire  $\overline{WE}$  rite cycle to avoid data bus contention on common I/O lines. If  $\overline{OE}$  is  $\overline{left}$  LOW, internal circuitry turns off the output buffers  $t_{HZWE}$  after  $\overline{WE}$  goes I OW

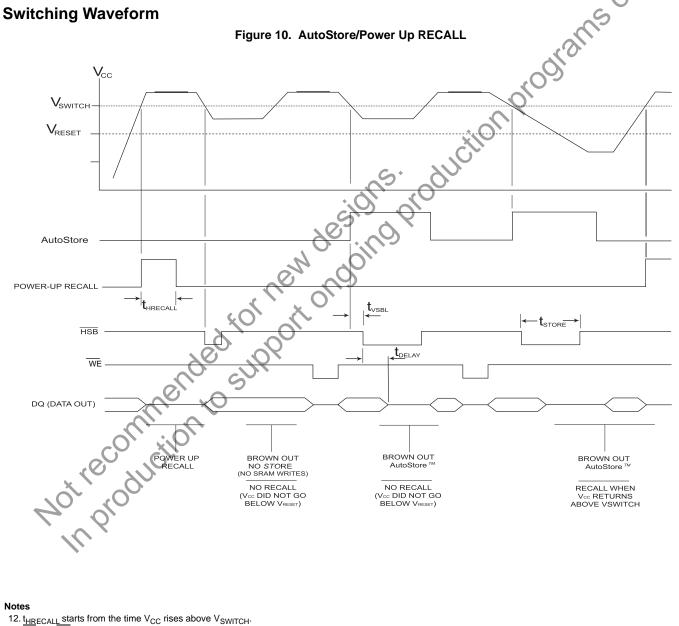

## **AutoStore Operation**

During normal operation, the device draws current from  $V_{CC}$  to charge a capacitor connected to the  $V_{CAP}$  pin. This stored charge is used by the chip to perform a single STORE operation. If the voltage on the  $V_{CC}$  pin drops below  $V_{SWITCH}$ , the part automatically disconnects the  $V_{CAP}$  pin from  $V_{CC}$ . A STORE operation is initiated with power provided by the  $V_{CAP}$  capacitor.

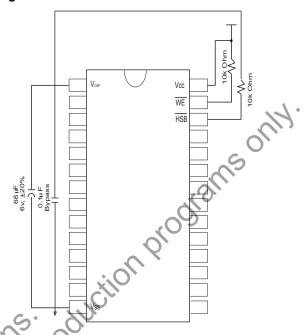

Figure 1 shows the proper connection of the storage capacitor ( $V_{CAP}$ ) for automatic store operation. A charge storage capacitor between 68  $\mu F$  and 220  $\mu F$  ( $\pm 20\%$ ) rated at 6V should be

Figure 1. AutoStore Mode

In system power mode, both V $_{CC}$  and V $_{CAP}$  are connected to the +5V power supply without the 68  $\mu F$  capacitor. In this mode, the AutoStore function of the STK22C48 operates on the stored system charge as power goes down. The user must, however, guarantee that V $_{CC}$  does not drop below 3.6V during the 10 ms STORE cycle.

To prevent unneeded STORE operations, automatic STOREs and those initiated by externally driving HSB LOW are ignored, unless at least one WRITE operation takes place since the most recent STORE or RECALL cycle. An optional pull up resistor is shown connected to HSB. This is used to signal the system that the AutoStore cycle is in progress.

### AutoStore Inhibit mode

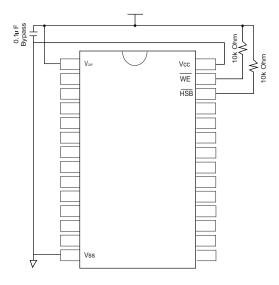

If an automatic STORE on power loss is not required, then  $V_{CC}$  is tied to ground and +5V is applied to  $V_{CAP}$  (Figure 2). This is the AutoStore Inhibit mode, where the AutoStore function is disabled. If the STK22C48 is operated in this configuration, references to  $V_{CC}$  are changed to  $V_{CAP}$  throughout this data sheet. In this mode, STORE operations are triggered with the HSB pin. It is not permissible to change between these three options "on the fly".

Figure 2. AutoStore Inhibit Mode

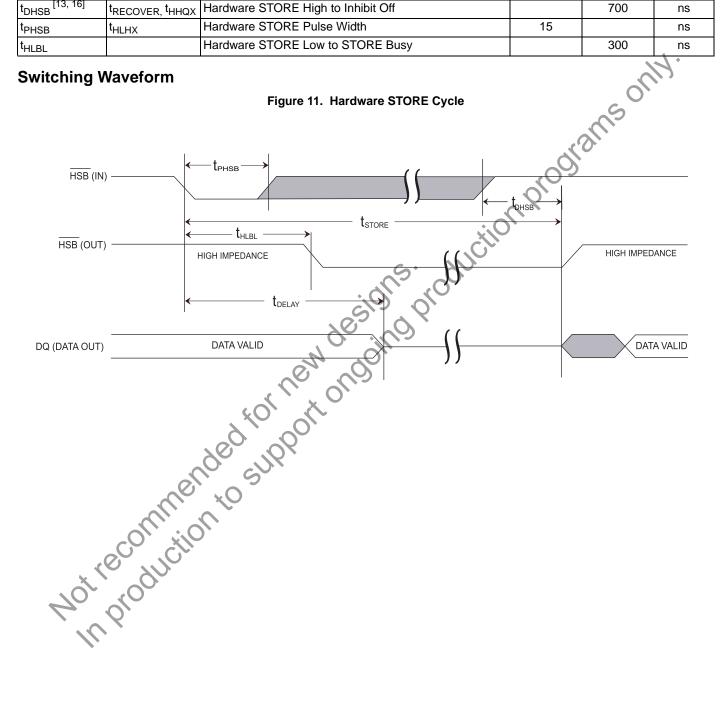

## Hardware STORE (HSB) Operation

The STK22C48 provides the  $\overline{\text{HSB}}$  pin for controlling and acknowledging the STORE operations. The  $\overline{\text{HSB}}$  pin is used to request a hardware STORE cycle. When the  $\overline{\text{HSB}}$  pin is driven LOW, the STK22C48 conditionally initiates a STORE operation after t<sub>DELAY</sub>. An actual STORE cycle only begins if a Write to the  $\overline{\text{SRAM}}$  takes place since the last STORE or RECALL cycle. The  $\overline{\text{HSB}}$  pin also acts as an open drain driver that is internally driven LOW to indicate a busy condition, while the STORE (initiated by any means) is in progress. Pull up this pin with an external 10K ohm resistor to V<sub>CAP</sub> if  $\overline{\text{HSB}}$  is used as a driver.

$\underline{\mathtt{SRAM}}$  Read and Write operations, that are in progress when  $\overline{\mathsf{HSB}}$  is driven LOW by any means, are given  $\underline{\mathsf{time}}$  to complete before the STORE operation is initiated. After  $\overline{\mathsf{HSB}}$  goes LOW, the STK22C48 continues SRAM operations for  $\mathsf{t}_{\mathsf{DELAY}}$ . During  $\mathsf{t}_{\mathsf{DELAY}}$ , multiple SRAM Read operations take place. If a Write is in progress when  $\overline{\mathsf{HSB}}$  is pulled LOW, it allows a time,  $\mathsf{t}_{\mathsf{DELAY}}$  to  $\underline{\mathsf{complete}}$ . However, any SRAM Write cycles requested after  $\overline{\mathsf{HSB}}$  goes LOW are inhibited until  $\overline{\mathsf{HSB}}$  returns HIGH.

During any STORE operation, regardless of how it is initiated, the STK22C48 continues to drive the HSB pin LOW, releasing it only when the STORE is complete. After completing the STORE operation, the STK22C48 remains disabled until the HSB pin returns HIGH.

If HSB is not used, it is left unconnected.

## Hardware RECALL (Power Up)

During power up or after any low power condition ( $V_{CC} < V_{RESET}$ ), an internal RECALL request is latched. When  $V_{CC}$  once again exceeds the sense voltage of  $V_{SWITCH}$ , a RECALL cycle is automatically initiated and takes  $t_{HRECALL}$  to complete.

### **Data Protection**

The STK22C48 protects data from corruption during low voltage conditions by inhibiting all externally initiated STORE and Write operations. The low voltage condition is detected when  $V_{CC}$  is less than  $V_{SWITCH}$ . If the STK22C48 is in a Write mode (both CE and  $\overline{WE}$  are low) at power up after a RECALL or after a STORE, the Write is inhibited until a negative transition on  $\overline{CE}$  or  $\overline{WE}$  is detected. This protects against inadvertent writes during power up or brown out conditions.

### **Noise Considerations**

The STK22C48 is a high speed memory. It must have a high frequency bypass capacitor of approximately 0.1  $\mu F$  connected between  $V_{CC}$  and  $V_{SS}$ , using leads and traces that are as short as possible. As with all high speed CMOS ICs, careful routing of power, ground, and signals reduce circuit noise.

## **Hardware Protect**

The STK22C48 offers hardware protection against inadvertent STORE operation and SRAM Writes during low voltage conditions. When  $V_{CAP} \triangleleft V_{SWITCH}$ , all externally initiated STORE operations and SRAM Writes are inhibited. AutoStore can be completely disabled by tying VCC to ground and applying +5V to  $V_{CAP}$ . This is the AutoStore Inhibit mode; in this mode, STOREs are only initiated by explicit request using either the software sequence or the  $\overline{HSB}$  pin.

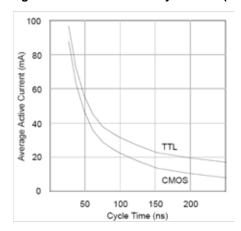

## Low Average Active Power

CMOS technology provides the STK22C48 the benefit of drawing significantly less current when it is cycled at times longer than 50 ns. Figure 3 shows the relationship between  $I_{CC}$  and Read or Write cycle time. Worst case current consumption is shown for both CMOS and TTL input levels (commercial temperature range, VCC = 5.5V, 100% duty cycle on chip enable). Only standby current is drawn when the chip is disabled. The overall average current drawn by the STK22C48 depends on the following items:

- The duty cycle of chip enable

- The overall cycle rate for accesses

- The ratio of Reads to Writes

- CMOS versus TTL input levels

- The operating temperature

- The V<sub>CC</sub> level

- I/O loading

Document Number: 001-51000 Rev. \*A Page 4 of 14

Figure 3. Current Versus Cycle Time (Read)

Figure 4. Current Versus Cycle Time (Write)

## **Preventing Store**

The STORE function is disabled by holding  $\overline{\text{HSB}}$  high with a driver capable of sourcing 30 mA at a  $V_{OH}$  of at least 2.2V, because it must overpower the internal pull down device. This

Table 1. Hardware Mode Selection

| CE | WE | HSB | A10-A0 | Mode              | I/O           | Power                           |

|----|----|-----|--------|-------------------|---------------|---------------------------------|

| Н  | X  | Н   | X      | Not Selected      | Output High Z | Standby                         |

| L  | ЭН | Н   | X      | Read SRAM         | Output Data   | Active <sup>[1]</sup>           |

| 74 | L  | Н   | X      | Write SRAM        | Input Data    | Active                          |

| X  | X  | L   | X      | Nonvolatile STORE | Output High Z | I <sub>CC2</sub> <sup>[2]</sup> |

device drives  $\overline{\text{HSB}}$  LOW for 20 ns at the onset of a STORE. When the STK22C48 is connected for AutoStore operation (system V<sub>CC</sub> connected to V<sub>CC</sub> and a 68  $\mu$ F capacitor on V<sub>CAP</sub>) and V<sub>CC</sub> crosses V<sub>SWITCH</sub> on the way down, the STK22C48 attempts to pull HSB LOW. If  $\overline{\text{HSB}}$  does not actually get below V<sub>IL</sub>, the part stops trying to pull HSB LOW and abort the STORE attempt.

## **Best Practices**

nvSRAM products have been used effectively for over 15 years. While ease of use is one of the product's main system values, experience gained working with hundreds of applications has resulted in the following suggestions as best practices:

- The nonvolatile cells in an nvSRAM are programmed on the test floor during final test and quality assurance. Incoming inspection routines at customer or contract manufacturer's sites sometimes reprogram these values. Final NV patterns are typically repeating patterns of AA, 55, 00, FF, A5, or 5A. The end product's firmware should not assume that an NV array is in a set programmed state. Routines that check memory content values to determine first time system configuration, cold or warm boot status, and so on must always program a unique NV pattern (for example, complex 4-byte pattern of 46 E6 49 53 hex or more random bytes) as part of the final system manufacturing test to ensure these system routines work consistently.

- Power up boot firmware routines should rewrite the nvSRAM into the desired state. While the nvSRAM is shipped in a preset state, best practice is to again rewrite the nvSRAM into the desired state as a safeguard against events that might flip the bit inadvertently (program bugs, incoming inspection routines, and so on).

- The V<sub>CAP</sub> value specified in this data sheet includes a minimum and a maximum value size. The best practice is to meet this requirement and not exceed the maximum V<sub>CAP</sub> value because the higher inrush currents may reduce the reliability of the internal pass transistor. Customers who want to use a larger V<sub>CAP</sub> value to make sure there is extra store charge should discuss their V<sub>CAP</sub> size selection with Cypress.

### Notes

1. I/O state assumes  $\overline{OE} \le V_{IL}$ . Activation of nonvolatile cycles does not depend on state of  $\overline{OE}$ .

HSB STORE operation occurs only if an SRAM Write is done since the last nonvolatile cycle. After the STORE (If any) completes, the part goes into standby mode, inhibiting all operations until HSB rises.

Document Number: 001-51000 Rev. \*A Page 5 of 14

## **Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. These user guidelines are not tested.

| Storage Temperature                        | –65°C to +150°C            |

|--------------------------------------------|----------------------------|

| Temperature under bias                     | –55°C to +125°C            |

| Supply Voltage on $V_{CC}$ Relative to GND | 0.5V to 7.0V               |

| Voltage on Input Relative to Vss           | $-0.6V$ to $V_{CC} + 0.5V$ |

| Voltage on DQ <sub>0-7</sub> or HSB  | 0.5V to Vcc + 0.5V     |

|--------------------------------------|------------------------|

| Power Dissipation                    | 1.0W                   |

| DC Output Current (1 output at a tin | ne, 1s duration) 15 mA |

## **Operating Range**

| Range      | Ambient Temperature | V <sub>CC</sub> |

|------------|---------------------|-----------------|

| Commercial | 0°C to +70°C        | 4.5V to 5.5V    |

| Industrial | -40°C to +85°C      | 4.5V to 5.5V    |

## **DC Electrical Characteristics**

Over the operating range ( $V_{CC}$  = 4.5V to 5.5V) [3]

| Parameter                       | Description                                                                   | Test Conditions                                                                                                                            |                                       | Min            | Max                   | Unit                 |

|---------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------|-----------------------|----------------------|

| I <sub>CC1</sub>                | Average V <sub>CC</sub> Current                                               | t <sub>RC</sub> = 25 ns<br>t <sub>RC</sub> = 45 ns<br>Dependent on output loading and cycle<br>rate. Values obtained without output loads. | Commercial Industrial                 |                | 85<br>65<br>90<br>65  | mA<br>mA<br>mA<br>mA |

| I <sub>CC2</sub>                | Average V <sub>CC</sub> Current during STORE                                  | I <sub>OUT</sub> = 0 mA.  All Inputs Do Not Care, V <sub>CC</sub> = Max  Average current for duration t <sub>STORE</sub>                   | 101,                                  |                | 3                     | mA                   |

| I <sub>CC3</sub>                | Average V <sub>CC</sub> Current at t <sub>RC</sub> = 200 ns, 5V, 25°C Typical | WE $\geq$ (V <sub>CC</sub> $-$ 0.2V). All other inputs cycling. Dependent on output loading and cycle rate obtained without output loads.  | . Values                              |                | 10                    | mA                   |

| I <sub>CC4</sub>                | Average V <sub>CAP</sub> Current during<br>AutoStore Cycle                    | All Inputs Do Not Care, V <sub>CC</sub> = Max<br>Average current for duration t <sub>STORE</sub>                                           |                                       |                | 2                     | mA                   |

| I <sub>SB1</sub> <sup>[4]</sup> | Average Vcc Current<br>(Standby, Cycling TTL Input                            | $t_{RC}$ = 25 ns, $\overrightarrow{CE} \ge V_{IH}$<br>$t_{RC}$ = 45 ns, $\overrightarrow{CE} \ge V_{IH}$                                   | Commercial                            |                | 25<br>18              | mA<br>mA             |

|                                 | Levels)                                                                       | LON LOS                                                                                                                                    | Industrial                            |                | 26<br>19              | mA<br>mA             |

| I <sub>SB2</sub> <sup>[4]</sup> | V <sub>CC</sub> Standby Current                                               | $CE \ge (V_{CC} - 0.2V)$ . All others $V_{IN} \le 0.2V$ or standby current level after nonvolatile cycle inputs are static. $f = 0$ MHz.   |                                       |                | 1.5                   | mA                   |

| I <sub>ILK</sub>                | Input Leakage Current                                                         | $V_{CC} = Max, V_{SS} \le V_{IN} \le V_{CC}$                                                                                               |                                       | -1             | +1                    | μΑ                   |

| I <sub>OLK</sub>                | Off State Output Leakage<br>Current                                           | $V_{CC} = Max, V_{SS} \le V_{IN} \le V_{CC}, \overline{CE} \text{ or } \overline{OE} \ge V_{CC}$                                           | <sub>IH</sub> or WE ≤ V <sub>IL</sub> | -5             | +5                    | μА                   |

| V <sub>IH</sub>                 | Input HIGH Voltage                                                            |                                                                                                                                            |                                       | 2.2            | V <sub>CC</sub> + 0.5 | V                    |

| $V_{IL}$                        | Input LOW Voltage                                                             |                                                                                                                                            |                                       | $V_{SS} - 0.5$ | 8.0                   | V                    |

| V <sub>OH</sub>                 | Output HIGH Voltage                                                           | I <sub>OUT</sub> = -4 mA except HSB                                                                                                        |                                       | 2.4            |                       | V                    |

| $V_{OL}$                        | Output LOW Voltage                                                            | I <sub>OUT</sub> = 8 mA except HSB                                                                                                         |                                       |                | 0.4                   | V                    |

| $V_{BL}$                        | Logic '0' Voltage on HSB Output                                               | I <sub>OUT</sub> = 3 mA                                                                                                                    |                                       |                | 0.4                   | V                    |

| V <sub>CAP</sub>                | Storage Capacitor                                                             | Between $V_{\text{CAP}}$ pin and Vss, 6V rated. 68 uF nom.                                                                                 | -10%, +20%                            | 61             | 220                   | μF                   |

# **Data Retention and Endurance**

| Parameter         | Description                  | Min   | Unit  |

|-------------------|------------------------------|-------|-------|

| DATA <sub>R</sub> | Data Retention               | 100   | Years |

| $NV_C$            | Nonvolatile STORE Operations | 1,000 | K     |

- V<sub>CC</sub> reference levels throughout this data sheet refer to VCC if that is where the power supply connection is made, or V<sub>CAP</sub> if VCC is connected to ground.

E ≥ V<sub>IH</sub> does not produce standby current levels until any nonvolatile cycle in progress has timed out.

Document Number: 001-51000 Rev. \*A Page 6 of 14

Capacitance

In the following table, the capacitance parameters are listed. [5]

| Parameter        | Description        | Test Conditions                         | Max | Unit |

|------------------|--------------------|-----------------------------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 8   | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 0$ to 3.0V                    | 7   | pF   |

### **Thermal Resistance**

In the following table, the thermal resistance parameters are listed. [5]

| Parameter     | Description                              | Test Conditions                                                                   | 28-SOIC<br>(300 mil) | 28-SOIC<br>(330 mil) | Unit |

|---------------|------------------------------------------|-----------------------------------------------------------------------------------|----------------------|----------------------|------|

| $\Theta_{JA}$ | Thermal Resistance (Junction to Ambient) | Test conditions follow standard test methods and procedures for measuring thermal | TBD                  | 7BD                  | °C/W |

| $\Theta_{JC}$ | Thermal Resistance (Junction to Case)    | impedance, per EIA / JESD51.                                                      | TBD                  | TBD                  | °C/W |

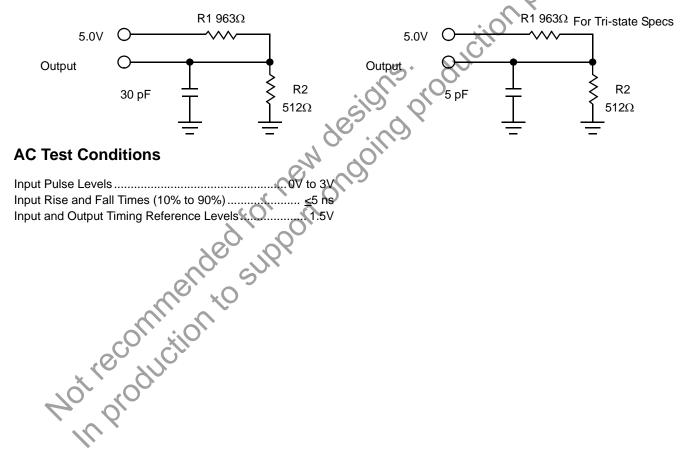

Figure 5. AC Test Loads

### Note

<sup>5.</sup> These parameters are guaranteed by design and are not tested.

## **AC Switching Characteristics**

## **SRAM Read Cycle**

| Pa                             | rameter                               |                                   | 25  | 25 ns |      | 45 ns |      |

|--------------------------------|---------------------------------------|-----------------------------------|-----|-------|------|-------|------|

| Cypress<br>Parameter           | Alt                                   | Description                       | Min | Max   | Min  | Max   | Unit |

| t <sub>ACE</sub>               | t <sub>ELQV</sub>                     | Chip Enable Access Time           |     | 25    |      | 45    | ns   |

| t <sub>RC</sub> <sup>[6]</sup> | t <sub>AVAV</sub> , t <sub>ELEH</sub> | Read Cycle Time                   | 25  |       | 45   |       | • ns |

| t <sub>AA</sub> <sup>[7]</sup> | t <sub>AVQV</sub>                     | Address Access Time               |     | 25    |      | 45    | ns   |

| t <sub>DOE</sub>               | t <sub>GLQV</sub>                     | Output Enable to Data Valid       |     | 10    |      | 20    | ns   |

| t <sub>OHA</sub> [7]           | t <sub>AXQX</sub>                     | Output Hold After Address Change  | 5   |       | 5    | 9     | ns   |

| t <sub>LZCE</sub> [8]          | t <sub>ELQX</sub>                     | Chip Enable to Output Active      | 5   |       | 5    |       | ns   |

| t <sub>HZCE</sub> [8]          | t <sub>EHQZ</sub>                     | Chip Disable to Output Inactive   |     | 10    | 4.O. | 15    | ns   |

| t <sub>LZOE</sub> [8]          | t <sub>GLQX</sub>                     | Output Enable to Output Active    | 0   |       | 0    |       | ns   |

| t <sub>HZOE</sub> [8]          | t <sub>GHQZ</sub>                     | Output Disable to Output Inactive |     | 10    |      | 15    | ns   |

| t <sub>PU</sub> <sup>[5]</sup> | t <sub>ELICCH</sub>                   | Chip Enable to Power Active       | 0   | 6     | 0    |       | ns   |

| t <sub>PD</sub> <sup>[5]</sup> | t <sub>EHICCL</sub>                   | Chip Disable to Power Standby     |     | 25    |      | 45    | ns   |

## **Switching Waveforms**

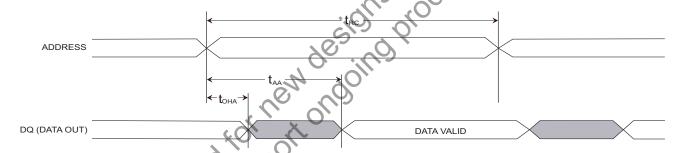

Figure 6. SRAM Read Cycle 1: Address Controlled  $^{[6,\,7]}$

Figure 7. SRAM Read Cycle 2: CE and OE Controlled [6]

### Notes

- WE and HSB must be High during SRAM Read cycles.

Device is continuously selected with CE and OE both Low.

- 8. Measured ±200 mV from steady state output voltage.

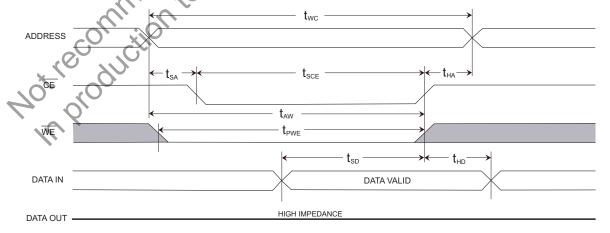

## **SRAM Write Cycle**

| Parameter               |                                       |                                  | 25  | ns  | 45 ns |      |      |

|-------------------------|---------------------------------------|----------------------------------|-----|-----|-------|------|------|

| Cypress<br>Parameter    | Alt                                   | Description                      | Min | Max | Min   | Max  | Unit |

| t <sub>WC</sub>         | t <sub>AVAV</sub>                     | Write Cycle Time                 | 25  |     | 45    |      | ns   |

| t <sub>PWE</sub>        | t <sub>WLWH</sub> , t <sub>WLEH</sub> | Write Pulse Width                | 20  |     | 30    |      | ns   |

| t <sub>SCE</sub>        | t <sub>ELWH</sub> , t <sub>ELEH</sub> | Chip Enable To End of Write      | 20  |     | 30    | 4    | ns   |

| t <sub>SD</sub>         | t <sub>DVWH</sub> , t <sub>DVEH</sub> | Data Setup to End of Write       | 10  |     | 15    |      | ns   |

| t <sub>HD</sub>         | t <sub>WHDX</sub> , t <sub>EHDX</sub> | Data Hold After End of Write     | 0   |     | 0     | 2(1) | ns   |

| t <sub>AW</sub>         | t <sub>AVWH</sub> , t <sub>AVEH</sub> | Address Setup to End of Write    | 20  |     | 30    | 0    | ns   |

| t <sub>SA</sub>         | t <sub>AVWL</sub> , t <sub>AVEL</sub> | Address Setup to Start of Write  | 0   |     | 0     | 7    | ns   |

| t <sub>HA</sub>         | t <sub>WHAX</sub> , t <sub>EHAX</sub> | Address Hold After End of Write  | 0   |     | 0     |      | ns   |

| t <sub>HZWE</sub> [8,9] | t <sub>WLQZ</sub>                     | Write Enable to Output Disable   |     | 10  | Ko    | 14   | ns   |

| t <sub>LZWE</sub> [8]   | t <sub>WHQX</sub>                     | Output Active After End of Write | 5   | .0  | 5     |      | ns   |

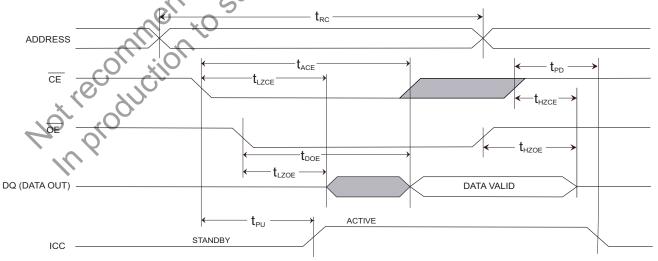

**Switching Waveforms**

Figure 8. SRAM Write Cycle 1: WE Controlled [10, 1]

Figure 9. SRAM Write Cycle 2: CE Controlled [10, 11]

- Notes

9. If WE is Low when CE goes Low, the outputs remain in the high impedance state.

10. HSB must be high during SRAM Write cycles.

11. CE or WE must be greater than V<sub>IH</sub> during address transitions.

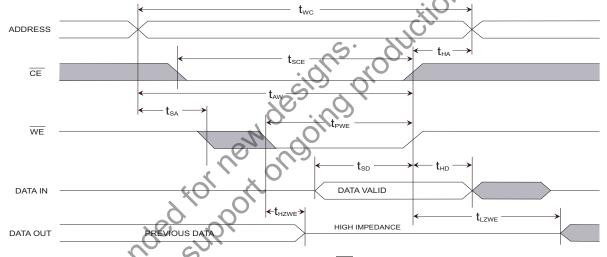

**AutoStore or Power Up RECALL**

| Parameter                         | Alt                                   | Description                                           | STK22C48 |     | Unit  |  |

|-----------------------------------|---------------------------------------|-------------------------------------------------------|----------|-----|-------|--|

| Parameter                         |                                       | Description                                           | Min      | Max | Offic |  |

| t <sub>HRECALL</sub> [12]         | t <sub>RESTORE</sub>                  | Power up RECALL Duration                              |          | 550 | μS    |  |

| t <sub>STORE</sub> [14, 15]       | t <sub>HLHZ</sub>                     | STORE Cycle Duration                                  |          | 10  | ms    |  |

| t <sub>DELAY</sub> [13]           | t <sub>HLQZ</sub> , t <sub>BLQZ</sub> | Time Allowed to Complete SRAM Cycle                   | 1        |     | μS    |  |

| V <sub>SWITCH</sub>               |                                       | Low Voltage Trigger Level                             | 4.0      | 4.5 | V     |  |

| V <sub>RESET</sub>                |                                       | Low Voltage Reset Level                               |          | 3.6 | 14    |  |

| t <sub>VSBL</sub> <sup>[10]</sup> |                                       | Low Voltage Trigger (V <sub>SWITCH</sub> ) to HSB Low |          | 300 | ns    |  |

### Notes

- 12.  $\underline{t_{HRECALL}}$  starts from the time  $V_{CC}$  rises above  $V_{SWITCH}$ . 13.  $\overline{CE}$  and  $\overline{OE}$  low for output behavior.

- 14.  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  low and WE high for output behavior.

- 15. HSB is asserted low for 1us when V<sub>CAP</sub> drops through V<sub>SWITCH</sub>. If an SRAM Write has not taken place since the last nonvolatile cycle, HSB is released and no store takes place.

## **Hardware STORE Cycle**

| Parameter                  | Alt                                      | Description                        | STK22C48 |     | Unit  |

|----------------------------|------------------------------------------|------------------------------------|----------|-----|-------|

|                            |                                          |                                    | Min      | Max | Offic |

| t <sub>DHSB</sub> [13, 16] | t <sub>RECOVER</sub> , t <sub>HHQX</sub> | Hardware STORE High to Inhibit Off |          | 700 | ns    |

| t <sub>PHSB</sub>          | t <sub>HLHX</sub>                        | Hardware STORE Pulse Width         | 15       |     | ns    |

| t <sub>HLBL</sub>          |                                          | Hardware STORE Low to STORE Busy   |          | 300 | ns    |

### Note

<sup>16.</sup>  $t_{\mbox{\scriptsize DHSB}}$  is only applicable after  $t_{\mbox{\scriptsize STORE}}$  is complete.

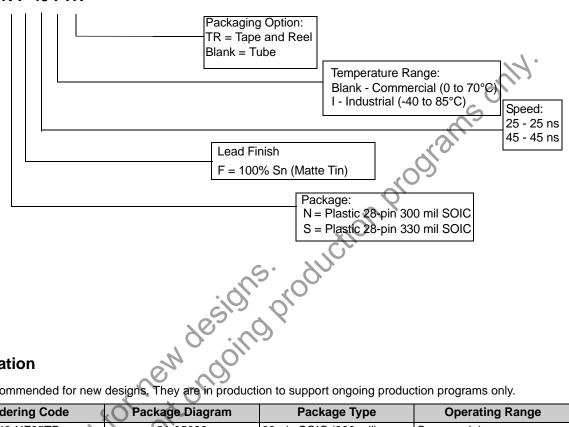

## **Part Numbering Nomenclature**

## STK22C48 - N F 45 I TR

## **Ordering Information**

These parts are not recommended for new designs. They are in production to support ongoing production programs only.

| Speed (ns) | Ordering Code    | Package Diagram | Package Type          | Operating Range |

|------------|------------------|-----------------|-----------------------|-----------------|

| 25         | STK22C48-NF25TR  | 51-85026        | 28-pin SOIC (300 mil) | Commercial      |

|            | STK22C48-NF25    | 51-85026        | 28-pin SOIC (300 mil) |                 |

|            | STK22C48-SF25TR  | 51-85058        | 28-pin SOIC (330 mil) |                 |

|            | STK22C48-SF25    | 51-85058        | 28-pin SOIC (330 mil) |                 |

|            | STK22C48-NF25ITR | 51-85026        | 28-pin SOIC (300 mil) | Industrial      |

|            | STK22C48-NF25I   | 51-85026        | 28-pin SOIC (300 mil) |                 |

|            | STK22C48-SF25ITR | 51-85058        | 28-pin SOIC (330 mil) |                 |

|            | STK22C48-SF25I   | 51-85058        | 28-pin SOIC (330 mil) |                 |

| 45         | STK22C48-NF45TR  | 51-85026        | 28-pin SOIC (300 mil) | Commercial      |

| 70         | STK22C48-NF45    | 51-85026        | 28-pin SOIC (300 mil) |                 |

| 1          | STK22C48-SF45TR  | 51-85058        | 28-pin SOIC (330 mil) |                 |

|            | STK22C48-SF45    | 51-85058        | 28-pin SOIC (330 mil) |                 |

|            | STK22C48-NF45ITR | 51-85026        | 28-pin SOIC (300 mil) | Industrial      |

|            | STK22C48-NF45I   | 51-85026        | 28-pin SOIC (300 mil) |                 |

|            | STK22C48-SF45ITR | 51-85058        | 28-pin SOIC (330 mil) |                 |

|            | STK22C48-SF45I   | 51-85058        | 28-pin SOIC (330 mil) |                 |

All parts are Pb-free. The above table contains Final information. Please contact your local Cypress sales representative for availability of these parts

## **Package Diagrams**

Figure 12. 28-Pin (300 mil) SOIC (51-85026)

51-85058-\*A

## **Document History Page**

|      | Document Title: STK22C48 16 Kbit (2K x 8) AutoStore nvSRAM Document Number: 001-51000 |                    |                    |                                                                                                                                                                                                                                                                                                                                  |  |  |

|------|---------------------------------------------------------------------------------------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Rev. | ECN No.                                                                               | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                            |  |  |

| **   | 2625139                                                                               | GVCH/PYRS          | 01/30/09           | New data sheet                                                                                                                                                                                                                                                                                                                   |  |  |

| *A   | 2826441                                                                               | GVCH               | 12/11/2009         | Added following text in the Ordering Information section: "These parts are not recommended for new designs. In production to support ongoing production programs only."  Added watermark in PDF stating "Not recommended for new designs. In production to support ongoing production programs only."  Added Contents on page 2. |  |  |

© Cypress Semiconductor Corporation, 2006-2009. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems call risk of such use and in doing so indemnifies Cypress against all charges. application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 001-51000 Rev. \*A Revised December 11, 2009

Page 14 of 14

All products and company names mentioned in this document may be the trademarks of their respective holders