# LC<sup>2</sup>MOS Complete, 8-Bit Analog I/O Systems

# AD7569/AD7669

#### **FEATURES**

2 μs ADC with Track/Hold

1 μs DAC with Output Amplifier AD7569, Single DAC Output AD7669, Dual DAC Output

On-Chip Bandgap Reference

Fast Bus Interface

Single or Dual 5 V Supplies

## **GENERAL DESCRIPTION**

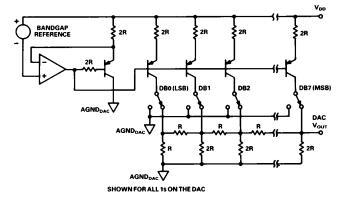

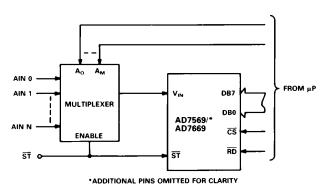

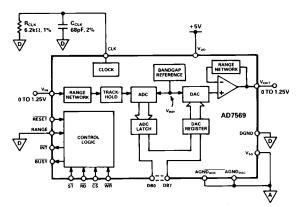

The AD7569/AD7669 is a complete, 8-bit, analog I/O system on a single monolithic chip. The AD7569 contains a high speed successive approximation ADC with 2  $\mu$ s conversion time, a track/hold with 200 kHz bandwidth, a DAC and an output buffer amplifier with 1  $\mu$ s settling time. A temperature-compensated 1.25 V bandgap reference provides a precision reference voltage for the ADC and the DAC. The AD7669 is similar, but contains two DACs with output buffer amplifiers.

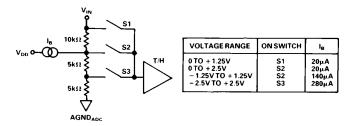

A choice of analog input/output ranges is available. Using a supply voltage of +5 V, input and output ranges of zero to 1.25 V and zero to 2.5 volts may be programmed using the RANGE input pin. Using a  $\pm 5$  V supply, bipolar ranges of  $\pm 1.25$  V or  $\pm 2.5$  V may be programmed.

Digital interfacing is via an 8-bit I/O port and standard microprocessor control lines. Bus interface timing is extremely fast, allowing easy connection to all popular 8-bit microprocessors. A separate start convert line controls the track/hold and ADC to give precise control of the sampling period.

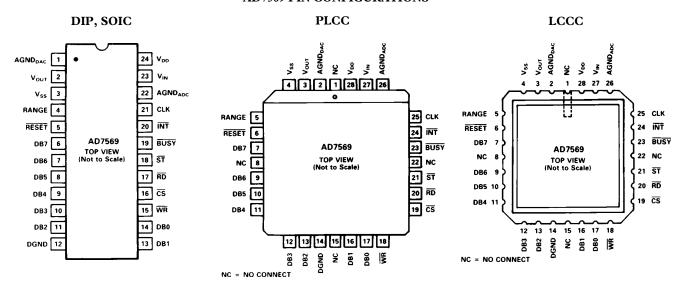

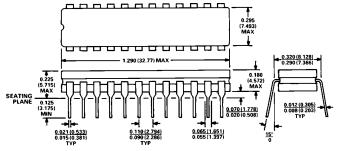

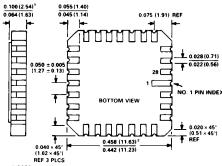

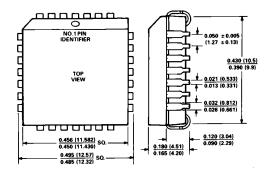

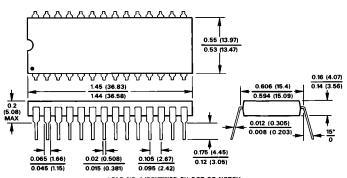

The AD7569/AD7669 is fabricated in Linear-Compatible CMOS (LC<sup>2</sup>MOS), an advanced, mixed technology process combining precision bipolar circuits with low power CMOS logic. The AD7569 is packaged in a 24-pin, 0.3" wide "skinny" DIP, a 24-terminal SOIC and 28-terminal PLCC and LCCC packages. The AD7669 is available in a 28-pin, 0.6" plastic DIP, 28-terminal SOIC and 28-terminal PLCC package.

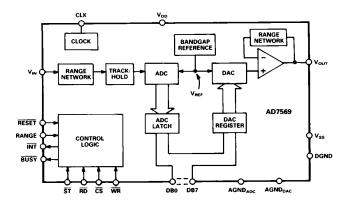

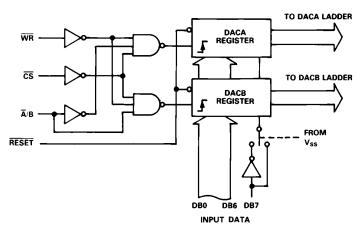

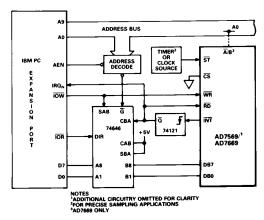

#### AD7569 FUNCTIONAL BLOCK DIAGRAM

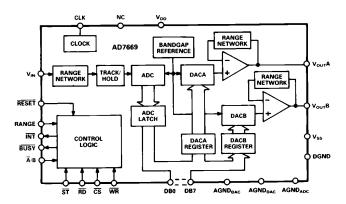

#### AD7669 FUNCTIONAL BLOCK DIAGRAM

#### PRODUCT HIGHLIGHTS

- Complete Analog I/O on a Single Chip.

The AD7569/AD7669 provides everything necessary to interface a microprocessor to the analog world. No external components or user trims are required and the overall accuracy of the system is tightly specified, eliminating the need to calculate error budgets from individual component specifications.

- Dynamic Specifications for DSP Users.

In addition to the traditional ADC and DAC specifications, the AD7569/AD7669 is specified for ac parameters, including signal-to-noise ratio, distortion and input bandwidth.

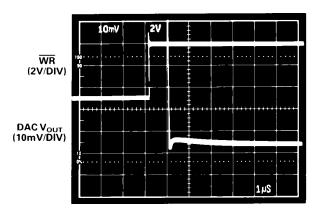

- Fast Microprocessor Interface.

The AD7569/AD7669 has bus interface timing compatible with all modern microprocessors, with bus access and relinquish times less than 75 ns and write pulse width less than 80 ns.

#### REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 World Wide Web Site: http://www.analog.com Fax: 617/326-8703 © Analog Devices, Inc., 1996

$\label{eq:continuous} \begin{array}{l} \textbf{AD7569/AD7669-SPECIFICATIONS} \\ \textbf{DAC SPECIFICATIONS}^1 & (V_{DD}=+5~V~\pm~5\%;~V_{SS}{}^2=\text{RANGE}=\text{AGND}_{DAC}=\text{AGND}_{DAC}=\text{DGND}=0~V;~R_L=2~k\Omega,~C_L=100~pF~to~AGND}_{DAC}\\ \textbf{unless otherwise noted.~All specifications}~T_{MIN}~to~T_{MAX}~unless~otherwise~noted.) \end{array}$

|                                                                                                                               | AD7569<br>J, A Versions <sup>3</sup><br>AD7669 | AD7569<br>K, B | AD7569        | AD7569         |                       |                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------|---------------|----------------|-----------------------|-------------------------------------------------------------------------|

| Parameter                                                                                                                     | J Version                                      | Versions       | S Version     | T Version      | Units                 | Conditions/Comments                                                     |

| STATIC PERFORMANCE                                                                                                            |                                                |                |               |                |                       |                                                                         |

| Resolution <sup>4</sup>                                                                                                       | 8                                              | 8              | 8             | 8              | Bits                  |                                                                         |

| Total Unadjusted Error <sup>5</sup>                                                                                           | ±2                                             | ±2             | ±3            | ±3             | LSB typ               |                                                                         |

| Relative Accuracy <sup>5</sup> Differential Nonlinearity <sup>5</sup>                                                         | ±1<br>±1                                       | ±1/2<br>±3/4   | ±1<br>±1      | ± 1/2<br>± 3/4 | LSB max<br>LSB max    | Guaranteed Monotonic                                                    |

| Unipolar Offset Error                                                                                                         | 1                                              | ± 5/4          | <sup>±1</sup> | ± 3/4          | LSB max               | DAC data is all 0s; $V_{SS} = 0 \text{ V}$                              |

| @ +25°C                                                                                                                       | ±2                                             | ±1.5           | ±2            | ±1.5           | LSB max               | Typical tempco is 10 $\mu$ V/°C for +1.25 V range                       |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                          | ±2.5                                           | ±2             | ±2.5          | ±2             | LSB max               | - Strong started to the few court of the sample                         |

| Bipolar Zero Offset Error                                                                                                     |                                                |                |               |                |                       | DAC data is all 0s; $V_{SS} = -5 \text{ V}$                             |

| @ +25°C                                                                                                                       | ±2                                             | ±15            | ±2            | ±1.5           | LSB max               | Typical tempco is 20 μV/°C for ±1.25 V range                            |

| $T_{MIN}$ to $T_{MAX}$                                                                                                        | ±2.5                                           | ±2             | ±2.5          | ±2             | LSB max               |                                                                         |

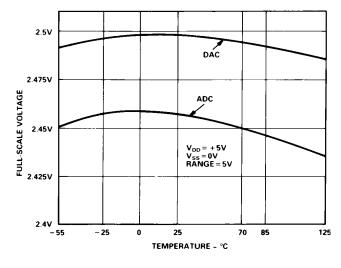

| Full-Scale Error <sup>6</sup> (AD7569 Only)                                                                                   |                                                |                |               |                | T 0D                  | $V_{DD} = 5 \text{ V}$                                                  |

| @ +25°C                                                                                                                       | ±2                                             | ±1             | ±2            | ±1             | LSB max               |                                                                         |

| T <sub>MIN</sub> to T <sub>MAX</sub><br>Full-Scale Error <sup>6</sup> (AD7669 Only)                                           | ±3                                             | ±2             | ±4            | ±3             | LSB max               | V - 5 V                                                                 |

| (AD7009 Only)                                                                                                                 | ±3                                             |                |               |                | LSB max               | $V_{\rm DD} = 5 \text{ V}$                                              |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                          | ±4.5                                           |                |               |                | LSB max               |                                                                         |

| DACA/DACB Full-Scale Error Match <sup>6</sup>                                                                                 | 1.5                                            |                |               |                | LOD Max               |                                                                         |

| (AD7669 Only)                                                                                                                 | ±2.5                                           |                |               |                | LSB max               | $V_{DD} = 5 \text{ V}$                                                  |

| $\Delta$ Full Scale/ $\Delta$ V <sub>DD</sub> , T <sub>A</sub> = +25°C                                                        | 0.5                                            | 0.5            | 0.5           | 0.5            | LSB max               | $V_{OUT} = 2.5 \text{ V}; \Delta V_{DD} = \pm 5\%$                      |

| $\Delta$ Full Scale/ $\Delta$ V <sub>SS</sub> , T <sub>A</sub> = +25°C                                                        | 0.5                                            | 0.5            | 0.5           | 0.5            | LSB max               | $V_{OUT} = -2.5 \text{ V}; \Delta V_{SS} = \pm 5\%$                     |

| Load Regulation at Full Scale                                                                                                 | 0.2                                            | 0.2            | 0.2           | 0.2            | LSB max               | $R_L = 2 k\Omega \text{ to } ^{\circ}/\text{C}$                         |

| DYNAMIC PERFORMANCE                                                                                                           |                                                |                |               |                |                       |                                                                         |

| Signal-to-Noise Ratio <sup>5</sup> (SNR)                                                                                      | 44                                             | 46             | 44            | 46             | dB min                | $V_{OUT}$ = 20 kHz full-scale sine wave with $f_{SAMPLING}$ = 400 kHz   |

| Total Harmonic Distortion (THD)                                                                                               | 48                                             | 48             | 48            | 48             | dB max                | $V_{OUT}$ = 20 kHz full-scale sine wave with $f_{SAMPLING}$ = 400 kHz   |

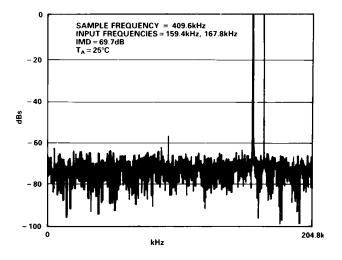

| Intermodulation Distortion <sup>5</sup> (IMD)                                                                                 | 55                                             | 55             | 55            | 55             | dB typ                | fa = 18.4 kHz, fb = 14.5 kHz with f <sub>SAMPLING</sub> = 400 kHz       |

| ANALOG OUTPUT                                                                                                                 |                                                |                |               |                |                       |                                                                         |

| Output Voltage Ranges                                                                                                         |                                                |                |               |                |                       |                                                                         |

| Unipolar                                                                                                                      | 0 to +1.25/2.5                                 |                |               |                | Volts                 | $V_{DD} = +5 \text{ V}, V_{SS} = 0 \text{ V}$                           |

| Bipolar                                                                                                                       | ±1.25/±2.5                                     |                |               |                | Volts                 | $V_{DD} = +5 \text{ V}, V_{SS} = -5 \text{ V}$                          |

| LOGIC INPUTS                                                                                                                  |                                                |                |               |                |                       |                                                                         |

| $\overline{\text{CS}}$ , $\overline{\text{X}}/\text{B}$ , $\overline{\text{WR}}$ , RANGE, $\overline{\text{RESET}}$ , DB0–DB7 |                                                |                |               |                |                       |                                                                         |

| Input Low Voltage, V <sub>INL</sub>                                                                                           | 0.8                                            | 0.8            | 0.8           | 0.8            | V max<br>V min        |                                                                         |

| Input High Voltage, V <sub>INH</sub> Input Leakage Current                                                                    | 2.4                                            | 10             | 10            | 10             | ν min<br>μA max       | $V_{IN} = 0$ to $V_{DD}$                                                |

| Input Capacitance <sup>7</sup>                                                                                                | 10                                             | 10             | 10            | 10             | pF max                | V <sub>IN</sub> = 0 to V <sub>DD</sub>                                  |

| DB0-DB7                                                                                                                       |                                                | 10             | 10            | 10             | pr mux                |                                                                         |

| Input Coding (Single Supply)                                                                                                  |                                                |                | Binary        |                |                       |                                                                         |

| Input Coding (Dual Supply)                                                                                                    |                                                |                | 2s Complem    | ent            |                       |                                                                         |

| AC CHARACTERISTICS <sup>7</sup>                                                                                               |                                                |                |               |                |                       |                                                                         |

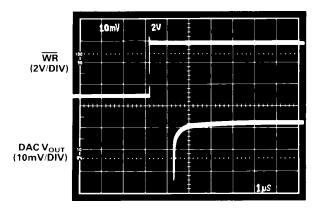

| Voltage Output Settling Time                                                                                                  |                                                |                |               |                |                       | Settling time to within $\pm 1/2$ LSB of final value                    |

| Positive Full-Scale Change                                                                                                    | 2                                              | 2              | 2             | 2              | μs max                | Typically 1 μs                                                          |

| Negative Full-Scale Change (Single Supply)                                                                                    | 4                                              | 4              | 4             | 4              | μs max                | Typically 2 μs                                                          |

| Negative Full-Scale Change (Dual Supply)                                                                                      | 2                                              | 2              | 2             | 2              | μs max                | Typically 1 μs                                                          |

| Digital-to-Analog Glitch Impulse <sup>5</sup>                                                                                 | 15                                             | 15             | 15            | 15             | nV secs typ           |                                                                         |

| Digital Feedthrough <sup>5</sup><br>V <sub>IN</sub> to V <sub>OUT</sub> Isolation                                             | 1 60                                           | 1 60           | 1 60          | 1 60           | nV secs typ<br>dB typ | $V_{IN} = \pm 2.5 \text{ V}, 50 \text{ kHz Sine Wave}$                  |

| DAC to DAC Crosstalk <sup>5</sup> (AD7669 Only)                                                                               | 1                                              | 00             | 100           | 100            | nV secs typ           | V <sub>IN</sub> = ±2.5 V, 50 KHz Sine wave                              |

| DACA to DACB Isolation <sup>5</sup> (AD7669 Only)                                                                             | -70                                            |                |               |                | dB max                |                                                                         |

| POWER REQUIREMENTS                                                                                                            |                                                |                |               |                |                       |                                                                         |

| V <sub>DD</sub> Range                                                                                                         | 4.75/5.25                                      | 4.75/5.25      | 4.75/5.25     | 4.75/5.25      | V min/V max           | For Specified Performance                                               |

| V <sub>SS</sub> Range (Dual Supplies)                                                                                         | -4.75/-5.25                                    | -4.75/-5.25    | -4.75/-5.25   | -4.75/-5.25    | V min/V max           | Specified Performance also applies to $V_{SS} = 0 \text{ V}$            |

|                                                                                                                               |                                                |                |               |                |                       | for unipolar ranges.                                                    |

| $I_{ m DD}$                                                                                                                   |                                                |                |               |                |                       | $V_{OUT} = V_{IN} = 2.5 \text{ V}$ ; Logic Inputs = 2.4 V; CLK = 0.8 V  |

| (AD7569)                                                                                                                      | 13                                             | 13             | 13            | 13             | mA max                | Output unloaded                                                         |

| (AD7669)                                                                                                                      | 18                                             |                | 1             |                | mA max                | Outputs unloaded                                                        |

| I <sub>SS</sub> (Dual Supplies)                                                                                               | 1,                                             |                | 1.            | ,              | l                     | $V_{OUT} = V_{IN} = -2.5 \text{ V}$ ; Logic Inputs = 2.4 V; CLK = 0.8 V |

| (AD7569)                                                                                                                      | 4 6                                            | 4              | 4             | 4              | mA max<br>mA max      | Output unloaded Outputs unloaded                                        |

| (AD7669)                                                                                                                      | 0                                              |                |               |                | mrx max               | Outputs diffoaccu                                                       |

| DAC/ADC MATCHING                                                                                                              |                                                |                |               |                |                       | V . v V                                                                 |

| Gain Matching <sup>6</sup>                                                                                                    | ,                                              | ,              | ,             | ,              | 0/ trun               | $V_{\rm IN}$ to $V_{\rm OUT}$ match with $V_{\rm IN} = \pm 2.5$ V,      |

| @ +25°C                                                                                                                       | 1                                              | 1              | 1             | 1              | % typ                 | 20 kHz sine wave                                                        |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                          | 1                                              | 1              | 1             | 1              | % typ                 |                                                                         |

| NOTES                                                                                                                         |                                                |                |               |                |                       |                                                                         |

Specifications subject to change without notice.

<sup>&</sup>lt;sup>1</sup>Specifications apply to both DACs in the AD7669. V<sub>OUT</sub> applies to both V<sub>OUT</sub>A and V<sub>OUT</sub>B of the AD7669.

<sup>2</sup>Except where noted, specifications apply for all output ranges including bipolar ranges with dual supply operation.

<sup>3</sup>Temperature ranges as follows: J, K versions; 0°C to +70°C

A, B versions;  $-40^{\circ}$ C to  $+85^{\circ}$ C S, T versions;  $-55^{\circ}$ C to  $+125^{\circ}$ C T versions;  $-55^{\circ}$ C to  $+125^{\circ}$ C V and  $\pm 1.25$  V ranges and  $\pm 1.2$

<sup>&</sup>lt;sup>5</sup>See Terminology.

<sup>6</sup>Includes internal voltage reference error and is calculated after offset error has been adjusted out. Ideal unipolar full-scale voltage is (FS – 1 LSB); ideal bipolar positive full-scale voltage is (FS/2 – 1 LSB) and ideal bipolar negative full-scale voltage is -FS/2.

7Sample tested at +25°C to ensure compliance.

$\begin{array}{ll} \textbf{ADC SPECIFICATIONS} & (\textbf{V}_{DD} = +5 \ \textbf{V} \pm 5\%; \textbf{V}_{SS}{}^{1} = \textbf{RANGE} = \textbf{AGND}_{DAC} = \textbf{DGND} = \textbf{0} \ \textbf{V}; \textbf{f}_{CLK} = 5 \ \textbf{MHz} \ \textbf{external unless otherwise noted.} \\ \textbf{Specifications T}_{MIN} \ \textbf{to T}_{MAX} \ \textbf{unless otherwise noted.} \\ \textbf{Specifications apply to Mode 1 interface.} \\ \end{array}$

|                                                                        | AD7569                                            | 17.74                      |                     |                     |                                         |                                                                                        |

|------------------------------------------------------------------------|---------------------------------------------------|----------------------------|---------------------|---------------------|-----------------------------------------|----------------------------------------------------------------------------------------|

| Parameter                                                              | J, A Versions <sup>3</sup><br>AD7669<br>J Version | AD7569<br>K, B<br>Versions | AD7569<br>S Version | AD7569<br>T Version | Units                                   | Conditions/Comments                                                                    |

| DC ACCURACY                                                            |                                                   |                            |                     |                     |                                         |                                                                                        |

| Resolution <sup>3</sup>                                                | 8                                                 | 8                          | 8                   | 8                   | Bits                                    |                                                                                        |

| Total Unadjusted Error <sup>4</sup>                                    | ±3                                                | ±3                         | ±4                  | $\pm 4$             | LSB typ                                 |                                                                                        |

| Relative Accuracy <sup>4</sup>                                         | ±1                                                | ±1/2                       | ±1                  | $\pm 1/2$           | LSB max                                 |                                                                                        |

| Differential Nonlinearity <sup>4</sup>                                 | ±1                                                | ±3/4                       | ±1                  | $\pm 3/4$           | LSB max                                 | No Missing Codes                                                                       |

| Unipolar Offset Error                                                  |                                                   |                            |                     |                     |                                         | Typical tempco is 10 $\mu$ V/°C for +1.25 V range; $V_{SS} = 0$ V                      |

| @ +25°C                                                                | ±2                                                | ±1.5                       | ±2                  | ±1.5                | LSB max                                 |                                                                                        |

| $T_{MIN}$ to $T_{MAX}$                                                 | ±3                                                | ±2.5                       | ±3                  | ±2.5                | LSB max                                 |                                                                                        |

| Bipolar Zero Offset Error                                              |                                                   |                            |                     |                     |                                         | Typical tempco is 20 $\mu$ V/°C for + 1.25 V range; $V_{SS} = -5$ V                    |

| @ +25°C                                                                | ±3                                                | ±2.5                       | ±3                  | ±2.5                | LSB max                                 |                                                                                        |

| $T_{MIN}$ to $T_{MAX}$                                                 | ±3.5                                              | ±3                         | ±4                  | ±3.5                | LSB max                                 |                                                                                        |

| Full-Scale Error <sup>5</sup>                                          |                                                   |                            |                     |                     |                                         | $V_{DD} = 5 \text{ V}$                                                                 |

| @ +25°C                                                                | -4, +0                                            | -4, +0                     | -4, +0              | -4, +0              | LSB max                                 |                                                                                        |

| $T_{MIN}$ to $T_{MAX}$                                                 | -5.5, +1.5                                        | -5.5, +1.5                 | -7.5, +2            | -7.5, +2            | LSB max                                 |                                                                                        |

| $\Delta$ Full Scale/ $\Delta$ V <sub>DD</sub> , T <sub>A</sub> = +25°C | 0.5                                               | 0.5                        | 0.5                 | 0.5                 | LSB max                                 | $V_{IN} = +2.5 \text{ V}; \Delta V_{DD} = \pm 5\%$                                     |

| $\Delta$ Full Scale/ $\Delta$ V <sub>SS</sub> , T <sub>A</sub> = +25°C | 0.5                                               | 0.5                        | 0.5                 | 0.5                 | LSB max                                 | $V_{IN} = -2.5 \text{ V}; \Delta V_{SS} = \pm 5\%$                                     |

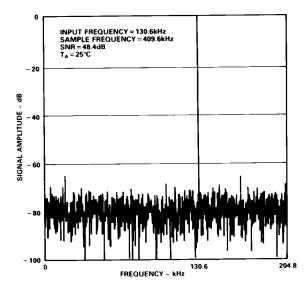

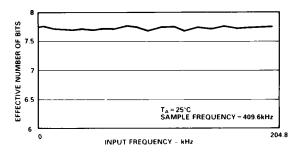

| DYNAMIC PERFORMANCE                                                    |                                                   |                            |                     |                     |                                         |                                                                                        |

| Signal-to-Noise Ratio <sup>4</sup> (SNR)                               | 44                                                | 46                         | 44                  | 45                  | dB min                                  | $V_{IN}$ = 100 kHz full-scale sine wave with $f_{SAMPLING}$ = 400 kHz <sup>6</sup>     |

| Total Harmonic Distortion <sup>4</sup> (THD)                           | 48                                                | 48                         | 48                  | 48                  | dB max                                  | $V_{IN} = 100 \text{ kHz full-scale sine wave with } f_{SAMPLING} = 400 \text{ kHz}^6$ |

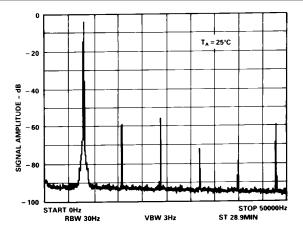

| Intermodulation Distortion <sup>4</sup> (IMD)                          | 60                                                | 60                         | 60                  | 60                  | dB typ                                  | fa = 99 kHz, fb = 96.7 kHz with $f_{SAMPLING}$ = 400 kHz                               |

| Frequency Response                                                     | 0.1                                               | 0.1                        | 0.1                 | 0.1                 | dB typ                                  | $V_{IN} = \pm 2.5 \text{ V}$ , dc to 200 kHz sine wave                                 |

| Track/Hold Acquisition Time <sup>7</sup>                               | 200                                               | 200                        | 300                 | 300                 | ns typ                                  | · IN                                                                                   |

| ANALOG INPUT                                                           |                                                   |                            |                     |                     |                                         |                                                                                        |

| Input Voltage Ranges                                                   |                                                   |                            |                     |                     |                                         |                                                                                        |

| Unipolar                                                               | 0 to +                                            | 1.25/ +2.5                 |                     |                     | Volts                                   | $V_{DD} = +5 \text{ V}; V_{SS} = 0 \text{ V}$                                          |

| Bipolar                                                                | ±1.25                                             |                            |                     |                     | Volts                                   | $V_{DD} = +5 \text{ V}; V_{SS} = -5 \text{ V}$                                         |

| Input Current                                                          | ±300                                              | ±300                       | ±300                | ±300                | μA max                                  | See equivalent circuit Figure 5                                                        |

| Input Capacitance                                                      | 10                                                | 10                         | 10                  | 10                  | pF typ                                  | See equivalent enealt righte 3                                                         |

| LOGIC INPUTS                                                           |                                                   |                            |                     |                     |                                         |                                                                                        |

| CS, RD, ST, CLK, RESET, RANGE                                          |                                                   |                            |                     |                     |                                         |                                                                                        |

| Input Low Voltage, V <sub>INI</sub>                                    | 0.8                                               | 0.8                        | 0.8                 | 0.8                 | V max                                   |                                                                                        |

| Input High Voltage, V <sub>INH</sub>                                   | 2.4                                               | 2.4                        | 2.4                 | 2.4                 | V min                                   |                                                                                        |

| Input Capacitance <sup>8</sup>                                         | 10                                                | 10                         | 10                  | 10                  | pF max                                  |                                                                                        |

| CS, RD, ST, RANGE, RESET                                               |                                                   | 10                         |                     |                     | Pr mun                                  |                                                                                        |

| Input Leakage Current                                                  | 10                                                | 10                         | 10                  | 10                  | μA max                                  | $V_{IN} = 0$ to $V_{DD}$                                                               |

| CLK                                                                    |                                                   |                            |                     |                     | , , , , , , , , , , , , , , , , , , , , | · IIV · · · · · · · · · · · · · · · · ·                                                |

| Input Current                                                          |                                                   |                            |                     |                     |                                         |                                                                                        |

| I <sub>INL</sub>                                                       | -1.6                                              | -1.6                       | -1.6                | -1.6                | mA max                                  | $V_{IN} = 0 \text{ V}$                                                                 |

| I <sub>INH</sub>                                                       | 40                                                | 40                         | 40                  | 40                  | μA max                                  | $V_{\rm IN} = V_{\rm DD}$                                                              |

| LOGIC OUTPUTS                                                          |                                                   |                            |                     |                     |                                         |                                                                                        |

| DB0-DB7, INT, BUSY                                                     |                                                   |                            |                     |                     |                                         |                                                                                        |

| V <sub>OL</sub> , Output Low Voltage                                   | 0.4                                               | 0.4                        | 0.4                 | 0.4                 | V max                                   | $I_{SINK} = 1.6 \text{ mA}$                                                            |

| V <sub>OH</sub> , Output High Voltage                                  | 4.0                                               | 4.0                        | 4.0                 | 4.0                 | V min                                   | I <sub>SOURCE</sub> = 200 μA                                                           |

| DB0-DB7                                                                |                                                   |                            |                     |                     |                                         | -500KCE p                                                                              |

| Floating State Leakage Current                                         | 10                                                | 10                         | 10                  | 10                  | μA max                                  |                                                                                        |

| Floating State Output Capacitance <sup>8</sup>                         | 10                                                | 10                         | 10                  | 10                  | pF max                                  |                                                                                        |

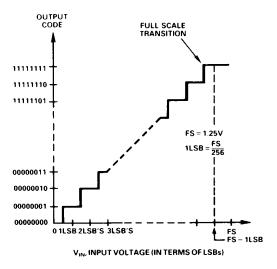

| Output Coding (Single Supply)                                          |                                                   | Binary                     |                     |                     |                                         |                                                                                        |

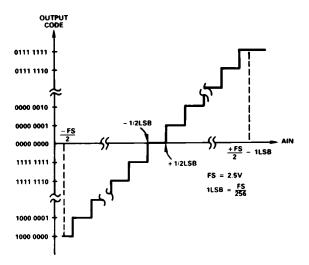

| Output Coding (Dual Supply)                                            |                                                   |                            | nplement            |                     |                                         |                                                                                        |

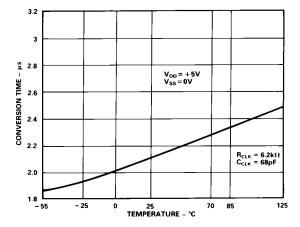

| CONVERSION TIME                                                        |                                                   |                            |                     |                     |                                         |                                                                                        |

| With External Clock                                                    | 2                                                 | 2                          | 2                   | 2                   | us max                                  | $f_{CLK} = 5 \text{ MHz}$                                                              |

| With Internal Clock, T <sub>A</sub> = +25°C                            | 1.6                                               | 1.6                        | 1.6                 | 1.6                 | us min                                  | Using recommended clock components shown in Figure 21.                                 |

|                                                                        | 2.6                                               | 2.6                        | 2.6                 | 2.6                 | us max                                  | Clock frequency can be adjusted by varying R <sub>CLK</sub> .                          |

|                                                                        |                                                   |                            |                     |                     |                                         |                                                                                        |

| POWER REQUIREMENTS                                                     | Acna                                              | DAC Specifi                | cations             |                     | I                                       | I                                                                                      |

| 10 " LK KLQUIKLINEN IO                                                 | l As per                                          | Dire opecili               | Cations             |                     |                                         |                                                                                        |

Except where noted, specifications apply for all ranges including bipolar ranges with dual supply operation.

2 Temperature ranges are as follows: J, K versions; 0°C to +70°C

A, B versions; -40°C to +85°C

S, T versions; -55°C to +125°C

3 1 LSB = 4.88 mV for 0 V to +1.25 V range, 9.76 mV for 0 V to +2.5 V and ±1.25 V ranges and 19.5 mV for +2.5 V range.

<sup>\*\*</sup>See Terminology.

5 Includes internal voltage reference error and is calculated after offset error has been adjusted out. Ideal unipolar last code transition occurs at (FS – 3/2 LSB). Ideal bipolar last code transition occurs at (FS/2 – 3/2 LSB).

<sup>&</sup>lt;sup>6</sup>Exact frequencies are 101 kHz and 384 kHz to avoid harmonics coinciding with sampling frequency.

<sup>7</sup>Rising edge of <u>BUSY</u> to falling edge of <u>ST</u>. The time given refers to the acquisition time, which gives a 3 dB degradation in SNR from the tested figure.

<sup>8</sup>Sample tested at +25°C to ensure compliance.

Specifications subject to change without notice.

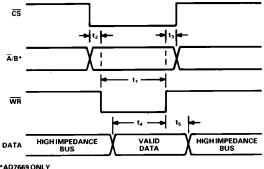

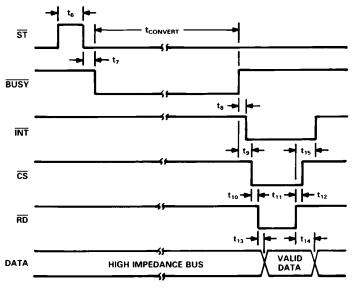

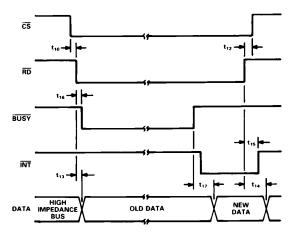

## AD7569/AD7669—TIMING CHARACTERISTICS<sup>1</sup> (See Figures 8, 10, 12; $V_{DD} = 5 \text{ V} \pm 5\%$ ; $V_{SS} = 0 \text{ V}$ or $-5 \text{ V} \pm 5\%$ )

| Parameter              | Limit at<br>25°C (All Grades) | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> (J, K, A, B Grades) | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> (S, T Grades) | Units  | Test Conditions/Comments                                                                     |

|------------------------|-------------------------------|------------------------------------------------------------------|------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------|

| DAC Timing             |                               |                                                                  |                                                            |        |                                                                                              |

| $t_1$                  | 80                            | 80                                                               | 90                                                         | ns min | WR Pulse Width                                                                               |

| $t_2$                  | 0                             | 0                                                                | 0                                                          | ns min | $\overline{\text{CS}}$ , $\overline{\text{A}}/\text{B}$ to $\overline{\text{WR}}$ Setup Time |

| $t_3$                  | 0                             | 0                                                                | 0                                                          | ns min | $\overline{\text{CS}}$ , $\overline{\text{A}}/\text{B}$ to $\overline{\text{WR}}$ Hold Time  |

| $t_4$                  | 60                            | 70                                                               | 80                                                         | ns min | Data Valid to WR Setup Time                                                                  |

| t <sub>5</sub>         | 10                            | 10                                                               | 10                                                         | ns min | Data Valid to WR Hold Time                                                                   |

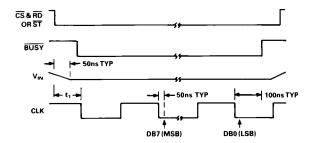

| ADC Timing             |                               |                                                                  |                                                            |        |                                                                                              |

| $t_6$                  | 50                            | 50                                                               | 50                                                         | ns min | ST Pulse Width                                                                               |

| t <sub>7</sub>         | 110                           | 130                                                              | 150                                                        | ns max | ST to BUSY Delay                                                                             |

| $t_8$                  | 20                            | 30                                                               | 30                                                         | ns max | BUSY to INT Delay                                                                            |

| t <sub>9</sub>         | 0                             | 0                                                                | 0                                                          | ns min | BUSY to CS Delay                                                                             |

| t <sub>10</sub>        | 0                             | 0                                                                | 0                                                          | ns min | $\overline{\text{CS}}$ to $\overline{\text{RD}}$ Setup Time                                  |

| t <sub>11</sub>        | 60                            | 75                                                               | 90                                                         | ns min | $\overline{\text{RD}}$ Pulse Width Determined by $t_{13}$ .                                  |

| $t_{12}$               | 0                             | 0                                                                | 0                                                          | ns min | $\overline{\text{CS}}$ to $\overline{\text{RD}}$ Hold Time                                   |

| $t_{12} \\ t_{13}^{2}$ | 60                            | 75                                                               | 90                                                         | ns max | Data Access Time after $\overline{RD}$ ; $C_L = 20 \text{ pF}$                               |

|                        | 95                            | 120                                                              | 135                                                        | ns max | Data Access Time after $\overline{RD}$ ; $C_L = 100 \text{ pF}$                              |

| $t_{14}^{3}$           | 10                            | 10                                                               | 10                                                         | ns min | Bus Relinquish Time after $\overline{\text{RD}}$                                             |

|                        | 60                            | 75                                                               | 85                                                         | ns max |                                                                                              |

| t <sub>15</sub>        | 65                            | 75                                                               | 85                                                         | ns max | $\overline{\text{RD}}$ to $\overline{\text{INT}}$ Delay                                      |

| t <sub>16</sub>        | 120                           | 140                                                              | 160                                                        | ns max | RD to BUSY Delay                                                                             |

| $t_{17}^{2}$           | 60                            | 75                                                               | 90                                                         | ns max | Data Valid Time after $\overline{BUSY}$ ; $C_L = 20 \text{ pF}$                              |

|                        | 90                            | 115                                                              | 135                                                        | ns max | Data Valid Time after $\overline{BUSY}$ ; $C_L = 100 \text{ pF}$                             |

#### NOTES

Specifications subject to change without notice.

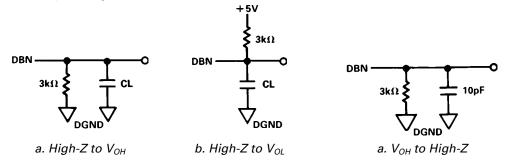

Figure 1. Load Circuits for Data Access Time Test

Figure 2. Load Circuits for Bus Relinquish Time Test

DBN

b. Vol to High-Z

## ABSOLUTE MAXIMUM RATINGS

| 112002012111111111111111111111111111111                            |

|--------------------------------------------------------------------|

| $V_{DD}$ to $AGND_{DAC}$ or $AGND_{ADC}$ 0.3 V, +7 V               |

| $V_{DD}$ to DGND $\dots\dots$ –0.3 V, +7 V                         |

| $V_{DD}$ to $V_{SS}$ 0.3 V, +14 V                                  |

| AGND DAC or AGND ADC to DGND $$ 0.3 V, VDD + 0.3 V                 |

| $AGND_{DAC}$ to $AGND_{ADC}$                                       |

| Logic Voltage to DGND0.3 V, $V_{DD}$ + 0.3 V                       |

| CLK Input Voltage to DGND0.3 V, $V_{DD}$ + 0.3 V                   |

| $V_{OUT}$ ( $V_{OUT}A$ , $V_{OUT}B$ ) to                           |

| $AGND_{DAC}^{1}$ $V_{SS} - 0.3 \text{ V}, V_{DD} + 0.3 \text{ V}$  |

| $V_{IN}$ to AGND <sub>ADC</sub> $V_{SS}$ – 0.3 V, $V_{DD}$ + 0.3 V |

| NOTE                                                               |

$^1$ Output may be shorted to any voltage in the range  $V_{SS}$  to  $V_{DD}$  provided that the power dissipation of the package is not exceeded. Typical short circuit current for a short to AGND or  $V_{SS}$  is 50 mA.

| Power Dissipation (Any Package) to +75°C 450 mW |

|-------------------------------------------------|

| Derates above 75°C by 6 mW/°C                   |

| Operating Temperature Range                     |

| Commercial (J, K)                               |

| Industrial (A, B)40°C to +85°C                  |

| Extended (S, T)55°C to +125°C                   |

| Storage Temperature Range65°C to +150°C         |

| Lead Temperature (Soldering, 10 secs) +300°C    |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7569/AD7669 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>1</sup>Sample tested at  $+25^{\circ}$ C to ensure compliance. All input control signals are specified with  $t_R = t_F = 5$  ns (10% to 90% of +5 V) and timed from a voltage level of 1.6 V.

<sup>&</sup>lt;sup>2</sup>t<sub>13</sub> and t<sub>17</sub> are measured with the load circuits of Figure 1 and defined as the time required for an output to cross either 0.8 V or 2.4 V.

$<sup>^{3}</sup>t_{14}$  is defined as the time required for the data line to change 0.5 V when loaded with the circuit of Figure 2.

#### NOTE:

The term DAC (Digital-to-Analog Converter) throughout the data sheet applies equally to the dual DACs in the AD7669 as well as to the single DAC of the AD7569 unless otherwise stated. It follows that the term  $V_{\rm OUT}$  applies to both  $V_{\rm OUT}A$  and  $V_{\rm OUT}B$  of the AD7669 also.

#### **TERMINOLOGY**

#### **Total Unadjusted Error**

Total unadjusted error is a comprehensive specification that includes internal voltage reference error, relative accuracy, gain and offset errors.

#### Relative Accuracy (DAC)

Relative Accuracy or endpoint nonlinearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after allowing for offset and gain errors. For the bipolar output ranges, the endpoints of the DAC transfer function are defined as those voltages that correspond to negative full-scale and positive full-scale codes. For the unipolar output ranges, the endpoints are code 1 and code 255. Code 1 is chosen because the amplifier is now working in single supply and, in cases where the true offset of the amplifier is negative, it cannot be seen at code 0. If the relative accuracy were calculated between code 0 and code 255, the "negative offset" would appear as a linearity error. If the offset is negative and less than 1 LSB, it will appear at code 1, and hence the true linearity of the converter is seen between code 1 and code 255.

#### Relative Accuracy (ADC)

Relative Accuracy is the deviation of the ADC's actual code transition points from a straight line drawn between the endpoints of the ADC transfer function. For the bipolar input ranges, these points are the measured, negative, full-scale transition point and the measured, positive, full-scale transition point. For the unipolar ranges, the straight line is drawn between the measured first LSB transition point and the measured full-scale transition point.

#### **Differential Nonlinearity**

Differential Nonlinearity is the difference between the measured change and an ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB max ensures monotonicity (DAC) or no missed codes (ADC). A differential nonlinearity of  $\pm 3/4$  LSB max ensures that the minimum step size (DAC) or code width (ADC) is 1/4 LSB, and the maximum step size or code width is 3/4 LSB.

#### Digital-to-Analog Glitch Impulse

Digital-to-Analog Glitch Impulse is the impulse injected into the analog output when the digital inputs change state with the DAC selected. It is normally specified as the area of the glitch in nV secs and is measured when the digital input code is changed by 1 LSB at the major carry transition.

#### Digital Feedthrough

Digital Feedthrough is also a measure of the impulse injected to the analog output from the digital inputs, but is measured when the DAC is not selected. It is essentially feedthrough across the die and package. It is also a measure of the glitch impulse transferred to the analog output when data is read from the internal ADC. It is specified in nV secs and is measured with  $\overline{WR}$  high and a digital code change from all 0s to all 1s.

#### DAC-to-DAC Crosstalk (AD7669 Only)

The glitch energy transferred to the output of one DAC due to an update at the output of the second DAC. The figure given is the worst case and is expressed in nV secs. It is measured with an update voltage of full scale.

#### DAC-to-DAC Isolation (AD7669 Only)

DAC-to-DAC Isolation is the proportion of a digitized sine wave from the output of one DAC, which appears at the output of the second DAC (loaded with all 1s). The figure given is the worst case for the second DAC output and is expressed as a ratio in dBs. It is measured with a digitized sine wave (f<sub>SAMPLING</sub> = 100 kHz) of 20 kHz at 2.5 V pk-pk.

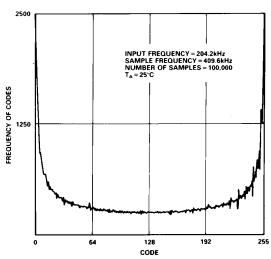

#### Signal-to-Noise Ratio

Signal-to-Noise Ratio (SNR) is the measured signal to noise at the output of the converter. The signal is the rms magnitude of the fundamental. Noise is the rms sum of all the nonfundamental signals (excluding dc) up to half the sampling frequency. SNR is dependent on the number of quantization levels used in the digitization process; the more levels, the smaller the quantization noise. The theoretical SNR for a sine wave is given by

$$SNR = (6.02N + 1.76) dB$$

where N is the number of bits. Thus for an ideal 8-bit converter, SNR = 50 dB.

#### **Harmonic Distortion**

Harmonic Distortion is the ratio of the rms sum of harmonics to the fundamental. For the AD7569/AD7669, Total Harmonic Distortion (THD) is defined as

$$20 \log \sqrt{\frac{{V_2}^2 + {V_3}^2 + {V_4}^2 + {V_5}^2 + {V_6}^2}{V_1}}$$

where  $V_1$  is the rms amplitude of the fundamental and  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$  and  $V_6$  are the rms amplitudes of the individual harmonics.

#### **Intermodulation Distortion**

With inputs consisting of sine waves at two frequencies, fa and fb, any active device with nonlinearities will create distortion products, of order (m + n), at sum and difference frequencies of mfa  $\pm$  nfb where m, n = 0, 1, 2, 3,... . Intermodulation terms are those for which m or n is not equal to zero. For example, the second order terms include (fa + fb) and (fa - fb) and the third order terms include (2fa + fb), (2fa - fb), (fa + 2fb) and (fa - 2fb).

#### **AD7569 PIN CONFIGURATIONS**

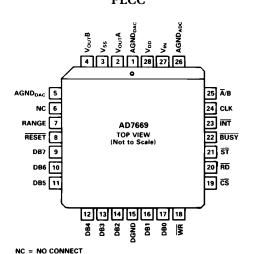

#### **AD7669 PIN CONFIGURATIONS**

#### DIP, SOIC

## PLCC

**ORDERING GUIDE**

| Model        | Temperature<br>Range | Relative<br>Accuracy<br>T <sub>MIN</sub> -T <sub>MAX</sub> | Package<br>Option <sup>1</sup> |

|--------------|----------------------|------------------------------------------------------------|--------------------------------|

| AD7569JN     | 0°C to +70°C         | ±1 LSB                                                     | N-24                           |

| AD7569JR     | 0°C to +70°C         | ±1 LSB                                                     | R-24                           |

| AD7569AQ     | −40°C to +85°C       | ±1 LSB                                                     | Q-24                           |

| $AD7569SQ^2$ | −55°C to +125°C      | ±1 LSB                                                     | Q-24                           |

| AD7569BN     | −40°C to +85°C       | ±0.5 LSB                                                   | N-24                           |

| AD7569KN     | 0°C to +70°C         | ±0.5 LSB                                                   | N-24                           |

| AD7569BR     | −40°C to +85°C       | ±0.5 LSB                                                   | R-24                           |

| AD7569BQ     | −40°C to +85°C       | ±0.5 LSB                                                   | Q-24                           |

| $AD7569TQ^2$ | −55°C to +125°C      | ±1/2 LSB                                                   | Q-24                           |

| AD7569JP     | 0°C to +70°C         | ±1 LSB                                                     | P-28A                          |

| $AD7569SE^2$ | −55°C to +125°C      | ±1 LSB                                                     | E-28A                          |

| AD7569KP     | 0°C to +70°C         | ±1/2 LSB                                                   | P-28A                          |

| $AD7569TE^2$ | −55°C to +125°C      | ±1/2 LSB                                                   | E-28A                          |

| AD7669AN     | −40°C to +85°C       | ±1 LSB                                                     | N-28                           |

| AD7669JN     | 0°C to +70°C         | ±1 LSB                                                     | N-28                           |

| AD7669JP     | 0°C to +70°C         | ±1 LSB                                                     | P-28A                          |

| AD7669AR     | −40°C to +85°C       | ±1 LSB                                                     | R-28                           |

| AD7669JR     | 0°C to +70°C         | ±1 LSB                                                     | R-28                           |

#### NOTES

<sup>1</sup>E = Leadless Ceramic Chip Carrier; N = Plastic DIP; P = Plastic Leaded Chip Carrier; Q = Cerdip; R = Small Outline SOIC.

<sup>2</sup>To order MIL-STD-883, Class B processed parts, add /883B to part number. Contact your local sales office for military data sheet.

-6- REV. B

#### PIN FUNCTION DESCRIPTION

(Applies to the AD7569 and AD7669 unless otherwise stated.)

| Pin<br>Mnemonic                                                                                                                                                                                                                                                                                                                                                       | Description                                                                                                                                                                                                                                                                            | Pin<br>Mnemonic                                                                                                                                                                                               | Description                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $AGND_{DAC}$                                                                                                                                                                                                                                                                                                                                                          | Analog Ground for the DAC(s). Separate ground return paths are provided for the                                                                                                                                                                                                        | CS                                                                                                                                                                                                            | Chip Select Input (Active Low). The device is selected when this input is active.                                                                                                                                                                                                                     |

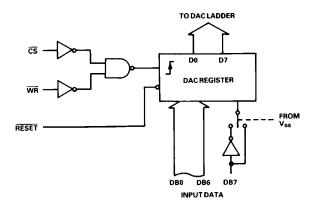

| $V_{OUT} \ (V_{OUT}A, V_{OUT}B)$                                                                                                                                                                                                                                                                                                                                      | DAC(s) and ADC to minimize crosstalk.  Output Voltage. V <sub>OUT</sub> is the buffered output voltage from the AD7569 DAC. V <sub>OUT</sub> A and V <sub>OUT</sub> B are the buffered DAC output voltages from the AD7669. Four different output voltages                             | RD                                                                                                                                                                                                            | READ Input (Active Low). This input must be active to access data from the part. In the Mode 2 interface, $\overline{\text{RD}}$ going low starts conversion. It is used in conjunction with the $\overline{\text{CS}}$ input (see Digital Interface Section).                                        |

| $V_{SS}$                                                                                                                                                                                                                                                                                                                                                              | age ranges can be achieved (see Table I).  Negative Supply Voltage (-5 V for dual supply or 0 V for single supply). This pin is also used with the RANGE pin to select the different input/output ranges and changes the data format from binary (V <sub>SS</sub> = 0 V) to 2s comple- | ST<br>BUSY                                                                                                                                                                                                    | Start Conversion (Edge triggered). This is used when precise sampling is required. The falling edge of $\overline{ST}$ starts conversion and drives $\overline{BUSY}$ low. The $\overline{ST}$ signal is not gated with $\overline{CS}$ .  BUSY Status Output (Active Low). When                      |

| RANGE                                                                                                                                                                                                                                                                                                                                                                 | ment ( $V_{SS} = -5$ V) (see Table I).<br>Range Selection Input. This is used with the $V_{SS}$ input to select the different ranges as per Table I. The range selected applies to both                                                                                                |                                                                                                                                                                                                               | this pin is active, the ADC is performing a conversion. The input signal is held prior to the falling edge of BUSY (see Digital Interface Section).                                                                                                                                                   |

| RESET                                                                                                                                                                                                                                                                                                                                                                 | the analog input voltage of the ADC and the output voltage from the DAC(s).  Reset Input (Active Low). This is an asynchronous system reset that clears the DAC register(s) to all 0s and clears the INT line of the ADC (i.e., makes the ADC ready for new                            | ĪNT Ā/B (AD7669                                                                                                                                                                                               | INTERRUPT Output (Active Low). INT going low indicates that the conversion is complete. INT goes high on the rising edge of $\overline{CS}$ or $\overline{RD}$ and is also set high by a low pulse on $\overline{RESET}$ (see Digital Interface Section).  DAC Select Input. This input selects which |

| conversion). In unipolar operation, this input sets the output voltage to 0 V; in bipolar operation, it sets the output to negative full scale.                                                                                                                                                                                                                       | Only)                                                                                                                                                                                                                                                                                  | DAC register data is written to under control of $\overline{CS}$ and $\overline{WR}$ . With this input low, data is written to the DACA register; with this input high, data is written to the DACB register. |                                                                                                                                                                                                                                                                                                       |

| DB7                                                                                                                                                                                                                                                                                                                                                                   | Data Bit 7. Most Significant Bit (MSB).                                                                                                                                                                                                                                                | CLK                                                                                                                                                                                                           | A TTL compatible clock signal may be used                                                                                                                                                                                                                                                             |

| DB6-DB2                                                                                                                                                                                                                                                                                                                                                               | Data Bit 6 to Data Bit 2.                                                                                                                                                                                                                                                              |                                                                                                                                                                                                               | to determine the ADC conversion time. Inte                                                                                                                                                                                                                                                            |

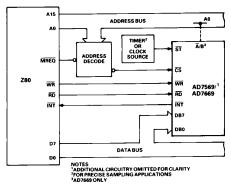

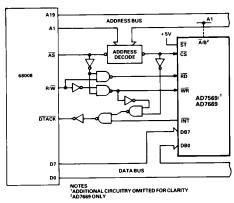

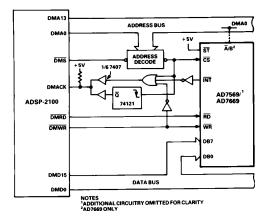

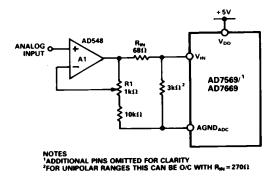

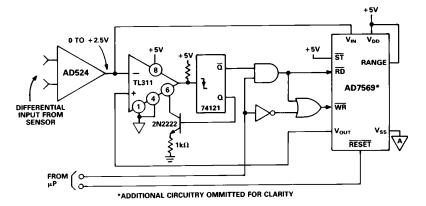

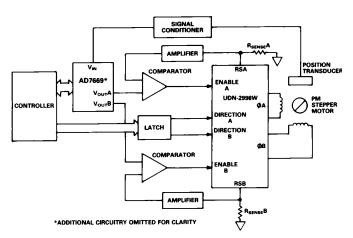

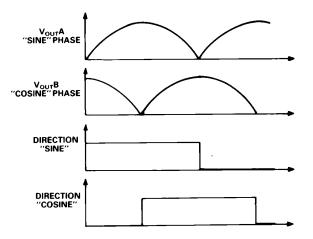

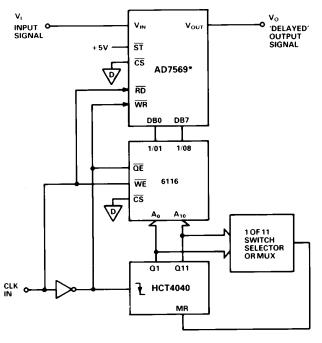

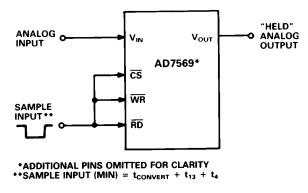

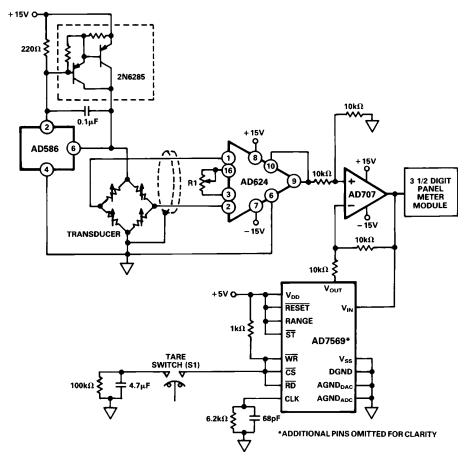

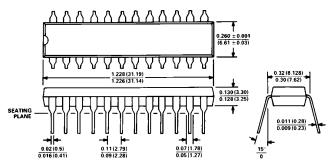

| DGND<br>DB1                                                                                                                                                                                                                                                                                                                                                           | Digital Ground.                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                               | a resistor and capacitor to ground.                                                                                                                                                                                                                                                                   |