# Intel<sup>®</sup> IXP28XX Network Processors

**Hardware Design Guide**

August 2005

Order Number: 309192-002US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel and Intel Xscale are registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2005, Intel Corporation. All Rights Reserved.

| 1 | Introd     | uction     |                                                                                     | 11 |

|---|------------|------------|-------------------------------------------------------------------------------------|----|

| • |            |            |                                                                                     |    |

|   | 1.1<br>1.2 |            | Overviewuide                                                                        |    |

|   | 1.2        |            | ypographical Conventions                                                            |    |

|   |            |            | Acronyms and Terminology                                                            |    |

|   | 1.3        |            | Documentation                                                                       |    |

|   | 1.4        |            | ng Intel®                                                                           |    |

| 2 |            |            | and Requirements                                                                    |    |

| _ | 2.1        | •          | atings                                                                              |    |

|   | 2.1        |            | oltage Power-up Sequence                                                            |    |

|   | 2.2        |            | Sequence for 1.4 / 1.0 GHz Devices                                                  |    |

|   |            |            | Sequence for 650 MHz Devices                                                        |    |

|   |            |            | Power Supply Regulation                                                             |    |

|   |            |            | 2.2.3.1 Power-Up Power Supply Regulation                                            |    |

|   |            |            | 2.2.3.2 Power Supply Decoupling                                                     |    |

|   | 2.3        |            | Network                                                                             |    |

|   | 2.4        |            | 0 Advanced Development Platform Power Supply Subsystem                              |    |

|   |            |            | Subsystem Block Diagram                                                             |    |

|   |            |            | Power-up Sequence                                                                   |    |

|   | 2.5        |            | Network Processor Power-On di/dt Profiles                                           |    |

|   |            | 2.5.1 d    | li/dt Droop Analysis Results                                                        | 31 |

|   |            | 2.5.2 F    | Recommendations From Droop Analysis                                                 | 31 |

| 3 | RDR/       | λM         |                                                                                     | 33 |

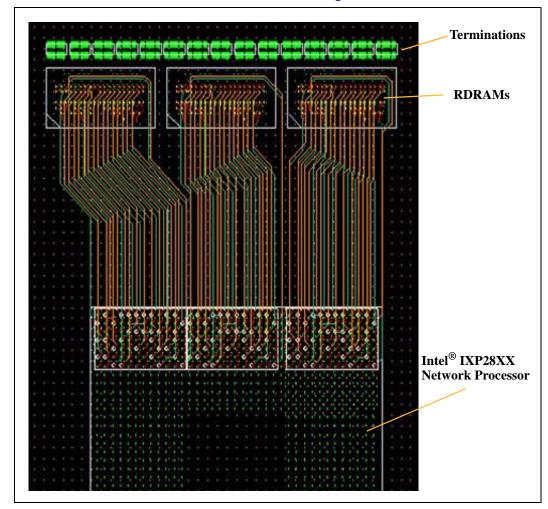

|   | 3.1        | IXMB280    | 0 RDRAM Subsystem Design                                                            | 33 |

|   |            |            | RDRAM Subsystem Implementation Options                                              |    |

|   | 3.2        |            | Channel Design                                                                      |    |

|   |            |            | RSL Trace Requirements and Recommendations                                          |    |

|   |            | 3.2.2 L    | Jnused Channel Guidelines                                                           | 36 |

|   |            | 3.2.3 C    | Crosstalk                                                                           | 36 |

|   |            | 3.2.4 T    | Third-party Sources                                                                 | 36 |

|   |            |            | XP28XX Network Processor Power-Up Sequence                                          | 36 |

|   |            |            | XP28XX Network Processor Power-Up Considerations when using NexMod*  Memory Modules | 37 |

|   | 3.3        |            | Network Processor Rambus* Controller Footprint and Via Placement                    |    |

|   | 3.4        | IXP28XX    | Network Processor Controller Escape Routing                                         |    |

|   | 3.5        | IXP28XX    | Network Processor Three-Channel Controller to HCD NexMod* RDRAM                     |    |

|   |            | Routing.   |                                                                                     |    |

|   | 3.6        | IXP28XX    | Network Processor Short Channel Routing                                             | 49 |

|   | 3.7        | Package    | Trace Lengths for RDRAM Signals                                                     | 50 |

| 4 | QDR        | SRAM       |                                                                                     | 53 |

|   | 4.1        | Introducti | on                                                                                  | 53 |

|   | 4.2        | QDR Clo    | cking Scheme                                                                        | 54 |

|   |            |            | SRAM Controller Configurations                                                      |    |

|   | 43         | ODR SR     | AM Connections                                                                      | 57 |

## IXP28XX Network Processor Contents

| 4.4  | QDR SRAM Interface                                                            | _   |

|------|-------------------------------------------------------------------------------|-----|

|      | 4.4.1 Using x9 Versus x18 QDR SRAM Parts                                      |     |

|      | 4.4.1.1 Examples of the QDR Interface                                         | 60  |

|      | 4.4.2 Signal Groups                                                           | 62  |

|      | 4.4.3 QDR Signal Mapping                                                      | 62  |

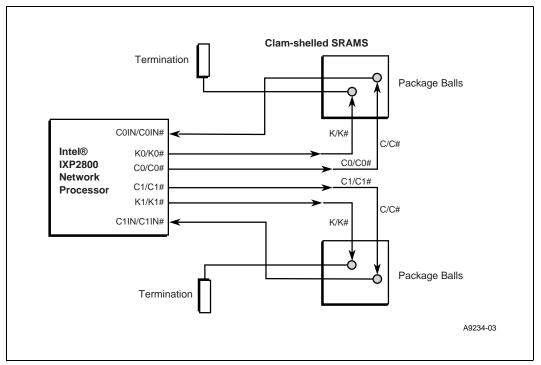

|      | 4.4.4 ClamShell Configuration of SRAMs                                        | 63  |

|      | 4.4.5 QDR SRAM Input/Output Timing Specifications                             | 64  |

|      | 4.4.5.1 IXP2800 Input Timing                                                  | 64  |

|      | 4.4.5.2 IXP2800 Output Timing                                                 |     |

|      | 4.4.6 QDR Signal Group Package Trace Length                                   |     |

| 4.5  | QDR SRAM Routing Rules                                                        |     |

|      | 4.5.1 QDR Trace Requirements                                                  |     |

|      | 4.5.2 QDR SRAM Address Topology                                               |     |

|      | 4.5.3 QDR SRAM D (Data Out) Topology                                          |     |

|      | 4.5.4 QDR SRAM Q (Data In) Topology                                           |     |

|      | 4.5.5 QDR SRAM K, K# Clock Topologies                                         |     |

|      | 4.5.5.1 Relationship between Address, Control, Data-OUT and K-Clock           |     |

|      | 4.5.6 QDR SRAM C, C#, CIN, CIN# Clock Topologies                              |     |

|      | 4.5.7 QDR SRAM RPE#, WPE#, BWE# Control Topologies                            |     |

| 4.6  | QDR SRAM VREF Generation                                                      |     |

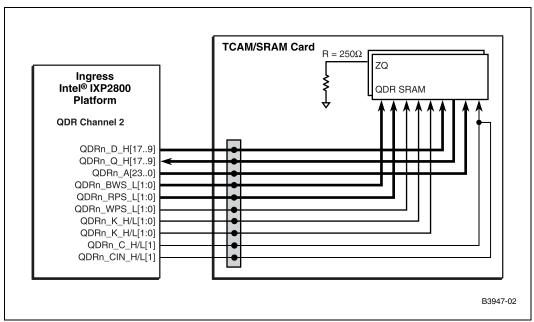

| 4.7  | TCAM/SRAM/Coprocessor Interface                                               |     |

|      | 4.7.1 TCAM/SRAM/Coprocessor Interface — Base Card Side                        |     |

|      | 4.7.1.1 Interface Topologies                                                  |     |

| 4.8  | IXDP2800 QDR Implementation Guidelines                                        |     |

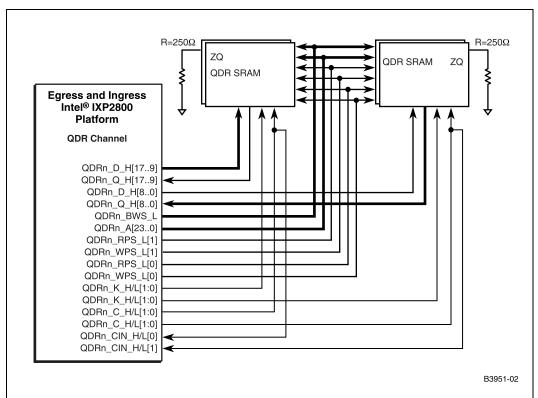

|      | 4.8.1 Routing for a Four-QDR SRAM Topology                                    |     |

|      | 4.8.2 Determining Loopclock Length for QDRII SRAM Used by IXDP2800 Advanced   |     |

|      | Development Platform                                                          | 85  |

|      | 4.8.3 QDR SRAM Alternating Routing Layers                                     |     |

| 4.9  | IXDP2800 TCAM Implementation                                                  |     |

|      | 4.9.1 TCAM and QDR SRAM Placement                                             |     |

|      | 4.9.2 QDR SRAM and TCAM Routing Implementation                                |     |

| 4.10 | QDR SRAM and TCAM Routing                                                     |     |

| 4.11 | QDR SRAM Design Review Checklist                                              |     |

| 4.12 | Package Trace Lengths for QDR Signals                                         | 95  |

| MSF  | (SPI-4/CSIX/FC)                                                               | 101 |

| 5.1  | Media and Switch Fabric Interface                                             |     |

| 0.1  | 5.1.1 SPI-4.2                                                                 |     |

|      | 5.1.2 CSIX                                                                    |     |

|      | 5.1.3 Flow Control Bus                                                        |     |

| 5.2  | Routing Recommendations for LVDS Signals                                      |     |

| 0.2  | 5.2.1 LVDS Trace Requirements                                                 |     |

|      | 5.2.2 LVDS Trace Characteristics for IXDP2800 Advanced Development Platform   |     |

|      | 5.2.3 Design Review Checklist                                                 |     |

|      | 5.2.4 LVDS Routing Example                                                    |     |

| 5.3  | Simulation Results for LVDS Signals on IXDP2800 Advanced Development Platform |     |

| 5.4  | Package Trace Lengths for LVDS_Diff Signals                                   |     |

|      |                                                                               |     |

| PCI  |                                                                               | 111 |

| 6.1  | PCI Controller                                                                |     |

| 6.2  | PCI Interface                                                                 | 111 |

6

5

|     |       | 6.2.1    | PPCI Bus Interface                                                             | 112    |

|-----|-------|----------|--------------------------------------------------------------------------------|--------|

|     |       |          | 6.2.1.1 PPCI Address/Data Signals                                              | 112    |

|     |       |          | 6.2.1.2 PPCI Clock Signals                                                     | 113    |

|     |       |          | 6.2.1.3 Address/Data Signals with IDSEL                                        |        |

|     |       | 6.2.2    | SPCI Bus Interface                                                             |        |

|     |       |          | 6.2.2.1 SPCI Address/Data Signals                                              |        |

|     |       |          | 6.2.2.2 SPCI Clock Signals                                                     | 11/    |

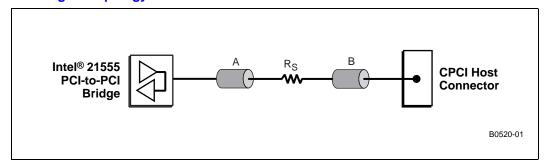

|     |       | 6.2.3    | 6.2.2.3 SPCI Address/Data Signals with IDSEL cPCI Bus Interface                |        |

|     |       | 0.2.3    | 6.2.3.1 cPCI Signals                                                           |        |

|     | 6.3   | PCI Da   | esign Review Checklist                                                         |        |

|     | 6.4   |          | outing Examples: IXP2800 Network Processor                                     |        |

|     | 6.5   |          | ge Trace Lengths for PCI Signals                                               |        |

| _   |       | `        |                                                                                |        |

| 7   | Slow  |          |                                                                                |        |

|     | 7.1   | Slowpo   | ort Interface                                                                  | 128    |

|     |       | 7.1.1    | Slowport Signals                                                               | 130    |

|     |       |          | 7.1.1.1 Topology and Routing                                                   | 130    |

|     |       | 7.1.2    | Flash Memory and Microprocessor Interface Support                              |        |

|     |       |          | 7.1.2.1 Flash PROM Interface Logic                                             |        |

|     |       |          | 7.1.2.2 Microprocessor Interface Logic                                         |        |

|     | 7.2   | Summa    | ary                                                                            | 145    |

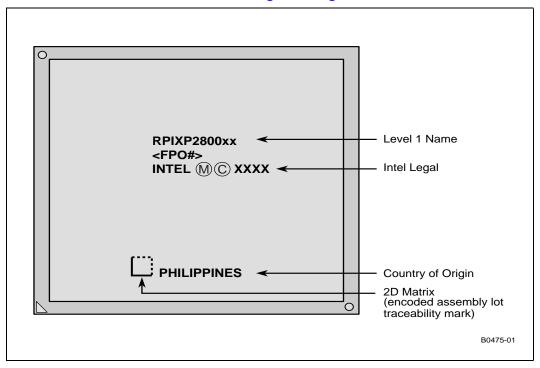

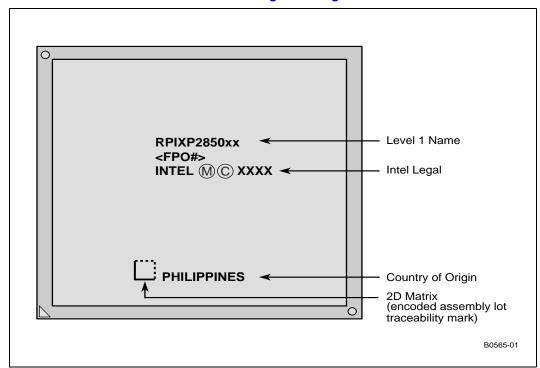

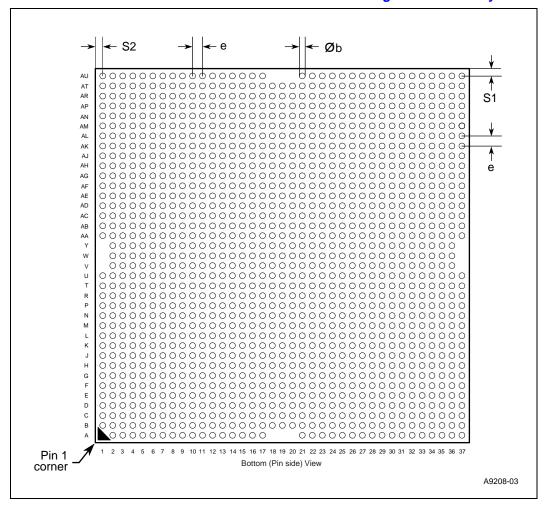

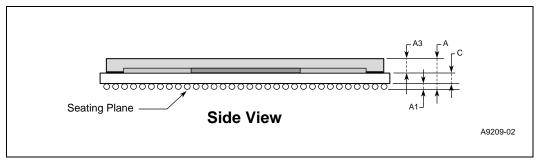

| 8   | Mech  | anical/P | Packaging                                                                      | 147    |

|     | 8.1   |          | ge Marking                                                                     |        |

|     | 8.2   |          | ge Dimensions                                                                  |        |

|     |       | `        |                                                                                |        |

|     | maex  | (        |                                                                                | 151    |

| Fic | jure  | \$       |                                                                                |        |

| 1   |       |          | P2850 Network Processor Functional Block Diagram                               | 12     |

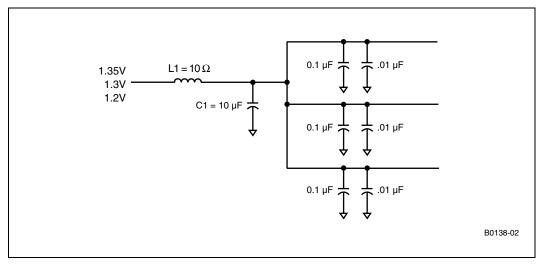

| 2   |       |          | Decoupling Implementation                                                      |        |

| 3   |       |          | etwork                                                                         |        |

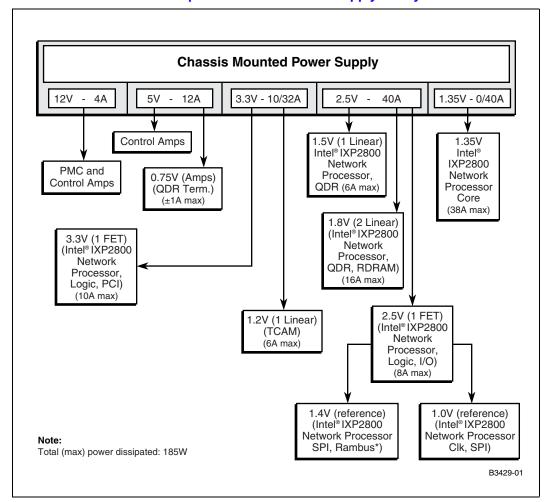

| 4   |       |          | Advanced Development Platform Power Supply Subsystem                           |        |

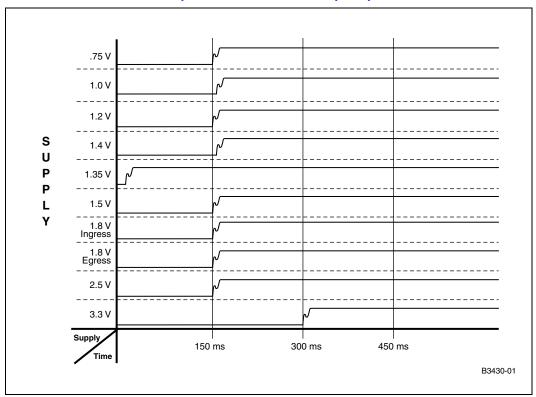

| 5   |       |          | Advanced Development Platform Power-up Sequence                                |        |

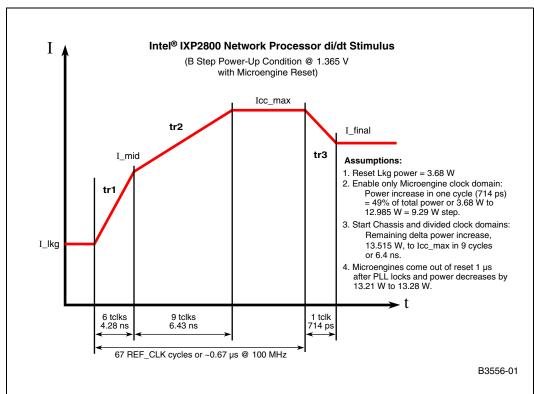

| 6   |       |          | etwork Processor di/dt Stimulus                                                |        |

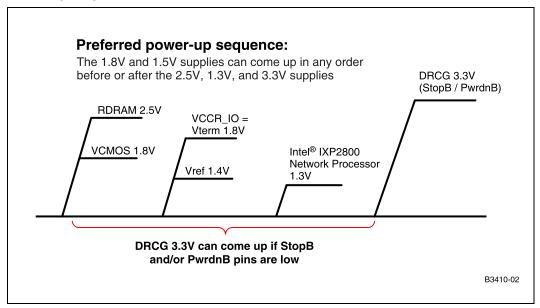

| 7   |       |          | Sequence                                                                       |        |

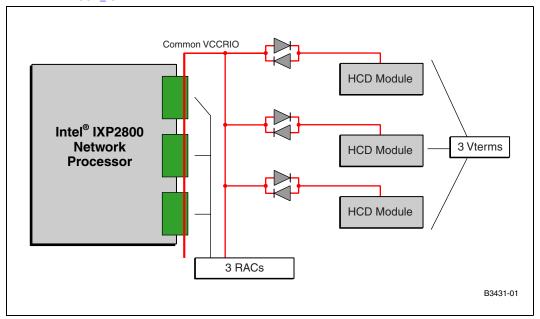

| 8   |       |          | CCR_IO for All Three RACs in the IXP28XX® Network Processor                    |        |

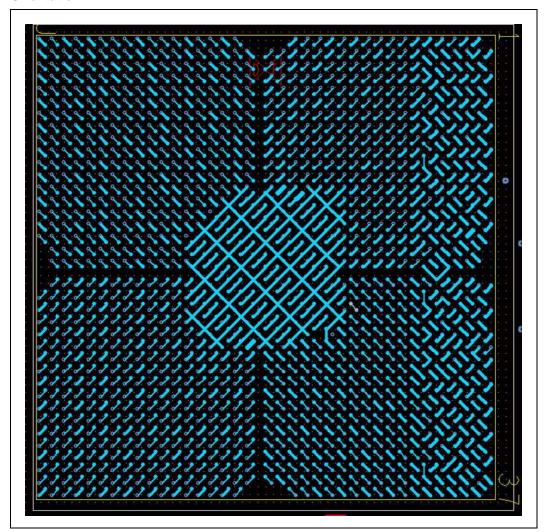

| 9   |       |          | controller Footprint and Via Placement Showing Alternating Dogbone Orientation |        |

|     |       |          | controller Footprint and Via Placement Showing Exploded View of                | ,,,,,, |

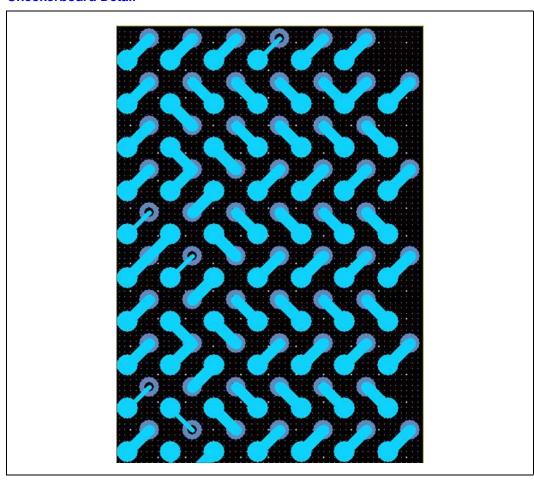

| •   |       |          | ard Detail                                                                     | 40     |

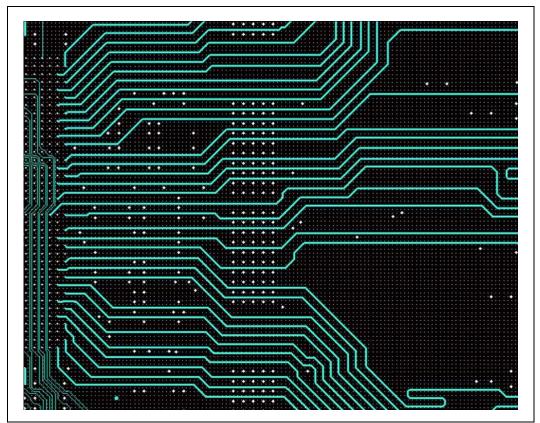

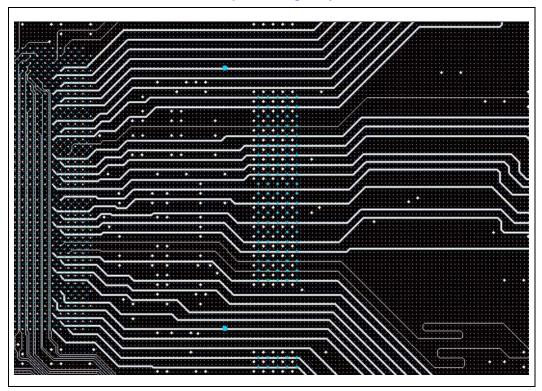

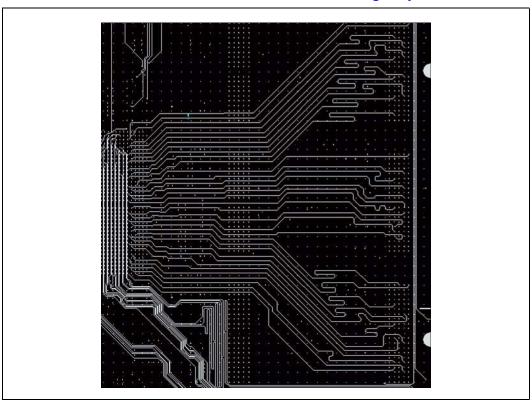

| 1   | 1 Net | work Pro | ocessor Controller Escape Routing - Layer 4                                    | 41     |

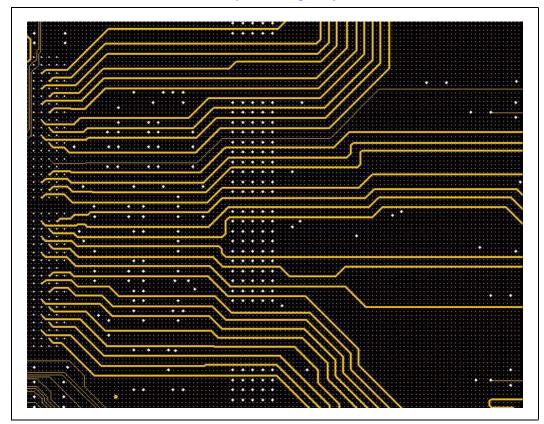

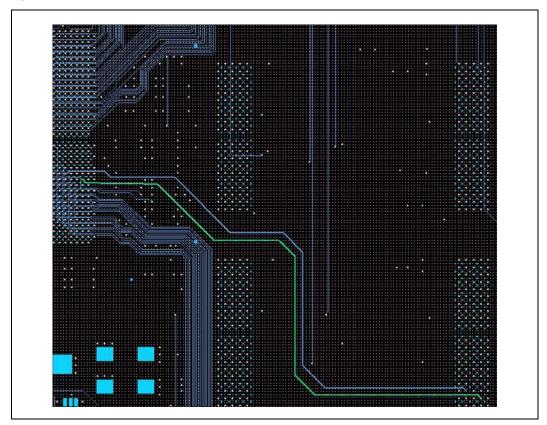

| 1   |       |          | ocessor Controller Escape Routing - Layer 6                                    |        |

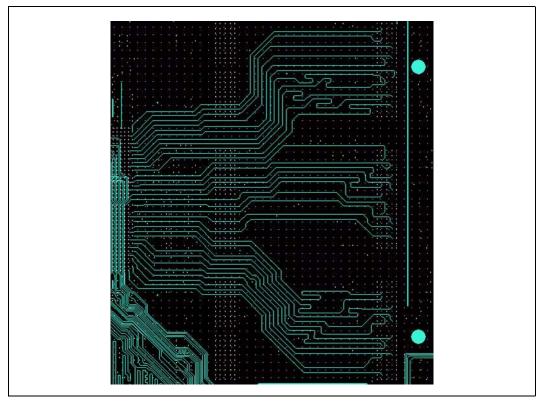

| 1   | 3 Net | work Pro | ocessor Controller Escape Routing - Layer 13                                   | 43     |

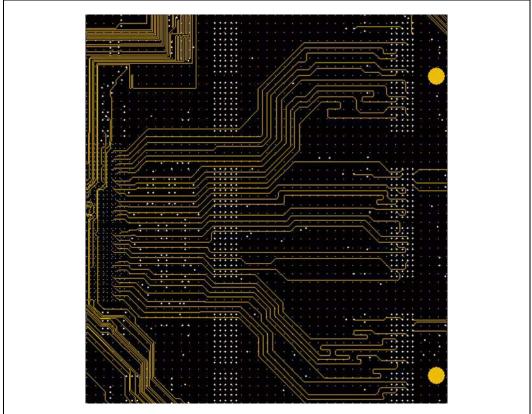

| 1   | 4 Net | work Pro | ocessor Controller Escape Routing - SCK/CMD Signals Routed on Layer 12         | 44     |

| 1   | 5 Net | work Pro | ocessor Controller Escape Routing - SCK/CMD Signals Routed on Layer 16         | 45     |

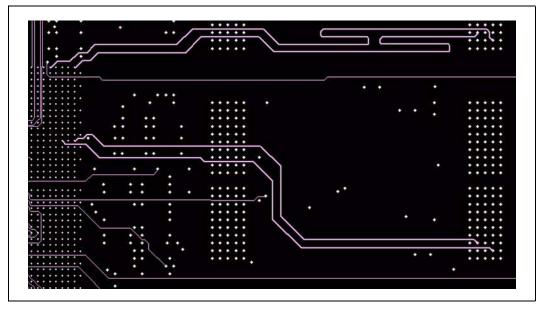

| 1   | 6 Thr | ee-Char  | nnel Controller to HCD NexMod* RDRAM Routing - Layer 4                         | 46     |

| 1   | 7 Thr | ee-Char  | nnel Controller to HCD NexMod* RDRAM Routing - Layer 6                         | 47     |

| 1   | 8 Thr | ee-Char  | nnel Controller to HCD NexMod* RDRAM Routing - Layer 13                        | 48     |

| 1   |       |          | nnel Controller to HCD NexMod* RDRAM Routing - SCK/CMD Layer 12                |        |

| 2   | 0 IXP | 28XX N   | etwork Processor Short Channel Routing                                         | 49     |

## IXP28XX Network Processor Contents

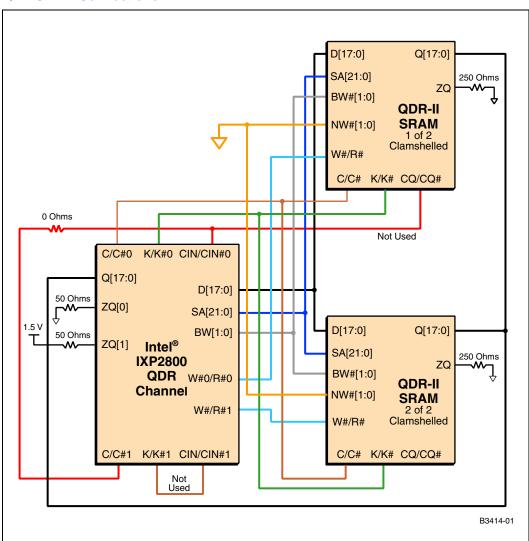

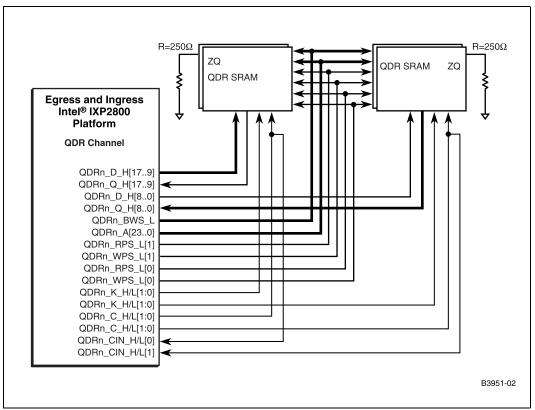

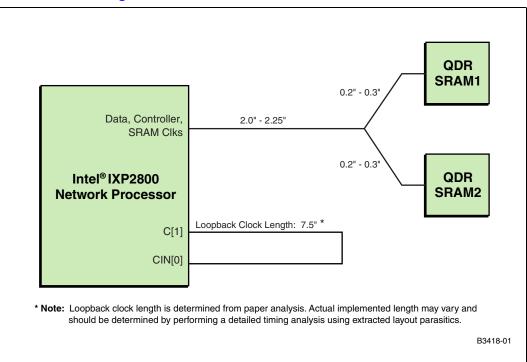

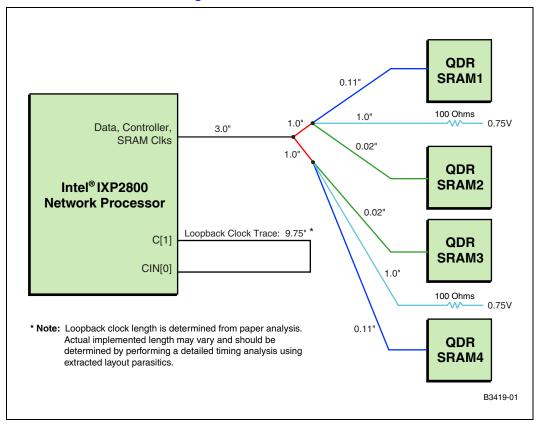

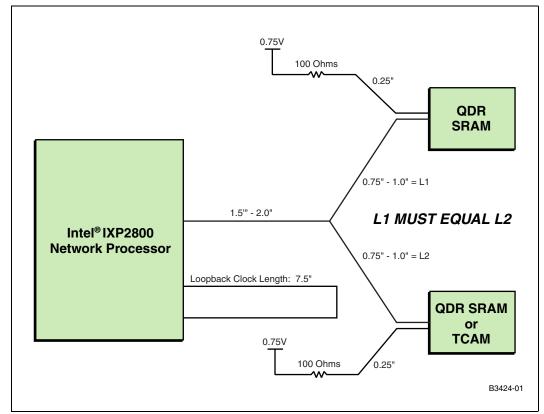

| 21 | Clocking Scheme for a QDR Interface Driving Four SRAMs                             | 54    |

|----|------------------------------------------------------------------------------------|-------|

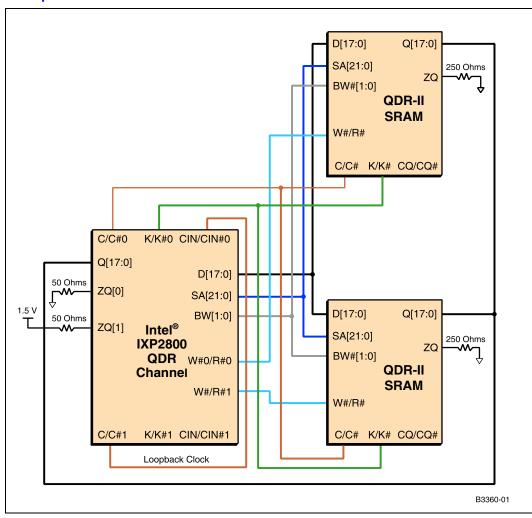

| 22 | QDR SRAM Connections                                                               |       |

| 23 | Topologies for Using x9 Versus x18 QDR SRAM Parts                                  | 59    |

| 24 | IXP2800 Width-Expanded QDR Interface                                               |       |

| 25 | Ingress IXP28XX Network Processor QDR Modular Channel Depth-Expanded QDR Interface | ce 61 |

| 26 | Ingress IXP2800 Network Processor QDR Modular Channel, Four-Load QDR Interface     | 61    |

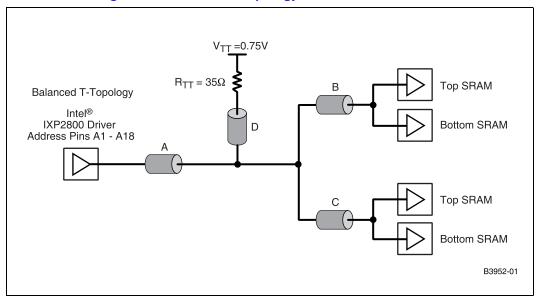

| 27 | QDR Address Signals — Balanced T-Topology                                          | 66    |

| 28 | QDR Address Routing — T-Topology with Daisy-Chain Branches                         | 66    |

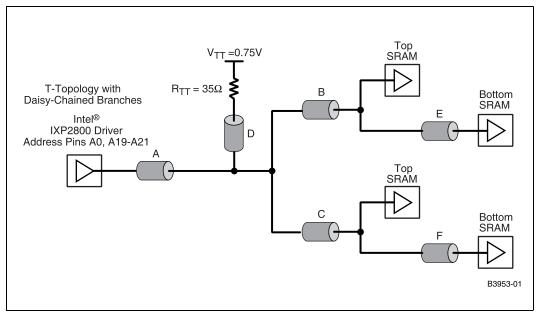

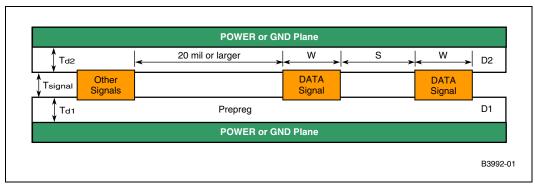

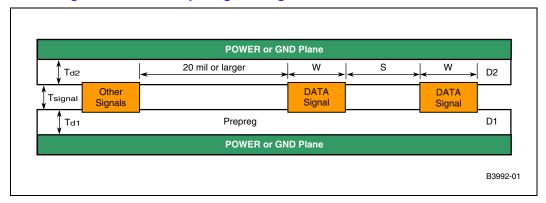

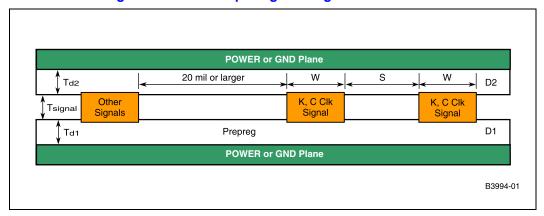

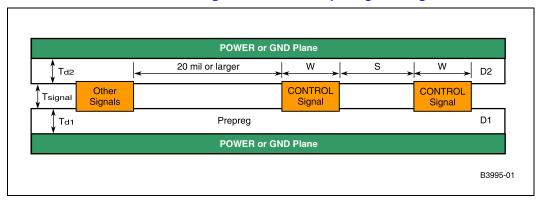

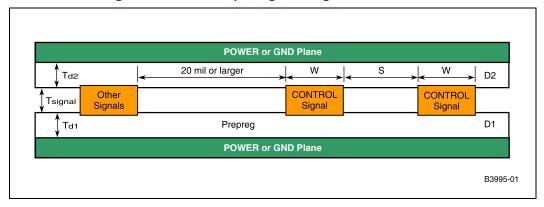

| 29 | QDR Address Signal Trace Width/Spacing Routing                                     | 67    |

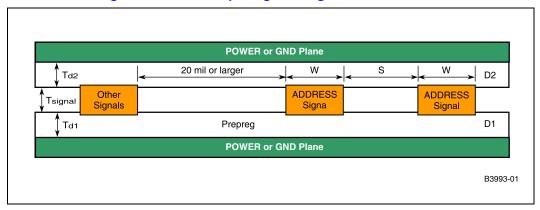

| 30 | D (Data Out) Routing Topology                                                      |       |

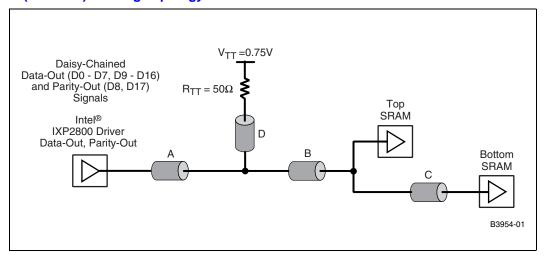

| 31 | QDR D Signal Trace Width/Spacing Routing                                           | 69    |

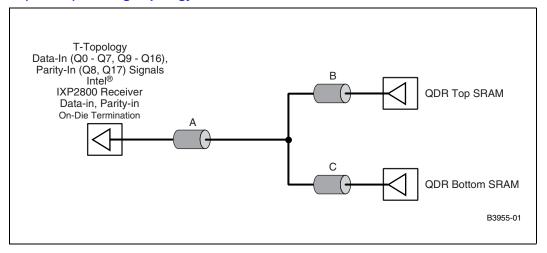

| 32 | Q (Data In) Routing Topology                                                       | 70    |

| 33 | QDR Q Signal Trace Width/Spacing Routing                                           | 71    |

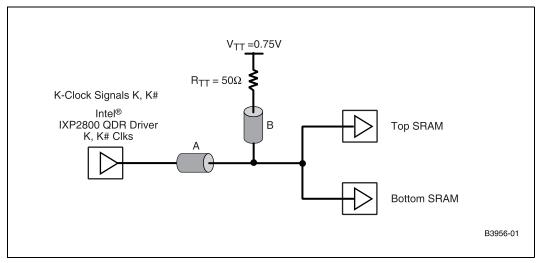

| 34 | QDR K and K# Routing Topology                                                      | 72    |

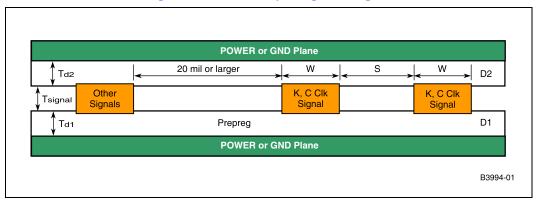

| 35 | QDR K and K# Signal Trace Width/Spacing Routing                                    | 73    |

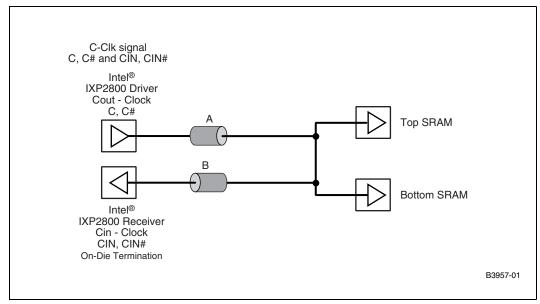

| 36 | QDR C, C#, CIN, and CIN# Routing Topology                                          | 74    |

| 37 | QDR C, C#, CIN, CIN# Signal Trace Width/Spacing Routing                            | 75    |

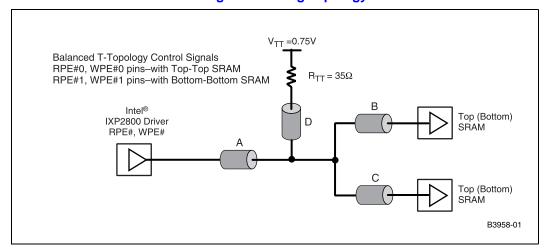

| 38 | QDR Control RPE# and WPE# Signals Routing Topology                                 | 76    |

| 39 | QDR Control RPE# and WPE# Signal Trace Width/Spacing Routing                       |       |

| 40 | QDR Control BWE# Signals Routing Topology                                          | 78    |

| 41 | Control BWE# Signal Trace Width/Spacing Routing                                    | 79    |

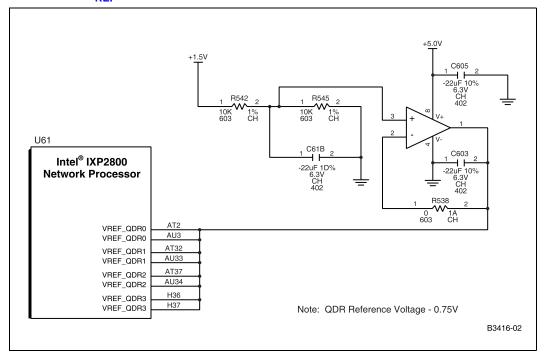

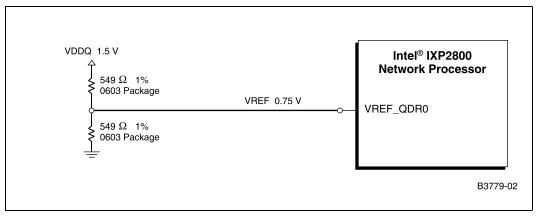

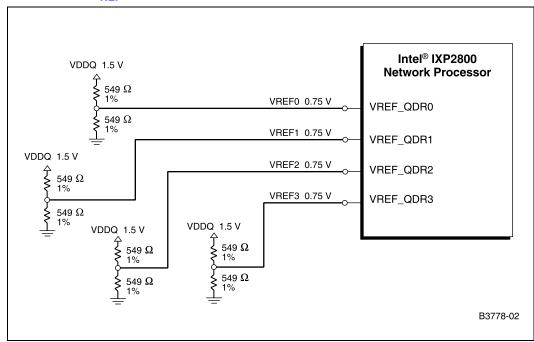

| 42 | QDR SRAM VREF Generation                                                           | 80    |

| 43 | Resistive QDR VREF Divider Example                                                 | 80    |

| 44 | Voltage QDR VREF Divider Example for Each QDR Channel                              | 81    |

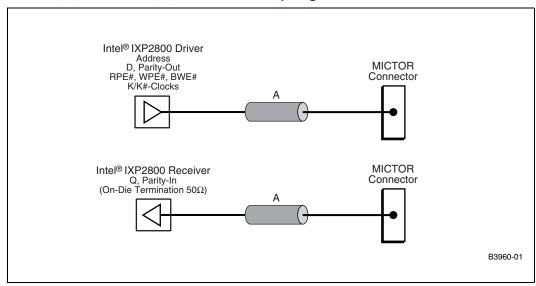

| 45 | Address, D, CONTROL, Q, and K-Clocks Topologies                                    | 82    |

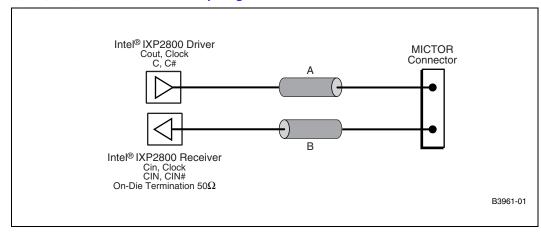

| 46 | C, C#, CIN, and CIN# Clocks Topologies                                             | 83    |

| 47 | QDR SRAM Routing Recommendations                                                   | 84    |

| 48 | Four-QDR SRAM Load Routing Recommendations                                         | 85    |

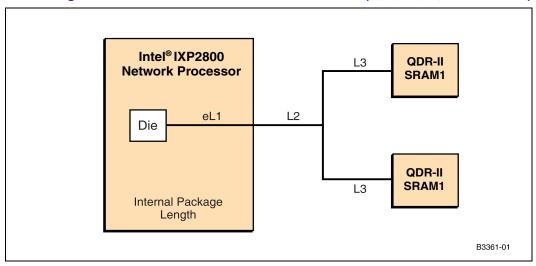

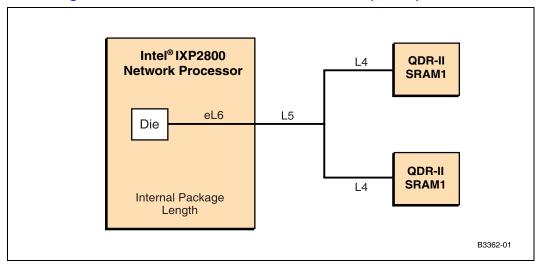

| 49 | Example Interconnects on the IXP28XX Network Processor, with a Two-QDRII SRAM Load |       |

|    | per Channel                                                                        |       |

| 50 | Trace Length from IXP28XX Network Processor to SRAM (C, K, SA, D, and R/W_BW)      |       |

| 51 | Trace Length from SRAM to IXP28XX Network Processor (Q Data)                       |       |

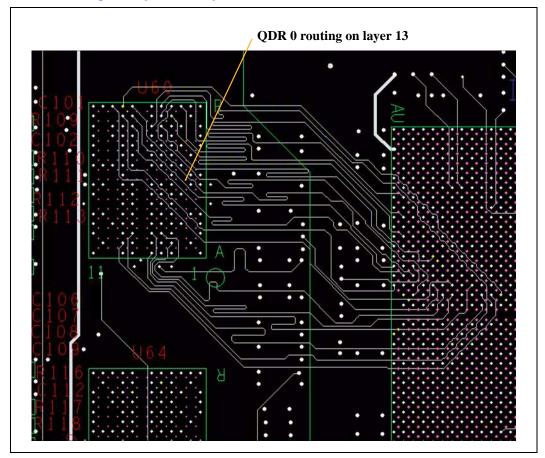

| 52 | QDR 0 Routing on Layer 13 - Adjacent QDR Clamshell Pairs                           |       |

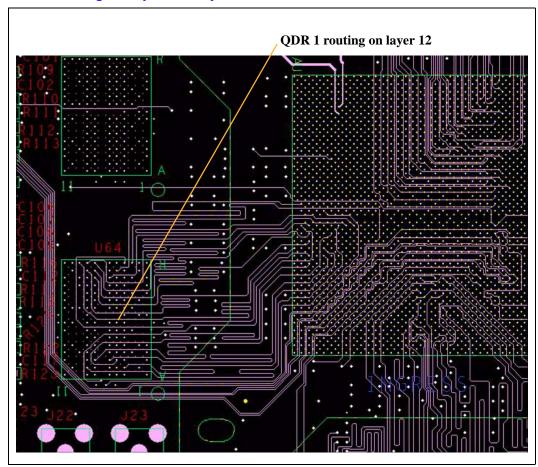

| 53 | QDR 1 Routing on Layer 12 - Adjacent QDR Clamshell Pairs                           |       |

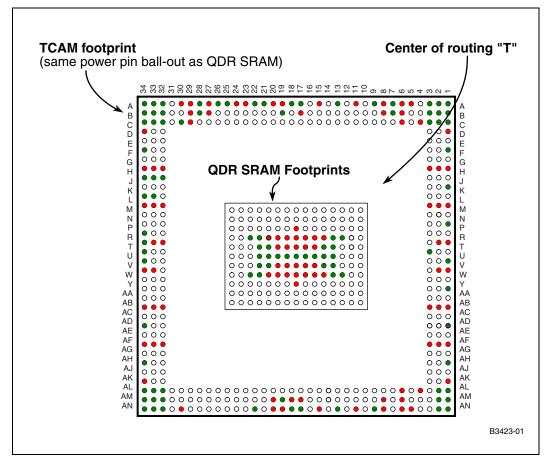

| 54 | TCAM and QDR SRAM Placement                                                        |       |

| 55 | Routing Recommendations for QDR SRAM and TCAM Routing                              |       |

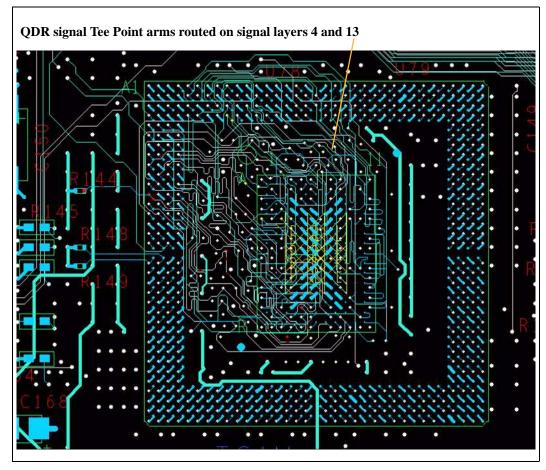

| 56 | QDR Signal from IXP28XX Network Processor to Tee Point on Layer 12                 |       |

| 57 | QDR Signal Tee Point Arms Routed on Signal Layers 4 and 13                         |       |

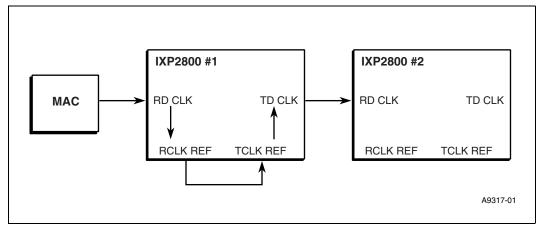

| 58 | SPI-4 Clock Configuration for Dual Network Processors                              |       |

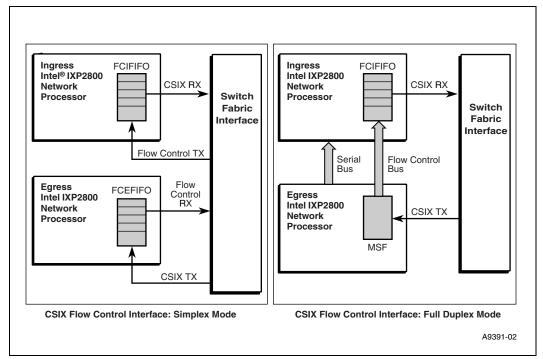

| 59 | CSIX Flow Control Interfaces: Simplex and Full Duplex Modes                        |       |

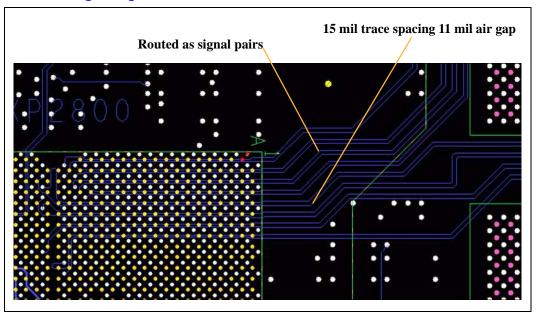

| 60 | LVDS Routing as Signal Pairs                                                       |       |

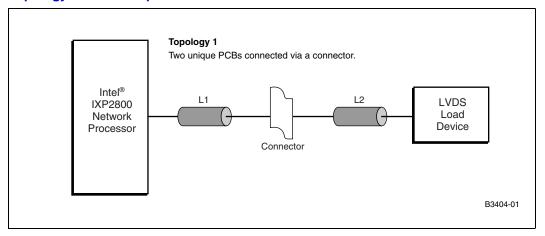

| 61 | Topology 1 - Two Unique PCBs Connected                                             |       |

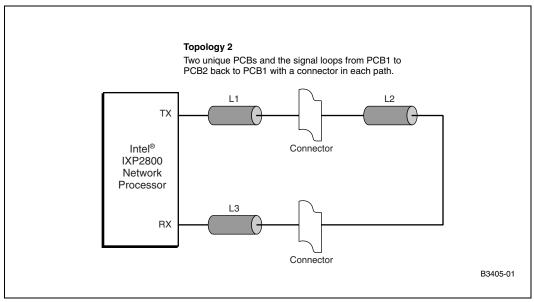

| 62 | Topology 2 - Two Unique PCBs with Signal Loopback Through Connectors               |       |

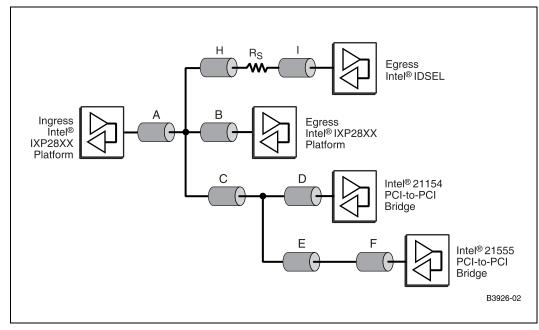

| 63 | PCI Subsystem                                                                      |       |

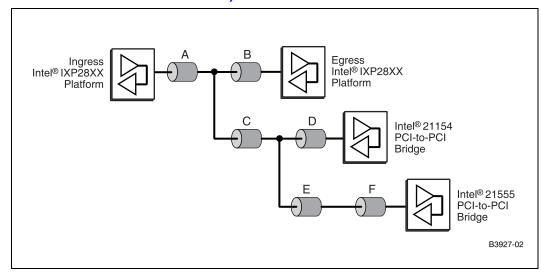

| 64 | PPCI Address/Data Signal Topology                                                  |       |

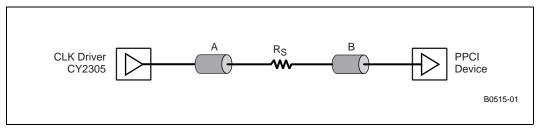

| 65 | PPCI Clock Signals Topology                                                        | . 114 |

| 66 | Address/Data Signals with IDSEL Topology (Showing Only the Ingress                 |       |

|    | Intel® IXP28XX Network Processor)                                                  |       |

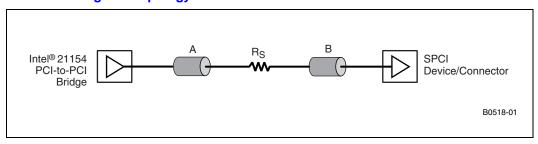

| 67 | SPCI Address/Data Signal Topology                                                  |       |

| 68 | SPCI Clock Signals Topology                                                        | . 117 |

| 69                                                                        | SPCI Address/Data Signals with IDSEL Signal Topology                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 70                                                                        | cPCI Signal Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

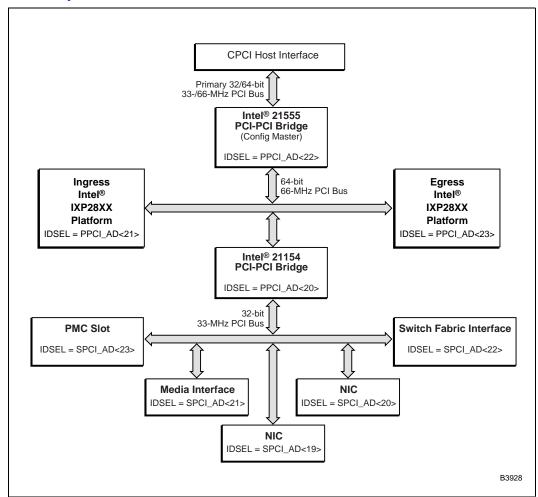

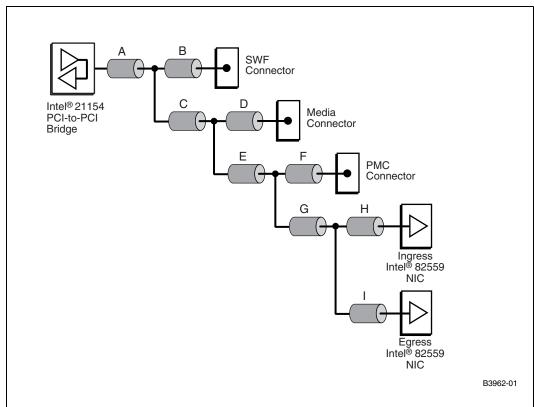

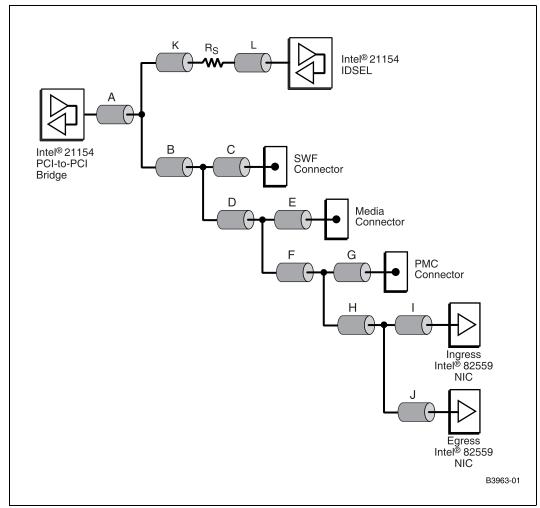

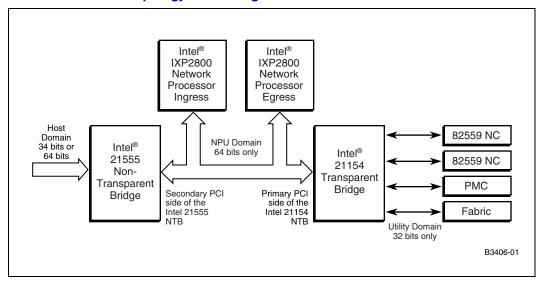

| 71                                                                        | IXDP2800 PCI Bus Topology Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                           | 121                                                |

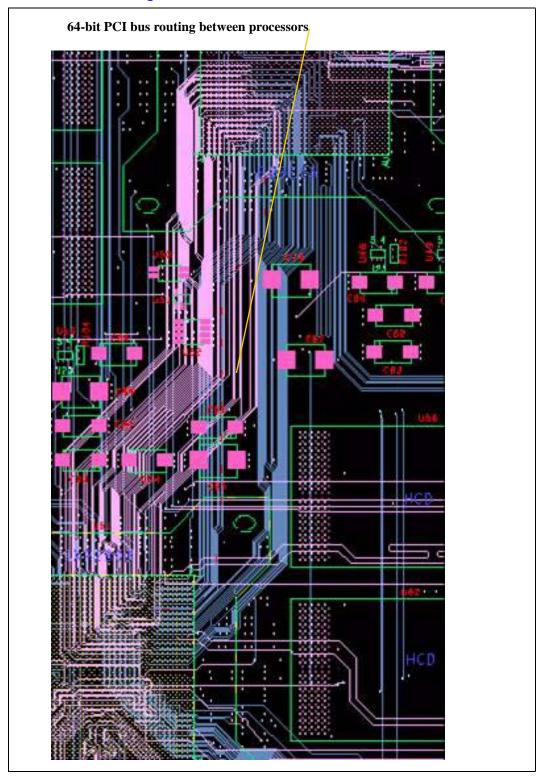

| 72                                                                        | 64-Bit PCI Bus Routing Between Processors                                                                                                                                                                                                                                                                                                                                                                                                                                         | 122                                                |

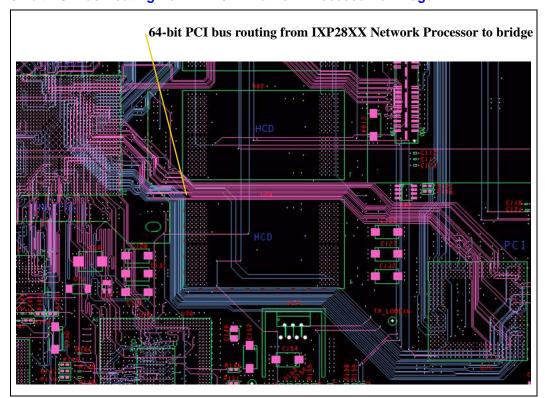

| 73                                                                        | 64-bit PCI Bus Routing from IXP28XX Network Processor to Bridge                                                                                                                                                                                                                                                                                                                                                                                                                   | 123                                                |

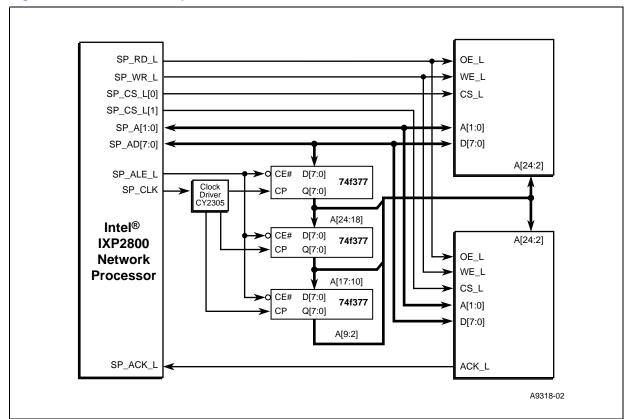

| 74                                                                        | Generic Slowport Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |

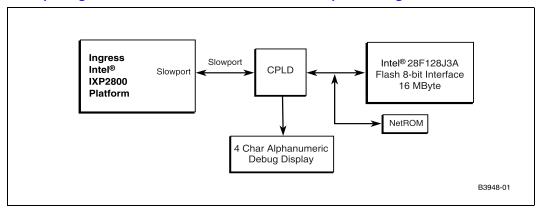

| 75                                                                        | Example Ingress IXP28XX Network Processor Slowport Configuration                                                                                                                                                                                                                                                                                                                                                                                                                  | 128                                                |

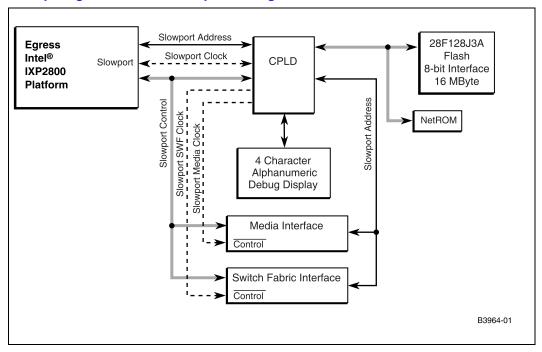

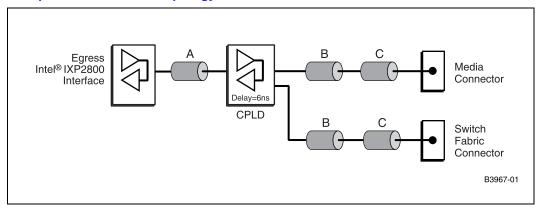

| 76                                                                        | Example Egress IXP28XX Slowport Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |

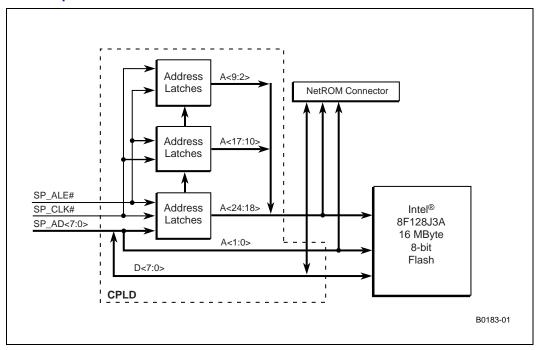

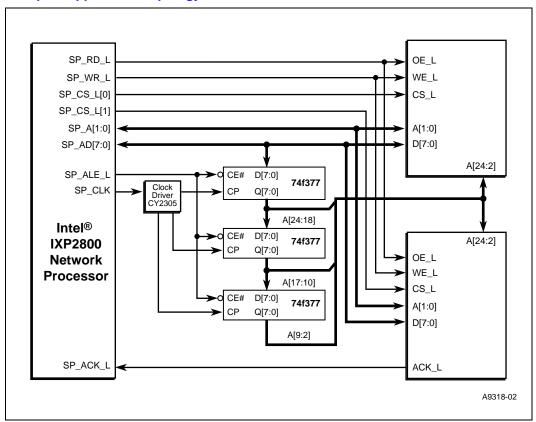

| 77                                                                        | CPLD Implementation of a Flash EEPROM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |

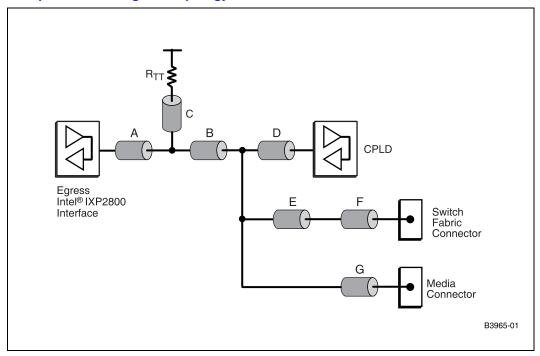

| 78                                                                        | Slowport Control Signals Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                    |

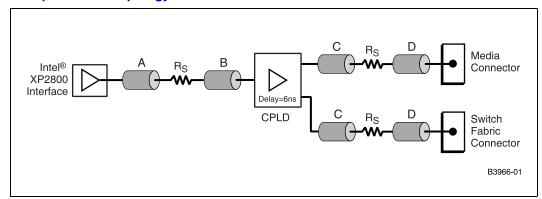

| 79                                                                        | Slowport Clock Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    |

| 80                                                                        | Slowport Address/Data Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |

| 81                                                                        | Slowport Application Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |

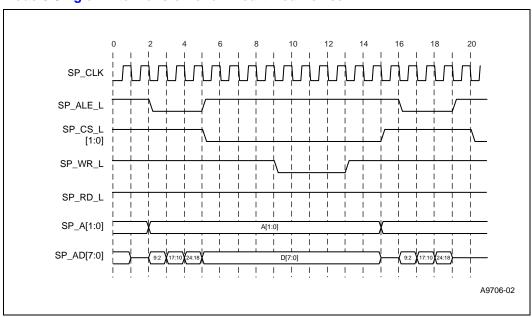

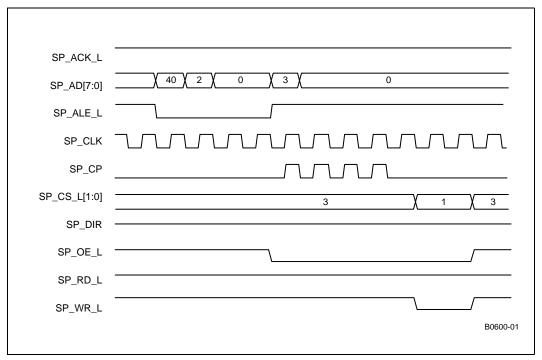

| 82                                                                        | Mode 0 Single Write Transfer for a Fixed-timed Device                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    |

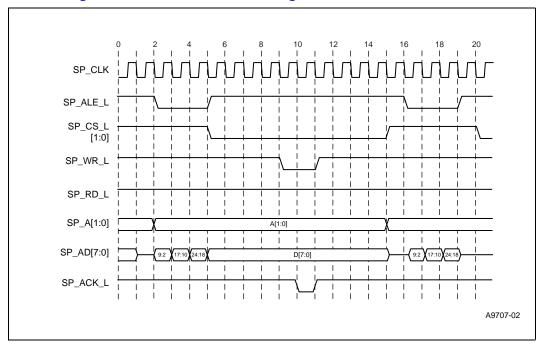

| 83                                                                        | Mode 0 Single Write Transfer for a Self-timing Device                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    |

| 84                                                                        | An Interface Topology with Intel / AMCC* SONET/SDH Device                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |

| 85                                                                        | Mode 3 32-Bit Write Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |

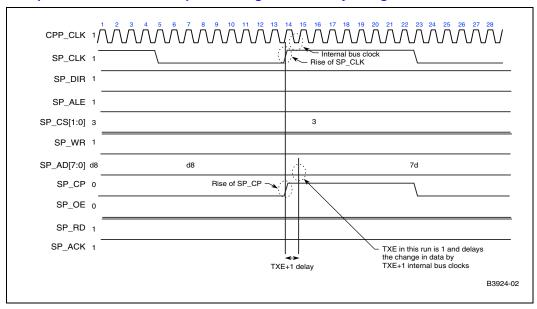

| 86                                                                        | Slowport Mode 3 write example showing TXE +1 delay using SP_TXE                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |

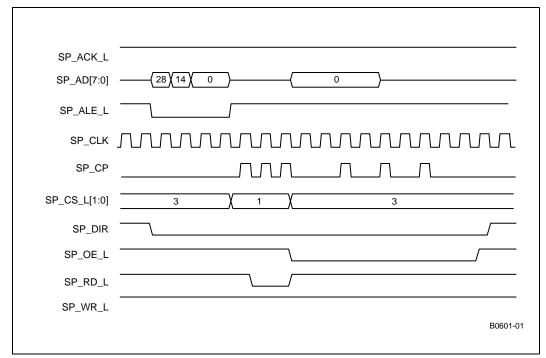

| 87                                                                        | Mode 32-Bit Read Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |

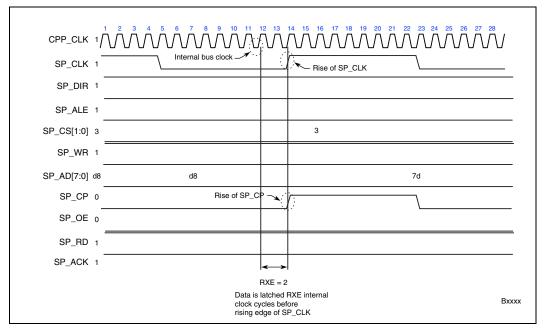

| 88                                                                        | Slowport Mode 3 read example showing RXE = 2                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |

| 89                                                                        | Intel® IXP2800 Network Processor Package Marking                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |

| 90                                                                        | Intel® IXP2850 Network Processor Package Marking                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |

| 91                                                                        | Intel® IXP2800 or Intel® IXP2850 Network Processor Package Ball Grid Array                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

| 92                                                                        | Intel® IXP2800 or Intel® IXP2850 Network Processor Package Side View                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

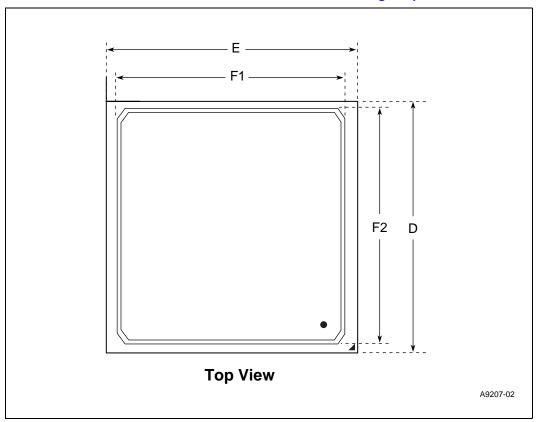

| 93                                                                        | Intel® IXP2800 or Intel® IXP2850 Network Processor Package Top View                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |

|                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |

| abl                                                                       | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

| 1                                                                         | Product Features of IXP28XX Network Processors                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12                                                 |

| 2                                                                         | Guide Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                    |

| 3                                                                         | Acronyms and Terminology                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |

| 4                                                                         | Absolute Maximum/Minimum Ratings Table                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                    |

| 5                                                                         | Functional Operating Temperature Range                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                    |

| 6                                                                         | Typical and Maximum Power                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |

| 7                                                                         | Functional Operating Voltage Range – 1.4/1.0 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |

| 8                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |

|                                                                           | Functional Operating Voltage Range – 650 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |

|                                                                           | Functional Operating Voltage Range – 650 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20                                                 |

| 9                                                                         | Example Power by Supply – 1.4 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20                                                 |

| 9<br>10                                                                   | Example Power by Supply – 1.4 GHz  Example Power by Supply – 1.0 GHz                                                                                                                                                                                                                                                                                                                                                                                                              | 20<br>21                                           |

| 9<br>10<br>11                                                             | Example Power by Supply – 1.4 GHz<br>Example Power by Supply – 1.0 GHz<br>Example Power by Supply – 650 MHz                                                                                                                                                                                                                                                                                                                                                                       | 20<br>21<br>22                                     |

| 9<br>10<br>11<br>12                                                       | Example Power by Supply – 1.4 GHz  Example Power by Supply – 1.0 GHz  Example Power by Supply – 650 MHz  RDRAM Subsystem Implementation Options                                                                                                                                                                                                                                                                                                                                   | 20<br>21<br>22<br>23                               |

| 9<br>10<br>11<br>12<br>13                                                 | Example Power by Supply – 1.4 GHz  Example Power by Supply – 1.0 GHz  Example Power by Supply – 650 MHz  RDRAM Subsystem Implementation Options.  Package Trace Lengths for RDRAM Signals                                                                                                                                                                                                                                                                                         | 2021233450                                         |

| 9<br>10<br>11<br>12<br>13<br>14                                           | Example Power by Supply – 1.4 GHz  Example Power by Supply – 1.0 GHz  Example Power by Supply – 650 MHz  RDRAM Subsystem Implementation Options  Package Trace Lengths for RDRAM Signals  SRAM Controller Configurations                                                                                                                                                                                                                                                          | 202123345055                                       |

| 9<br>10<br>11<br>12<br>13<br>14<br>15                                     | Example Power by Supply – 1.4 GHz  Example Power by Supply – 1.0 GHz  Example Power by Supply – 650 MHz  RDRAM Subsystem Implementation Options  Package Trace Lengths for RDRAM Signals  SRAM Controller Configurations  QDR Address/RPE/WPE Mapping                                                                                                                                                                                                                             | 202123345055                                       |

| 9<br>10<br>11<br>12<br>13<br>14<br>15<br>16                               | Example Power by Supply – 1.4 GHz  Example Power by Supply – 1.0 GHz  Example Power by Supply – 650 MHz  RDRAM Subsystem Implementation Options  Package Trace Lengths for RDRAM Signals  SRAM Controller Configurations  QDR Address/RPE/WPE Mapping  Total Memory per Channel                                                                                                                                                                                                   | 202123345055                                       |

| 9<br>10<br>11<br>12<br>13<br>14<br>15<br>16                               | Example Power by Supply – 1.4 GHz  Example Power by Supply – 1.0 GHz  Example Power by Supply – 650 MHz  RDRAM Subsystem Implementation Options  Package Trace Lengths for RDRAM Signals  SRAM Controller Configurations  QDR Address/RPE/WPE Mapping  Total Memory per Channel  An Overview of QDR signal groups                                                                                                                                                                 | 202134505555                                       |

| 9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18                   | Example Power by Supply – 1.4 GHz  Example Power by Supply – 1.0 GHz  Example Power by Supply – 650 MHz  RDRAM Subsystem Implementation Options  Package Trace Lengths for RDRAM Signals  SRAM Controller Configurations  QDR Address/RPE/WPE Mapping  Total Memory per Channel  An Overview of QDR signal groups  QDR SRAM Signal Mapping                                                                                                                                        | 20<br>21<br>34<br>50<br>55<br>55<br>62             |

| 9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18                   | Example Power by Supply – 1.4 GHz  Example Power by Supply – 1.0 GHz  Example Power by Supply – 650 MHz  RDRAM Subsystem Implementation Options  Package Trace Lengths for RDRAM Signals  SRAM Controller Configurations  QDR Address/RPE/WPE Mapping  Total Memory per Channel  An Overview of QDR signal groups  QDR SRAM Signal Mapping  QDR Address Signal Group Routing Guidelines                                                                                           | 20<br>21<br>23<br>34<br>50<br>55<br>55<br>62<br>62 |

| 9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20       | Example Power by Supply – 1.4 GHz  Example Power by Supply – 1.0 GHz  Example Power by Supply – 650 MHz  RDRAM Subsystem Implementation Options.  Package Trace Lengths for RDRAM Signals  SRAM Controller Configurations  QDR Address/RPE/WPE Mapping  Total Memory per Channel  An Overview of QDR signal groups  QDR SRAM Signal Mapping  QDR Address Signal Group Routing Guidelines  QDR Address Stack-up Signal Cross-section Details                                       | 20212334505555626262                               |

| 9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21 | Example Power by Supply – 1.4 GHz  Example Power by Supply – 1.0 GHz  Example Power by Supply – 650 MHz  RDRAM Subsystem Implementation Options  Package Trace Lengths for RDRAM Signals  SRAM Controller Configurations  QDR Address/RPE/WPE Mapping  Total Memory per Channel  An Overview of QDR signal groups  QDR SRAM Signal Mapping  QDR Address Signal Group Routing Guidelines  QDR Address Stack-up Signal Cross-section Details  QDR D Signal Group Routing Guidelines | 2021233450555562626768                             |

| 9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20       | Example Power by Supply – 1.4 GHz  Example Power by Supply – 1.0 GHz  Example Power by Supply – 650 MHz  RDRAM Subsystem Implementation Options.  Package Trace Lengths for RDRAM Signals  SRAM Controller Configurations  QDR Address/RPE/WPE Mapping  Total Memory per Channel  An Overview of QDR signal groups  QDR SRAM Signal Mapping  QDR Address Signal Group Routing Guidelines  QDR Address Stack-up Signal Cross-section Details                                       |                                                    |

## IXP28XX Network Processor Contents

| 24 | QDR Q Stack-up Signal Cross-section Details                                        | 71  |

|----|------------------------------------------------------------------------------------|-----|

| 25 | QDR K and K# Signal Group Routing Guidelines                                       | 72  |

| 26 | QDR K-Clock Stack-up Signal Cross-section Details                                  | 73  |

| 27 | QDR C, C#, CIN, and CIN# Signal Group Routing Guidelines                           | 74  |

| 28 | QDR C and CIN Clock Signal Trace Width/Spacing Routing Details                     | 75  |

| 29 | QDR Control RPE# and WPE# Signal Group Routing Guidelines                          | 76  |

| 30 | QDR CONTROL Stack-up Signal Cross-section Details                                  | 77  |

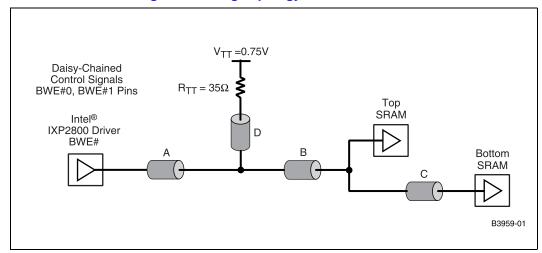

| 31 | QDR Control BWE# Signal Group Routing Guidelines                                   | 78  |

| 32 | QDR CONTROL Stack-up Signal Cross-section Details                                  | 79  |

| 33 | TCAM/SRAM/Coprocessor Interface Guidelines (Address, D, CONTROL, Q, and K-Clocks). | 82  |

| 34 | TCAM/SRAM/Coprocessor Interface Guidelines (C, C#, CIN, and CIN# Clocks)           | 83  |

| 35 | Package Trace Lengths for QDR Signals                                              | 96  |

| 36 | Topology 1 Network Length Results                                                  | 106 |

| 37 | Topology 2 Network Length Results                                                  | 107 |

| 38 | Package Trace Lengths for LVDS_Diff Signals                                        | 108 |

| 39 | PPCI Address/Data Group Guidelines                                                 | 113 |

| 40 | PPCI Clock Signals Group Guidelines                                                | 114 |

| 41 | Address/Data Signal with IDSEL Group Guidelines                                    | 115 |

| 42 | SPCI Address/Data Group Guidelines                                                 | 116 |

| 43 | SPCI Clock Signals Group Guidelines                                                | 117 |

| 44 | SPCI Address/Data Signals with IDSEL Group Guidelines                              | 119 |

| 45 | cPCI Signal Group Guidelines                                                       |     |

| 46 | Package Trace Lengths for PCI Signals                                              | 124 |

| 47 | Signal Description                                                                 | 130 |

| 48 | Slowport Control Signals Routing Guidelines                                        | 131 |

| 49 | Slowport Clock Signals Guideline                                                   | 132 |

| 50 | Slowport Address/Data Routing Guidelines                                           | 133 |

| 51 | Intel® IXP2800 or IXP2850 Network Processor Package Dimensions                     | 150 |

## **Revision History**

| Date          | Revision | Description                    |

|---------------|----------|--------------------------------|

| August 2005   | 002      | Updates to Chapter 4 QDR SRAM. |

| December 2004 | 001      | Initial release                |

#### IXP28XX Network Processor Revision History

# Introduction

1

The purpose of this manual is to accelerate the development of Intel<sup>®</sup> IXP28XX Network Processor hardware designs. The manual provides the hardware developer general design guidelines and includes specific design implementations used on the IXDP2800 Advanced Development Platform.

These guidelines have been developed to ensure maximum flexibility for board designers and to reduce board-related problems. The design information in this document is in two categories:

- Design Recommendations, based on Intel's simulations and lab debugging experience to date, and are strongly recommended (or necessary) to meet timing and signal quality specifications.

- **Design Considerations** or suggestions, based on the development platforms designed by Intel. They should be used as examples, but may not be applicable to particular designs.

**Note:** The guidelines recommended in this document are based on simulation work completed by Intel. This work is ongoing, and recommendations are subject to change.

**Note:** General information regarding certain artwork in this document. Due to differences in output devices, some figures may display inconsistently. For example, viewing a figure on a computer screen and producing hardcopy to a printer can result in the screen providing finer resolution than the printer.

#### 1.1 System Overview

The IXP28XX network processors enable fast deployment of complete content processing by providing unlimited programming flexibility, code re-use, and high-performance processing. These network processors support a wide variety of WAN and LAN applications that require a broad range of speeds, currently ranging from OC-3 through OC-192. High performance and scalability is achieved through an innovative Microengine architecture that includes a multi-threaded distribution cache architecture that enables pipeline features in software.

In addition to the standard feature set available with the Intel® IXP2800 Network Processor, the Intel® IXP2850 Network Processor integrates functionality for secure network traffic at 10 Gbytes/sec. This enables the up-front design of secure network equipment and results in lower power consumption and more efficient use of space on the printed circuit board.

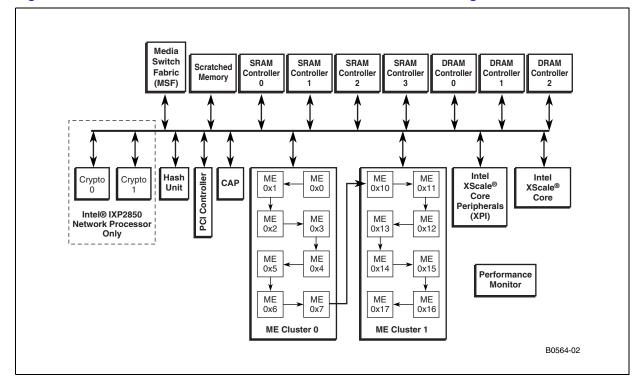

Table 1 summarizes the product features. Figure 1 provides a functional overview of the Intel® IXP2800 Network Processor and Intel® IXP2850 Network Processor internal hardware, showing the major internal blocks.

#### Table 1. Product Features of IXP28XX Network Processors

| Feature                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sixteen integrated Microengines (Version 2)                                | <ul> <li>Operating frequency of up to 1.4 GHz</li> <li>Configurable to four or eight threads per Microengine</li> <li>640 Dwords of local memory per Microengine</li> <li>Sixteen-entry CAM per Microengine, with single cycle lookup</li> <li>Next Neighbor bus accessing adjacent Microengines</li> <li>CRC unit per Microengine</li> <li>8K instructions control store per Microengine</li> <li>Support for Generalized Thread Signaling</li> </ul> |

| Integrated Intel XScale® core                                              | <ul> <li>Operating frequency of up to 700 MHz</li> <li>High performance, low power 32-bit embedded RISC processor</li> <li>32-Kbyte instruction cache</li> <li>32-Kbyte data cache</li> </ul>                                                                                                                                                                                                                                                          |

| Two integrated Cryptographic units (Intel® IXP2850 Network Processor only) | <ul> <li>Operating frequency of 700 MHz</li> <li>Support for DES, 3DES, AES, and SHA-1 algorithms</li> <li>Support for AES 128-, 192-, and 256-bit keys</li> </ul>                                                                                                                                                                                                                                                                                     |

| Three industry-standard RDRAM interfaces                                   | Peak bandwidth of 2.1 Gbytes/sec  800-MHz and 1066-MHz RDRAM  Error Correction Code (ECC)  Addressable from Intel XScale® core, Microengines, and PCI                                                                                                                                                                                                                                                                                                  |

| Four industry-standard 32-bit<br>QDR SRAM interfaces                       | <ul> <li>Peak bandwidth of 1.9 Gbytes/sec per channel</li> <li>233-MHz SRAM</li> <li>Hardware support for Linked List and Ring operations</li> <li>Atomic bit operations</li> <li>Atomic arithmetic support</li> <li>Addressable from Intel XScale® core, Microengines, and PCI</li> </ul>                                                                                                                                                             |

| Integrated Media Switch Fabric interface                                   | <ul> <li>Two unidirectional 16-bit Low-Voltage Differential Signaling (LVDS) data interfaces</li> <li>Up to 500 MHz per channel</li> <li>Separately configurable for either SPI-4 or CSIX protocols</li> </ul>                                                                                                                                                                                                                                         |

| Industry-standard PCI Bus                                                  | PCI Local Bus Specification, Version 2.2* interface for 64-bit, 66-MHz I/O                                                                                                                                                                                                                                                                                                                                                                             |

| Additional integrated features                                             | <ul> <li>Hardware Hash Unit (48-, 64-, and 128-bit)</li> <li>16-KByte Scratchpad Memory</li> <li>Serial UART port for debug</li> <li>Eight general-purpose I/O pins</li> <li>Four 32-bit timers</li> </ul>                                                                                                                                                                                                                                             |

| 1356 Ball FCBGA package                                                    | Dimensions of 37.5mm x 37.5mm     1 mm solder ball pitch                                                                                                                                                                                                                                                                                                                                                                                               |

Figure 1. IXP2800/IXP2850 Network Processor Functional Block Diagram

#### 1.2 In This Guide

This document comprises the following chapters and appendixes that describe the IXP28XX network processor:

- Chapter 2, "Power Ratings and Requirements," describes the minimum and maximum operating voltages and temperatures.

- Chapter 3, "RDRAM," describes the IXP28XX network processor's Rambus\* DRAM implementation.

- Chapter 4, "QDR SRAM," describes the IXP28XX network processor's four independent SRAM controllers, each of which supports pipelined QDR synchronous static RAM (SRAM).

- Chapter 5, "MSF (SPI-4/CSIX/FC)," describes the Media and Switch Fabric (MSF) interface.

- Chapter 6, "PCI," describes the use of the PCI controller to provide a 64-bit, 66-MHz-capable *PCI Local Bus Specification*, *Version* 2.2\* interface for the IXP28XX network processor.

- Chapter 7, "Slowport," describes the Slowport external interface to the IXP28XX network processor.

- Chapter 8, "Mechanical/Packaging," describes the dimensions of the IXP28XX network processor and package markings for the processor chip.

#### 1.2.1 Typographical Conventions

This guide contains the following text and typography conventions:

#### Table 2. Guide Conventions

| Convention                                               | Description                                                                                                                                                   |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Italics                                                  | New terms and titles of documents or help systems appear in italics.                                                                                          |

| bold                                                     | Special text for labels of items appears in bold type.                                                                                                        |

| monospace                                                | Code and names of drives, pathnames, directories, and filenames appear in Courier monospace type.                                                             |

| monospace bold                                           | Example commands given to show user input.                                                                                                                    |

| table of contents<br>table of figures<br>table of tables | Each item in the tables of contents, figures, and tables is a hyperlink.                                                                                      |

| >                                                        | Indicates the sequential choice of menu items. For example, the menu items for the Developers Workbench are <b>Start &gt; IXA SDK 4.1 &gt; DevWorkbench</b> . |

### 1.2.2 Acronyms and Terminology

Table 3 defines the acronyms and terminology that are used throughout this document.

#### Table 3. Acronyms and Terminology (Sheet 1 of 3)

| Acronym/Terminology | Definition                                                          |

|---------------------|---------------------------------------------------------------------|

| AES                 | Advanced Encryption Standard                                        |

| ATM                 | Asynchronous Transfer Mode                                          |

| BGA                 | ball grid array                                                     |

| BWE                 | Byte Write Enable, a type of control signal that is active low      |

| CFM                 | Clock-to-Master, positive polarity                                  |

| CFMN                | Clock-to-Master, negative polarity                                  |

| Clamshelling        | Locating two devices on opposite sides of the printed circuit board |

| cPCI                | Compact PCI, a 32- or 64-bit bus, operating at either 33 or 66 MHz  |

| CPIX                | Common Programming Interface Forum                                  |

| CSIX                | Common Switch Interface                                             |

| CPLD                | Complex Programmable Logic Device                                   |

| CSR                 | Control Status Register                                             |

| СТМ                 | Clock-to-Master, positive polarity                                  |

| CTMN                | Clock-to-Master, negative polarity                                  |

| DDR                 | Double Data Rate                                                    |

| DES                 | Data Encryption Standard                                            |

| DLL                 | Dynamic Link Library                                                |

| DMA                 | Direct Memory Access                                                |

| DRAM                | Dynamic Random Access Memory                                        |

#### Table 3. Acronyms and Terminology (Sheet 2 of 3)

| Acronym/Terminology | Definition                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRCG                | Direct Rambus* Clock Generator                                                                                                                                                                                                                                                                                                                                                   |

| ECC                 | Error Correction Code                                                                                                                                                                                                                                                                                                                                                            |

| EEPROM              | Electrically Erasable Programmable Read-only Memory                                                                                                                                                                                                                                                                                                                              |

| LVDS                | Low-Voltage Differential Signaling                                                                                                                                                                                                                                                                                                                                               |

| MAC                 | Medium Access Control, a 48-bit number unique to each LAN network interface card (NIC)                                                                                                                                                                                                                                                                                           |

| MSF                 | Media Switch Fabric                                                                                                                                                                                                                                                                                                                                                              |

| NA                  | Not applicable                                                                                                                                                                                                                                                                                                                                                                   |

| NIC                 | Network Interface Card                                                                                                                                                                                                                                                                                                                                                           |

| NPF                 | Network Processor Forum; organized to facilitate the development of next-<br>generation networking and telecommunications products based on network<br>processing technologies                                                                                                                                                                                                   |

| OIF                 | Optical Internetworking Forum                                                                                                                                                                                                                                                                                                                                                    |

| PCB                 | Printed circuit board                                                                                                                                                                                                                                                                                                                                                            |

| PCI                 | Peripheral Component Interconnect                                                                                                                                                                                                                                                                                                                                                |

| PHY                 | physical layer device                                                                                                                                                                                                                                                                                                                                                            |

| PGA                 | pin grid array                                                                                                                                                                                                                                                                                                                                                                   |