# CY7C53150, CY7C53120

# **Neuron Chip Network Processor**

## Features

- Three 8-bit pipelined processors for concurrent processing of application code and network traffic

- 11-pin I/O port programmable in 34 modes for fast application program development

- Two 16-bit timer/counters for measuring and generating I/O device waveforms

- 5-pin communication port that supports direct connect and network transceiver interfaces

- Programmable pull ups on IO4–IO7 and 20 mA sink current on IO0–IO3

- Unique 48-bit ID number in every device to facilitate network installation and management

- Low operating current: sleep mode operation for reduced current consumption<sup>[1]</sup>

- 0.35 µm Flash process technology

- 5.0V operation

- On-chip LVD circuit to prevent nonvolatile memory corruption during voltage drops

- 2,048 bytes of SRAM for buffering network data, system, and application data storage

- 512 bytes (CY7C53150), 2048 bytes (CY7C53120E2), 4096 bytes (CY7C53120E4) of Flash memory with on-chip charge pump for flexible storage of configuration data and application code

- Addresses up to 58 KB of external memory (CY7C53150)

- 10 KB (CY7C53120E2), 12 KB (CY7C53120E4) of ROM containing LonTalk network protocol firmware

- Maximum input clock operation of 20 MHz (CY7C53150), 10 MHz (CY7C53120E2), 40 MHz (CY7C53120E4) over a -40°C to 85°C<sup>[2]</sup> temperature range

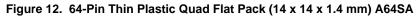

- 64-pin TQFP package (CY7C53150)

- 32-pin SOIC or 44-pin TQFP package (CY7C53120)

#### Notes

- 1. Rare combinations of wake-up events occurring during the go to sleep sequence could produce unexpected sleep behavior. See the Neuron Technical Reference Manual for more details.

- 2. Maximum Junction Temperature is 105°C. T<sub>Junction</sub> = T<sub>Ambient</sub> + V•I• $\theta_{JA}$ . 32-pin SOIC  $\theta_{JA}$  = 51C/W. 44-pin TQFP  $\theta_{JA}$  = 43C/W. 64-pin TQFP  $\theta_{JA}$  = 44C/W.

198 Champion Court

Cypress Semiconductor Corporation • Document #: 38-10001 Rev. \*F San Jose, CA 95134-1709 • 408-943-2600 Revised November 20, 2009

## Contents

| Functional Description                         | 3 |

|------------------------------------------------|---|

| Pin Configurations                             | 3 |

| Pin Descriptions                               |   |

| Memory Usage                                   |   |

| Flash Memory Retention and Endurance           |   |

| 40 MHz 3120 Operation                          |   |

| Low Voltage Inhibit Operation                  | 6 |

| Communications Port                            | 6 |

| Programmable Hysteresis Values                 | 7 |

| Programmable Glitch Filter Values <sup>[</sup> |   |

| Receiver                                       |   |

| Differential Receiver                          |   |

| Electrical Characteristics                     | 8 |

| LVI Trip Point                                         |

|--------------------------------------------------------|

| Differential Transceiver<br>Electrical Characteristics |

|                                                        |

| Ordering Information                                   |

| Package Diagrams 12                                    |

| Document History Page 15                               |

| Sales, Solutions, and Legal Information 15             |

| Worldwide Sales and Design Support 15                  |

| Products 15                                            |

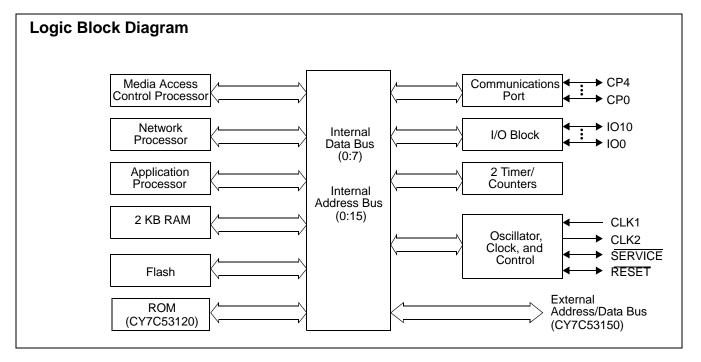

## **Functional Description**

The CY7C531x0 Neuron chip implements a node for LonWorks distributed intelligent control networks. It incorporates, on a single chip, the necessary communication and control functions, both in hardware and firmware, that facilitate the design of a LonWorks node.

The CY7C531x0 contains a very flexible 5-pin communication port that can be configured to interface with a wide variety of media transceivers at a wide range of data rates. The most common transceiver types are twisted-pair, powerline, RF, IR, fiber-optics, and coaxial.

The CY7C531x0 is manufactured using state of the art 0.35  $\mu m$  Flash technology, providing to designers the most cost-effective Neuron chip solution.

Services at every layer of the OSI networking reference model are implemented in the LonTalk firmware based protocol stored in 10-KB ROM (CY7C53120E2), 12-KB ROM (CY7C53120E4), or off-chip memory (CY7C53150). The firmware also contains 34 preprogrammed I/O drivers, greatly simplifying application programming. The application program is stored in the Flash memory (CY7C53120) and/or off-chip memory (CY7C53150), and may be updated by downloading over the network.

The CY7C53150 incorporates an external memory interface that can address up to 64 KB with 6 KB of the address space mapped internally. LonWorks nodes that require large application programs can take advantage of this external memory capability.

The CY7C53150 Neuron chip is an exact replacement for the Motorola MC143150Bx and Toshiba TMPN3150B1 devices. The CY7C53120E2 Neuron chip is an exact replacement for the Motorola MC143120E2 device since it contains the same firmware in ROM.

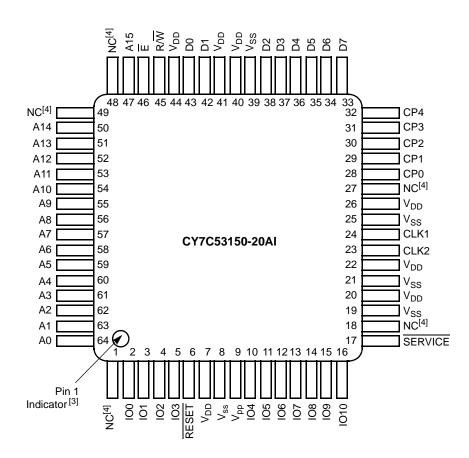

## **Pin Configurations**

### Figure 1. CY7C53150 64-Pin Thin Quad Flat Pack

#### Notes

3. The smaller dimple at the bottom left of the marking indicates pin 1.

4. No Connect (NC) — Must not be used. (These pins may be used for internal testing.)

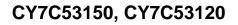

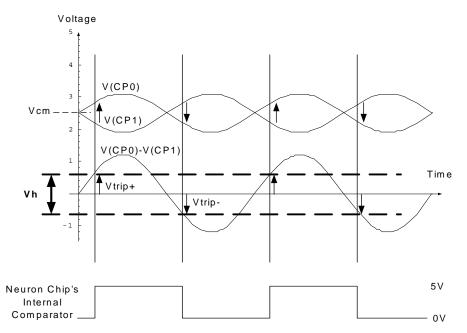

### Figure 2. 32-Pin SOIC and 44-Pin QFP

## **Pin Descriptions**

| Pin Name        | I/O                                        | Pin Function                                                                                                                                                             | CY7C53150<br>TQFP-64 Pin No.                                            | CY7C53120xx<br>SOIC-32 Pin No. | CY7C53120xx<br>TQFP-44 Pin No.                     |

|-----------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------|----------------------------------------------------|

| CLK1            | Input                                      | Oscillator connection or external clock input.                                                                                                                           | 24                                                                      | 15                             | 15                                                 |

| CLK2            | Output                                     | <b>Oscillator connection</b> . Leave open when external clock is input to CLK1. Maximum of one external load.                                                            | 23                                                                      | 14                             | 14                                                 |

| RESET           | I/O (Built-In<br>Pull up)                  | <b>Reset pin (active LOW)</b> . <b>Note</b> The allowable external capacitance connected to the RESET pin is 100–1000 pF.                                                | 6                                                                       | 1                              | 40                                                 |

| SERVICE         | I/O (Built-In<br>Configurable<br>Pull up)  | <b>Service pin (active LOW)</b> . Alternates between input and output at a 76-Hz rate.                                                                                   | 17                                                                      | 8                              | 5                                                  |

| 100–103         | I/O                                        | Large current-sink capacity (20 mA).<br>General I/O port. The output of timer/<br>counter 1 may be routed to IO0. The output<br>of Timer/Counter 2 may be routed to IO1. | 2, 3, 4, 5                                                              | 7, 6, 5, 4                     | 4, 3, 2, 43                                        |

| 104–107         | I/O (Built-In<br>Configurable<br>Pull ups) | <b>General I/O port</b> . The input to<br>Timer/Counter 1 may be derived from one<br>of IO4–IO7. The input to Timer/Counter 2<br>may be derived from IO4.                | 10, 11, 12, 13                                                          | 3, 30, 29, 28                  | 42, 36, 35, 32                                     |

| IO8–IO10        | I/O                                        | General I/O port. May be used for serial communication under firmware control.                                                                                           | 14, 15, 16                                                              | 27, 26, 24                     | 31, 30, 27                                         |

| D0–D7           | I/O                                        | Bidirectional memory data bus.                                                                                                                                           | 43, 42, 38, 37,<br>36, 35, 34, 33                                       | N/A                            | N/A                                                |

| R/W             | Output                                     | Read/write control output for external memory.                                                                                                                           | 45                                                                      | N/A                            | N/A                                                |

| E               | Output                                     | Enable clock control output for external memory.                                                                                                                         | 46                                                                      | N/A                            | N/A                                                |

| A0–A15          | Output                                     | Memory address output port.                                                                                                                                              | 64, 63, 62, 61, 60,<br>59, 58, 57, 56, 55,<br>54, 53, 52, 51, 50,<br>47 | N/A                            | N/A                                                |

| V <sub>DD</sub> | Input                                      | <b>Power input (5V nom)</b> . All V <sub>DD</sub> pins must be connected together externally.                                                                            | 7, 20, 22, 26,<br>40, 41, 44                                            | 2, 11, 12,<br>18, 25, 32       | 9, 10, 19,<br>29, 38, 41                           |

| V <sub>SS</sub> | Input                                      | <b>Power input (0V, GND)</b> . All V <sub>SS</sub> pins must be connected together externally.                                                                           | 8,19, 21, 25, 39                                                        | 9, 13, 16, 23, 31              | 7,13, 16, 26, 37                                   |

| Vpp             | Input                                      | In-circuit test mode control. If Vpp is high when RESET is asserted, the I/O, address and data buses become Hi-Z.                                                        | 9                                                                       | 10                             | 8                                                  |

| CP0–CP4         | Communication<br>Network<br>Interface      | Bidirectional port supporting communi-<br>cations in three modes.                                                                                                        | 28, 29, 30, 31, 32                                                      | 19, 20, 17, 21, 22             | 20, 21, 18, 24, 25                                 |

| NC              |                                            | <b>No connect</b> . Must not be connected on the user's PC board, since they may be connected internal to the chip.                                                      | 1, 18, 27, 48, 49                                                       | N/A                            | 1, 6, 11, 12, 17,<br>22, 23, 28, 33, 34,<br>39, 44 |

## **Memory Usage**

All Neuron chips require system firmware to be present when they are powered up. In the case of the CY7C53120 family, this firmware is preprogrammed in the factory in an on-chip ROM. In the case of the CY7C53150, the system firmware must be present in the first 16 KB of an off-chip nonvolatile memory such as Flash, EPROM, EEPROM, or NVRAM. These devices must be programmed in a device programmer before board assembly. Because the system firmware implements the network protocol, it cannot itself be downloaded over the network.

For the CY7C53120 family, the user application program is stored in on-chip Flash memory. It may be programmed using a device programmer before board assembly, or may be downloaded and updated over the LonTalk network from an external network management tool.

For the CY7C53150, the user application program is stored in on-chip Flash Memory and also in off-chip memory. The user program may initially be programmed into the off-chip memory device using a device programmer.

## **Flash Memory Retention and Endurance**

Data and code stored in Flash Memory is guaranteed to be retained for at least 10 years for programming temperature range of  $-25^{\circ}$ C to  $85^{\circ}$ C.

The Flash Memory can typically be written 100,000 times without any data loss.<sup>[5]</sup> An erase/write cycle takes 20 ms. The system firmware extends the effective endurance of Flash memory in two ways. If the data being written to a byte of Flash memory is the same as the data already present in that byte, the firmware does not perform the physical write. So for example, an application that sets its own address in Flash memory after every reset does not use up any write cycles if the address has not changed. In addition, system firmware version 13.1 or higher is able to aggregate writes to eight successive address locations into a single write for CY7C53120E4 devices. For example, if 4 KB of code is downloaded over the network, the firmware would execute only 512 writes rather than 4,096.

### 40 MHz 3120 Operation

The CY7C53120E4-40 device was designed to run at frequencies up to 40 MHz using an external clock oscillator. It is important to note that external oscillators may typically take on the order of 5 ms to stabilize after power-up. The Neuron chip must be held in reset until the CLK1 input is stable. With some oscillators, this may require the use of a reset-stretching Low-Voltage Detection chip/circuit. Check the oscillator vendor's specification for more information about start-up stabilization times.

## Low Voltage Inhibit Operation

The on-chip Low-voltage Inhibit circuit trips the Neuron chip whenever the V<sub>DD</sub> input is less than 4.1  $\pm$  0.3V. This feature prevents the corruption of nonvolatile memory during voltage drops.

### **Communications Port**

The Neuron chip includes a versatile 5-pin communications port that can be configured in three different ways. In Single-Ended Mode, pin CP0 is used for receiving serial data, pin CP1 for transmitting serial data, and pin CP2 enables an external transceiver. Data is communicated using Differential Manchester encoding.

In Special Purpose Mode, pin CP0 is used for receiving serial data, pin CP1 for transmitting serial data, pin CP2 transmits a bit clock, and pin CP4 transmits a frame clock for use by an external intelligent transceiver. In this mode, the external transceiver is responsible for encoding and decoding the data stream.

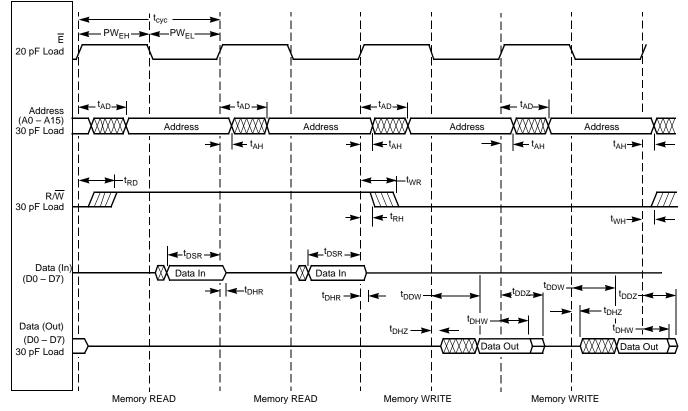

In Differential Mode, pins CP0 and CP1 form a differential receiver with built-in programmable hysteresis and low pass filtering. Pins CP2 and CP3 form a differential driver. Serial data is communicated using Differential Manchester encoding. The following tables describe the communications port when used in Differential Mode.

## **Programmable Hysteresis Values**

(Expressed as differential peak-to-peak voltages in terms of V<sub>DD</sub>)

| Hysteresis <sup>[6]</sup> | V <sub>hys</sub> Min  | V <sub>hys</sub> Typ  | V <sub>hys</sub> Max  |

|---------------------------|-----------------------|-----------------------|-----------------------|

| 0                         | 0.019 V <sub>DD</sub> | 0.027 V <sub>DD</sub> | 0.035 V <sub>DD</sub> |

| 1                         | 0.040 V <sub>DD</sub> | 0.054 V <sub>DD</sub> | 0.068 V <sub>DD</sub> |

| 2                         | 0.061 V <sub>DD</sub> | 0.081 V <sub>DD</sub> | 0.101 V <sub>DD</sub> |

| 3                         | 0.081 V <sub>DD</sub> | 0.108 V <sub>DD</sub> | 0.135 V <sub>DD</sub> |

| 4                         | 0.101 V <sub>DD</sub> | 0.135 V <sub>DD</sub> | 0.169 V <sub>DD</sub> |

| 5                         | 0.121 V <sub>DD</sub> | 0.162 V <sub>DD</sub> | 0.203 V <sub>DD</sub> |

| 6                         | 0.142 V <sub>DD</sub> | 0.189 V <sub>DD</sub> | 0.236 V <sub>DD</sub> |

| 7                         | 0.162 V <sub>DD</sub> | 0.216 V <sub>DD</sub> | 0.270 V <sub>DD</sub> |

### Programmable Glitch Filter Values<sup>[7]</sup>

(Receiver (end-to-end) filter values expressed as transient pulse suppression times)

| Filter (F) | Min | Тур  | Max  | Unit |

|------------|-----|------|------|------|

| 0          | 10  | 75   | 140  | ns   |

| 1          | 120 | 410  | 700  | ns   |

| 2          | 240 | 800  | 1350 | ns   |

| 3          | 480 | 1500 | 2600 | ns   |

### Receiver<sup>[8]</sup> (End-to-End) Absolute Asymmetry

(Worst case across hysteresis)

| Filter (F) | Max (t <sub>PLH</sub> – t <sub>PHL</sub> ) | Unit |

|------------|--------------------------------------------|------|

| 0          | 35                                         | ns   |

| 1          | 150                                        | ns   |

| 2          | 250                                        | ns   |

| 3          | 400                                        | ns   |

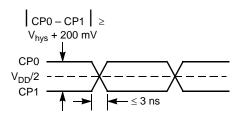

### Figure 3. Receiver Input Waveform

### **Differential Receiver (End-to-End) Absolute** Symmetry<sup>[9, 10]</sup>

| Filter (F) | Hysteresis (H) | Max (t <sub>PLH</sub> – t <sub>PHL</sub> ) | Unit |

|------------|----------------|--------------------------------------------|------|

| 0          | 0              | 24                                         | ns   |

#### Notes

- 6. Hysteresis values are on the condition that the input signal swing is 200 mV greater than the programmed value.

- Hysterests Values are on the conductor that the input signal swing is 200 my greater than the programmed value.

Must be disabled if data rate is 1.25 Mbps or greater.

Receiver input, V<sub>D</sub> = V<sub>CP0</sub> V<sub>CP1</sub>, at least 200 mV greater than hysteresis levels. See Figure 3.

CPO and CP1 inputs each 0.60 Vp p, 1.25 MHz sine wave 180° out of phase with each other as shown in Figure 10. V<sub>DD</sub> = 5.00 V ± 5%.

t<sub>PLL</sub>: Time from input switching states from low to high to output switching states. t<sub>PHL</sub>: Time from input switching states from high to low to output switching states.

## Electrical Characteristics (V<sub>DD</sub> = 4.5V–5.5V)

| Parameter            | Description                                                                                                                                                                                                                                                                                                                                                   | Min                                                                                                         | Тур | Max                                    | Unit |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|----------------------------------------|------|

| V <sub>IL</sub>      | Input Low Voltage<br>IO0–IO10, CP0, CP3, CP4, SERVICE, D0-D7, RESET<br>CP0, CP1 (Differential)                                                                                                                                                                                                                                                                |                                                                                                             |     | 0.8<br>Programmable                    | V    |

| V <sub>IH</sub>      | Input High Voltage<br>IO0–IO10, CP0, CP3, CP4, SERVICE, D0-D7, RESET<br>CP0, CP1 (Differential)                                                                                                                                                                                                                                                               | 2.0<br>Programmable                                                                                         |     |                                        | V    |

| V <sub>OL</sub>      | Low-Level Output Voltage<br>$I_{out} < 20 \ \mu A$<br>Standard Outputs ( $I_{OL} = 1.4 \ mA$ ) <sup>[11]</sup><br>High Sink (IO0–IO3), <u>SERVICE</u> , <u>RESET</u> ( $I_{OL} = 20 \ mA$ )<br>High Sink (IO0–IO3), SERVICE, RESET ( $I_{OL} = 10 \ mA$ )<br>Maximum Sink (CP2, CP3) ( $I_{OL} = 40 \ mA$ )<br>Maximum Sink (CP2, CP3) ( $I_{OL} = 15 \ mA$ ) | -<br>-<br>-<br>-                                                                                            |     | 0.1<br>0.4<br>0.8<br>0.4<br>1.0<br>0.4 | V    |

| V <sub>OH</sub>      | High-Level Output Voltage<br>$I_{out} < 20 $ μA<br>Standard Outputs ( $I_{OH} = -1.4 $ mA) <sup>[11]</sup><br>High Sink (IO0 – IO3), SERVICE ( $I_{OH} = -1.4$ mA)<br>Maximum Source (CP2, CP3) ( $I_{OH} = -40$ mA)<br>Maximum Source (CP2, CP3) ( $I_{OH} = -15$ mA)                                                                                        | $\begin{array}{c} V_{DD} - 0.1 \\ V_{DD} - 0.4 \\ V_{DD} - 0.4 \\ V_{DD} - 1.0 \\ V_{DD} - 0.4 \end{array}$ |     | <br>                                   | V    |

| V <sub>hys</sub>     | Hysteresis (Excluding CLK1)                                                                                                                                                                                                                                                                                                                                   | 175                                                                                                         | _   | —                                      | mV   |

| l <sub>in</sub>      | Input Current (Excluding Pull Ups) $(V_{SS} \text{ to } V_{DD})^{[12]}$                                                                                                                                                                                                                                                                                       | —                                                                                                           | _   | ±10                                    | μA   |

| I <sub>pu</sub>      | Pull Up Source Current (V <sub>out</sub> = 0 V, Output = High-Z) <sup>[12]</sup>                                                                                                                                                                                                                                                                              | 60                                                                                                          |     | 260                                    | μA   |

| I <sub>DD</sub>      | Operating Mode Supply Current <sup>[13]</sup> 40-MHz Clock <sup>[14]</sup><br>20-MHz Clock<br>10-MHz Clock<br>5-MHz Clock<br>2.5-MHz Clock<br>1.25-MHz Clock<br>0.625-MHz Clock <sup>[14]</sup>                                                                                                                                                               | -<br>-<br>-<br>-<br>-<br>-                                                                                  |     | 55<br>32<br>20<br>12<br>8<br>7<br>3    | mA   |

| I <sub>DDsleep</sub> | Sleep Mode Supply Current <sup>[1, 13]</sup>                                                                                                                                                                                                                                                                                                                  | —                                                                                                           |     | 100                                    | μΑ   |

## LVI Trip Point (V<sub>DD</sub>)

| Part Number                             | Min | Тур | Max | Unit |

|-----------------------------------------|-----|-----|-----|------|

| CY7C53120E2, CY7C53120E4, and CY7C53150 | 3.8 | 4.1 | 4.4 | V    |

### Notes

- 11. Standard outputs are IO4–IO10. CP0, CP1, and CP4. (RESET is an open drain input/output. CLK2 must have ≤ 15 pF load.) For CY7C53150, standard outputs also include A0–A15, D0–D7, E, and R/W.

- also include A0-A15, D0-D7, E, and K/W.

12. IO4-IO7 and SERVICE have configurable pull ups. RESET has a permanent pull up.

13. Supply current measurement conditions: V<sub>DD</sub> = 5V, all outputs under no-load conditions, all inputs ≤ 0.2V or ≥ (V<sub>DD</sub> 0.2V), configurable pull ups off, crystal oscillator clock input, differential receiver disabled. The differential receiver adds approximately 200 µA typical and 600 µA maximum when enabled. It is enabled on either of the following conditions:

Neuron chip in Operating mode and Comm Port in Differential mode.

Neuron chip in Sleep mode and Comm Port in Differential mode and Comm Port Wake-up not masked.

14. Supported through an external oscillator only.

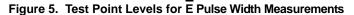

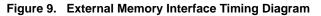

## External Memory Interface Timing — CY7C53150, $V_{DD} \pm 10\%$ (V<sub>DD</sub> = 4.5V to 5.5 V, T<sub>A</sub> = -40°C to + 85°C <sup>[2]</sup>)

| Parameter        | Description                                                                                  | Min           | Max             | Unit |

|------------------|----------------------------------------------------------------------------------------------|---------------|-----------------|------|

| t <sub>cyc</sub> | Memory Cycle Time (System Clock Period) <sup>[15]</sup>                                      | 100           | 3200            | ns   |

| PW <sub>EH</sub> | Pulse Width, E High <sup>[16]</sup>                                                          | $t_{cyc}/2-5$ | $t_{cyc}/2 + 5$ | ns   |

| PW <sub>EL</sub> | Pulse Width, E Low <sup>[16]</sup>                                                           | $t_{cyc}/2-5$ | $t_{cyc}/2 + 5$ | ns   |

| t <sub>AD</sub>  | Delay, E High to Address Valid <sup>[20]</sup>                                               | —             | 35              | ns   |

| t <sub>AH</sub>  | Address Hold Time After E High <sup>[20]</sup>                                               | 10            | —               | ns   |

| t <sub>RD</sub>  | Delay, $\overline{E}$ High to R/W Valid Read <sup>[20]</sup>                                 | —             | 25              | ns   |

| t <sub>RH</sub>  | R/W Hold Time Read After E High                                                              | 5             | —               | ns   |

| t <sub>WR</sub>  | Delay, $\overline{E}$ High to R/ $\overline{W}$ Valid Write                                  | —             | 25              | ns   |

| t <sub>WH</sub>  | R/W Hold Time Write After E High                                                             | 5             | —               | ns   |

| t <sub>DSR</sub> | Read Data Setup Time to E High                                                               | 15            | —               | ns   |

| t <sub>DHR</sub> | Data Hold Time Read After E High                                                             | 0             | —               | ns   |

| t <sub>DHW</sub> | Data Hold Time Write After E High <sup>[17, 18]</sup>                                        | 10            | —               | ns   |

| t <sub>DDW</sub> | Delay, E Low to Data Valid                                                                   | —             | 12              | ns   |

| t <sub>DHZ</sub> | Data Three State Hold Time After $\overline{E}$ Low <sup>[19]</sup>                          | 0             |                 | ns   |

| t <sub>DDZ</sub> | Delay, E High to Data Three-State <sup>[18]</sup>                                            | —             | 42              | ns   |

| t <sub>acc</sub> | External Memory Access Time ( $t_{acc} = t_{cyc} - t_{AD} - t_{DSR}$ ) at 20-MHz input clock | 50            | —               | ns   |

## **Differential Transceiver Electrical Characteristics**

| Characteristic                                                            | Min                        | Max                       | Unit |

|---------------------------------------------------------------------------|----------------------------|---------------------------|------|

| Receiver Common Mode Voltage Range to maintain hysteresis <sup>[21]</sup> | 1.2                        | V <sub>DD</sub> – 2.2     | V    |

| Receiver Common Mode Range to operate with unspecified hysteresis         | 0.9                        | V <sub>DD</sub> – 1.75    | V    |

| Input Offset Voltage                                                      | -0.05V <sub>hys</sub> - 35 | 0.05V <sub>hys</sub> + 35 | mV   |

| Propagation Delay (F = 0, $V_{ID} = V_{hys}/2 + 200 \text{ mV}$ )         | —                          | 230 ns                    | ns   |

| Input Resistance                                                          | 5                          | —                         | MΩ   |

| Wake-up Time                                                              | —                          | 10                        | μS   |

| Differential Output Impedance for CP2 and CP3 <sup>[22]</sup>             |                            | 35                        | Ω    |

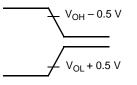

### Figure 4. Signal Loading for Timing Specifications Unless Otherwise Specified

TEST SIGNAL

$C_L = 20 \text{ pF for } \overline{E}$   $C_L = 30 \text{ pF for A0-A15, D0-D7, and } R/\overline{W}$   $C_L = 50 \text{ pF for all other signals}$

### Notes

15.  $t_{cyc} = 2(1/f)$ , where f is the input clock (CLK1) frequency (20, 10, 5, 2.5, 1.25, or 0.625 MHz). 16. Refer to Figure 5 for detailed measurement information.

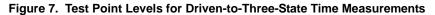

16. Refer to Figure 5 for detailed measurement information. 17. The data hold parameter,  $t_{DHW}$ , is measured to the disable levels shown in Figure 7, rather than to the traditional data invalid levels. 18. Refer to Figure 8 and Figure 7 for detailed measurement information. 19. The three-state condition is when the device is not actively driving data. Refer to Figure 4 and Figure 7 for detailed measurement information. 20. To meet the timing above for 20-MHz operation, the loading on A0–A15, D0–D7, and RW is 30 pF. Loading on E is 20 pF. 21. Common mode voltage is defined as the average value of the waveform at each input at the time switching occurs. 22.  $Z_0 = |V[CP2]-V[CP3]|/40$  mA for 4.75  $\leq V_{DD} \leq 5.25V$ .

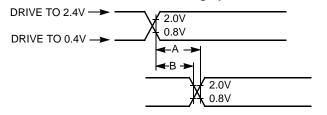

### Figure 6. Drive Levels and Test Point Levels for Timing Specifications Unless Otherwise Specified

A — Signal valid-to-signal valid specification (maximum or minimum)

B — Signal valid-to-signal invalid specification (maximum or minimum)

$V_{OH}\,{-}\,$  Measured high output drive level  $V_{OL}\,{-}\,$  Measured low output drive level

### Figure 8. Signal Loading for Driven-to-Three-State Time Measurements

Document #: 38-10001 Rev. \*F

Page 10

### Figure 10. Differential Receiver Input Hysteresis Voltage Measurement Waveforms

Common-Mode voltage: Vcm = (V(CP0) + V(CP1)) / 2

Hysteresis Voltage: Vh = [Vtrip+] - [Vtrip-]

| Part Number                       | Flash<br>(KB) | ROM<br>(KB) | Firmware<br>Version | Max Input<br>Clock<br>(MHz) | Package<br>Name | Package Type                                         |

|-----------------------------------|---------------|-------------|---------------------|-----------------------------|-----------------|------------------------------------------------------|

| CY7C53150-20AXI                   | 0.5           | 0           | N/A                 | 20 <sup>[25]</sup>          | A64SA           | 64-lead Thin Plastic Quad Flat Pack                  |

| CY7C53150-20AXIT                  | 0.5           | 0           | N/A                 | 20 <sup>[25]</sup>          | A64SA           | 64-lead Thin Plastic Quad Flat Pack<br>Tape and Reel |

| CY7C53120E2-10SXI <sup>[24]</sup> | 2             | 10          | 6                   | 10                          | S32.45          | 32-lead (450 mil) Molded SOIC                        |

| CY7C53120E4-40SXI <sup>[26]</sup> | 4             | 12          | 12                  | 40                          | S32.45          | 32-lead (450 mil) Molded SOIC                        |

| CY7C53120E4-40SXIT                | 4             | 12          | 12                  | 40                          | S32.45          | 32-lead (450 mil) Molded SOIC Tape and Reel          |

| CY7C53120E2-10AXI <sup>[24]</sup> | 2             | 10          | 6                   | 10                          | A44             | 44-lead Thin Plastic Quad Flat Pack                  |

| CY7C53120E4-40AXI <sup>[26]</sup> | 4             | 12          | 12                  | 40                          | A44             | 44-lead Thin Plastic Quad Flat Pack                  |

## **Ordering Information**<sup>[23]</sup>

Notes

23. All parts contain 2 KB of SRAM.

- 24. CY7C53120E2 firmware is bit-for-bit identical with Motorola MC143120E2 firmware.

- 25. CY7C53150 may be used with 20-MHz input clock only if the firmware in external memory is version 13 or later.

26. CY7C53120E4 requires upgraded LonBuilder® and NodeBuilder® software.

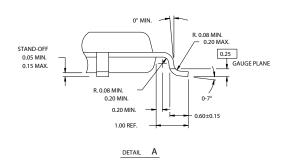

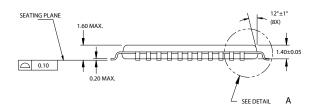

## **Package Diagrams**

Figure 11. 44-Pin Thin Plastic Quad Flat Pack A44

NOTE:

#### . .

1. JEDEC STD REF MS-026

2. BODY LENGTH DIMENSION DOES NOT INCLUDE MOLD PROTRUSION/END FLASH MOLD PROTRUSION/END FLASH SHALL NOT EXCEED 0.0098 in (0.25 mm) PER SIDE BODY LENGTH DIMENSIONS ARE MAX PLASTIC BODY SIZE INCLUDING MOLD MISMATCH

3. DIMENSIONS IN MILLIMETERS

51-85064-\*C

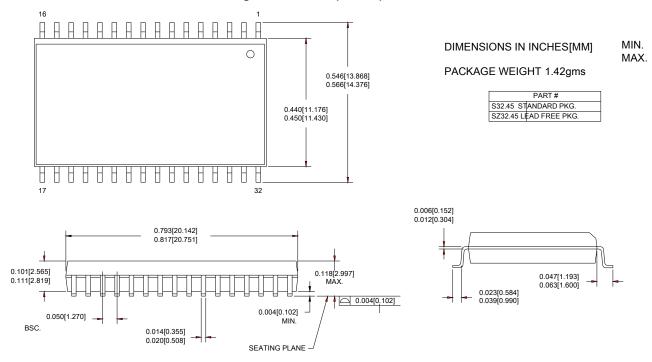

## Package Diagrams (continued)

## Package Diagrams (continued)

. •

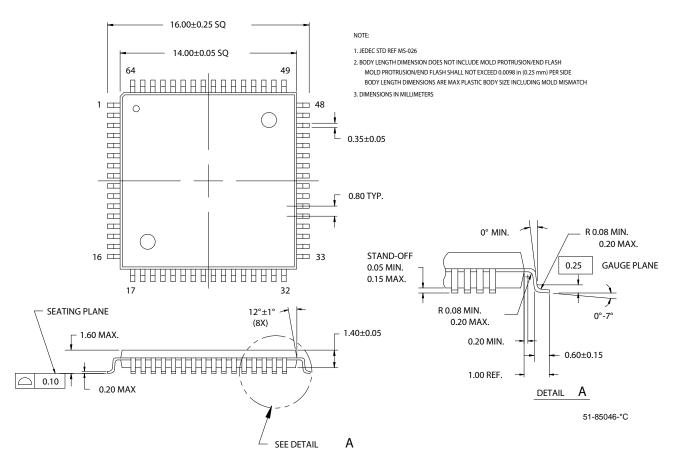

Figure 13. 32-Pin (450-Mil) SOIC S32.45

51-85081-\*C

Document #: 38-10001 Rev. \*F

## **Document History Page**

| Document Title: CY7C53150, CY7C53120 Neuron Chip Network Processor<br>Document Number: 38-10001 |         |                    |                    |                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REV.                                                                                            | ECN NO. | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                    |

| **                                                                                              | 111472  | 11/28/01           | DSG                | Change from Spec number: 38-00891 to 38-10001                                                                                                                            |

| *A                                                                                              | 111990  | 02/06/02           | CFB                | Changed the max. cur rent values<br>Specified the Flash endurance of "100K typical" with reference to qual report<br>Fixed some incorrect footnotes and figure numbering |

| *В                                                                                              | 114465  | 04/24/02           | КВО                | Added Sleep Metastability footnote<br>Added Junction Temperature footnote<br>Added maximum sleep current footnote<br>Changed "EEPROM" references to "Flash Memory"       |

| *C                                                                                              | 115269  | 04/26/02           | KBO                | Repositioned Note 3                                                                                                                                                      |

| *D                                                                                              | 124450  | 03/25/03           | КВО                | Removed Note 2 regarding data retention<br>Removed Note 16 regarding max sleep current<br>Changed the system image firmware version from V12 to V13.1                    |

| *E                                                                                              | 837840  | 3/14/07            | BOO                | Implemented new template. Modified the Ordering Information table; added an "X" to indicate the part numbers are Pb-free; two tape-and-reel options are available now.   |

| *F                                                                                              | 2811866 | 11/20/2009         | TGE                | Updated template.<br>Modified Note 1 to add reference to the Neuron TRM.                                                                                                 |

## Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

### Products

| PSoC             | psoc.cypress.com     |

|------------------|----------------------|

| Clocks & Buffers | clocks.cypress.com   |

| Wireless         | wireless.cypress.com |

| Memories         | memory.cypress.com   |

| Image Sensors    | image.cypress.com    |

© Cypress Semiconductor Corporation, 2001-2009. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document #: 38-10001 Rev. \*F

#### Revised November 20, 2009

Page 15

All products and company names mentioned in this document may be the trademarks of their respective holders.