# Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

Hardware Design Guidelines

December 2007

Document Number: 252817-008US December 2007

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting Intel's Web Site.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See http://www.intel.com/products/processor\_number for details.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2007, Intel Corporation. All rights reserved.

## Contents

| 1.0 | Intro | duction                                                                          | 9    |

|-----|-------|----------------------------------------------------------------------------------|------|

|     | 1.1   | About this Document                                                              | 9    |

|     | 1.2   | Related Documentation                                                            |      |

|     | 1.3   | Acronyms and Abbreviations                                                       |      |

|     | 1.4   | Overview                                                                         |      |

|     | 1.5   | Key Features                                                                     |      |

|     | 1.6   | Typical Applications                                                             | . 14 |

| 2.0 | Syste | m Architecture                                                                   | 15   |

|     | 2.1   | System Architecture Description                                                  |      |

|     | 2.2   | System Memory Map                                                                |      |

| 3.0 | Gono  | ral Hardware Design Considerations                                               |      |

| 3.0 | 3.1   | PC133 SDRAM Interface                                                            |      |

|     | 3.1   | 3.1.1 SDRAM Interface Signals                                                    |      |

|     |       | 3.1.2 SDRAM Block Diagrams                                                       |      |

|     |       | 3.1.3 SDRAM block Diagrams                                                       |      |

|     | 3.2   | Expansion Bus                                                                    |      |

|     | 5.2   | 3.2.1 Expansion Bus Interface Signals                                            |      |

|     |       | 3.2.2 Configuration Straps                                                       |      |

|     |       | 3.2.2.1 User-Configurable Field                                                  |      |

|     |       | 3.2.3 Flash Interface                                                            |      |

|     |       | 3.2.4 SRAM Interface                                                             |      |

|     |       | 3.2.5 Design Notes                                                               |      |

|     | 3.3   | UART Interface                                                                   |      |

|     | 0.0   | 3.3.1 UART Interface Signals                                                     |      |

|     |       | 3.3.2 High-Speed UART                                                            |      |

|     |       | 3.3.3 Console UART                                                               |      |

|     | 3.4   | MII Interface                                                                    |      |

|     |       | 3.4.1 Ethernet Interface Signals                                                 | 33   |

|     |       | 3.4.2 MII Block Diagram                                                          |      |

|     | 3.5   | GPIO Interface                                                                   | 35   |

|     |       | 3.5.1 GPIO Interface Signals                                                     | 36   |

|     |       | 3.5.2 Design Notes                                                               |      |

|     | 3.6   | I <sup>2</sup> C Interface                                                       |      |

|     |       | 3.6.1 Pull-Ups and Pull-Downs                                                    | 38   |

|     |       | 3.6.2 Layout Notes                                                               | 38   |

|     | 3.7   | USB Interface                                                                    |      |

|     |       | 3.7.1 Signals                                                                    |      |

|     |       | 3.7.2 USB Interface                                                              |      |

|     |       | 3.7.3 Design Notes                                                               |      |

|     | 3.8   | UTOPIA Interface                                                                 |      |

|     |       | 3.8.1 Interface Signals                                                          |      |

|     |       | 3.8.2 UTOPIA-2 Interface Block Diagram                                           |      |

|     | 3.9   | HSS Interface                                                                    |      |

|     |       | 3.9.1 Interface Signals                                                          |      |

|     | 2 10  | 3.9.2 HSS Interface Block Diagram                                                |      |

|     | 3.10  | PCI Interface                                                                    |      |

|     |       | 3.10.1 PCI Interface Signals                                                     |      |

|     |       | <ul><li>3.10.2 PCI Interface Block Diagram</li><li>3.10.3 Design Notes</li></ul> |      |

|     | 3.11  | JTAG Interface                                                                   |      |

|     | 3.11  |                                                                                  | 40   |

|     |            | 3.11.1 Interface Signals                     |

|-----|------------|----------------------------------------------|

|     |            | 3.11.2 Pull-Up/Down Resistors                |

|     | 3.12       | Clock                                        |

|     |            | 3.12.1 Clock Signals                         |

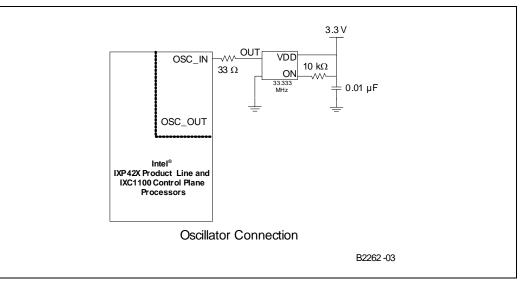

|     |            | 3.12.2 Using Oscillator                      |

|     |            | 3.12.3 Design Notes                          |

|     | 2 1 2      | 3.12.4 Block Diagram                         |

|     | 3.13       | Power                                        |

|     |            | 3.13.1 Power supply Requirements             |

|     |            | 3.13.2 +3.3 V DC                             |

|     |            | 3.13.3 + 1.3 V DC                            |

|     |            |                                              |

| 4.0 | PBGA       | A Package                                    |

|     | 4.1        | PBGA Package Overview55                      |

|     | 4.2        | Signal Grouping55                            |

| 5.0 | Gene       | eral PCB Guide                               |

|     | 5.1        | PCB Overview                                 |

|     | 5.2        | General Recommendations                      |

|     | 5.3        | Component Selection                          |

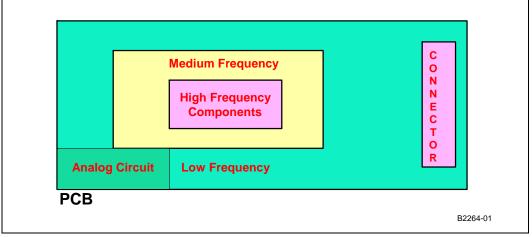

|     | 5.4        | Component Placement                          |

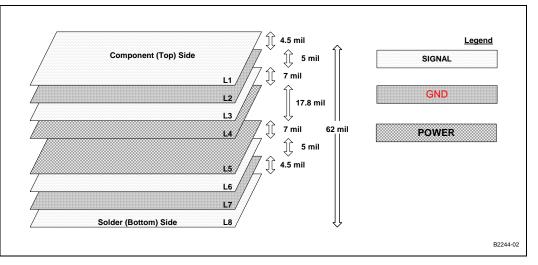

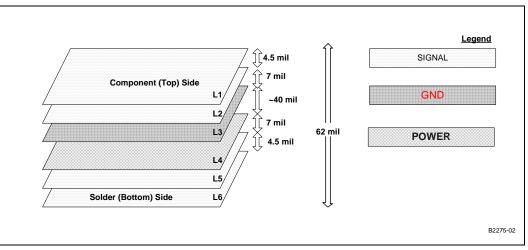

|     | 5.5        | Stack Up Selection                           |

| 6.0 | Cono       | eral Layout and Routing Guide                |

| 0.0 | 6.1        | Overview                                     |

|     | 6.2        | General Layout Guidelines                    |

|     | 0.2        | 6.2.1 General Component Spacing              |

|     | 6.3        | General Routing Guides                       |

|     | 0.5        | 6.3.1 Clock Signal Considerations            |

|     |            | 6.3.2 LAN Signal Considerations              |

|     |            | 6.3.3 USB Considerations                     |

|     |            | 6.3.4 Crosstalk                              |

|     |            | 6.3.5 EMI Design Considerations              |

|     |            | 6.3.6 Trace Impedance                        |

|     |            | 6.3.7 Power and Decoupling                   |

|     | 6.4        | Devices' Decoupling70                        |

|     |            | 6.4.1 General Decoupling/Bypass Guidelines70 |

| 7.0 | Critic     | cal Routing Topologies                       |

|     | 7.1        | PC133 SDRAM Topologies                       |

|     |            | 7.1.1 PC 133 SDRAM Clock                     |

|     | 7.2        | PCI Topologies                               |

|     |            | 7.2.1 Trace Length Limits                    |

|     |            | 7.2.2 Routing Guidelines                     |

|     |            | 7.2.3 Signal Loading                         |

| А   | Desi       | ign Checklist                                |

| ~   | A.1        | Checklist                                    |

|     | A.1<br>A.2 | SDRAM Interface                              |

|     | A.2        | PCI Interface                                |

|     | A.4        | High-Speed Serial Interface                  |

|     | A.5        | MII Interface                                |

|     | A.6        | UTOPIA-2 Interface                           |

|     | A.7        | Expansion Bus Interface                      |

|     |            | A.7.1 Expansion Bus Configuration Strappings |

|     | A.8        | UART Interface                               |

Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Hardware Design Guidelines  $\ensuremath{4}$

|    | A.9  | USB Interface                                                                                         | 89 |

|----|------|-------------------------------------------------------------------------------------------------------|----|

|    | A.10 | Oscillator Interface                                                                                  | 89 |

|    |      | A.10.1 Oscillator Interface                                                                           | 89 |

|    | A.11 | GPIO Interface                                                                                        | 90 |

|    | A.12 | JTAG Interface                                                                                        | 90 |

|    | A.13 | System Interface                                                                                      | 90 |

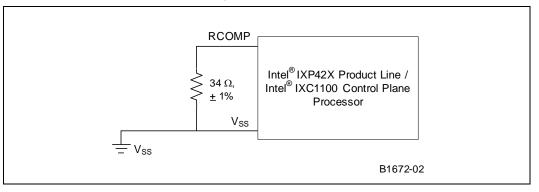

|    |      | A.13.1 RCOMP Pin Requirements                                                                         | 91 |

|    | A.14 | Power Interface                                                                                       |    |

|    | A.15 | V <sub>CCPLL1</sub> , V <sub>CCPLL2</sub> , V <sub>CCOSCP</sub> , V <sub>CCOSC</sub> Pin Requirements | 92 |

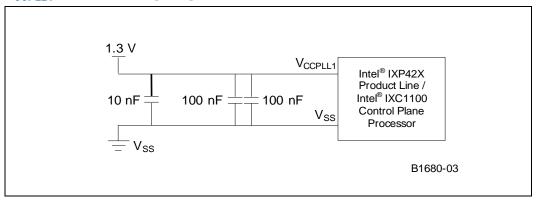

|    |      | A.15.1 V <sub>CCPLL1</sub> Requirement                                                                |    |

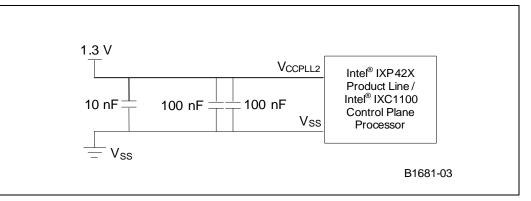

|    |      | A.15.2 V <sub>CCPLL2</sub> Requirement                                                                | 92 |

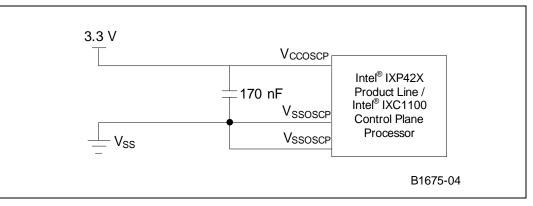

|    |      | A.15.3 V <sub>CCOSCP</sub> Requirement                                                                | 93 |

|    |      | A.15.4 V <sub>CCOSC</sub> Requirement                                                                 | 93 |

|    | A.16 | Common Issues                                                                                         | 94 |

|    | A.17 | Design Considerations                                                                                 | 95 |

| Ju | res  |                                                                                                       |    |

|    | Dev  | ices' Component Block Diagram                                                                         | 14 |

| 2  | Dev  | ices' System Block Diagram                                                                            | 16 |

| 3  | Dua  | I-Bank SDRAM System Block Diagram (x32 Devices)                                                       | 22 |

| ł  | Sing | le Bank SDRAM System Block Diagram (x16 Devices)                                                      | 23 |

| 5  | Dua  | I Bank SDRAM System Block Diagram (x16 Devices)                                                       | 24 |

| 5  | Expa | ansion Bus Flash Interface                                                                            | 28 |

| 7  | Exp  | ansion Bus SRAM Interface                                                                             | 29 |

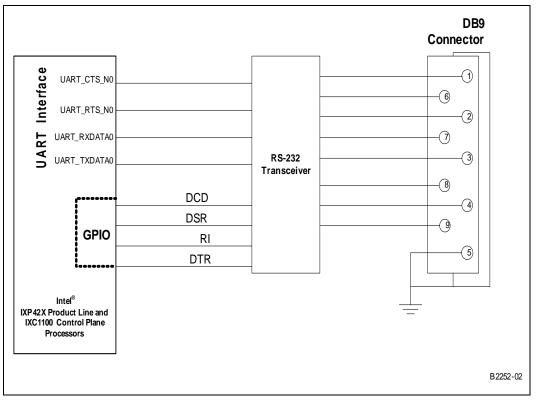

| 3  |      | UART Interface                                                                                        |    |

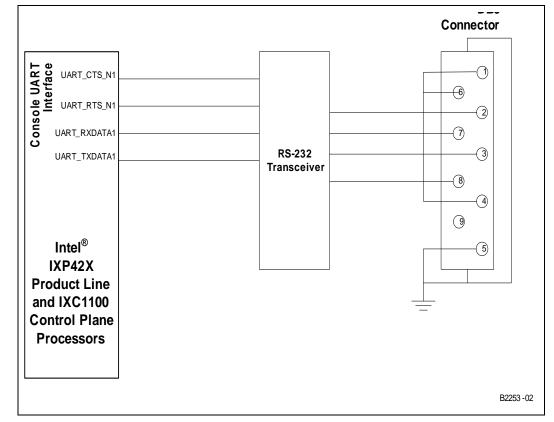

| )  | Con  | sole UART Interface                                                                                   | 32 |

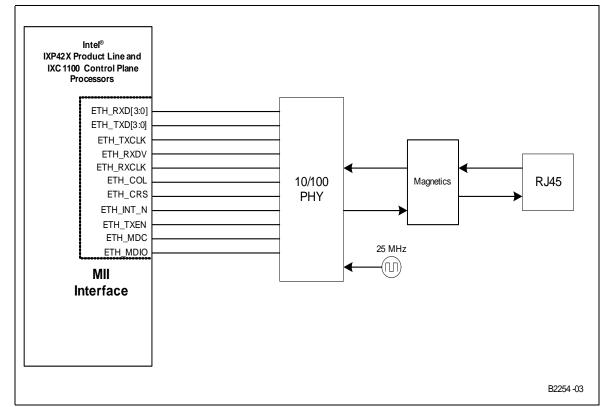

| 0  |      | Block Diagram                                                                                         |    |

### Fia

| yu |                                                                 |    |

|----|-----------------------------------------------------------------|----|

| 1  | Devices' Component Block Diagram                                | 14 |

| 2  | Devices' System Block Diagram                                   |    |

| 3  | Dual-Bank SDRAM System Block Diagram (x32 Devices)              | 22 |

| 4  | Single Bank SDRAM System Block Diagram (x16 Devices)            |    |

| 5  | Dual Bank SDRAM System Block Diagram (x16 Devices)              |    |

| 6  | Expansion Bus Flash Interface                                   |    |

| 7  | Expansion Bus SRAM Interface                                    |    |

| 8  | Fast UART Interface                                             |    |

| 9  | Console UART Interface                                          | 32 |

| 10 | MII Block Diagram                                               |    |

| 11 | I <sup>2</sup> C EEPROM Interface                               |    |

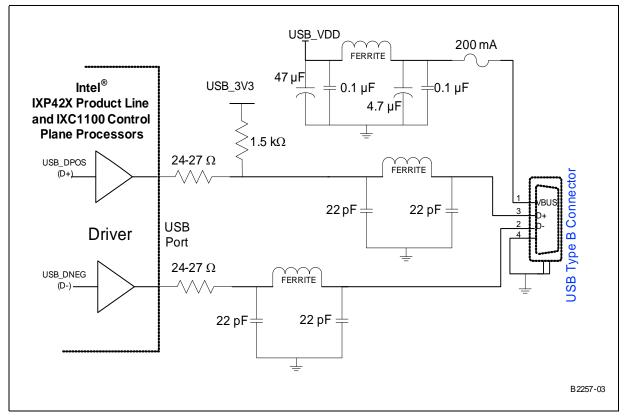

| 12 | USB Interface                                                   |    |

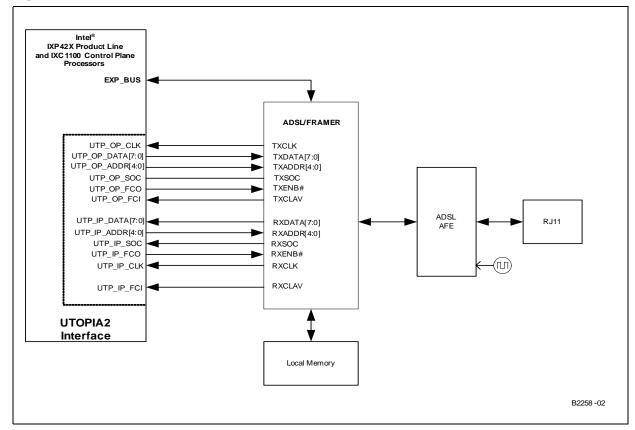

| 13 | UTOPIA Interface                                                |    |

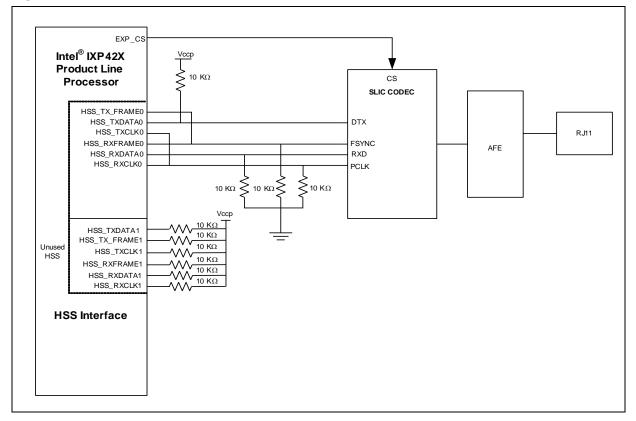

| 14 | HSS Interface                                                   | 44 |

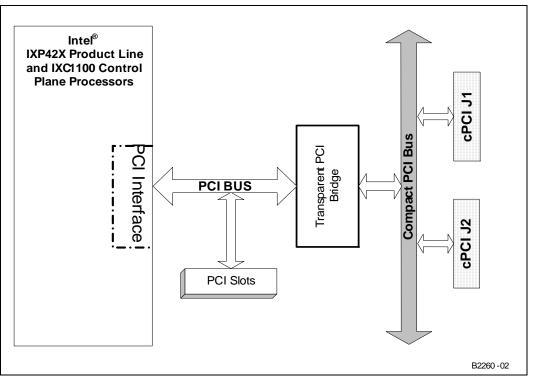

| 15 | PCI Interface                                                   |    |

| 16 | Clock Connections                                               |    |

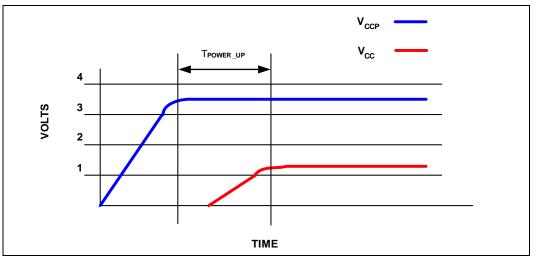

| 17 | Power-up Sequence Timing                                        | 52 |

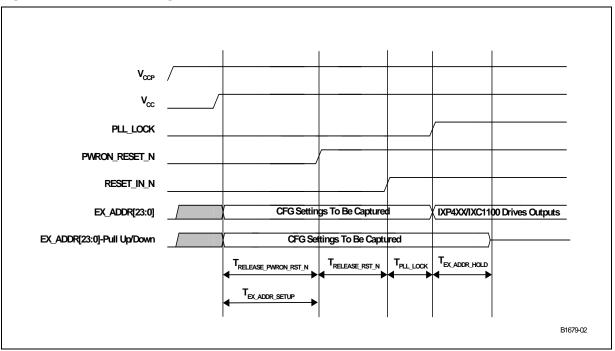

| 18 | Reset Timings                                                   |    |

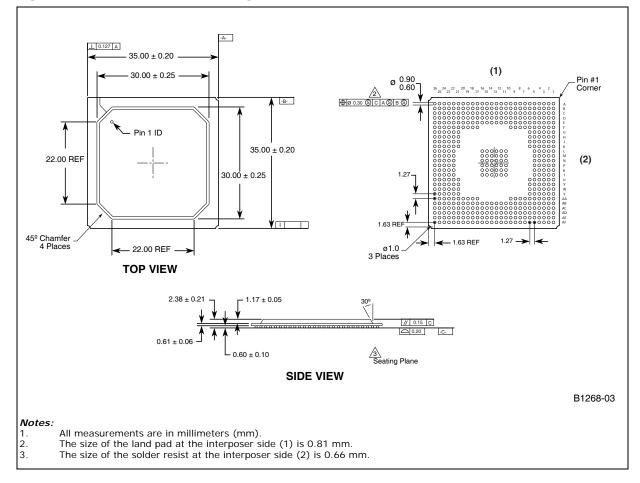

| 19 | 492-Ball PBGA Package                                           |    |

| 20 | Devices' Signals by Function                                    |    |

| 21 | Component Placement on a PCB                                    |    |

| 22 | 8-Layer Stackup                                                 |    |

| 23 | 6-Layer Stackup                                                 |    |

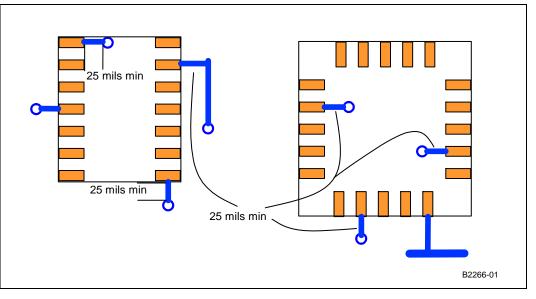

| 24 | Good Design Practice for VIA Hole Placement                     |    |

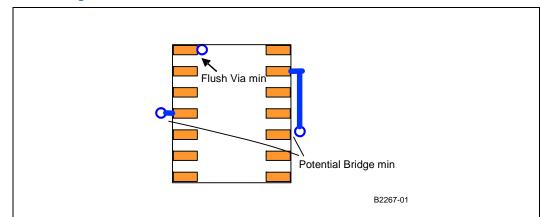

| 25 | Poor Design Practice for VIA Placement                          |    |

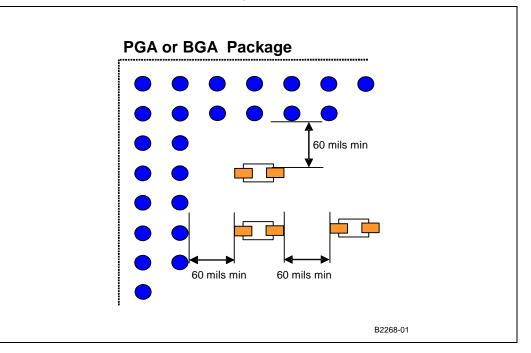

| 26 | Pad-to-Pad Clearance of Passive Components to a PGA or BGA      |    |

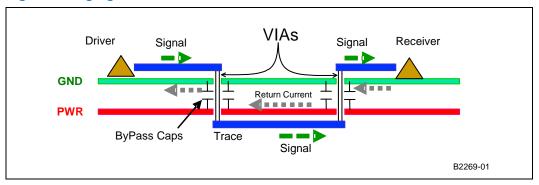

| 27 | Signal Changing Reference Planes                                |    |

| 28 | SDRAM Topology                                                  |    |

| 29 | SDRAM Clock Topology                                            |    |

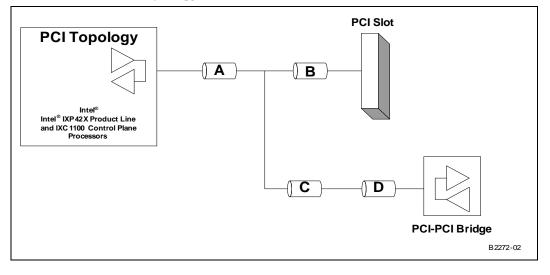

| 30 | PCI Address/Data Topology                                       |    |

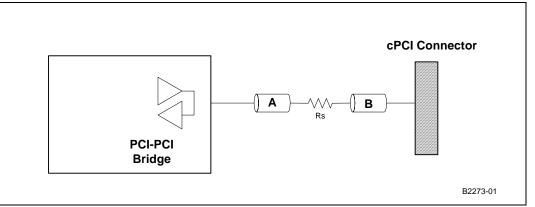

| 31 | PCI Address/Data Topology (PCI Bridge to cPCI Bridge Connector) |    |

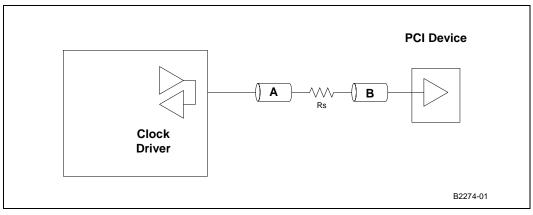

| 32 | PCI Clock Topology                                              |    |

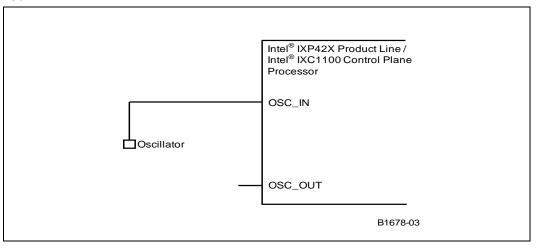

| 33 | Typical Connection to an Oscillator                             |    |

| 34 | RCOMP Pin External Resistor Requirements                        |    |

| 35 | V <sub>CCPLL1</sub> Power Filtering Diagram                     |    |

| 36 | V <sub>CCPLL2</sub> Power Filtering Diagram                     |    |

| 37 | V <sub>CCOSCP</sub> Power Filtering Diagram                     |    |

| 38 | V <sub>CCOSC</sub> Power Filtering Diagram                      | 94 |

### **Tables**

| 1  | Memory Map                                                      | .17 |

|----|-----------------------------------------------------------------|-----|

| 2  | SDRAM Interface Signals                                         | .20 |

| 3  | SDRAM Memory Types                                              | .20 |

| 4  | Expansion Bus Interface Signals                                 | .26 |

| 5  | Expansion Bus Address Description                               | .27 |

| 6  | UART Interface Signals                                          | .29 |

| 7  | Ethernet Interface Signals                                      | .33 |

| 8  | GPIO Interface Signals                                          | .36 |

| 9  | Signals                                                         | .38 |

| 10 | Interface Signals                                               | .40 |

| 11 | PCI Bus Signals                                                 | .45 |

| 12 | JTAG Interface Signals                                          | .48 |

| 13 | Clock Signals                                                   | .49 |

| 14 | Power Pins                                                      | .50 |

| 15 | Reset Timings Table Parameters                                  | .53 |

| 16 | SDRAM Address/Data/Control Routing Guidelines                   | .74 |

| 17 | SDRAM Clock Routing Guidelines                                  | .75 |

| 18 | PCI Address/Data Routing Guidelines                             | .76 |

| 19 | PCI Address/Data Routing Guidelines                             | .77 |

| 20 | PCI Clock Routing Guidelines                                    | .78 |

| 21 | Signal Type Definitions                                         | .81 |

| 22 | SDRAM Interface                                                 | .82 |

| 23 | PCI Interface                                                   | .82 |

| 24 | High-Speed, Serial Interface 0                                  | .83 |

| 25 | High-Speed, Serial Interface 1                                  | .83 |

| 26 | MII Interfaces                                                  | .84 |

| 27 | UTOPIA-2 Interface                                              | .85 |

| 28 | Expansion Bus Interface                                         |     |

| 29 | Expansion Bus Configuration Register 0                          | .87 |

| 30 | Setting the Intel XScale <sup>®</sup> Processor Operation Speed | .88 |

| 31 | UART Interfaces                                                 | .88 |

| 32 | USB Interface                                                   | .89 |

| 33 | Oscillator Interface                                            | .89 |

| 34 | GPIO Interface                                                  | .90 |

| 35 | JTAG Interface                                                  |     |

| 36 | System Interface                                                | .90 |

| 37 | Power Interface                                                 | .91 |

|    |                                                                 |     |

## **Revision History**

L

| Date                                                                 | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| December 2007                                                        | 008      | 1. Updated Section 3.1.3 with updated SDRAM initialization information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| February 2007                                                        | 007      | <ol> <li>Added a new Appendix A, "Design Checklist".</li> <li>Changed RCOMP signal to be an Output signal.</li> <li>Updated Figure 2 by replacing RJ11 block connection to the RS-232<br/>Serial Port block with a DB9 block.</li> <li>Updated Section 3.2.3 by replacing Intel StrataFlash<sup>®</sup> memory (J3) with<br/>Intel<sup>®</sup> Embedded Flash Memory (J3 v.D).</li> <li>Updated Figure 17 to more clearly show power-up sequence<br/>requirements.</li> <li>Removed information regarding using a crystal as the system clock<br/>source.</li> <li>Changed some of the I/O signals pins from <i>pulled low</i> to <i>pulled high</i><br/>when not in use for new designs. These include signal pins of MII, PCI,<br/>UART, HSS, Expansion Bus, UTOPIA, GPIO. No changed required for<br/>existing designs.</li> <li>Updated Figure 14 by pulling the unused pins high.</li> <li>Updated Intel<sup>®</sup> product branding. References to Intel XScale core were<br/>updated to Intel XScale Processor.</li> <li>Updated figures with references to<br/><i>Intel<sup>®</sup> IXP4XX</i> by changing to <i>Intel<sup>®</sup> IXP42X</i>.</li> </ol> |  |

| June 2004                                                            | 006      | Updated Intel <sup>®</sup> product branding.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| April 2004 005 Added information for Intel <sup>®</sup> IXP420 Netwo |          | Added information for Intel <sup>®</sup> IXP420 Network Processor variants.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| February 2004                                                        | 004      | Updated clock references from 33.333MHz to 33.33MHz as specified in the Intel® IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Datasheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| September 2003                                                       | 003      | Updated JTAG signal descriptions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| August 2003                                                          | 002      | Improved guidelines in Sections 3, 5, 6, and 7. Other minor updates through the document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| April 2003                                                           | 001      | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

§§

Intel<sup>®</sup> IXP42X product line and IXC1100 control plane processors—Revision History

## 1.0 Introduction

This document provides design recommendations for hardware and systems designers using the Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor. Information on the generic hardware interface, PCB, and bus topologies are also included.

**Design recommendations** are necessary to meet the timing and signal quality specifications. The guidelines recommended in this document are based on experience and simulation work done at Intel while developing the Intel<sup>®</sup> IXDP425 Development Platform. These recommendations are subject to change.

#### 1.1 About this Document

This document is intended for hardware and systems designers who are experienced with systems and board design. The hardware design guidelines assume that the designer has a working knowledge of the vocabulary and practices of systems and hardware design.

This document contains the following sections:

| Chapter Name                                             | Description                                                                                     |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Chapter 1.0, "Introduction"                              | Conventions used in this manual and related documentation                                       |

| Chapter 2.0, "System Architecture"                       | Shows how the processors implement and interface to other devices.                              |

| Chapter 3.0, "General Hardware Design<br>Considerations" | Describes the interfaces between the processors and other devices.                              |

| Chapter 4.0, "PBGA Package"                              | Describes package information for the processors.                                               |

| Chapter 5.0, "General PCB Guide"                         | Provides recommended guidelines for printed circuit board setup.                                |

| Chapter 6.0, "General Layout and Routing Guide"          | Provides routing guidelines for layout and design of a printed circuit board.                   |

| Chapter 7.0, "Critical Routing Topologies"               | Describes PC133 and SDRAM and PCI-bus routing topologies.                                       |

| Appendix A, "Design Checklist"                           | Highlights design considerations that should be reviewed prior to manufacturing a system board. |

Chapter 3.0, "General Hardware Design Considerations" and Chapter 4.0, "PBGA Package" contain specific design considerations for each on-chip peripheral interface within the processors. Not all sections are applicable to all designs because not all units of the processors are used in every design.

### 1.2 Related Documentation

| Title                                                                                                               | Document # |

|---------------------------------------------------------------------------------------------------------------------|------------|

| Intel <sup>®</sup> IXP4XX Product Line of Network Processors Specification Update                                   | 306428     |

| Intel <sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Developer's Manual | 252480     |

| Intel <sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Datasheet          | 252479     |

| Intel <sup>®</sup> IXP400 Software Specification Update                                                             | 307310     |

| Intel <sup>®</sup> IXP400 Software Programmer's Guide                                                               | 252539     |

| Title                                                                                                                                                                                              | Document #                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Intel <sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor: Spread-Spectrum Clocking to Reduce EMI                                                           | 254028                                                      |

| Intel <sup>®</sup> IXP42X Product Line and IXC1100 Control Plane Processors: $I^2C$ Implementation Using the GPIO Pins                                                                             | 252137                                                      |

| Intel <sup>®</sup> XScale™ Core Developer's Manual                                                                                                                                                 | 273473                                                      |

| Intel XScale <sup>®</sup> Microarchitecture Technical Summary                                                                                                                                      | _                                                           |

| Intel StrataFlash <sup>®</sup> Embedded Memory (P30) to Intel <sup>®</sup> IXP42X Product<br>Line of Network Processors and IXC1100 Control Plane Processor Design<br>Guide - Application Note 832 | 308294                                                      |

| Intel StrataFlash <sup>®</sup> Memory J3 to Intel StrataFlash <sup>®</sup> Embedded Memory<br>(P30) Migration Guide - Application Note 812                                                         | 306667                                                      |

| PCI Local Bus Specification, Rev. 2.2                                                                                                                                                              | N/A                                                         |

| Universal Serial Bus Specification, Revision 1.1                                                                                                                                                   | N/A                                                         |

| PC133 SDRAM Specification                                                                                                                                                                          | N/A                                                         |

| UTOPIA Level 2 Specification, Revision 1.0                                                                                                                                                         | N/A                                                         |

| IEEE 802.3 Specification                                                                                                                                                                           | N/A                                                         |

| IEEE 1149.1 Specification                                                                                                                                                                          | N/A                                                         |

| <i>I<sup>2</sup>C-Bus Specification</i> from Philips Semiconductors*                                                                                                                               | (Available at<br>http://<br>www.semiconductors.philips.com) |

## 1.3 Acronyms and Abbreviations

| Acronym or Abbreviation | Description                                 |

|-------------------------|---------------------------------------------|

| AHB                     | Advanced High-Performance Bus               |

| ATM                     | Asynchronous Transfer Mode                  |

| EMI                     | Electro-Magnetic Interference               |

| GPIO                    | General Purpose Input/Output                |

| HSS                     | High Speed Serial                           |

| LAN                     | Local Area Network                          |

| MII                     | Media-Independent Interface                 |

| NPE                     | Network Processor Engine                    |

| PCB                     | Printed Circuit Board                       |

| PCI                     | Peripheral Component Interface              |

| PHY                     | Physical Layer Interface                    |

| PLL                     | Phase-Locked Loop                           |

| PMU                     | Performance Monitoring Unit                 |

| SDRAM                   | Synchronous Dynamic Random Access Memory    |

| UART                    | Universal Asynchronous Receiver-Transmitter |

| USB                     | Universal Serial Bus                        |

Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Hardware Design Guidelines 10

### 1.4 Overview

The IXP42X product line and IXC1100 control plane processors are multi-function processors and incorporate many advanced architecture features, including an industry-standard, 32-bit PCI controller, UART, PC133 SDRAM memory controller, interrupt controller, Intel XScale<sup>®</sup> Microarchitecture compliant with the ARM\* Version 5TE instruction set architecture (ISA), USB (device only), UTOPIA-2, GPIO, 133-MHz internal bus, AHB bridges, timers, 8-Kbyte Queue Manager, PMU, Network Processor Engines (NPEs), and industry-standard Media Independent Interfaces (MII).

With the highly integrated solution and rich feature set, the processors deliver high performance system-on-chip and helps to reduce the overall cost of system implementations.

The processors can operate at a variety of frequencies, allowing systems designers to trade off performance for lower power consumption. The Intel XScale<sup>®</sup> Microarchitecture and the internal components are clocked from an internal PLL. The internal and external interfaces use a 66/133-MHz, 32-bit data bus; a 32-bit address bus; and control signals that enable the interface between the Intel XScale<sup>®</sup> Microarchitecture and peripheral logic to optimize performance.

### 1.5 Key Features

- Intel XScale<sup>®</sup> Processor (compliant with Intel<sup>®</sup> StrongARM<sup>\*</sup> architecture)

- High-performance processor based on Intel XScale<sup>®</sup> technology

- Seven/eight-stage Intel<sup>®</sup> Super-Pipelined RISC Technology

- Management unit

- 32-entry, data memory management unit

- 32-entry, instruction memory management unit

- 32-Kbyte, 32-way, set associative instruction cache

- 32-Kbyte, 32-way, set associative data cache

- · 2 Kbyte, two-way, set associative mini-data cache

- 128-entry, branch target buffer

- Eight-entry write buffer

- Four-entry fill and pend buffers

- Clock speeds:

- 266 MHz

- 400 MHz

- 533 MHz

- ARM\* Version 5TE Compliant

- Intel<sup>®</sup> Media Processing Technology Multiply-accumulate coprocessor

- Debug unit. Accessible through JTAG port

- PCI interface

- 32-bit interface

- Selectable clock

- 33-MHz clock output derived from either GPI014 or GPI015

- 0- to 66-MHz clock input

- PCI Local Bus Specification, Rev. 2.2 compatible

- PCI arbiter supporting up to four external PCI devices (four REQ/GNT pairs)

- Host/option capable

- Master/target capable

- Two DMA channels

- USB v 1.1 device controller

- Full-speed capable

- Embedded transceiver

- 16 endpoints

- SDRAM interface

- 32-bit data

- 13-bit address

- 133 MHz

- Up to eight open pages simultaneously maintained

- Programmable auto-refresh

- Programmable CAS/data delay

- 8 MB minimum up to 256 MB maximum supported

- Expansion interface

- 24-bit address

- 16-bit data

- Eight programmable chip selects

- Supports Intel and Motorola\* microprocessor style bus cycles

- Multiplexed-style bus cycles

- Simplex-style bus cycles

- Texas Instruments\* DSPs supporting HPI-8 and HPI-16 bus cycles

- High-speed UART

- 1,200 Baud to 921 Kbaud

- 16550 compliant

- 64-Byte Tx and Rx FIFOs

- CTS and RTS modem control signals

- Console UART

- 1,200 Baud to 921 Kbaud

- 16550 compliant

- 64-byte Tx and Rx FIFOs

- CTS and RTS modem control signals

- Internal bus performance monitoring unit

- Seven 27-bit event counters

- Monitors internal bus occurrence and duration events

- 16 GPIOs

- Four internal timers

- Packaging

- 492-pin PBGA

- Commercial temperature (0° to +70° C)

- Extended temperature (-40° to +85° C)

- Lead free support

The remaining features described in the product line features list require software in order for these features to be functional. To determine if the feature is enabled, see the *Intel<sup>®</sup> IXP400 Software Programmer's Guide*.

• Three network processor engines (NPEs)

Used to off load typical Layer-2 networking functions like:

- Ethernet filtering

- ATM SARing

- HDLC

- Encryption/Authentication

- DES

- Triple-DES (3DES)

- AES 128-bit and 256-bit

- ARC4/WEP-CRC

- SHA-1

- MD5

- Two MII interfaces

- 802.3 MII interfaces

- Single MDIO interface to control both MII interfaces

- UTOPIA-2 Interface

- Eight-bit interface

- Up to 33 MHz clock speed

- Five transmit and five receive address lines

- Two high-speed, serial interfaces

- Six-wire

- Supports speeds up to 8.192 MHz

- Supports connection to T1/E1 framers

- Supports connection to CODEC/SLICs

- Eight HDLC Channels

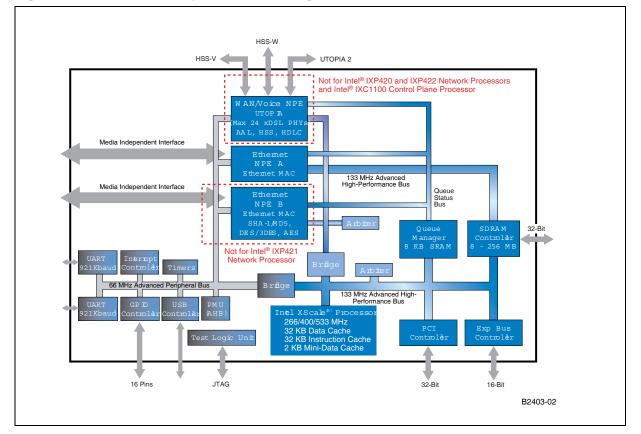

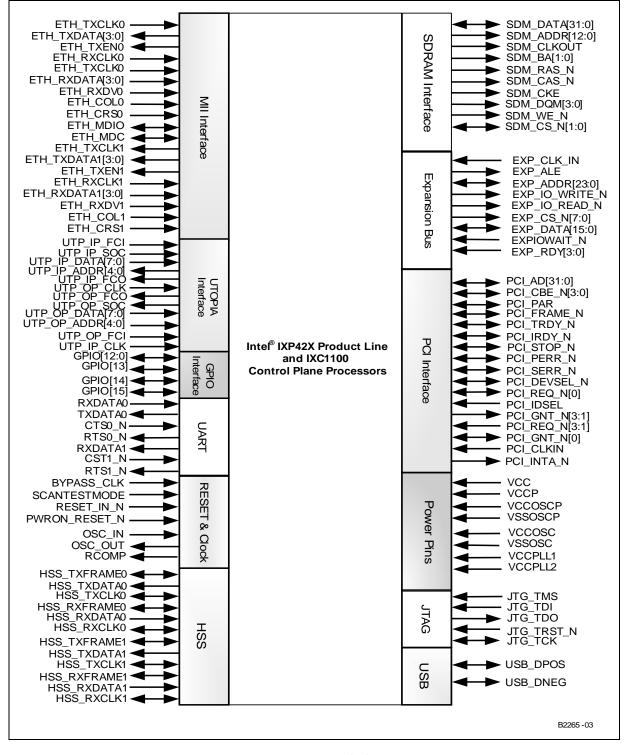

Figure 1 illustrates the major internal components of the IXP42X product line and IXC1100 control plane processors.

Refer to the Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Datasheet for complete feature list and block diagram description.

#### Figure 1. Devices' Component Block Diagram

The Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Datasheet lists the feature set for each of the IXP42X product line and IXC1100 control plane processors.

### 1.6 Typical Applications

- High-performance DSL modem

- High-performance cable modem

- Residential gateway

- SME router

- Integrated access device (IAD)

- Set-top box

- Access points 802.11a/b/g

- Industrial controllers

- · Network printers

- · Control plane

§§

System Architecture–Intel<sup>®</sup> IXP42X product line and IXC1100 control plane processors

## 2.0 System Architecture

### 2.1 System Architecture Description

The Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor are multi-function processors that integrate the Intel XScale<sup>®</sup> Processor (ARM\* architecture compliant) with intelligent peripheral controllers, including a 32-bit PCI controller that can be used in many applications such as networking and communications.

The processors are highly integrated and designed and manufactured with Intel's 0.18micron production semiconductor process technology. This process technology — along with numerous, dedicated-function peripheral interfaces and many features with the Intel XScale processor — addresses the needs of many system applications and helps reduce system costs. The processors can be configured to meet many system application and implementation needs.

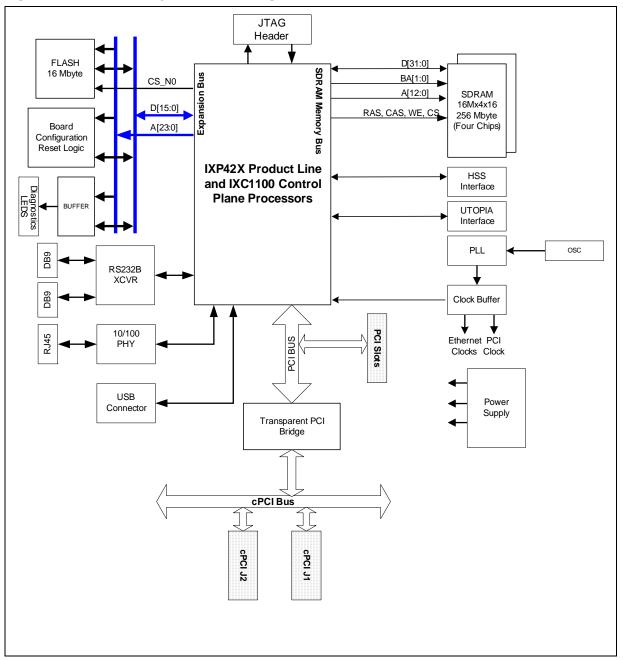

Figure 2 illustrates one of many applications that the processors can be implemented and interfaced. For detailed functional descriptions, see the Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Developer's Manual.

Figure 2. Devices' System Block Diagram

### 2.2 System Memory Map

The IXP42X product line and IXC1100 control plane processors implement a single address map that is used for all internal memory and register space. The complete address space consists of 2^32 byte addressable location.

Table 1 shows the memory map of peripherals connected to the AHB.

Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Hardware Design Guidelines 16

#### Table 1. Memory Map

| Start Address | End Address | Size     | Use                                                                            |

|---------------|-------------|----------|--------------------------------------------------------------------------------|

| 0000_0000     | OFFF_FFFF   | 256 MB   | Expansion Bus Data (Mirrored)/SDRAM Data <sup>†</sup>                          |

| 0000_0000     | 2FFF_FFF    | 768 MB   | SDRAM Data (Aliased) <sup>†</sup>                                              |

| 3000_0000     | 3FFF_FFF    |          | (Reserved)                                                                     |

| 4000_0000     | 47FF_FFFF   |          | (Reserved)                                                                     |

| 4800_0000     | 4FFF_FFFF   | 128 MB   | PCI Data                                                                       |

| 5000_0000     | 5FFF_FFF    | 256 MB   | Expansion Bus Data                                                             |

| 6000_0000     | 63FF_FFFF   | 64 MB    | Queue manager                                                                  |

| 6400_0000     | BFFF_FFF    |          | (Reserved)                                                                     |

| C000_0000     | C3FF_FFFF   | 64 MB    | PCI Controller Configuration and Status Registers                              |

| C400_0000     | C7FF_FFFF   | 64 MB    | Expansion Bus Configuration Registers                                          |

| C800_0000     | C800_0FFF   | 1 KB     | High-Speed UART                                                                |

| C800_1000     | C800_1FFF   | 1 KB     | Console UART                                                                   |

| C800_2000     | C800_2FFF   | 1 KB     | Internal Bus Performance Monitoring Unit                                       |

| C800_3000     | C800_3FFF   | 1 KB     | Interrupt Controller                                                           |

| C800_4000     | C800_4FFF   | 1 KB     | GPIO Controller                                                                |

| C800_5000     | C800_5FFF   | 1 KB     | Timers                                                                         |

| C800_6000     | C800_6FFF   | 1 KB     | WAN/HSS NPE = NPE A (IXP400 software definition)<br>– Not User Programmable    |

| C800_7000     | C800_7FFF   | 1 KB     | Ethernet NPE A = NPE B (IXP400 software definition)<br>– Not User Programmable |

| C800_8000     | C800_8FFF   | 1 KB     | Ethernet NPE B = NPE C (IXP400 software definition)<br>– Not User Programmable |

| C800_9000     | C800_9FFF   | 1 KB     | Ethernet MAC A                                                                 |

| C800_A000     | C800_AFFF   | 1 KB     | Ethernet MAC B                                                                 |

| C800_B000     | C800_BFFF   | 1 KB     | USB Controller                                                                 |

| C800_C000     | C800_FFFF   |          | (Reserved)                                                                     |

| C801_0000     | CBFF_FFF    |          | (Reserved)                                                                     |

| CC00_0000     | CC00_00FF   | 256 Byte | SDRAM Configuration Registers                                                  |

| CC00_0100     | FFFF_FFFF   |          | (Reserved)                                                                     |

The lowest 256 Mbyte of address space is configurable based on the value of a configuration register bit located in the Expansion Bus Controller (bit 31 of EXP\_CNFG0.)

When bit 31 (MEM\_MAP) of configuration register #0 (EXP\_CNFG0) is set to logic 1, the Expansion Bus

occupies the lowest 256 Mbytes of address space.

When bit 31 (MEM\_MAP) of configuration register #0 (EXP\_CNFG0) is set to logic 0 the SDRAM

occupies the lowest 256 Mbytes of address space starting at 5000\_0000 while the SDRAM occupies the

lowest 256 MB of address address space.

In both cases, regardless of the value of MEM\_MAP, the SDRAM occupies the 768 MB (1000\_0000 to 2FFF\_FFFF) immediately following the lowest 256 MB and the Expansion Bus can be accessed starting at address 5000\_0000.

The largest SDRAM memory size supported by the Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor is 256 Mbytes. The actual memory implemented in any given configuration will be aliased (repeated) to fill the 1-Gbyte SDRAM address space. Due to aliasing, all of the SDRAM will be accessible even when the Expansion Bus occupies the lowest 256 Mbytes of address space. On reset, bit 31 (MEM\_MAP) of the Configuration Register #0 (EXP\_CNFG0) will be set to logic 1. This setting is required because the dedicated boot memory is flash memory located on the Expansion Bus.

Details in the Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Developer's Manual.

Intel<sup>®</sup> IXP42X product line and IXC1100 control plane processors—System Architecture

General Hardware Design Considerations—Intel<sup>®</sup> IXP42X product line and IXC1100 control plane processors

## 3.0 General Hardware Design Considerations

This chapter contains information on how to implement and interface the SDRAMs, flash, SRAM, Ethernet PHYs, UART and other peripherals to the Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor.

This chapter's signal-definition tables list pull-up and pull-down resistor recommendations that are required when the particular enabled interface is *not* being used in the application. These external resistor requirements are only needed if the particular model of Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor has the particular interface *enabled* and the interface is *not required* in the application.

*Warning:* All IXP42X product line and IXC1100 control plane processors I/O pins are *not* 5-V tolerant.

*Disabled* features, within the IXP42X product line and IXC1100 control plane processors, do not require external resistors as the processor will have internal pull-up or pull-down resistors enabled as part of the *disabled* interface.

### 3.1 PC133 SDRAM Interface

The SDRAM memory controller, integrated into the IXP42X product line and IXC1100 control plane processors, supports a 32-bit data bus interface operating at 133 MHz, eight open pages, two external banks with memory configuration from 8 to 256 Mbytes.

General SDRAM routing guidelines can be found in Section 7.1, "PC133 SDRAM Topologies" on page 73. For more detailed information, see the PC133 SDRAM Specification.

These are the features:

- Performs eight word length burst size to SDRAM

- · Supports bursts up to eight words internally

- · Is a target device on the Internal Buses and does not split any transactions

- Has RAS-to-CAS delay of three clocks

- Has a CAS-to-data latency of two or three clocks, as programmed by the configuration register

- Runs at 133 MHz frequency (same as the internal bus frequency)

- Maintains up to eight open pages

- Supports a total of two physical banks totaling to 8 Mbytes/256 Mbytes of memory space

- · Handles transactions from the internal bus in a big-endian manner

- · Automatically refreshes the SDRAM devices using an internal refresh counter

### 3.1.1 SDRAM Interface Signals

#### Table 2. SDRAM Interface Signals

| Name           | Type* | Description                                                                                                                                                                  |

|----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDM_ADDR[12:0] | 0     | SDRAM Address: A0-A12 are output during the READ/WRITE command and ACTIVE command to select a location in memory.                                                            |

| SDM_DATA[31:0] | 1/0   | SDRAM Data: bidirectional data bus used to transfer data to and from the SDRAM.                                                                                              |

| SDM_CLKOUT     | 0     | SDRAM Clock: All SDRAM input signals are sampled on the rising edge of SDM_CLKOUT. All output signals are driven with respect to the rising edge of the Clock.               |

| SDM_BA[1:0]    | 0     | SDRAM Bank Address: SDM_BA0 and SDM_BA1 define the bank the current command is accessing.                                                                                    |

| SDM_RAS_N      | 0     | SDRAM Row Address strobe/select (active low): Along with SDM_CAS_N, SDM_WE_N, and SDM_CS_N signals determines the current command to be executed.                            |

| SDM_CAS_N      | 0     | SDRAM Column Address strobe/select (active low): Along with<br>SDM_RAS_N, SDM_WE_N, and SDM_CS_N signals determines the current<br>command to be executed.                   |

| SDM_CS_N[1:0]  | 0     | SDRAM Chip select (active low): CS# enables the command decoder in the external SDRAM when logic low and disables the command decoder in the external SDRAM when logic high. |

| SDM_WE_N       | 0     | SDRAM Write enable (active low): Along with SDM_CAS_N, SDM_RAS_N, and SDM_CS_N signals determines the current command to be executed.                                        |

| SDM_CKE        | 0     | SDRAM Clock Enable: CKE is driving high to activate the clock to an<br>external SDRAM and driver low to de-activate the CLK to an external<br>SDRAM.                         |

| SDM_DQM[3:0]   | 0     | SDRAM Data bus mask: DQM is used to bytes select data during read/write access to an external SDRAM.                                                                         |

Note: For explanations of the Type column abbreviations, see Table 21 on page 81.

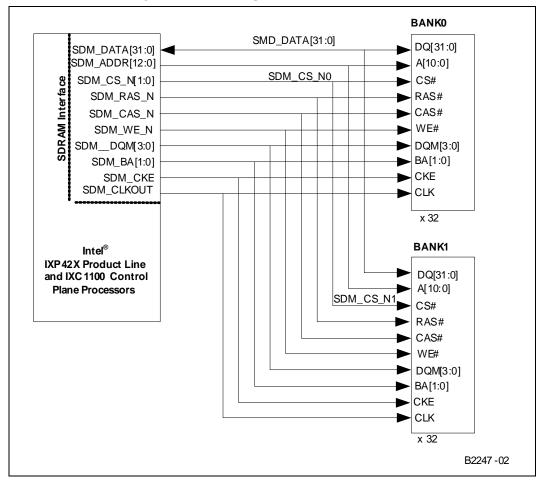

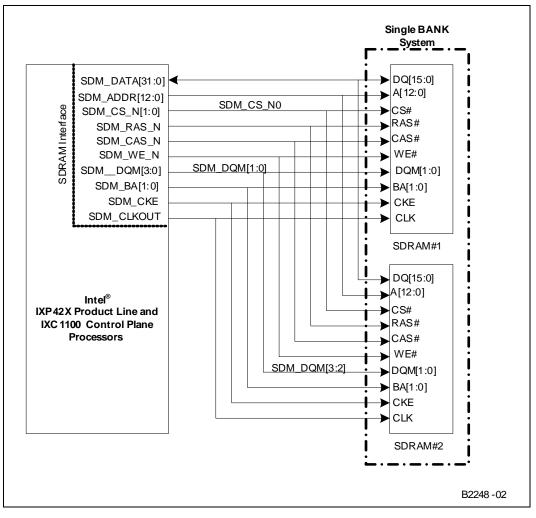

#### 3.1.2 SDRAM Block Diagrams

The IXP42X product line and IXC1100 control plane processors support the PC133compatible SDRAM 16 and 32-bit wide devices. The banks are accessed 32 bits at a time. The maximum configuration is two physical banks of SDRAM devices (each bank consists of two SDRAM 16-bit devices or single SDRAM 32-bit device), using two independent chip-selects.

The supported memory types are listed in Table 3. The processors' SDRAM interfaces support a maximum of 256 Mbytes of SDRAM and a minimum of 8 Mbytes, using two SDRAM devices. The PC133 SDRAM memory bus I/O buffers are designed to support up to four loads total for two banks of PC133 of SDRAM memory.

#### Table 3.SDRAM Memory Types

| SDRAM<br>Technology | SDRAM<br>Arrangement | Number of Chips | Number of Banks<br>(Systems) | Total Memory Size |

|---------------------|----------------------|-----------------|------------------------------|-------------------|

| 64 Mbit             | 2M x 32              | 1               | 1                            | 8 Mbytes          |

|                     | 2M x 32              | 2               | 2                            | 16 Mbytes         |

|                     | 4M x 16              | 2               | 1                            | 16 Mbytes         |

|                     | 4M x 16              | 4               | 2                            | 32 Mbytes         |

Note: The 4 M x 32, \* 8 M x 32 and \* 16 M x 32 devices have not been fully validated by Intel.

General Hardware Design Considerations—Intel<sup>®</sup> IXP42X product line and IXC1100 control plane processors

#### Table 3. SDRAM Memory Types

| SDRAM<br>Technology | SDRAM<br>Arrangement | Number of Chips | Number of Banks<br>(Systems) | Total Memory Size |

|---------------------|----------------------|-----------------|------------------------------|-------------------|

|                     | 8M x 16              | 2               | 1                            | 32 Mbytes         |

| 128 Mbit            | 8M x 16              | 4               | 2                            | 64 Mbytes         |

|                     | * 4M x 32            | 1               | 1                            | 16 Mbytes         |

|                     | * 4M x 32            | 2               | 2                            | 32 Mbytes         |

|                     | 16M x 16             | 2               | 1                            | 64 Mbytes         |

| 256 Mbit            | 16M x 16             | 4               | 2                            | 128 Mbytes        |

| 256 MDIT            | * 8M x 32            | 1               | 1                            | 32 Mbytes         |

|                     | * 8M x 32            | 2               | 2                            | 64 Mbytes         |

|                     | 32M x 16             | 2               | 1                            | 128 Mbytes        |

| 512 Mbit            | 32M x 16             | 4               | 2                            | 256 Mbytes        |

|                     | * 16M x 32           | 1               | 1                            | 64 Mbytes         |

|                     | * 16M x 32           | 2               | 2                            | 128 Mbytes        |

Note: The 4 M x 32, \* 8 M x 32 and \* 16 M x 32 devices have not been fully validated by Intel.

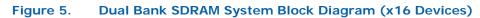

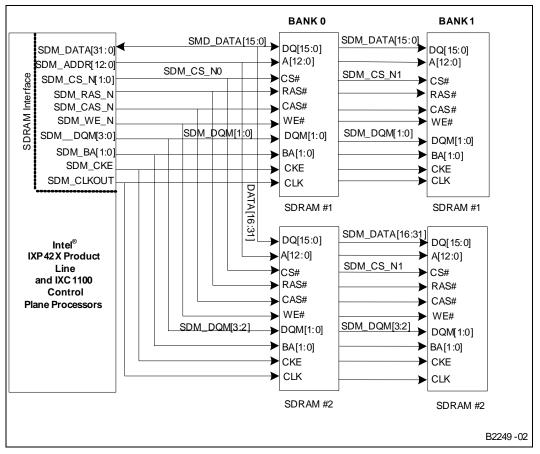

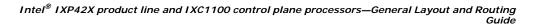

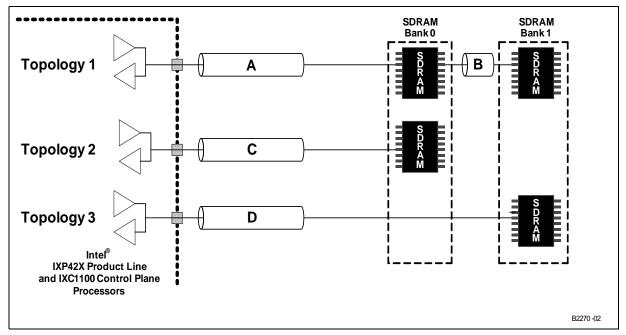

Figure 3, Figure 4, and Figure 5 illustrate how the PC133 SDRAM interfaces to the processors' memory bus. The figures do not include any termination resistors that may be needed. For best signal integrity results the designer may perform simulations.

*Note:* The SDM\_CLKOUT is the reference clock signal for all SDRAM devices and generated by the onchip PLL. Layout guidelines can be found in Section 7.1.1, "PC 133 SDRAM Clock" on page 74.

#### Figure 3. Dual-Bank SDRAM System Block Diagram (x32 Devices)

Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Hardware Design Guidelines 22

Figure 4 illustrates how the IXP42X product line and IXC1100 control plane processors' interfaces to one bank (2 Chips) of the PC133 SDRAM using the 8 M x 16 (128-Mbit), 16 M x 16 (256-Mbit), or 32 M x 16 (512-Mbit).

#### Figure 4. Single Bank SDRAM System Block Diagram (x16 Devices)

December 2007 Document Number: 252817-008US

Figure 5 illustrates how the IXP42X product line and IXC1100 control plane processors' interfaces to two banks (4 Chips) of the PC133 SDRAM using the 8 M x 16 (128-Mbit), 16 M x 16 (256-Mbit), or 32 M x 16 (512-Mbit).

#### 3.1.3 SDRAM Initialization

Initialization of the SDRAM devices is performed by the operating system. The following sequence must be followed:

- The memory controller applies the clock enable pin (SDM\_CKE) during power up and must stabilize the clock signal within 100 µs after power stabilizes.

- The memory controller holds all the control pins to the memory inactive (SDM\_RAS\_N, SDM\_CAS\_N, SDM\_WE\_N, SDM\_CS\_N[1:0]=1) for a minimum of 1 ms after supply voltage reaches the desired level.

- SDM\_CKE is driven to VCC all the time. The IXP42X product line and IXC1100 control plane processors never de-assert SDM\_CKE

- Software disables the refresh counter by setting the SDRAM Refresh (SDR\_REFRESH) Register to zero.

- Software issues one NOP cycle after the 1ms SDRAM device deselect. A NOP is accomplished by setting the SDRAM Instruction (SDR\_IR) Register to 011. The memory controller asserts SDM\_CKE with the NOP.

- Software pauses 200 µs after the NOP.

Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Hardware Design Guidelines

- Software issues a precharge-all command to the SDRAM interface by setting SDR\_IR to 010

- Software provides eight auto-refresh cycles. An auto-refresh cycle is accomplished by setting SDR\_IR to 100. Software must ensure at least  $T_{rc}$  cycles between each auto-refresh command.  $T_{rc}$  (active to active command period) is determined by the SDRAM being used

- Software issues a mode-register-select command by writing to SDR\_IR to program the SDRAM parameters. Setting SDR\_IR to 000 programs the MCU for CAS latency of two, while setting the SDR\_IR to 001 programs the memory controller and SDRAM for CAS latency of three.

- The memory controller may issue a row activate command three clocks after the mode register set command (T<sub>mrd</sub>).

- Software re-enables the refresh counter by setting the SDR\_REFRESH to the required value.

- *Note:* The SDRAM clock starts with the release of PWRON\_RESET\_N. The first access made by the internal auto-refresh counter (set to default value of 0x384) happens ~7µs after RESET\_IN\_N is released. Software will not be able to disable this counter before the first access is made. To meet a specific SDRAMs 100-200 ms requirement before the first access, the designer may have to add additional delay between PWRON\_RESET\_N and RESET\_IN\_N beyond the required minimum of 10 ns.

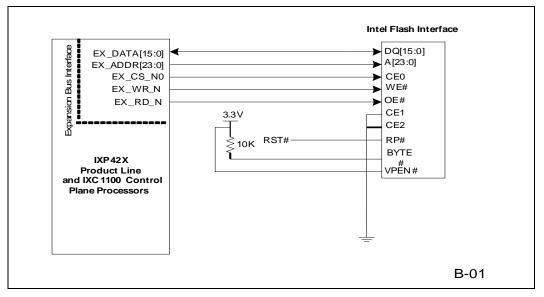

### 3.2 Expansion Bus

The IXP42X product line and IXC1100 control plane processors' expansion bus supports a variety of types and speeds of I/O accesses and is specifically designed for compatibility with Intel and Motorola\* microprocessor style bus cycles and the Texas Instruments\* DSP standard Host-Port Interfaces (HPI).

All of these modes are supported seamlessly, without any additional glue logic. Other cycle types may be supported due to the programmability of the access phases defined for each cycle type.

The processors' expansion bus provides a 24-bit address bus and a 16-bit-wide data interface for each of its eight independent chip-selects and maps transfers between the internal bus and the external devices. Multiplexed and non-multiplexed address/data buses are both supported.

Applications having less than 16-bit external data paths may connect to less than the full 16 bits. Devices with a wider than 16-bit data bus interface are not supported. The address range of the processors' expansion bus is from 512 bytes to 16 Mbytes and provides glueless connection of up to eight independent external devices.

December 2007 Document Number: 252817-008US

Downloaded from Elcodis.com electronic components distributor

I

### 3.2.1 Expansion Bus Interface Signals

#### Table 4. Expansion Bus Interface Signals

| Name          | Type* | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EX_CLK        | I     | Input clock signal used to sample all expansion interface inputs and clock all expansion interface outputs.                                                                                                                                                                                                                                                                                                                                                                                             |  |

| EX_ALE        | 0     | Address-latch enable used for multiplexed address/data bus accesses. Used in Intel and Motorola* multiplexed modes of operation.                                                                                                                                                                                                                                                                                                                                                                        |  |

| EX_ADDR[23:0] | 1/0   | Expansion-bus address used as an output for data accesses over the expansion bus. Also, used as an input during reset to capture device configuration. These signals have a weak pull-up resistor attached internally. Based on the desired configuration, various address signals must be tied low in order for the device to operate in the desired mode. (For details, see the Intel <sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Developer's Manual.) |  |

| EX_WR_N       | 0     | Intel-mode write strobe / Motorola-mode data strobe<br>(EXP_MOT_DS_N) / TI*-mode data strobe (TI_HDS1_N).                                                                                                                                                                                                                                                                                                                                                                                               |  |

| EX_RD_N       | 0     | Intel-mode read strobe / Motorola-mode read-not-write<br>(EXPB_MOT_RNW) / TI mode read-not-write (TI_HR_W_N).                                                                                                                                                                                                                                                                                                                                                                                           |  |

| EX_CS_N[7:0]  | 0     | <ul> <li>External chip selects for expansion bus.</li> <li>Chip selects 0 through 7 can be configured to support Intel or<br/>Motorola bus cycles.</li> <li>Chip selects 4 through 7 can be configured to support TI HPI bus<br/>cycles.</li> </ul>                                                                                                                                                                                                                                                     |  |

| EX_DATA[15:0] | 1/0   | Expansion-bus, bidirectional data                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| EX_IOWAIT_N   | I     | Data ready/acknowledge from expansion-bus devices. Expansion-<br>bus access is halted when an external device sets EX_IOWAIT_N to<br>logic 0 and resume from the halted location once the external device<br>sets EX_IOWAIT_N to logic 1. This signal affects accesses that use<br>$EX_CS_N[7:0]$ when the chip select is configured in Intel- or<br>Motorola-mode operation.<br>Should be pulled high through a $10$ -k $\Omega$ resistor, when the signal is<br>not being used in the system.         |  |

| EX_RDY[3:0]   | I     | HPI interface ready signals. Can be configured to be active high or active low. These signals are used to halt accesses using chip Selects 7 through 4 when the chip selects are configured to operate in HPI mode. There is one RDY signal per chip select. This signal only affects accesses that use $EX_CS_N[7:4]$ . Should be pulled high through a 10-k $\Omega$ resistor when the signal is not being used in the system.                                                                        |  |

*Note:* For explanations of the **Type** column abbreviations, see Table 21 on page 81.

### 3.2.2 Configuration Straps

At power up or whenever a reset is asserted, the expansion-bus address outputs are switched to inputs and the states of the bits are captured and stored in Configuration Register 0, bits 23 through 0. This occurs on the first cycle after the synchronous deassertion of the reset signal.

These configuration bits are made available to the system through the expansion-bus address lines. To set a bit to 0, place a 4.7-k $\Omega$ , pull-down resistor on the appropriate address line. Weak pull-up resistors are placed on each expansion-bus address pin; so no population is needed to set the bit to 1.

Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Hardware Design Guidelines

#### Table 5. Expansion Bus Address Description

| Bit   | Name                                                  | Description                                                                                                                                                                                                   |

|-------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | MEM_MAP                                               | Location of Expansion Bus in memory map space:<br>0 = Located at "50000000" (normal mode)<br>1 = Located at "00000000" (boot mode)                                                                            |

| 30:24 |                                                       | (Reserved)                                                                                                                                                                                                    |

| 23:21 | Intel XScale <sup>®</sup> Processor<br>Clock Set[2:0] | Allow a slower Intel XScale <sup>®</sup> Processor clock speed to override device fuse settings; however, cannot be used to over-clock processor speed. Refer to Table 30 on page 88, for additional details. |