# **ICs for Communications**

**Extended PCM Interface Controller**

EPIC®-1

PEB 2055 / PEF 2055 Versions A3

EPIC®-S

PEB 2054 / PEF 2054 Versions 1.0

User's Manual 02.97

| PEB 2055<br>PEF 2055<br>Revision H        | istory: | User's Manual 02.97                          |

|-------------------------------------------|---------|----------------------------------------------|

| Previous Release:                         |         | Technical Manual 02.92 (Editorial Update)    |

| Page (in Page Previous (in User's Manual) |         | Subjects (major changes since last revision) |

#### Edition 02.97

This edition was realized using the software system FrameMaker®.

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 7/23/97. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| Table o | f Contents                                                     | Page |

|---------|----------------------------------------------------------------|------|

| 1       | Overview                                                       | 7    |

| 1.1     | Features                                                       |      |

| 1.2     | Pin Configuration                                              |      |

| 1.3     | Pin Definitions and Functions                                  |      |

| 1.4     | Logic Symbols                                                  | 14   |

| 1.5     | Functional Block Diagram                                       | 16   |

| 1.6     | Using the EPIC-S                                               |      |

| 1.7     | System Integration and Application                             | 18   |

| 1.7.1   | Digital Line Card                                              |      |

| 1.7.1.1 | Switching, Layer-1 Control                                     | 18   |

| 1.7.1.2 | Decentralized D-Channel Handling                               | 18   |

|         | Central D-Channel Processing                                   | 20   |

| 1.7.1.4 | 3, - 3                                                         |      |

|         | Packet Data Centralized                                        | 21   |

| 1.7.2   | Analog Line Card                                               |      |

| 1.7.3   | Packet Handlers                                                | 24   |

| 2       | Functional Description                                         | 27   |

| 2.1     | Bus Interface                                                  |      |

| 2.2     | PCM Interface                                                  |      |

| 2.3     | Configurable Interface                                         |      |

| 2.4     | Memory Structure and Switching                                 |      |

| 2.5     | Pre-processed Channels, Layer-1 Support                        |      |

| 2.6     | Special Functions                                              |      |

|         | •                                                              |      |

| 3       | Operational Description                                        |      |

| 3.1     | Microprocessor Interface Operation                             |      |

| 3.2     | Clocking                                                       |      |

| 3.3     | Reset                                                          |      |

| 3.4     | EPIC® Operation                                                |      |

| 3.4.1   | PCM-Interface                                                  |      |

| 3.4.2   | Configurable Interface                                         |      |

| 3.4.3   | Switching Functions                                            |      |

| 3.4.4   | Special Functions                                              |      |

| 3.5     | Initialization Procedure                                       |      |

| 3.5.1   | Hardware Reset                                                 |      |

| 3.5.2   | EPIC® Initialization                                           |      |

| 3.5.2.1 | Register Initialization                                        |      |

| 3.5.2.2 | Control Memory Reset                                           |      |

| 3.5.2.3 | Initialization of Pre-processed Channels                       |      |

| 3.5.2.4 | Initialization of the Upstream Data Memory (DM) Tristate Field |      |

| 3.5.3   | Activation of the PCM and CFI Interfaces                       | 45   |

| Table o | f Contents                                                  | Page |

|---------|-------------------------------------------------------------|------|

| 4       | Detailed Register Description                               | 46   |

| 4.1     | Register Address Arrangement                                | 46   |

| 4.2     | Detailed Register Description                               | 48   |

| 4.2.1   | PCM Interface Registers                                     | 48   |

| 4.2.1.1 | PCM-Mode Register (PMOD)                                    | 48   |

| 4.2.1.2 | Bit Number per PCM-Frame (PBNR)                             | 50   |

| 4.2.1.3 | PCM-Offset Downstream Register (POFD)                       | 50   |

| 4.2.1.4 | PCM-Offset Upstream Register (POFU)                         | 51   |

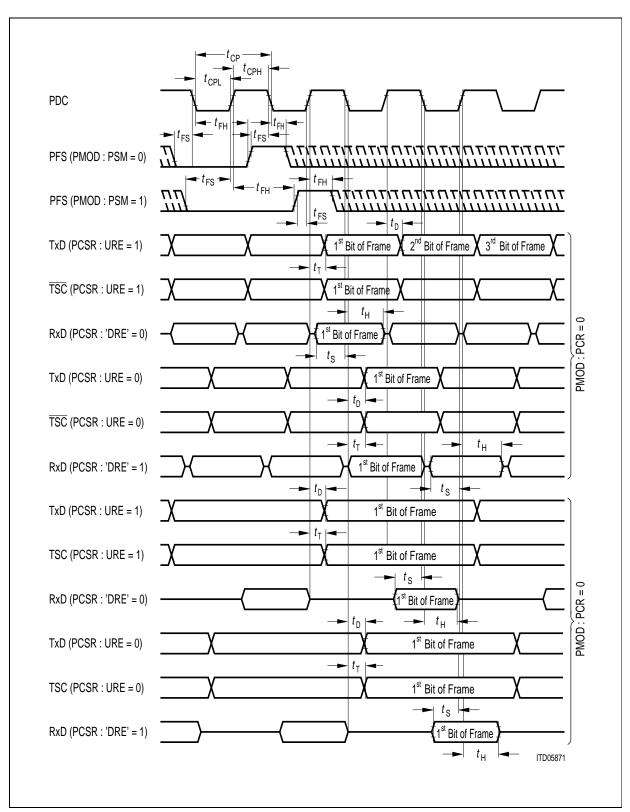

|         | PCM-Clock Shift Register (PCSR)                             |      |

| 4.2.1.6 | PCM-Input Comparison Mismatch (PICM)                        | 52   |

| 4.2.2   | Configurable Interface Registers                            | 53   |

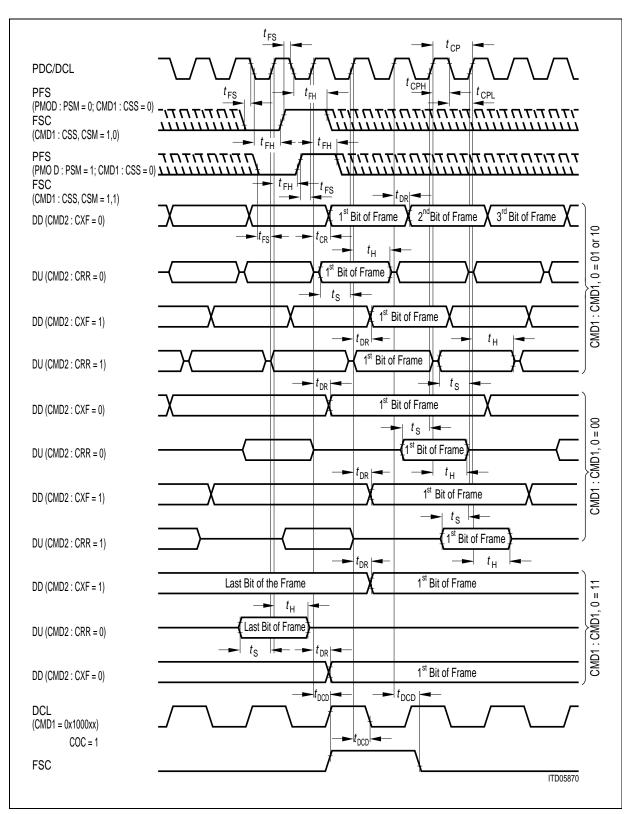

|         | Configurable Interface Mode Register 1 (CMD1)               |      |

| 4.2.2.2 | Configurable Interface Mode Register 2 (CMD2)               | 55   |

| 4.2.2.3 | Configurable Interface Bit Number Register (CBNR)           | 58   |

| 4.2.2.4 | Configurable Interface Time Slot Adjustment Register (CTAR) | 58   |

| 4.2.2.5 | Configurable Interface Bit Shift Register (CBSR)            | 59   |

| 4.2.2.6 | Configurable Interface Subchannel Register (CSCR)           | 60   |

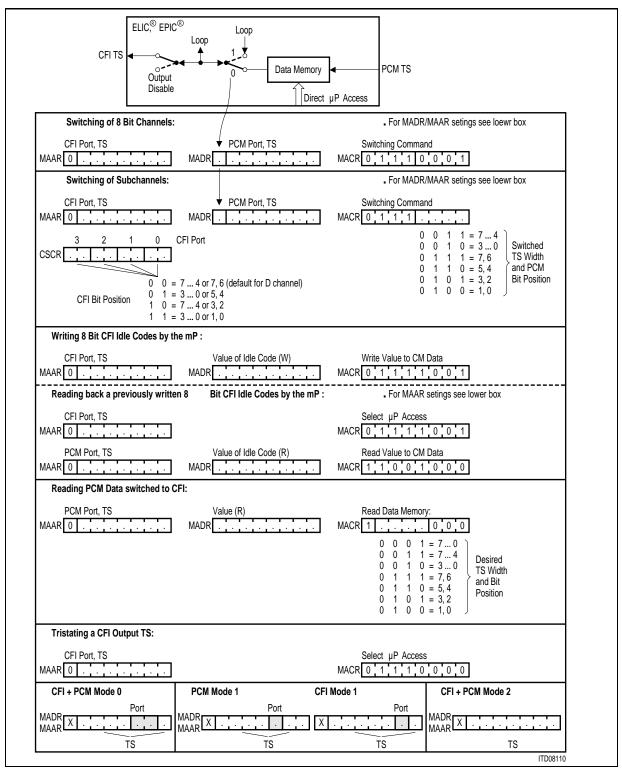

| 4.2.3   | Memory Access Registers                                     |      |

| 4.2.3.1 | Memory Access Control Register (MACR)                       | 61   |

| 4.2.3.2 | Memory Access Address Register (MAAR)                       | 65   |

| 4.2.3.3 | Memory Access Data Register (MADR)                          | 66   |

| 4.2.4   | Synchronous Transfer Registers                              | 67   |

| 4.2.4.1 | Synchronous Transfer Data Register (STDA)                   | 67   |

| 4.2.4.2 | Synchronous Transfer Data Register B (STDB)                 | 67   |

| 4.2.4.3 | Synchronous Transfer Receive Address Register A (SARA)      | 68   |

| 4.2.4.4 | Synchronous Transfer Receive Address Register B (SARB)      | 69   |

| 4.2.4.5 | Synchronous Transfer Transmit Address Register A (SAXA)     | 69   |

| 4.2.4.6 | Synchronous Transfer Transmit Address Register B (SAXB)     | 70   |

| 4.2.4.7 | Synchronous Transfer Control Register (STCR)                | 70   |

| 4.2.5   | Monitor/Feature Control Registers                           | 71   |

| 4.2.5.1 | MF-Channel Active Indication Register (MFAIR)               | 71   |

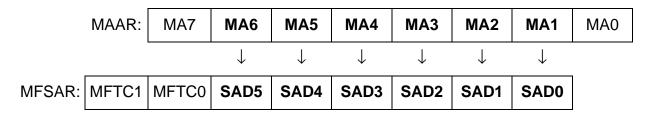

| 4.2.5.2 | MF-Channel Subscriber Address Register (MFSAR)              | 72   |

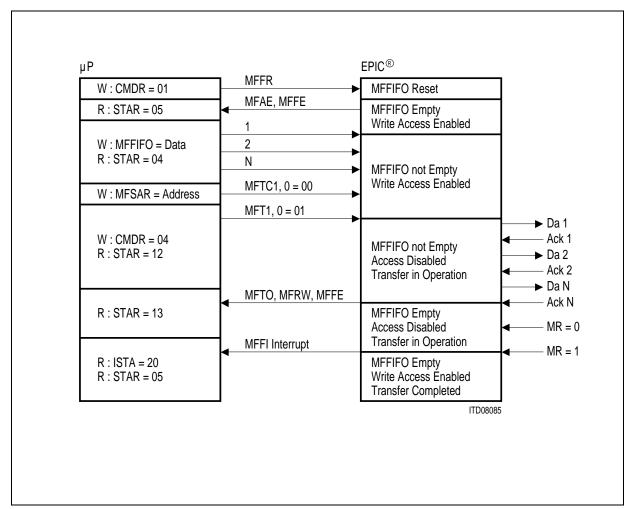

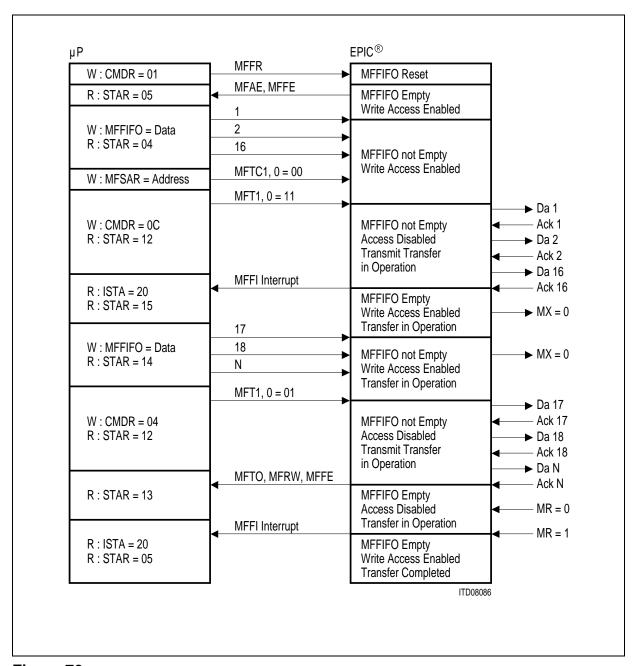

| 4.2.5.3 | Monitor/Feature Control Channel FIFO (MFFIFO)               | 73   |

| 4.2.6   | Status/Control Registers                                    | 73   |

| 4.2.6.1 | Signaling FIFO (CIFIFO)                                     | 73   |

| 4.2.6.2 | Timer Register (TIMR)                                       | 74   |

| 4.2.6.3 |                                                             |      |

| 4.2.6.4 | Command Register (CMDR)                                     | 76   |

| 4.2.6.5 |                                                             |      |

| 4.2.6.6 | Mask Register (MASK)                                        | 79   |

|         | Operation Mode Register (OMDR)                              |      |

| Table o | f Contents                                                   | Page |

|---------|--------------------------------------------------------------|------|

| 4.2.6.8 | Version Number Status Register (VNSR)                        | 82   |

| 5       | Application Hints                                            | 83   |

| 5.1     | Introduction                                                 | 83   |

| 5.1.1   | IOM® and SLD Functions                                       | 83   |

| 5.2     | Configuration of Interfaces                                  | 89   |

| 5.2.1   | PCM Interface Configuration                                  | 89   |

| 5.2.1.1 | PCM Interface Signals                                        | 89   |

| 5.2.1.2 | PCM Interface Registers                                      | 89   |

| 5.2.1.3 | PCM Interface Characteristics                                | 91   |

| 5.2.2   | Configurable Interface Configuration                         | 102  |

| 5.2.2.1 | CFI Interface Signals                                        | 102  |

| 5.2.2.2 | CFI Registers                                                | 102  |

| 5.2.2.3 | CFI Characteristics                                          | 104  |

| 5.3     | Data and Control Memories                                    | 130  |

| 5.3.1   | Memory Structure                                             |      |

| 5.3.2   | Indirect Register Access                                     | 131  |

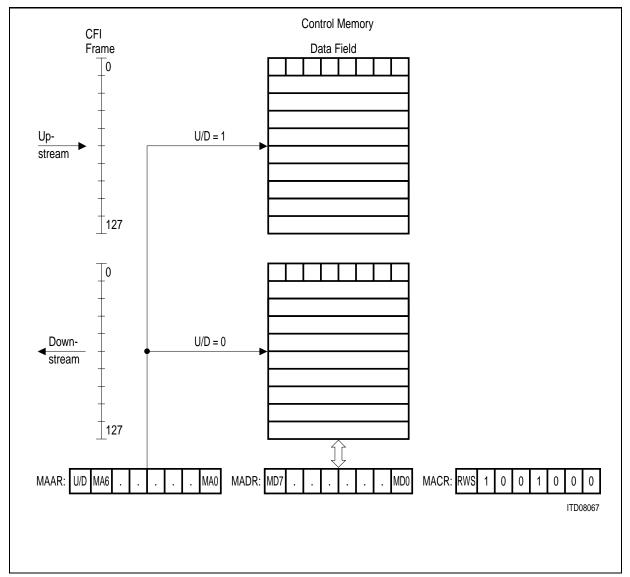

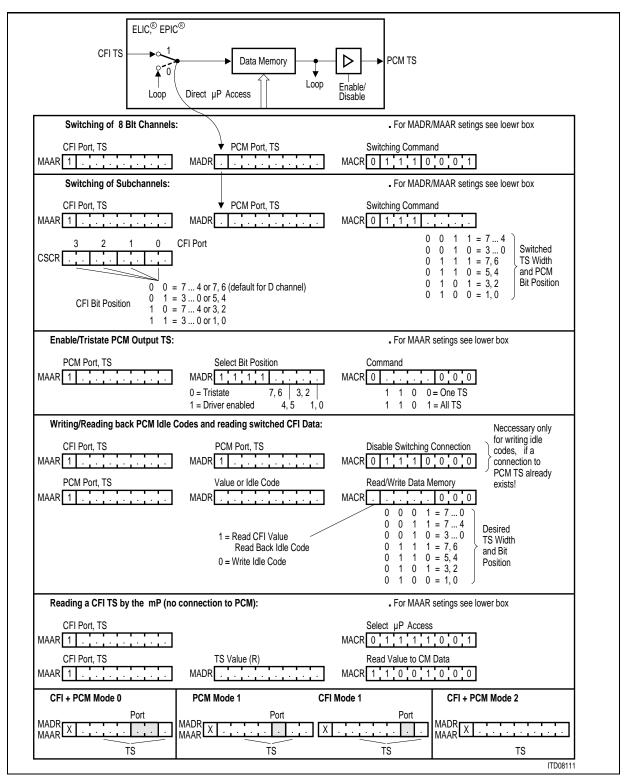

| 5.3.3   | Memory Access Commands                                       | 135  |

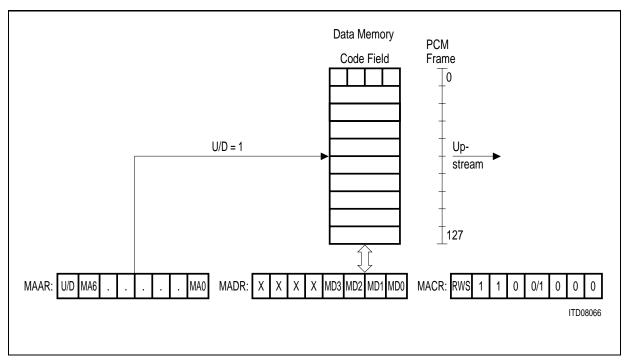

| 5.3.3.1 | Access to the Data Memory Data Field                         | 135  |

|         | Access to the Data Memory Code (Tristate) Field              |      |

| 5.3.3.3 | Access to the Control Memory Data Field                      |      |

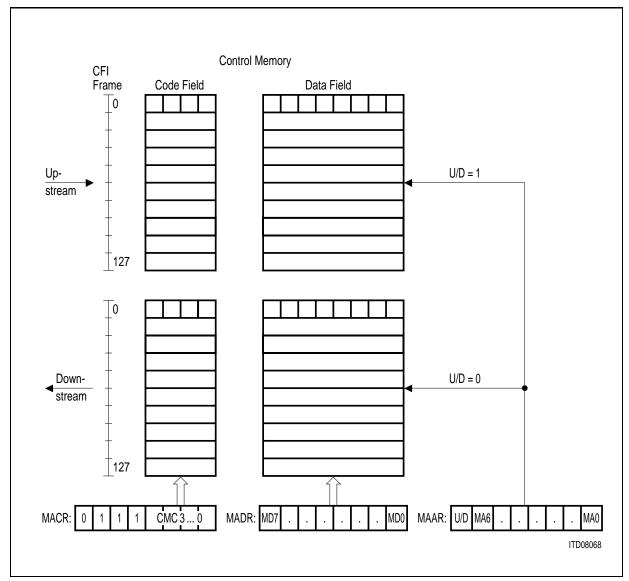

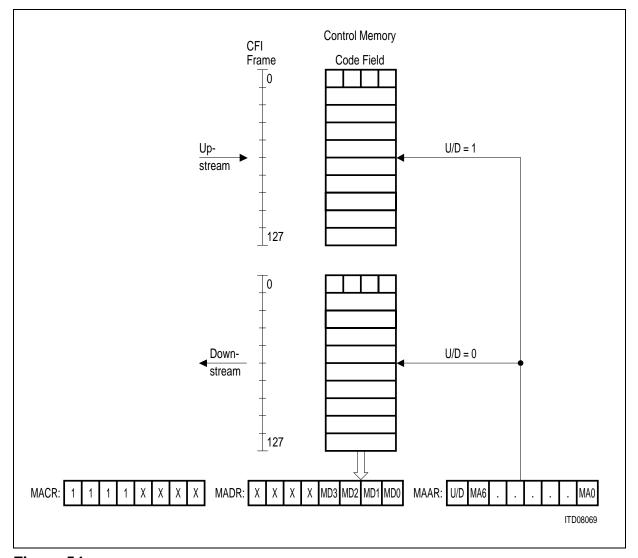

| 5.3.3.4 | Access to the Control Memory Code Field                      | 144  |

| 5.4     | Switched Channels                                            |      |

| 5.4.1   | CFI - PCM Time Slot Assignment                               |      |

| 5.4.2   | Subchannel Switching                                         |      |

| 5.4.3   | Loops                                                        |      |

| 5.4.3.1 | CFI - CFI Loops                                              |      |

|         | PCM - PCM Loops                                              |      |

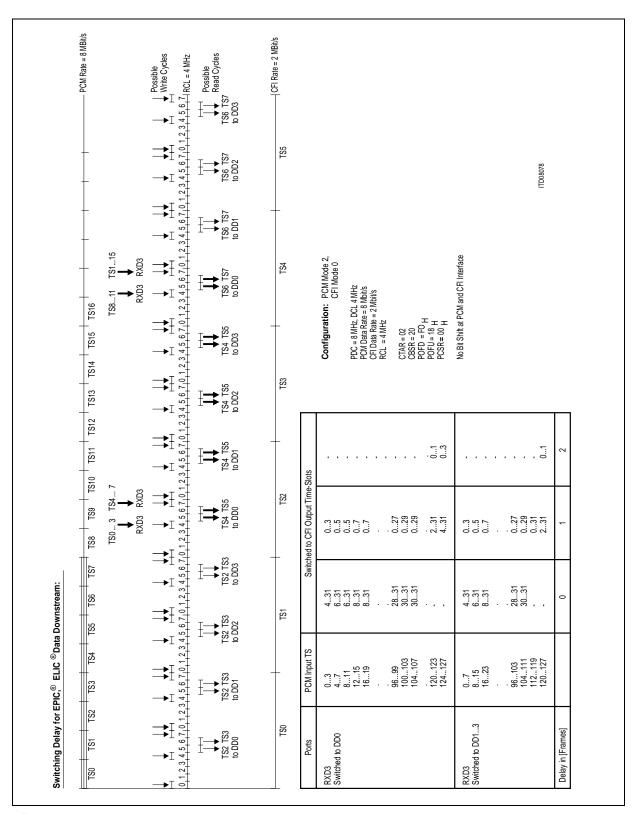

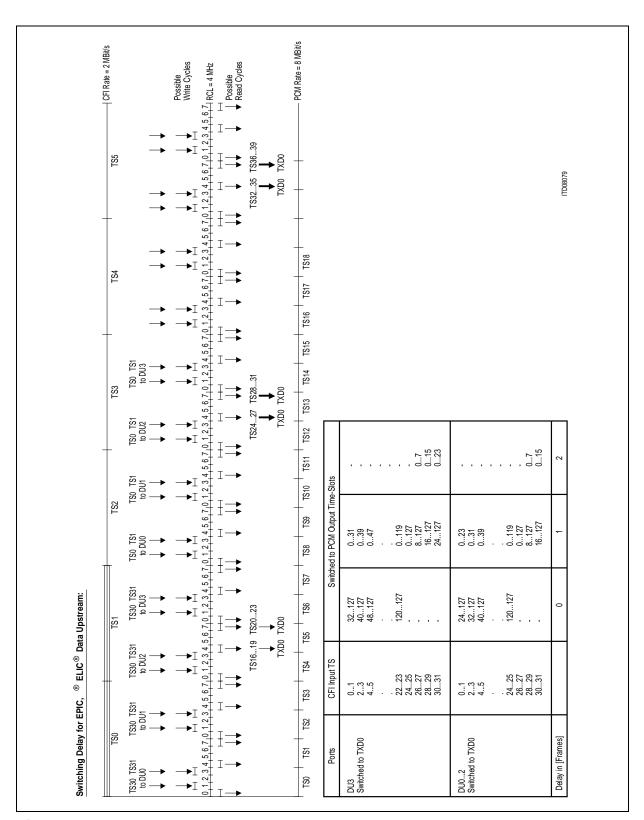

| 5.4.4   | Switching Delays                                             |      |

| 5.4.4.1 | Internal Procedures at the Serial Interfaces                 |      |

|         | How to Determine the Delay                                   |      |

|         | Example: Switching of Wide Band ISDN Channels with the EPIC® |      |

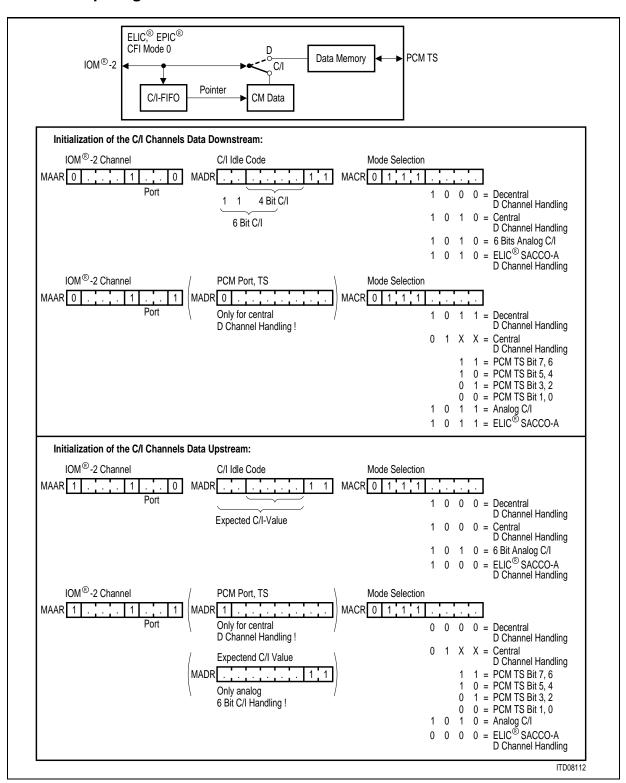

| 5.5     | Preprocessed Channels                                        |      |

| 5.5.1   | Initialization of Preprocessed Channels                      |      |

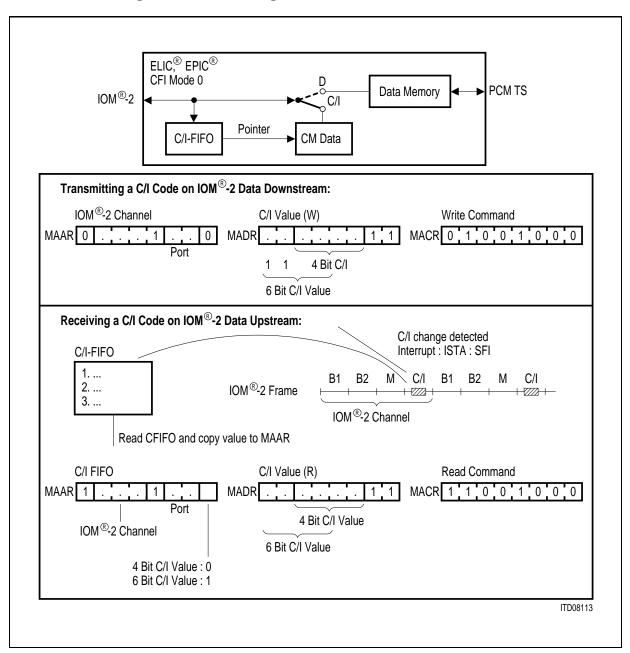

| 5.5.2   | Control/Signaling (CS) Handler                               |      |

| 5.5.2.1 | Registers used in Conjunction with the CS Handler            |      |

| 5.5.2.2 | Access to Downstream C/I and SIG Channels                    |      |

| 5.5.2.3 | Access to the Upstream C/I and SIG Channels                  |      |

| 5.5.3   | Monitor/Feature Control (MF) Handler                         |      |

| 5.5.3.1 | Registers used in Conjunction with the MF Handler            |      |

| 5.5.3.2 | Description of the MF Channel Commands                       |      |

| 5.6     | μP Channels                                                  | 208  |

| Table c | of Contents                                                          | Page |

|---------|----------------------------------------------------------------------|------|

| 5.7     | Synchronous Transfer Utility                                         | 212  |

| 5.7.1   | Registers Used in Conjunction with the Synchronous Transfer Utility  |      |

| 5.8     | Supervision Functions                                                |      |

| 5.8.1   | Hardware Timer                                                       | 221  |

| 5.8.2   | PCM Input Comparison                                                 | 223  |

| 5.8.3   | PCM Framing Supervision                                              |      |

| 5.8.4   | Power and Clock Supply Supervision/Chip Version                      |      |

| 5.9     | Applications                                                         |      |

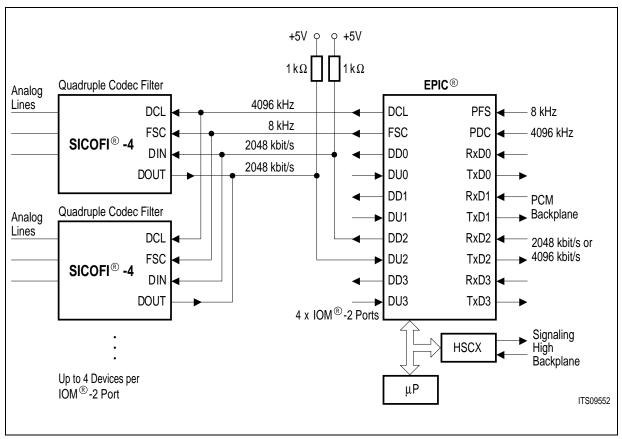

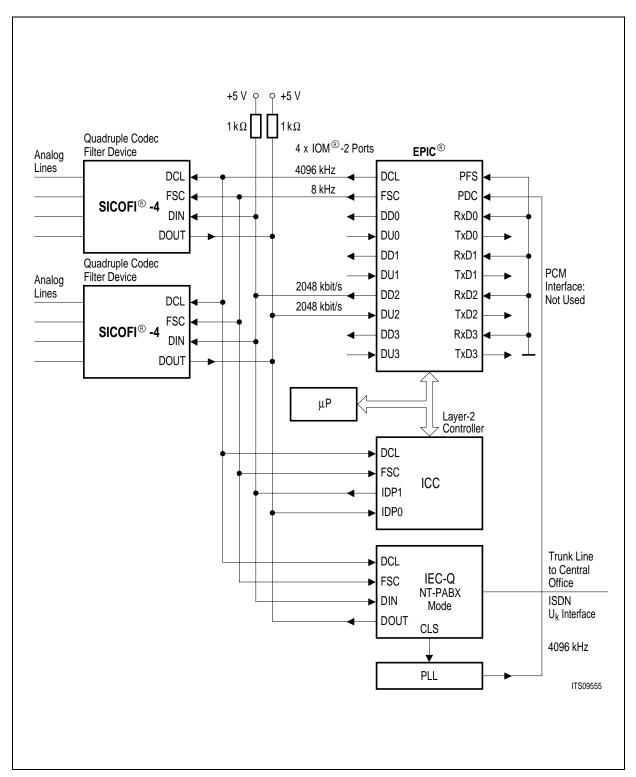

| 5.9.1   | Analog IOM®-2 Line Card with SICOFI®-4 as Codec/Filter Device        |      |

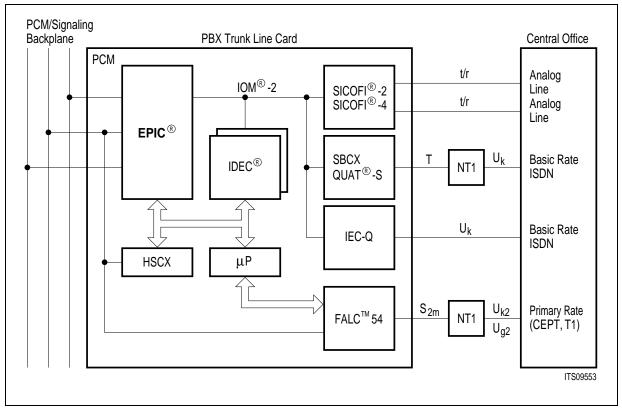

| 5.9.2   | IOM®-2 Trunk Line Applications                                       |      |

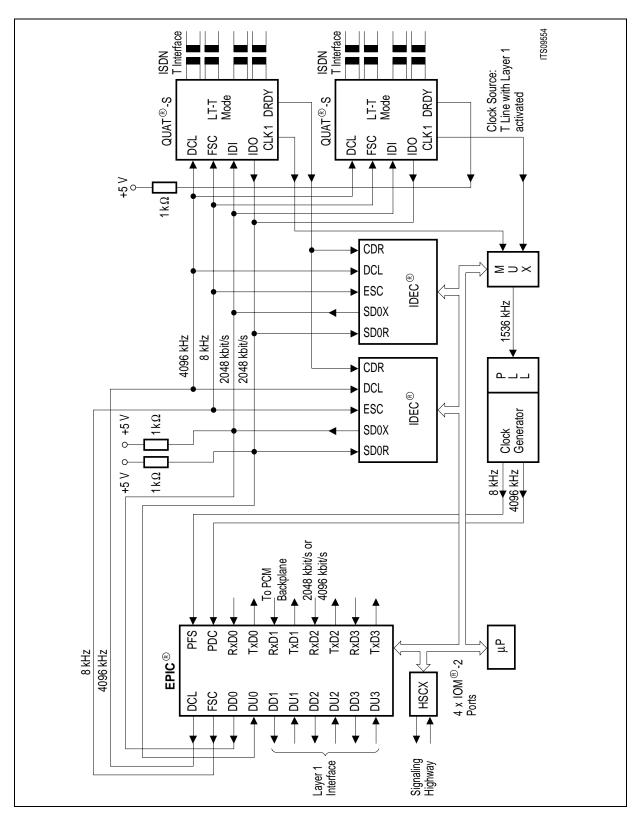

| 5.9.2.1 | PBX With Multiple ISDN Trunk Lines                                   |      |

| 5.9.2.2 |                                                                      |      |

| 5.9.3   | Miscellaneous                                                        |      |

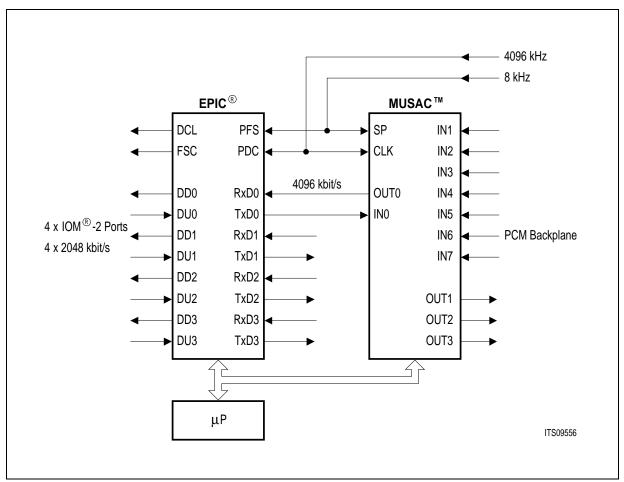

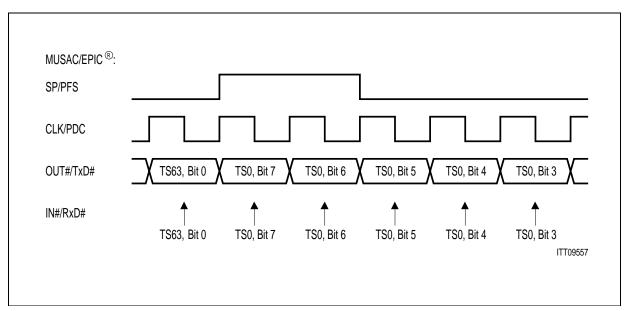

| 5.9.3.1 | Interfacing the EPIC <sup>®</sup> to a MUSAC <sup>™</sup>            |      |

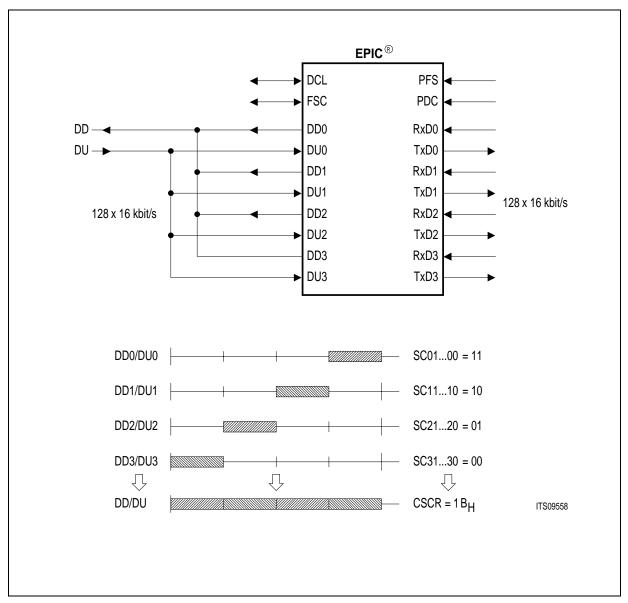

| 5.9.3.2 | Space and Time Switch for 16 kbit/s Channels                         | 242  |

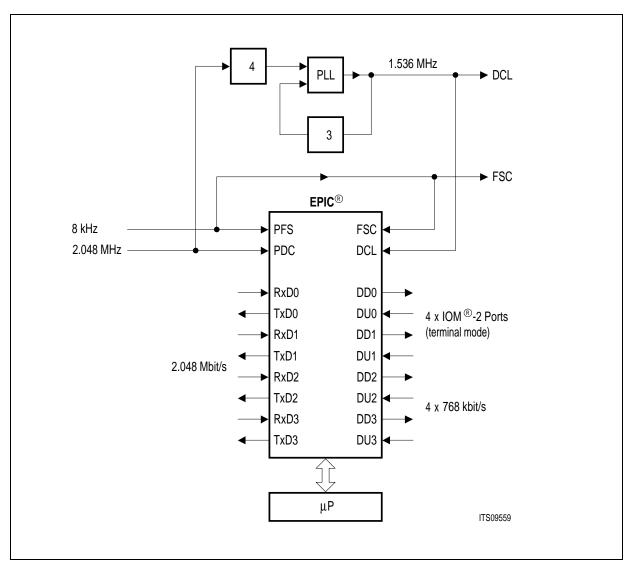

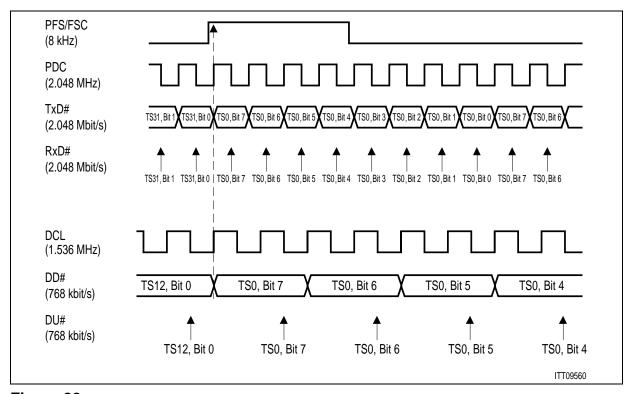

| 5.9.3.3 | Interfacing an IOM®-2 Terminal Mode Interface                        | 044  |

|         | to a 2.048 Mbit/s PCM Backplane                                      | 244  |

| 6       | Electrical Characteristics                                           | 246  |

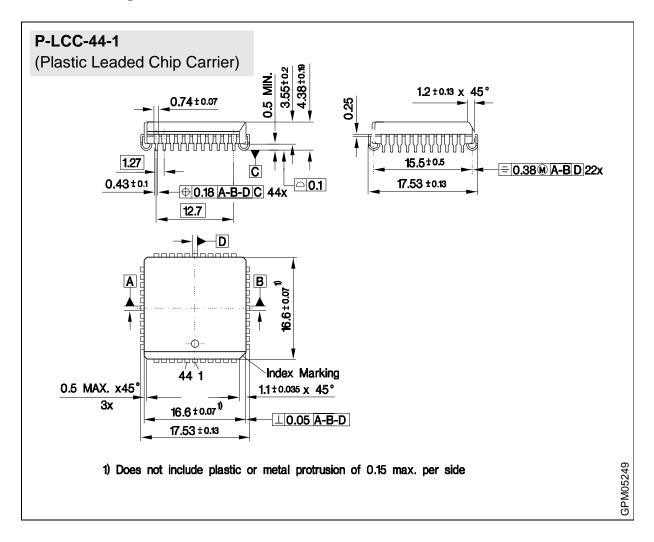

| 7       | Package Outlines                                                     | 257  |

| 8       | Appendix                                                             | 258  |

| 8.1     | Working Sheets                                                       |      |

| 8.1.1   | Register Summary for EPIC® Initialization                            |      |

| 8.1.2   | Switching of PCM Time Slots to the CFI Interface (data downstream) . |      |

| 8.1.3   | Switching of CFI Time Slots to the PCM Interface (data upstream)     |      |

| 8.1.4   | Preparing EPIC®s C/I Channels                                        | 264  |

| 8.1.5   | Receiving and Transmitting IOM®-2 C/I-Codes                          | 265  |

| 8.2     | Development Tools                                                    | 266  |

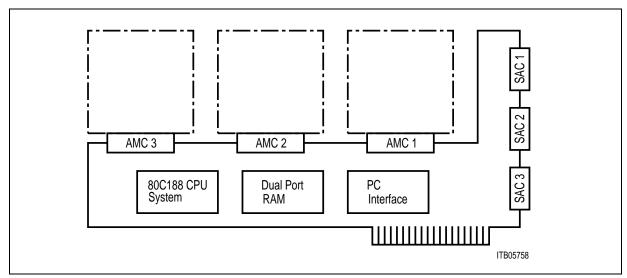

| 8.2.1   | SIPB 5000 Mainboard                                                  |      |

| 8.2.2   | SIPB 5121 IOM®-2 Line Card (EPIC®/IDEC®)                             |      |

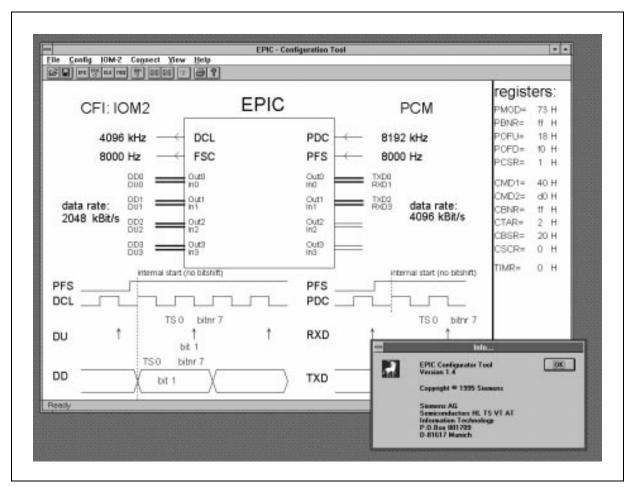

| 8.2.3   | EPIC® Configurator                                                   | 268  |

| 9       | Lists                                                                | 269  |

| 9.1     | Glossary                                                             | 269  |

IOM®, IOM®-1, IOM®-2, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4µC, SLICOFI®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, EPIC®-1, EPIC®-S, ELIC®, IPAT®-2, ITAC®, ISAC®-S, ISAC®-S TE, ISAC®-P, ISAC®-P TE, IDEC®, SICAT®, OCTAT®-P, QUAT®-S are registered trademarks of Siemens AG.

MUSAC™-A, FALC™54, IWE™, SARE™, UTPT™, ASM™, ASP™ are trademarks of Siemens AG.

Purchase of Siemens I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C-system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. Copyright Philips 1983.

### 1 Overview

The PEB 2055 (Extended PCM Interface Controller) is a highly integrated controller circuit optimized for analog and ISDN line card and central switches applications. The EPIC-1 provides the circuitry necessary to manage up to 32 digital (ISDN or proprietary) or 64 analog subscribers.

The EPIC-1 is dedicated to switch PCM data between two serial interfaces, the system interface (PCM interface) and the configurable interface (CFI). The EPIC-1 performs non-blocking time and space switching for up to 128 channels.

Since the system cost of the EPIC-1 is divided by the number of lines it controls, an highly economical implementation of digital or analog subscriber lines can be performed.

The EPIC-S (PEB 2054) is a pin compatible device offering half the switching capacity of the EPIC-1. Therefore the EPIC-S is capable of handling up to 16 ISDN or 32 analog subscribers. It is programmable according to the EPIC-1 with respect of the pins not available.

The EPIC is implemented in a Siemens advanced CMOS-technology and manufactured in a P-LCC-44-1 package.

The EPIC is member of a chip family supporting a highly economical implementation of line cards and subscriber terminals.

### **Chip Family**

| ina  | Cards: |

|------|--------|

| ırı⇔ | Caros  |

| PEB 2055  | Extended PCM Interface Controller    | (EPIC)     |

|-----------|--------------------------------------|------------|

| PEB 20550 | Extended Line Card Controller        | (ELIC)     |

| PEB 2096  | Octal U <sub>PN</sub> Transceiver    | (OCTAT-P)  |

| PEB 2095  | ISDN Burst Transceiver Circuit       | (IBC)      |

| PEB 2084  | Quadruple S <sub>0</sub> Transceiver | (QUAT-S)   |

| PEB 2465  | Quadruple DSP based Codec Filter     | (SICOFI-4) |

| PEB 2075  | ISDN D-Channel Exchange Controller   | (IDEC)     |

### Terminals:

| PSB 2196 | Digital Subscriber Access Controller | (ISAC-P TE) |

|----------|--------------------------------------|-------------|

|          | for U <sub>PM</sub> Interface        |             |

PEB 2081 (V3.2) S/T-Bus Interface Circuit Extended (SBCX)

Extended PCM Interface Controller EPIC®-1, EPIC®-S

PEB 2055 PEF 2055 PEB 2054 PEF 2054

Versions A3 (PEB 2055), V1.0 (PEB 2054)

**CMOS**

#### 1.1 Features

### **Switching**

- Board Controller for up to

- 32 ISDN or 64 analog subscribers (PEB 2055)

- 16 ISDN or 32 analog subscribers (PEB 2054)

- · Non-blocking switch for

- 128 channels (PEB 2055)

- 64 channels (PEB 2054)

- Switching of 16-, 32-, or 64-kbit/s channels

- Two consecutive 64-kbit/s channels can be switched as a single 128-kbit/s channel

- Freely programmable time slot assignment for all subscribers

- Two serial interfaces (PCM and CFI) programmable over a wide data range (128 -8192 kbit/s)

- Data rates of PCM and configurable interface independent from each other (data rate adaptation)

- PCM-interface

- Tristate control signals for external drivers

- Programmable clock shift

- Single or double data clock

- · Configurable interface

- Configurable for IOM-, SLD- and PCM-applications

- High degree of flexibility for datastream adaptation

- Programmable clockshift

- Single or double data clock

- Synchronous µP-access to two selected channels

| Туре     | Ordering Code     | Package    |

|----------|-------------------|------------|

| PEB 2055 | Q67100-H6035      | P-LCC-44-1 |

| PEF 2055 | Q67100-H6216      | P-LCC-44-1 |

| PEB 2054 | Q67100-H6420      | P-LCC-44-1 |

| PEF 2054 | Q67100-H6534-B701 | P-LCC-44-1 |

Overview

### **Handling of Layer-1 Functions**

- Change detection for C/I-channel (IOM-configuration) or feature control (SLD-configuration)

- Double last-look logic for C/I-channel (IOM-2 analog configuration)

- Additional last-look logic for feature control (SLD-configuration)

- Buffered monitor (IOM-configuration) or signaling channel (SLD-configuration)

### **Bus Interface**

- Siemens/Intel or Motorola type μP-interface

- 8-bit demultiplexed bus interface

- FIFO-access interrupt or DMA controlled

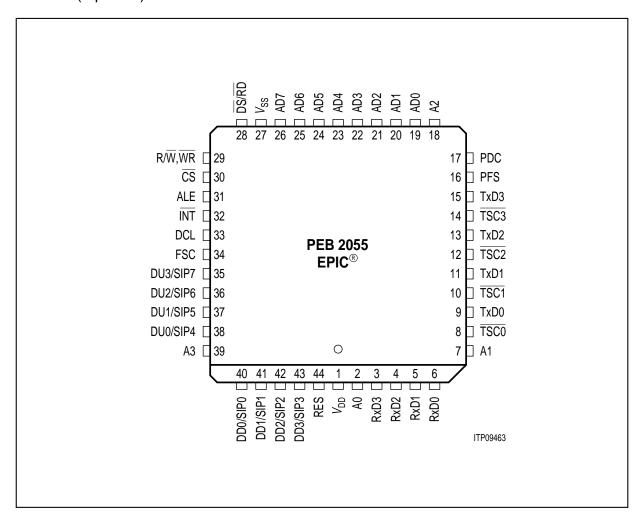

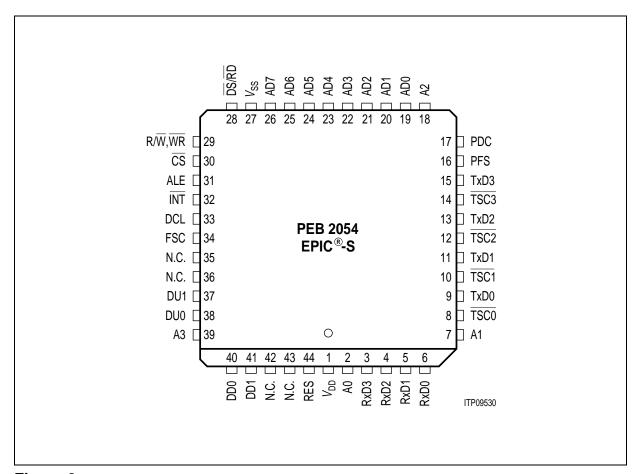

### 1.2 Pin Configuration

(top view)

Figure 1 Pin Configuration EPIC®-1

Figure 2 Pin Configuration EPIC®-S

Overview

## 1.3 Pin Definitions and Functions

| Pin No.<br>EPIC-S EPIC                       |                                              | Symbol Input (I) Output (O)                                                          |                                               | Function                                                                                                                                                                                                                                                                                                             |  |

|----------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 30                                           | 30                                           | CS                                                                                   | I                                             | Chip Select; active low. A "low" on this line selects the EPIC for read/write operations.                                                                                                                                                                                                                            |  |

| 29                                           | 29                                           | WR,<br>R/W                                                                           |                                               | Write, active low, Siemens/Intel bus mode. When "low", a write operation is indicated. Read/Write, Motorola bus mode. When "high" a valid μP-access identifies a read operation, when "low" it identifies a write access.                                                                                            |  |

| 28                                           | 28                                           | RD, DS                                                                               |                                               | Read, active low, Siemens/Intel bus mode. When "low" a read operation is indicated. Data Strobe, Motorola bus mode. A rising edge marks the end of a read or write operation.                                                                                                                                        |  |

| 19<br>20<br>21<br>22<br>23<br>24<br>25<br>26 | 19<br>20<br>21<br>22<br>23<br>24<br>25<br>26 | AD0, D0<br>AD1, D1<br>AD2, D2<br>AD3, D3<br>AD4, D4<br>AD5, D5<br>AD6, D6<br>AD7, D7 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Address/Data Bus; multiplexed bus mode. Transfers addresses from the μP-system to the EPIC and data between the μP and the EPIC. Data Bus; demultiplexed bus mode. Transfers data between the μP and the EPIC. When driving data the pins have push pull characteristic, otherwise they are in high impedance state. |  |

| 31                                           | 31                                           | ALE                                                                                  | 1                                             | Address Latch Enable ALE controls the on chip address latch in multiplexed bus mode. While ALE is "high", the latch is transparent. The falling edge latches the current address. During the first read/write access following reset ALE is evaluated to select the bus mode.                                        |  |

| 32                                           | 32                                           | INT                                                                                  | O<br>(OD)                                     | Interrupt Request, active low. This signal is activated when the EPIC requests an interrupt. Due to the open drain (OD) characteristic of INT multiple interrupt sources can be connected together.                                                                                                                  |  |

| 44                                           | 44                                           | RES                                                                                  | I                                             | Reset A "high" forces the EPIC into reset state.                                                                                                                                                                                                                                                                     |  |

| 16                                           | 16                                           | PFS                                                                                  | I                                             | PCM Interface Frames Synchronization                                                                                                                                                                                                                                                                                 |  |

# **1.3** Pin Definitions and Functions (cont'd)

| Pin<br>EPIC-S       |                          | Symbol                                       | Input (I)<br>Output (O)                          | Function                                                                                                                                                                                                                                                                                            |

|---------------------|--------------------------|----------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                  | 17                       | PDC                                          | I                                                | PCM Interface Data Clock Single or double data rate.                                                                                                                                                                                                                                                |

| 6<br>5<br>4<br>3    | 6<br>5<br>4<br>3         | RxD0<br>RxD1<br>RxD2<br>RxD3                 | <br>                                             | Receive PCM Interface Data Time-slot oriented data is received on this pins and forwarded into the downstream data memory of the EPIC.                                                                                                                                                              |

| 9<br>11<br>13<br>15 | 9<br>11<br>13<br>15      | TxD0<br>TxD1<br>TxD2<br>TxD3                 | 0 0 0 0                                          | Transmit PCM Interface Data Time slot oriented data is shifted out of the EPIC's upstream data memory on this lines. For time-slots which are flagged in the tristate data memory or when bit OMDR:PSB is reset the pins are set to high impedance state.                                           |

| 8<br>10<br>12<br>14 | 8<br>10<br>12<br>14      | TSC0<br>TSC1<br>TSC2<br>TSC3                 | 0 0 0 0                                          | Tristate Control Supplies a control signal for an external driver. These lines are "low" when the corresponding TxD outputs are valid. During reset these lines are "high".                                                                                                                         |

| 34                  | 34                       | FSC                                          | I/O                                              | Frame Synchronization Input or output in IOM configuration. Direction indication signal in SLD mode.                                                                                                                                                                                                |

| 33                  | 33                       | DCL                                          | I/O                                              | Data Clock Input or output in IOM, slave clock in SLD configuration. In IOM configuration single or double data rate, single data rate in SLD mode.                                                                                                                                                 |

| 38<br>37<br>-       | 38<br>37<br>36 *<br>35 * | DU0/SIP4<br>DU1/SIP5<br>DU2/SIP6<br>DU3/SIP7 | I/IO (OD)<br>I/IO (OD)<br>I/IO (OD)<br>I/IO (OD) | Data Upstream Input; IOM or PCM configuration. Serial Interface Port, SLD configuration. Depending on the bit OMDR:COS these lines have push pull or open drain characteristic. For unassigned channels or when bit OMDR:CSB is reset the pins are in the state high impedance. * Note: EPIC-1 only |

Overview

# **1.3** Pin Definitions and Functions (cont'd)

| Pin<br>EPIC-S      | _                        | Symbol                                       | Input (I)<br>Output (O)                          | Function                                                                                                                                                                                                                                                                                               |

|--------------------|--------------------------|----------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40 41 -            | 40<br>41<br>42 *<br>43 * | DD0/SIP0<br>DD1/SIP1<br>DD2/SIP2<br>DD3/SIP3 | O/IO (OD)<br>O/IO (OD)<br>O/IO (OD)<br>O/IO (OD) | Data Downstream Output, IOM or PCM configuration. Serial Interface Port, SLD configuration. Depending on the bit OMDR:COS these lines have push pull or open drain characteristic. For unassigned channels or when bit OMDR:CSB is reset the pins are in the high impedance state. * Note: EPIC-1 only |

| 2<br>7<br>18<br>39 | 2<br>7<br>18<br>39       | A0<br>A1<br>A2<br>A3                         | I/O                                              | Address bus in the demultiplexed $\mu P$ interface mode.                                                                                                                                                                                                                                               |

| 1                  | 1                        | $V_{DD}$                                     | I                                                | Supply voltage: 5 V ± 5%                                                                                                                                                                                                                                                                               |

| 27                 | 27                       | $V_{SS}$                                     | I                                                | Ground: 0 V                                                                                                                                                                                                                                                                                            |

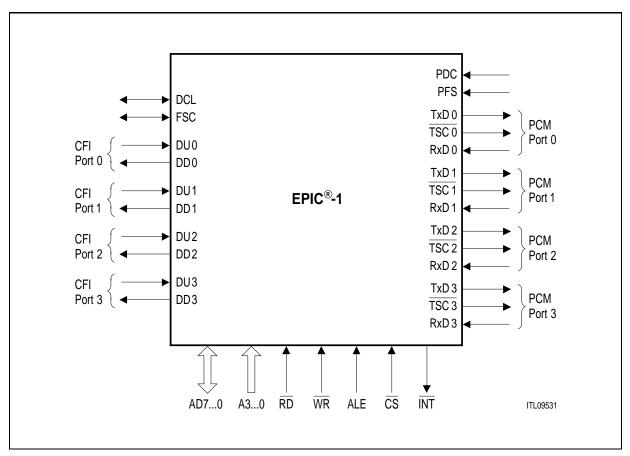

## 1.4 Logic Symbols

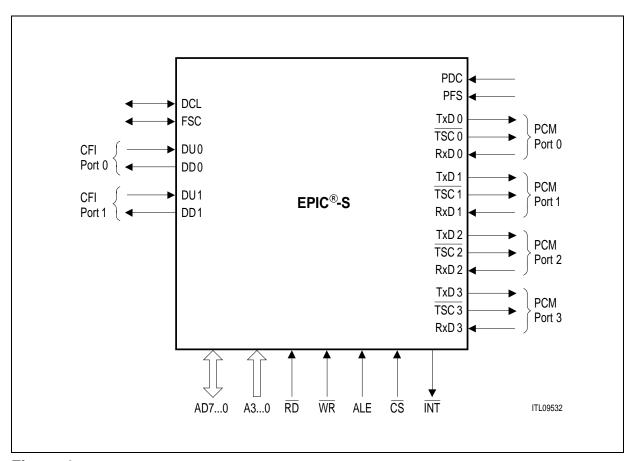

Figure 3 Logic Symbol of the EPIC®-1

Figure 4 Logic Symbol of the EPIC®-S

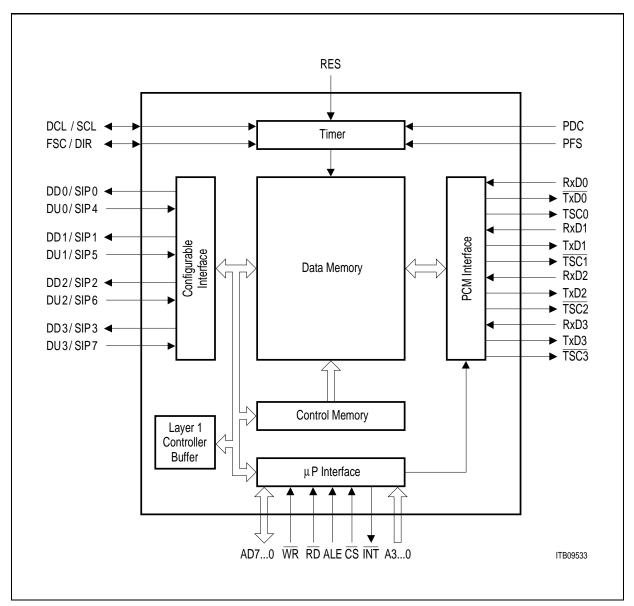

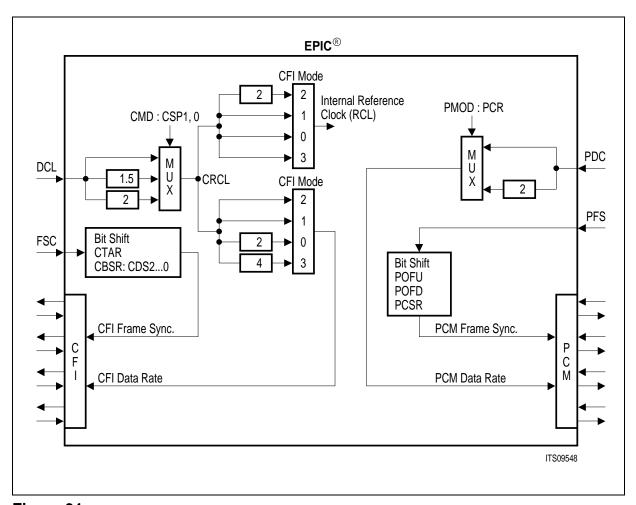

### 1.5 Functional Block Diagram

Figure 5

Functional Block Diagram EPIC®

### 1.6 Using the EPIC-S

The EPIC-S is based on the same technology as the EPIC-1 aside from only providing CFI port 0 and CFI port 1. Therefore this User's Manual applies to both, the EPIC-S and the EPIC-1.

When using the EPIC-S the user has to be aware not to program connections that would imply the not supported CFI ports.

The following points require specific attention:

- 1. During power up the EPIC-S must be supplied with an external Hardware Reset.

- 2. Register bit OMDR:CSB may be programmed to high (switch off standby of CFI interface) only after a Control Memory reset procedure with MACR:CMC3..0 =  $0_H$ .

- 3. The pins not available with respect to the EPIC-1 (PEB 2055) must not be programmed as outputs.

### 1.7 System Integration and Application

The main application fields of the EPIC are:

- Digital line cards with different architectures,

- Central control units of key systems,

- Analog line cards,

- Concentrators.

### 1.7.1 Digital Line Card

### 1.7.1.1 Switching, Layer-1 Control

The EPIC provides a switching capability for up to 32 digital subscribers between the PCM system highway and the IOM-2 interface (64 B-channels). Typically it switches 64-kbit/s channels between the PCM and the IOM-interfaces. Moreover it is able to handle also 16-, 32- and 128-kbit/s channels.

The signaling handler supports the command/indication (C/I) channel which is used to exchange predefined layer-1 information with the transceiver device.

A monitor handler supports the handshake protocol defined on the IOM-monitor channel. It allows programming of layer-1 devices which do not have a dedicated  $\mu P$  interface.

The EPIC can be operated in tandem, i.e. one device is active, another one is a backup device. The backup device can instantaneously take over from the active device when the active device fails. Due to this tandem operation capability and the high number of ISDN subscribers which can be connected to one EPIC, the use of single line cards is feasible.

Several line card architectures are possible.

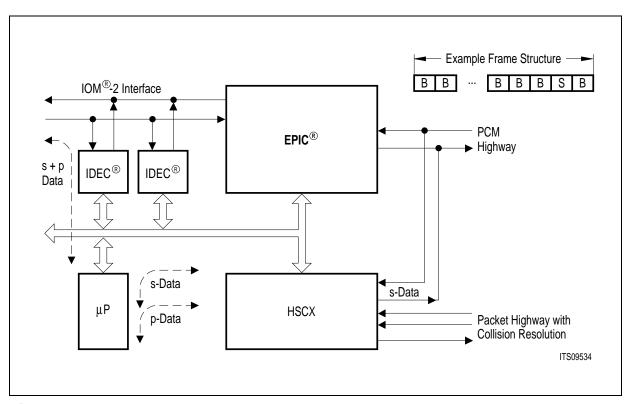

### 1.7.1.2 Decentralized D-Channel Handling

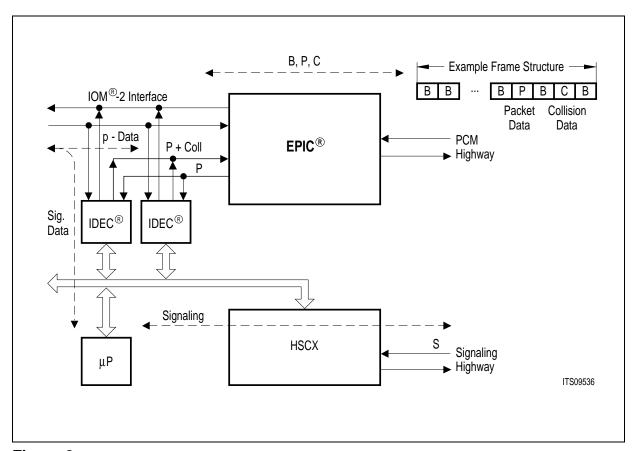

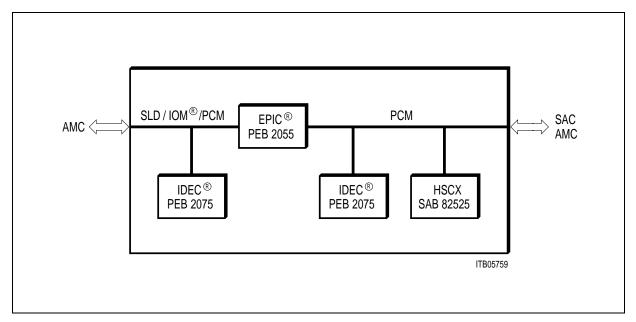

In completely decentral D-channel processing architectures (see **figure 6**), the processing capacity of the line card is usually designed to avoid blocking situations even under maximum conceivable D-channel traffic conditions. In such an architecture the EPIC switches the B-channels and performs C/I and monitor channel control.

The IDECs handle the layer 2 functions for signaling and data packets in the D-channel. They transfer the extracted data via the  $\mu P$  and an HDLC controller, e.g. the HSCX (High Level Serial Controller Extended SAB 82525) to the system. One of the channels of the HSCX may access either a time slot of programmable bandwidth on one of the system highways or a separate signalling highway.

In both cases the highway capacity used for packet traffic can be shared among several line cards due to the statistical multiplexing capabilities of the HSCX.

Figure 6

Line Card Architecture for Completely Decentral D-Channel Processing

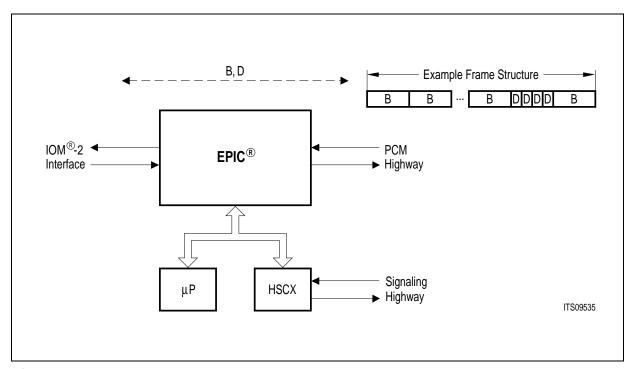

### 1.7.1.3 Central D-Channel Processing

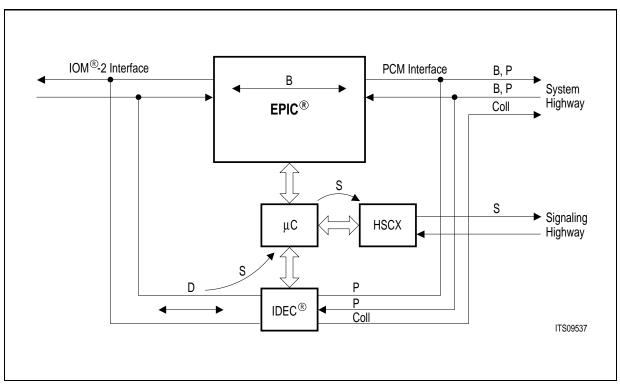

In this application the EPIC not only switches the B-channels and performs the C/I- and monitor channel control function, but switches also the D-channel data onto the system highway. In upstream direction the EPIC can combine up to four 16-kbit/s D-channels into one 64-kbit/s channel. In downstream direction it provides the capability to distribute one 64-kbit/s channel to four 16-kbit/s channels.

Figure 7

Digital Line Card Architecture with a Completely Central D-Channel Handling

# 1.7.1.4 Mixed D-Channel Processing, Signaling Decentralized, Packet Data Centralized

Another possibility is a mixed architecture with centralized packet data and decentralized signaling handling. This is a very flexible architecture which reduces the dynamic load of central processing units by evaluating the signaling information on the line card, but does not require resources for packet data handling. Any increase of packet data traffic does not necessitate a change in the line card architecture, the central packet handling unit can be expanded.

In this application IDECs are employed to handle the data on the D-channel. The IDECs separate signaling information from data packets. The signaling messages are transferred to the  $\mu P$ , which in turn hands them over to the group controller using the HSCX.

The packet data is processed differently. Together with the collision resolution information it is transferred to one IOM-2 port of the EPIC. The EPIC switches the channels to the PCM-highway, optionally combining four D-channels to one 64-kbit/s channel. In this configuration one IOM-2 interface is occupied by IDECs, reducing the total switching capability of the EPIC-1 to 24 ISDN-subscribers.

Figure 8

Line Card Architecture for Mixed D-Channel Processing

Alternatively, the packet and collision data can be directly exchanged between the IDECs and the PCM-highway. Thus, the full 32 subscriber switching capability of the EPIC is retained.

Figure 9

Line Card Architecture for Mixed D-Channel Processing

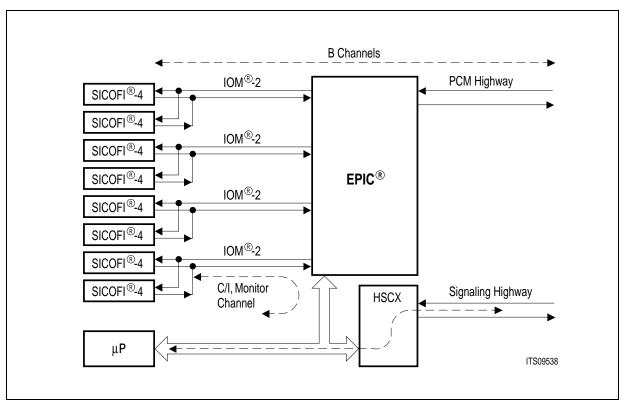

### 1.7.2 Analog Line Card

Together with the highly flexible Siemens codec filter circuits SLICOFI, SICOFI, SICOFI-2 or SICOFI-4 the EPIC constitutes an optimized analog subscriber board architecture.

The EPIC-1 handles the signalling and voice data for up to 64 subscriber channels with 64 kbit/s. The HSCX establishes the link to the group controller board.

Figure 10

Line Card Architecture for Analog Subscribers

#### 1.7.3 Packet Handlers

The EPIC is an important building block for networks based on either central, decentral or mixed signaling and packet data handling architectures. Its flexibility allows for the modification of the packet handling architecture according to the changing needs.

Thus it may be useful to add central packet handling groups to a network originally based on decentral signaling and packet handling. This may be the case if growing data packet traffic exceeds the initial capacity of the network. The result is a mixed architecture.

On the other hand, increasing packet handling demand on a few dedicated subscriber lines calls for solutions which back up the capacity at these few decentral line cards.

In both of these cases and several other applications, the EPIC is a powerful device for solving the problem of packet handling. In most applications it is used together with the IDEC (ISDN D channel Exchange Controller).

Decentralized and mixed packet handling has already been covered in the line card chapter. In the following, the centralized signaling/packet handlers built up with the EPIC will be described.

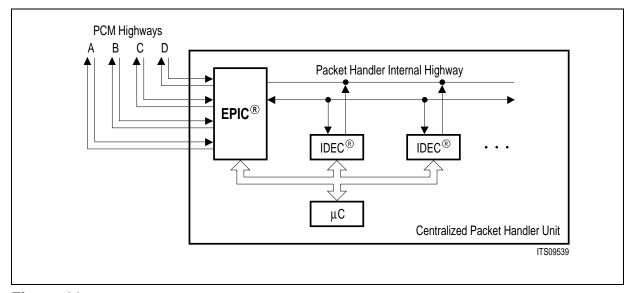

Central packet handling is used if many subscribers with a generally low demand for packet switching are to be connected to a system. Concentrating the packet servers for multiple users eliminates the need to provide a packet server channel for every user. The overall number of packet server channels can thus be reduced.

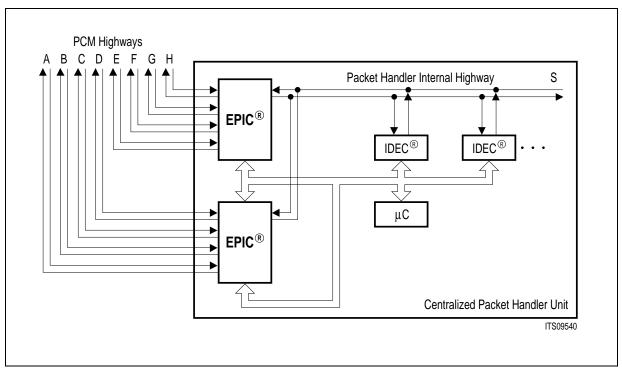

In such a central packet handling group, the EPIC performs the switching and concentrator function. It connects a variable number of PCM highways to the packet handler internal highway. HDLC controllers are also connected to this internal highway as illustrated in **figure 11**.

Figure 11

Centralized Packet Handler with a Single Internal Highway Connected to 4 PCM Highways

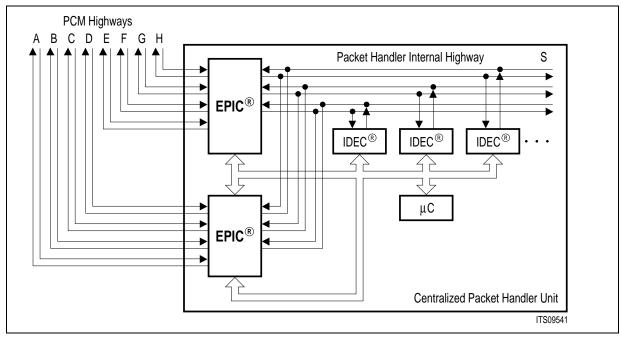

This figure shows one EPIC connecting four PCM highways to one packet handler internal highway. These highways are accessed by the IDECs, which are 4 channel HDLC controller and handle the packets. If more than four PCM highways shall be connected to the centralized packet handler, further EPICs are necessary. Such a configuration is shown in **figure 12**, where 8 highways are switched to one packet handler internal highway. In this case the two EPICs are connected in parallel at the packet handlers internal side.

Figure 12 Centralized Packet Handler with One Internal Highway Connected to 8 PCM Highways

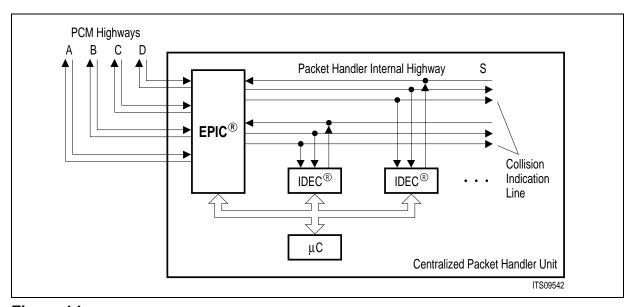

The data rate of the packet handler internal highway can be up to 4.096 Mbit/s. If this capacity is not sufficient, other packet handler internal highways may be added as depicted in **figure 13**.

Figure 13

Centralized Packet Handler with 3 Internal Highways

In some applications an additional collision resolution signal is required for the HDLC controllers. This information can be demultiplexed from the PCM highways to a third line for each packet handler internal highway (refer to **figure 14**).

Figure 14

Centralized Packet Handler with Internal Collision Line

The applications apply equally to centralized signaling as well as to data packet handlers.

### **2** Functional Description

In the following chapters the functions of the PEB 2055 will be covered in more detail.

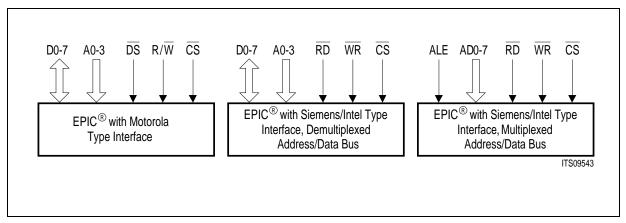

### 2.1 Bus Interface

All registers and the FIFOs of the EPIC are accessible via the flexible bus interface supporting Siemens / Intel and Motorola type microprocessors. Depending on the register functionality a read, write or read/write access is possible.

The bus interface consists of the following elements

- Data bus, 8-bit wide, D7 .. 0

- Address bus, 4-bit wide, A3 .. 0

- Chip select, CS

- Address latch enable, ALE

- Two read/write control lines: RD and WR (Intel mode) or DS and R/W (Motorola mode)

- Interrupt, INT

- Reset, RES

The ALE line is used to control the bus structure and interface type.

Table 1

Selectable Bus Configurations

| ALE                        | Interface       | Bus Structure | Pin 28 | Pin 29 |

|----------------------------|-----------------|---------------|--------|--------|

| Fixed to $V_{\mathrm{DD}}$ | Motorola        | demultiplexed | DS     | R/W    |

| Fixed to ground            | Siemens / Intel | demultiplexed | RD     | WR     |

| Switching                  | Siemens / Intel | multiplexed   | RD     | WR     |

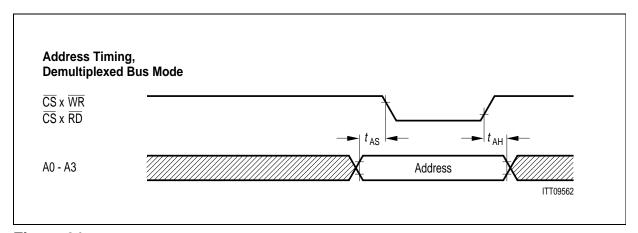

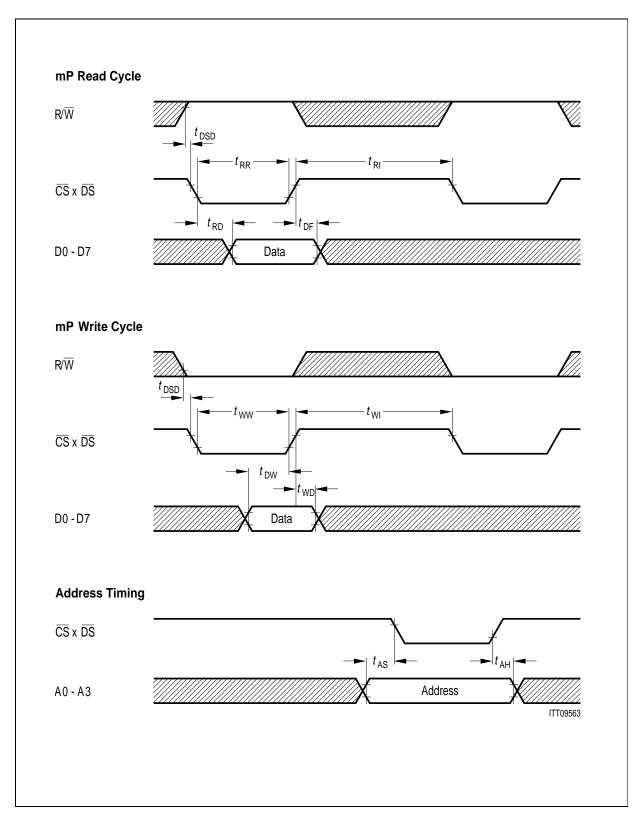

Figure 15

Selectable Bus Interface Structures

In order to simplify the use of 8- and 16-bit Siemens / Intel type CPUs, different register addresses are defined in multiplexed and demultiplexed bus mode (see **chapter 4.1**). In the multiplexed mode even addresses are used (AD0 always 0).

For a demultiplexed  $\mu P$  interface mode the OMDR:RBS bit is needed in addition to the address lines A3 .. A0. With OMDR:RBS (register bank selection) one of two register banks is selected.

RBS = "1" selects a set of registers used for device initialization (e.g. CFI and PCM interface initialization).

RBS = "0" switches to a group of registers necessary during operation (e.g. connection programming).

The OMDR register containing the RBS bit can be accessed with either value of RBS.

### Interrupts

An interrupt of the EPIC is indicated by activating the INT line. The detailed cause of the request can be determined by reading the ISTA register.

The INT output is level active. It remains active until all interrupt sources have been serviced. If a new status bit is set while an interrupt is being serviced, the INT remains active. However, for the duration of a write access to the MASK-register the INT line is deactivated. When using an edge-triggered interrupt controller, it is thus recommended to rewrite the MASK register at the end of any interrupt service routine.

Every interrupt source can be selectively masked by setting the respective bit of the MASK register. Such masked interrupts will not be indicated in the ISTA register, nor will they activate the INT line.

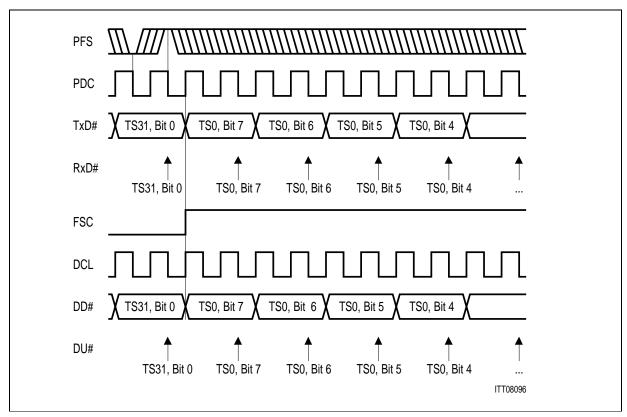

### 2.2 PCM Interface

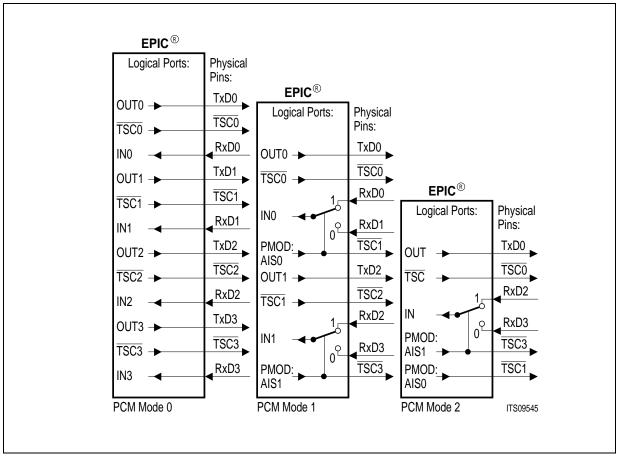

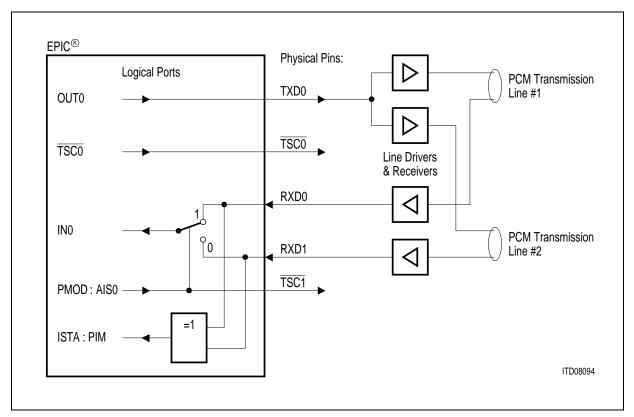

The PCM interface formats the data transmitted or received at the PCM highways. It can be configured to provide one (max. 8.192 Mbit/s), two (max. 4.096 Mbit/s) or four (max. 2.048 Mbit/s) PCM-ports, consisting each of a data receive (RxD), a data transmit (TxD) and an output tristate indication line (TSC).

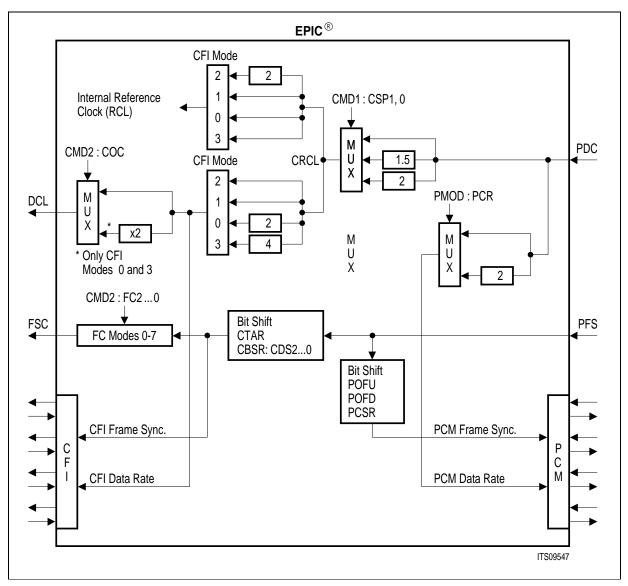

The PCM interface is supplied with a frame signal (PFS) and a PCM clock (PDC). To properly clock the PCM interface, a PDC signal with a frequency equal or twice the data rate has to be applied to the EPIC.

Port configuration, data rates, clock shift and sampling conditions are programmable.

### 2.3 Configurable Interface

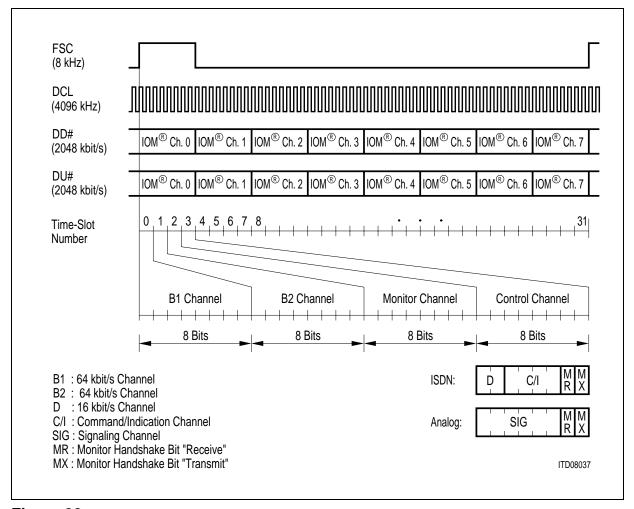

In order to optimize the on-board interchip communication, a very flexible serial interface is available. It formats the data transmitted or received at the DDn-, DUn- or SIPn-lines. Although it is typically used in IOM-2 or SLD-configuration to connect layer-1 devices, application specific frame structures can be defined (e.g. to interface ADPCM-converters or maintenance blocks).

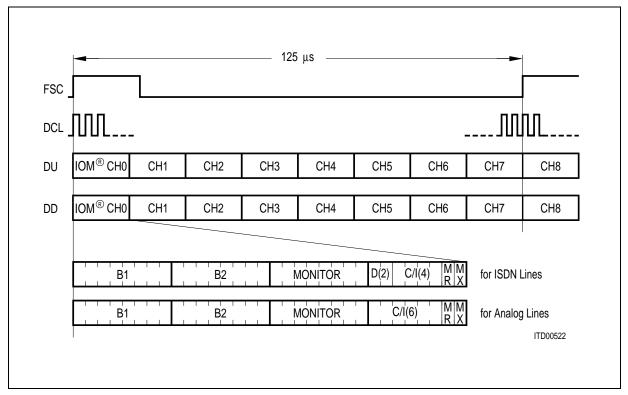

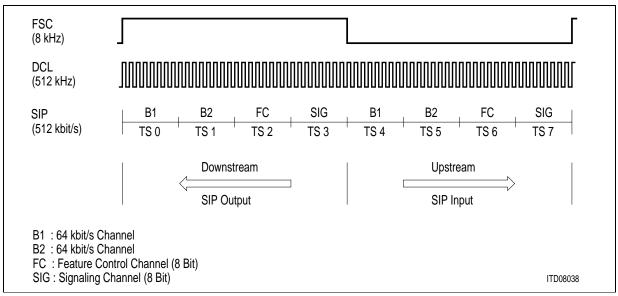

Figure 16 shows the IOM-2 Interface structure in Line Card Mode:

Figure 16 IOM®-2 Frame Structure with 2.048 Mbit/s Data Rate

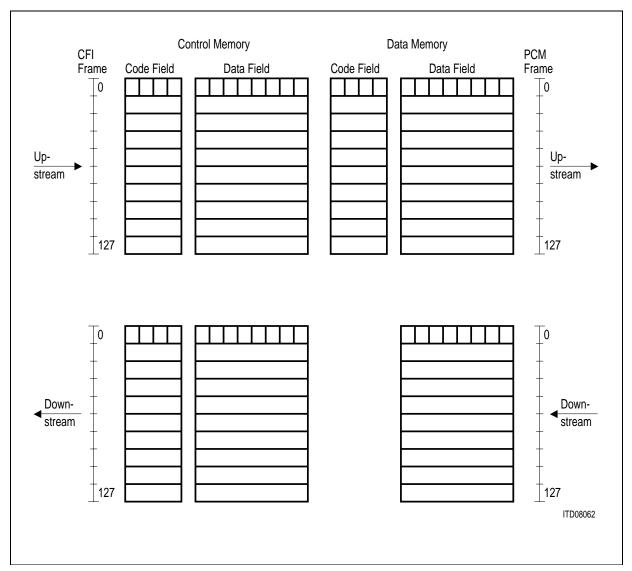

### 2.4 Memory Structure and Switching

The memory block of the EPIC performs the switching functionality. It consists of four sub blocks:

- Upstream data memory

- Downstream data memory

- Upstream control memory

- Downstream control memory.

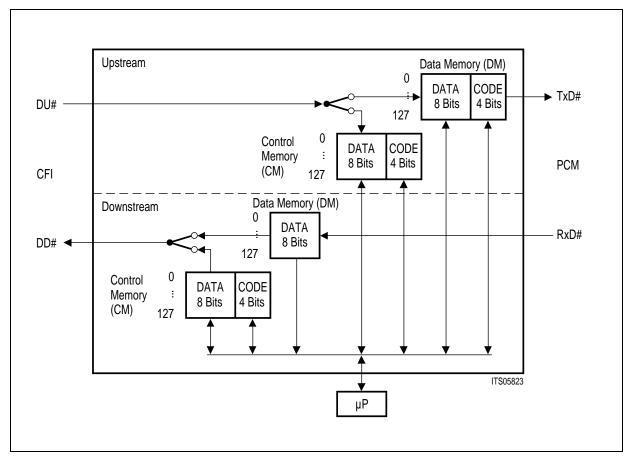

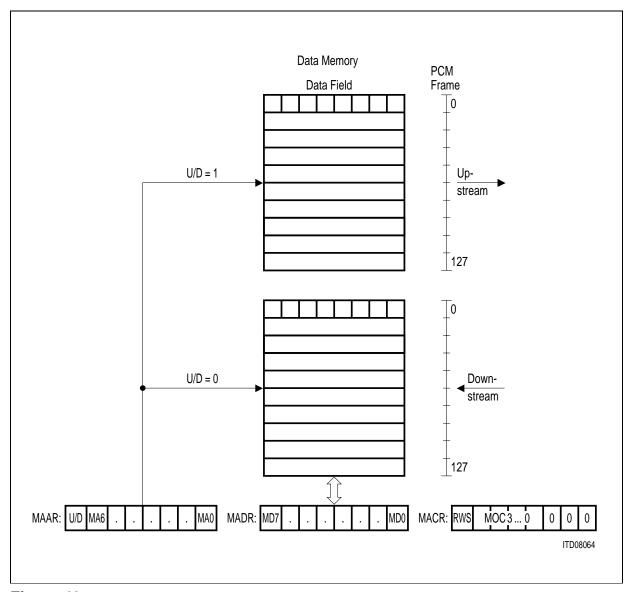

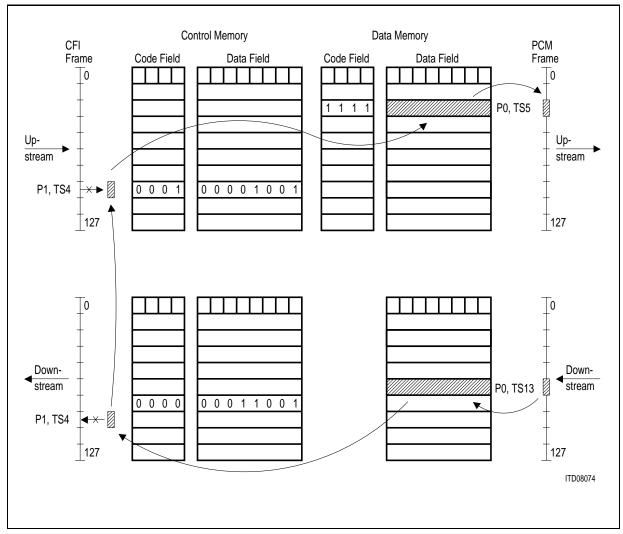

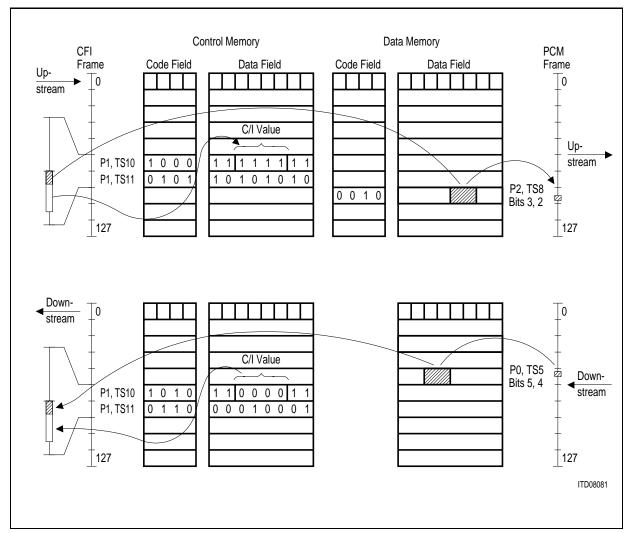

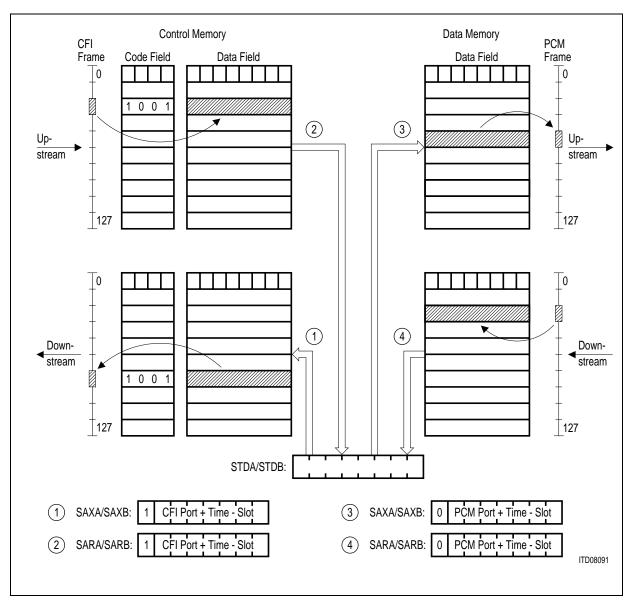

The PCM-interface reads periodically from the upstream (writes periodically to the downstream) data memory (cyclical access), see **figure 17**.

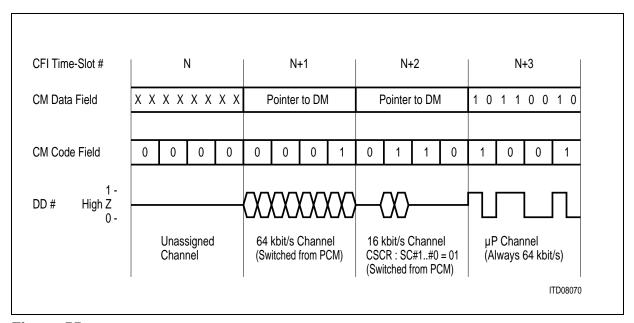

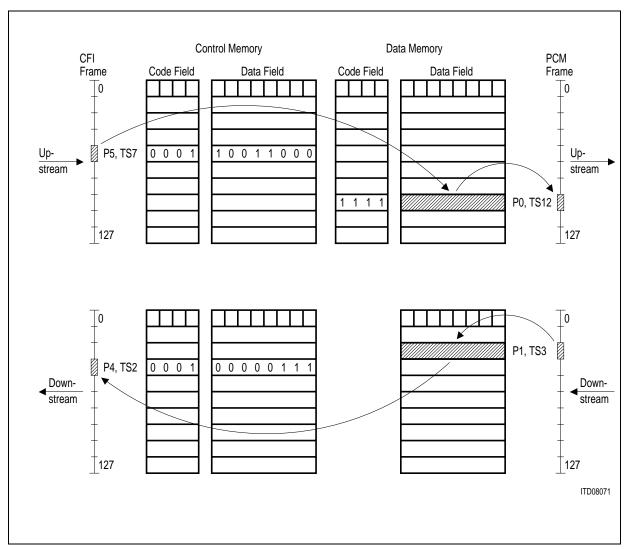

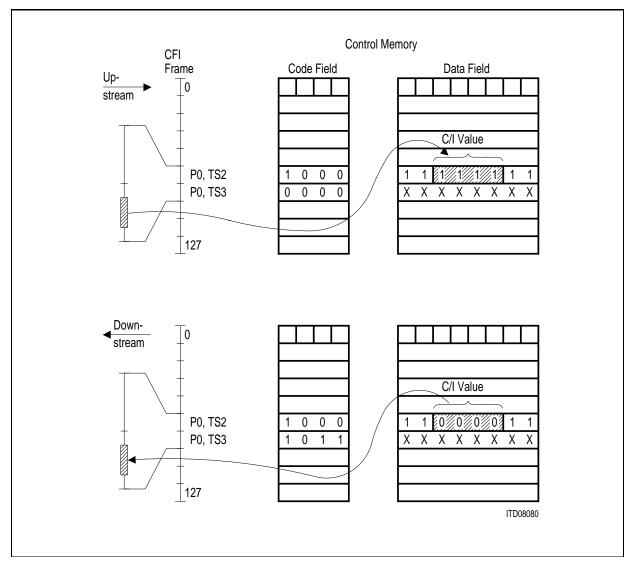

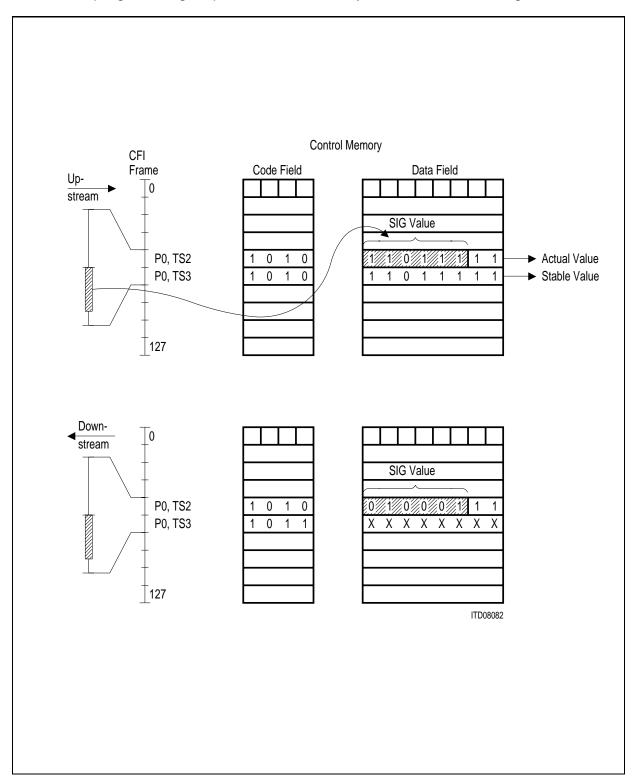

The CFI reads periodically the control memory and uses the extracted values as pointers to write to the upstream (read from the downstream) data memory (random access). In the case of C/I- or signaling channel applications the corresponding data is stored in the control memory. In order to select the application of choice, the control memory provides a code portion.

The control memory is accessible via the  $\mu P$ -interface. In order to establish a connection between CFI time slot A and PCM-interface time slot B, the B-pointer has to be loaded into the control memory location A.

Figure 17 EPIC®-1 Memory Structure

### 2.5 Pre-processed Channels, Layer-1 Support

The EPIC supports the monitor/feature control and control/signalling channels according to SLD or IOM-2 interface protocol.

The monitor handler controls the data flow on the monitor/feature control channel either with or without an active handshake protocol. To reduce the dynamic load of the CPU a 16-byte transmit/receive FIFO is provided.

The signaling handler supports different schemes (D-channel + C/I-channel, 6-bit signaling, 8-bit signaling).

In downstream direction the relevant content of the control memory is transmitted in the appropriate CFI time slot. In the case of centralized ISDN D-channel handling, a 16-kbit/s D-channel received at the PCM-interface is included.

In upstream direction the signaling handler monitors the received data. Upon a change it generates an interrupt, the channel address is stored in the 9-byte deep C/I FIFO and the actual value is stored in the control memory. In 6-bit and 8-bit signaling schemes a double last look check is provided.

### 2.6 Special Functions

- Synchronous transfer.

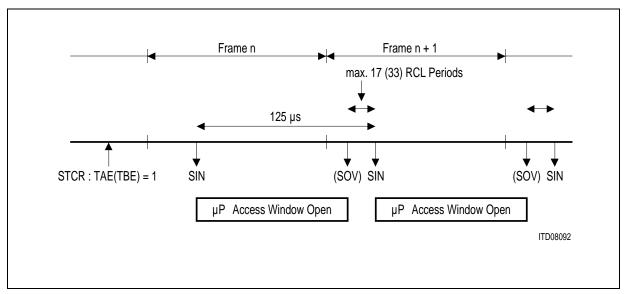

- This utility allows the synchronous  $\mu P$ -access to two independent channels on the PCM or CFI interface. Interrupts are generated to indicate the appropriate access windows.

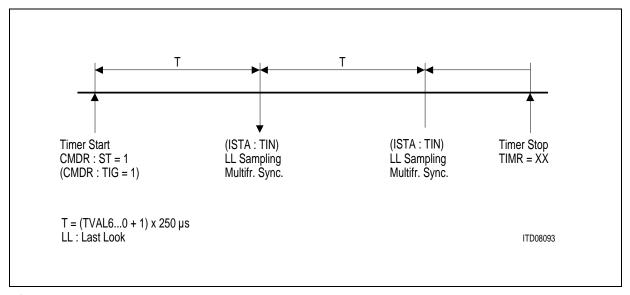

- 7-bit hardware timer.

- The timer can be used to cyclically interrupt the CPU, to determine the double last look period, to generate a proper CFI-multiframe synchronization signal or to generate a defined RESIN pulse width.

- Frame length checking.

The PFS period is internally checked against the programmed frame length.

- Alternative input functions.

- In PCM mode 1 and 2, the unused ports can be used for redundancy purposes. In these modes, for every active input port a second input port exists which can be connected to a redundant PCM line. Additionally the two lines are checked for mismatches.

### **Operational Description**

### 3 Operational Description

The EPIC, designed as a flexible line-card controller, has the following main applications:

- Digital line cards, with the CFI typically configured as IOM-2, IOM-1 (MUX) or SLD.

- Analog line cards, with the CFI typically configured as IOM-2 or SLD.

- Key systems, where the EPIC's ability to mix CFI configurations is utilized.

To operate the EPIC the user must be familiar with the device's microprocessor interface, interrupt structure and reset logic.

### 3.1 Microprocessor Interface Operation

The EPIC is programmed via an 8-bit parallel interface that can be selected to be

- (1) Motorola type, with control signals  $\overline{DS}$ , R/W and  $\overline{CS}$ .

- (2) Siemens / Intel non-multiplexed bus type, with control signals WR, RD and CS.

- (3) Siemens / Intel multiplexed address/data bus type, with control signals ALE, WR, RD, and CS.

The selection is performed via pin ALE as follows:

```

ALE tied to V_{\rm DD} \Rightarrow (1)

ALE tied to V_{\rm SS} \Rightarrow (2)

Edge on ALE \Rightarrow (3)

```

The occurrence of an edge on ALE, either positive or negative, at any time during the operation immediately selects interface type (3). A return to one of the other interface types is only possible by issuing a hardware reset.

In order to simplify the use of 8- and 16-bit Siemens / Intel type CPUs, different register addresses are defined in multiplexed and demultiplexed bus mode (see **chapter 4.1**). In the multiplexed mode even addresses are used (AD0 always 0).

For a demultiplexed  $\mu P$  interface mode the OMDR:RBS bit is needed in addition to the address lines A3 .. A0. With OMDR:RBS (register bank selection) one of two register banks is selected.

RBS = "1" selects a set of registers used for device initialization (e.g. CFI and PCM interface initialization).

RBS = "0" switches to a group of registers necessary during operation (e.g. connection programming).

The OMDR register containing the RBS bit can be accessed with either value of RBS.

### **Operational Description**

### Interrupts

An interrupt of the EPIC is indicated by activating the INT line. The detailed cause of the request can be determined by reading the ISTA register.

The INT-output is level active. It remains active until all interrupt sources have been serviced. If a new status bit is set while an interrupt is being serviced, the INT remains active. However, for the duration of a write access to the MASK-register the INT line is deactivated. When using an edge-triggered interrupt controller, it is thus recommended to rewrite the MASK-register at the end of any interrupt service routine.

Every interrupt source can be selectively masked by setting the respective bit of the MASK register. Such masked interrupts will not be indicated in the ISTA register, nor will they activate the  $\overline{\text{INT}}$  line.

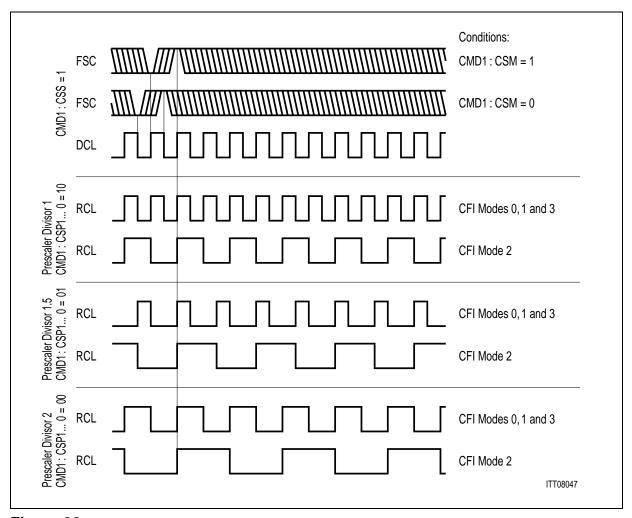

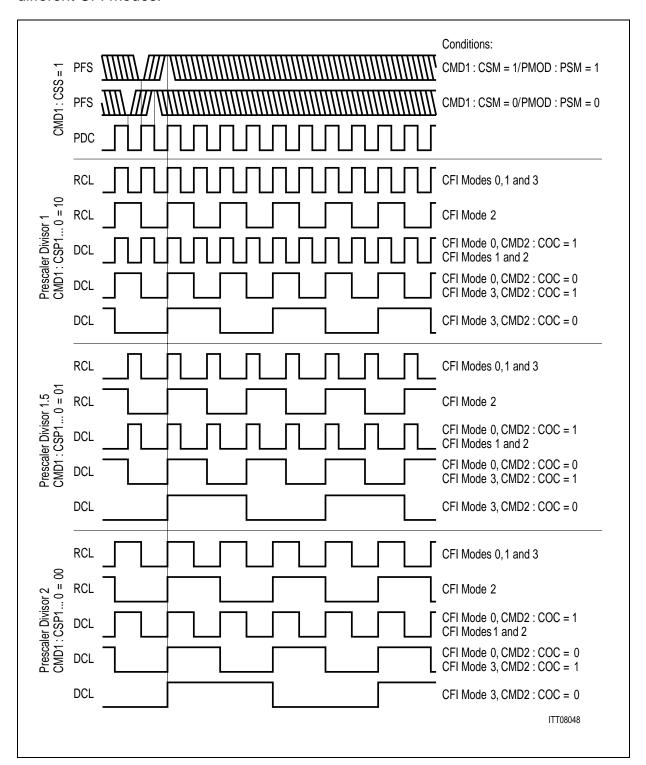

### 3.2 Clocking

To operate properly, the EPIC always requires a PDC-clock.

To synchronize the PCM side, the EPIC should normally also be provided with a PFS strobe. In most applications, the DCL and FSC will be output signals of the EPIC, derived from the PDC via prescalers.

If the required CFI data rate cannot be derived from the PDC, DCL and FSC can also be programmed as input signals. This is achieved by setting the EPIC CMD1:CSS-bit. Frequency and phase of DCL and FSC may then be chosen almost independently of the frequency and phase of PDC and PFS. However, the CFI clock source **must** still be synchronous to the PCM-interface clock source; i.e. the clock source for the CFI interface and the clock source for the PCM-interface must be derived from the same master clock.

**Chapter 5.2.2** provides further details on clocking.

### 3.3 Reset

A reset pulse of at least 4 PDC clock cycles has to be applied at the RES pin. The reset pulse sets all registers to their reset values described in **section 4**.

The EPIC is now in CM reset mode (refer to **4.2.6.7**). As the hardware reset does not affect the EPIC memories CM and DM, a "software reset" of the CM has to be performed. Subsequently the EPIC can be programmed to CM initialization, normal operation or test mode.

During reset the address latch enable pin ALE is evaluated to determine the bus interface type.

SIEMENS PEB 2055 PEF 2055

### **Operational Description**

### 3.4 EPIC® Operation

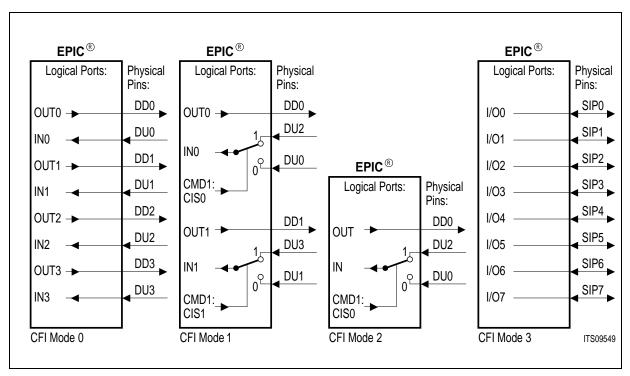

The EPIC is principally an intelligent switch of PCM data between two serial interfaces, the system interface (PCM interface) and the configurable interface (CFI). Up to 128 channels per direction can be switched dynamically between the CFI and the PCM-interfaces. The EPIC performs non-blocking space and time switching for these channels which may have a bandwidth of 16, 32, 64 or 128 kbit/s.

Both interfaces can be programmed to operate at different data rates of up to 8.192 Mbit/s. The PCM interface consists of up to four duplex ports with a tristate control signal for each output line. The configurable interface can be selected to provide either four duplex ports or 8 bi-directional (I/O) ports (EPIC-S: two duplex or 4 bi-directional ports).

The configurable interface incorporates a control block (layer-1 buffer) which allows the  $\mu P$  to gain access to the control channels of an IOM (ISDN-Oriented Modular) or SLD (Subscriber Line Data) interface. The EPIC can handle the layer-1 functions buffering the C/I and monitor channels for IOM compatible devices and the feature control and signaling channels for SLD compatible devices. One major application of the EPIC is therefore as line card controller on digital and analog line cards. The layer-1 and codec devices are connected to the CFI, which is then configured to operate as IOM-2, SLD or multiplexed IOM-1 interface.

The configurable interface of the EPIC can also be configured as plain PCM-interface i.e. without IOM- or SLD-frame structure. Since it's possible to operate the two serial interfaces at different data rates, the EPIC can then be used to adapt two different PCM systems.

The EPIC-1 can handle up to 32 ISDN-subscribers with their 2B + D channel structure or up to 64 analog subscribers with their 1B channel structure in IOM-configuration. In SLD- configuration up to 16 analog subscribers can be accommodated.

The EPIC-S can handle up to 16 ISDN-subscribers with their 2B + D channel structure or up to 32 analog subscribers with their 1B channel structure in IOM-configuration. In SLD- configuration up to 8 analog subscribers can be accommodated.

The system interface is used for the connection to a PCM backplane. On a typical digital line card, the EPIC switches the ISDN B channels and, if required, also the D channels to the PCM backplane. Due to its capability to dynamically switch the 16-kbit/s D channel, the EPIC is one of the fundamental building blocks for networks with either central, decentral or mixed signaling and packet data handling architecture.

SIEMENS PEB 2055 PEF 2055

**Operational Description**

### 3.4.1 PCM-Interface

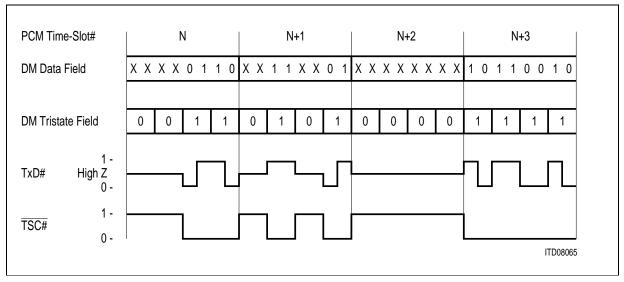

The serial PCM interface provides up to four duplex ports consisting each of a data transmit (TxD), a data receive (RxD) and a tristate control (TSC) line. The transmit direction is also referred to as the upstream direction, whereas the receive direction is referred to as the downstream direction.

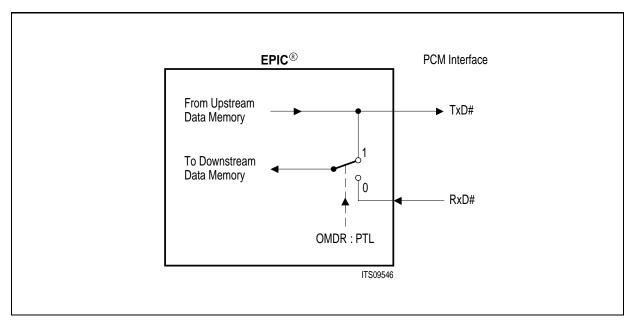

Data is transmitted and received at normal TTL / CMOS-levels, the output drivers being of the tristate type. Unassigned time slots may be either be tristated, or programmed to transmit a defined idle value. The selection of the states "high impedance" and "idle value" can be performed with a two bit resolution. This tristate capability allows several devices to be connected together for concentrator functions. If the output driver capability of the EPIC should prove to be insufficient for a specific application, an external driver controlled by the TSC can be connected.

The **PCM-standby function** makes it possible to switch all PCM-output lines to high impedance with a single command. Internally, the device still works normally. Only the output drivers are switched off.

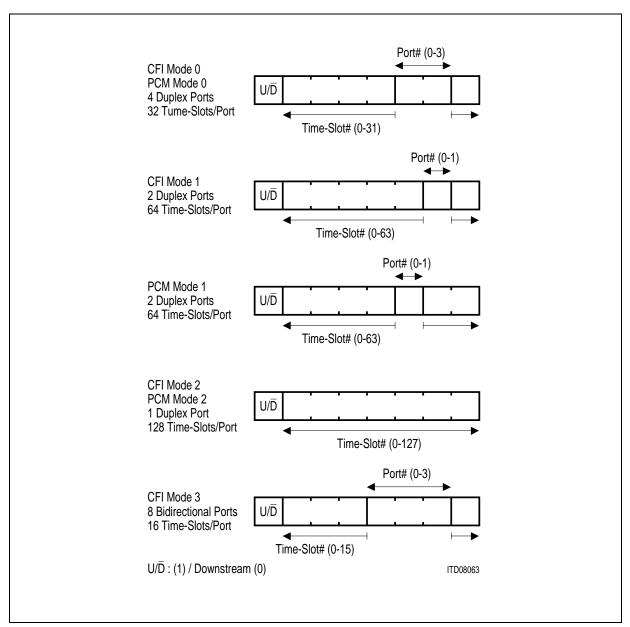

The number of time slots per 8-kHz frame is programmable in a wide range (from 4 to 128). In other words, the **PCM-data rate can range between 256 kbit/s up to 8.192 Mbit/s**. Since the overall switching capacity is limited to 128 time slots per direction, the number of PCM-ports also depends on the required number of time slots: in case of 32 time slots per frame (2.048 Mbit/s) for example, four highways are available, in case of 128 time slots per frame (8.192 Mbit/s), only one highway is available.

The partitioning between number of ports and number of bits per frame is defined by the **PCM mode.** There are three PCM-modes.

The timing characteristics at the PCM interface (data rate, bit shift, etc.) can be varied in a wide range, but they are the same for each of the four PCM ports, i.e. if a data rate of 2.048 Mbit/s is selected, all four ports run at this data rate of 2.048 Mbit/s.

The PCM-interface has to be clocked with a **PCM Data Clock (PDC)** signal having a frequency equal to or twice the selected PCM-data rate. In **single clock rate** operation, a frame consisting of 32 time slots, for example, requires a PDC of 2.048 MHz. In **double clock rate** operation, however, the same frame structure would require a PDC of 4.096 MHz.

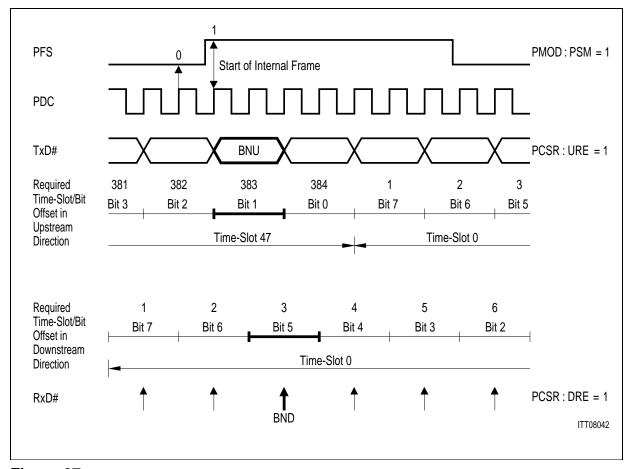

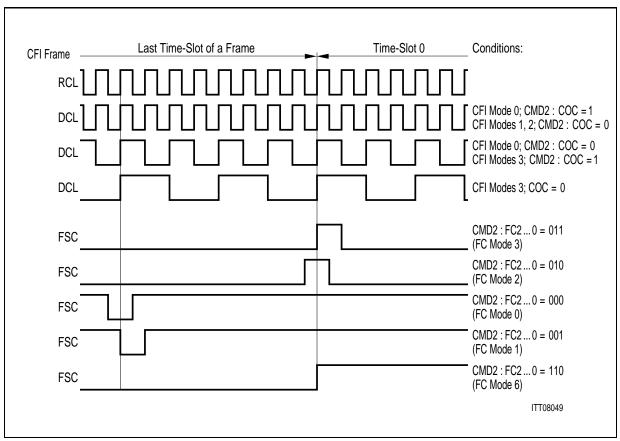

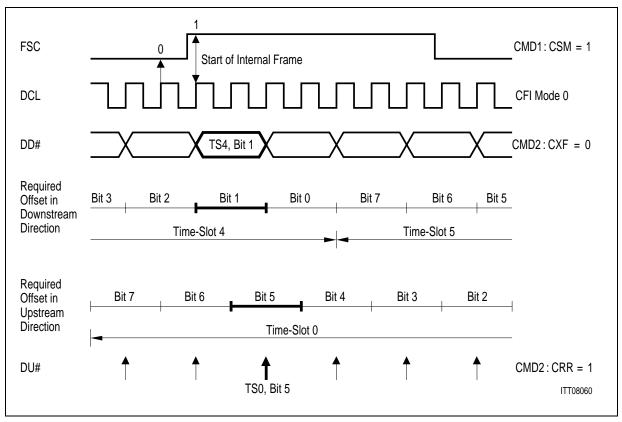

For the synchronization of the time slot structure to an external PCM system, a **PCM** Framing Signal (PFS) must be applied. The EPIC evaluates the rising PFS edge to reset the internal time slot counters. In order to adapt the PFS timing to different timing requirements, the EPIC can latch the PFS-signal with either the rising or the falling PDC edge. The PFS signal defines the position of the first bit of the internal PCM frame. The actual position of the external upstream and downstream PCM frames with respect to the framing signal PFS can still be adjusted using the **PCM offset function** of the EPIC.

### **Operational Description**

The offset can then be programmed such that PFS marks any bit number of the external frame.

Furthermore it is possible to select either the rising or falling PDC-clock edge for transmitting and sampling the PCM-data.

Usually, the repetition rate of the applied framing pulse PFS is identical to the frame period (125  $\mu s$ ). If this is the case, the loss of synchronism indication function can be used to supervise the clock and framing signals for missing or additional clock cycles. The EPIC checks the PFS-period internally against the duration expected from the programmed data rate. If, for example, double clock operation with 32 time slots per frame is programmed, the EPIC expects 512 clock periods within one PFS period. The synchronous state is reached after the EPIC has detected two consecutive correct frames. The synchronous state is lost if one bad clock cycle is found. The synchronization status (gained or lost) can be read from an internal register and each status change generates an interrupt.

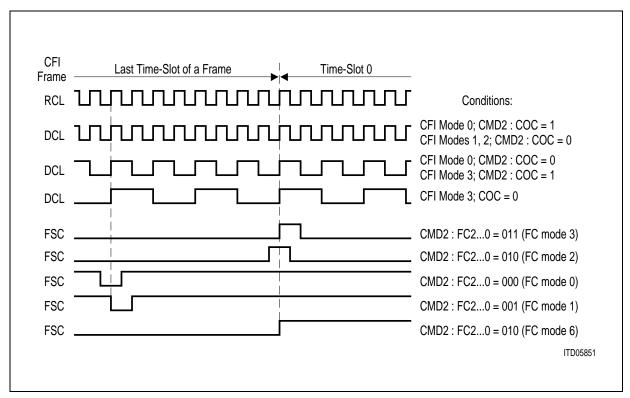

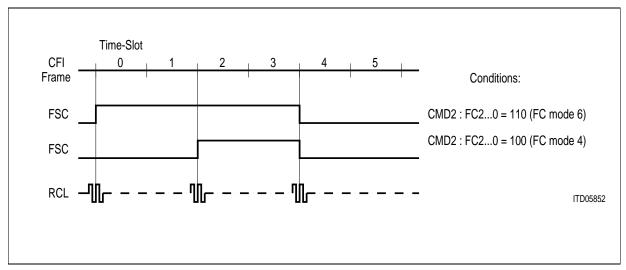

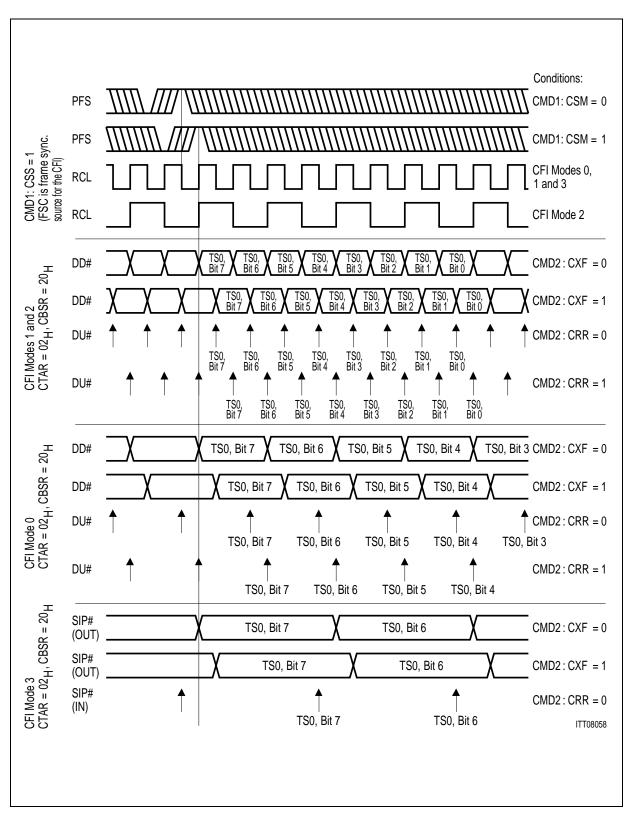

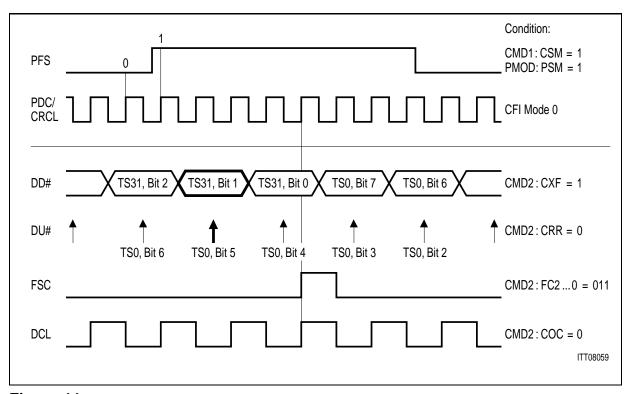

### 3.4.2 Configurable Interface

The serial configurable interface (CFI) can be operated either in duplex modes or in a bidirectional mode.

In **duplex modes** the EPIC-1 provides up to four ports (EPIC-S: up to two ports) consisting each of a data output ( $\overline{DD}$ ) and a data input ( $\overline{DU}$ ) line. The output pins are called "Data Downstream" pins and the input pins are called "Data Upstream" pins. These modes are especially suited to realize a standard serial PCM interface (PCM highway) or to implement an IOM (ISDN-Oriented Modular) interface. The IOM interface generated by the EPIC offers all the functionality like C/I- and monitor channel handling required for operating all kinds of IOM compatible layer-1 and codec devices.

In **bi-directional mode** the EPIC-1 provides eight bi-directional ports (SIP), the EPIC-S four bi-directional ports, respectively. Each time slot at any of these ports can individually be programmed as input or output. This mode is mainly intended to realize an SLD interface (Serial Line Data). In case of an SLD interface the frame consists of eight time slots where the first four time slots serve as outputs (downstream direction) and the last four serve as inputs (upstream direction). The SLD interface generated by the EPIC offers signaling and feature control channel handling.

Data is transmitted and received at normal TTL/CMOS-levels at the CFI. **Tristate or open drain output drivers** can be selected. In case of open drain drivers, external pull-up resistors are required. Unassigned output time slots may be switched to high impedance or be programmed to transmit a defined idle value. The selection between the states "high impedance" or "idle value" can be performed on a per time slot basis.

The **CFI-standby function** switches all CFI-output lines to high impedance with a single command. Internally the device still works normally, only the output drivers are switched off.

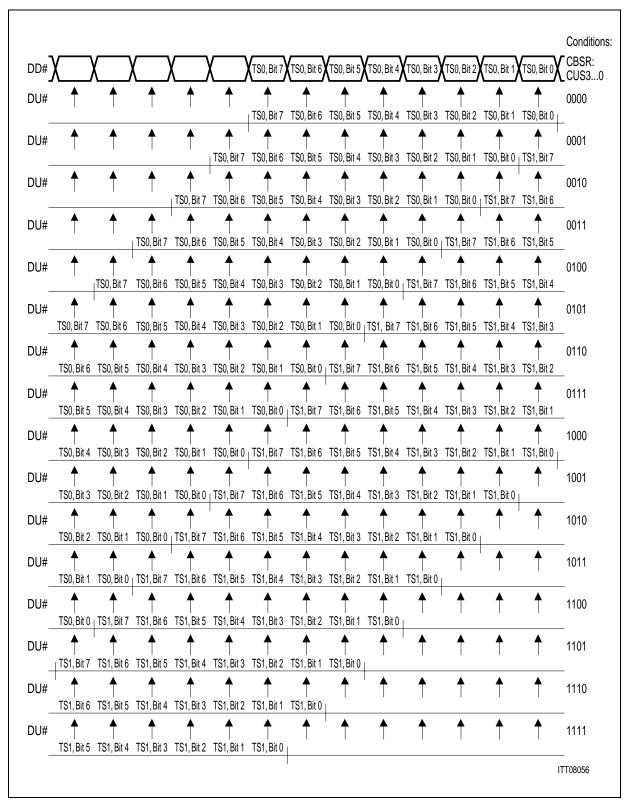

The number of time slots per 8-kHz frame is programmable from 2 to 128. In other words, the **CFI-data rate can range between 128 kbit/s up to 8.192 Mbit/s**. Since the overall switching capacity is limited to 128 time slots per direction, the number of CFI- ports also depends on the required number of time slots: in case of 32 time slots per frame (2.048 Mbit/s) for example, four (EPIC-S: two) highways are available, in case of 128 time slots per frame (8.192 Mbit/s), only one highway is available. Usually, the number of bits per 8-kHz frame is an integer multiple of the number of time slots per frame (1 time slot = 8 bits).

The timing characteristics at the CFI (data rate, bit shift, etc.) can be varied in a wide range, but they are the same for each of the four (EPIC-S: two) CFI-ports, i.e. if a data rate of 2.048 Mbit/s is selected, all four (EPIC-S: two) ports run at this data rate of 2.048 Mbit/s. It is thus not possible to have one port used in IOM-2 line card mode (2.048 Mbit/s) while another port is used in IOM-2 terminal mode (768 kbit/s)!

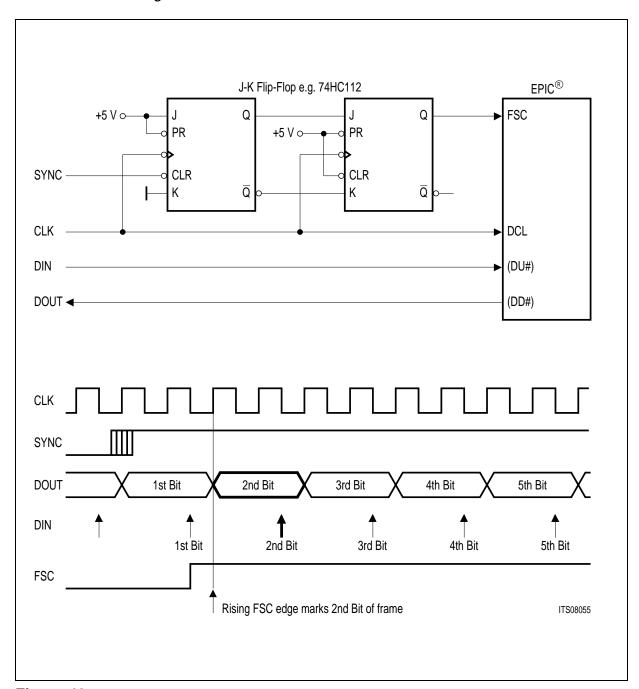

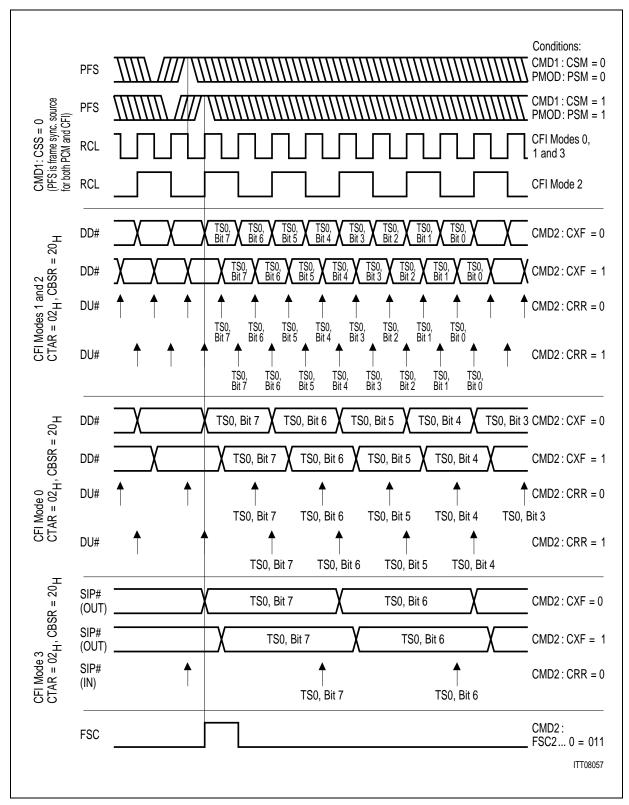

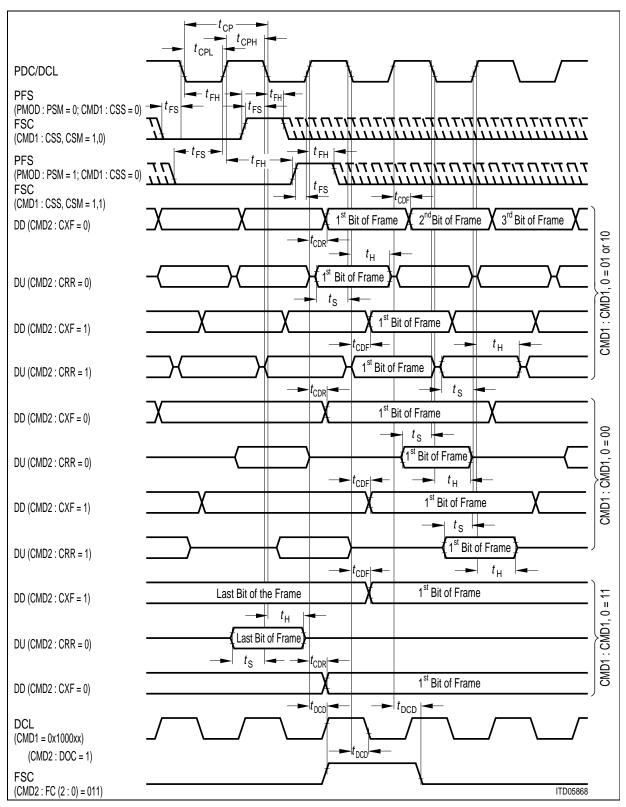

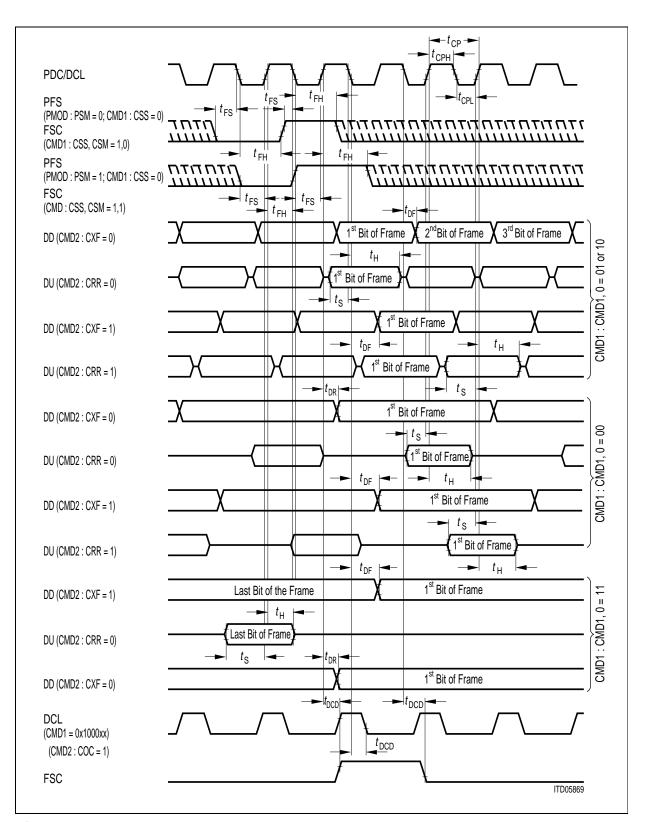

The clock and framing signals necessary to operate the configurable interface may be derived either from the clock and framing signals of the PCM interface (PDC and PFS pins), or may be fed in directly via the DCL and FSC pins.

In the first case, the CFI data rate is obtained by internally dividing down the PCM clock signal PDC. Several prescaler factors are available to obtain the most commonly used data rates. A CFI reference clock (CRCL) is generated out of the PDC-clock. The PCM-framing signal PFS is used to synchronize the CFI-frame structure. Additionally, the EPIC generates clock and framing signals as outputs to operate the connected subscriber circuits such as layer-1 and codec filter devices. The generated data clock DCL has a frequency equal to or twice the CFI data rate. The generated framing signal FSC can be chosen from a great variety of types to suit the different applications: IOM-2, multiplexed IOM-1, SLD, etc.

Note that if PFS is selected as the framing signal source, the FSC signal is an output with a fixed timing relationship with respect to the CFI data lines. The relationship between FSC and the CFI frame depends only on the selected FSC-output wave form (CMD2 register). The CFI offset function shifts both the frame and the FSC output signal with respect to the PFS signal.

In the second case, the CFI data rate is derived from the DCL-clock, which is now used as an input signal. The DCL clock may also first be divided down by internal prescalers before it serves as the CFI reference clock CRCL and before defining the CFI data rate. The framing signal FSC is used to synchronize the CFI frame structure.

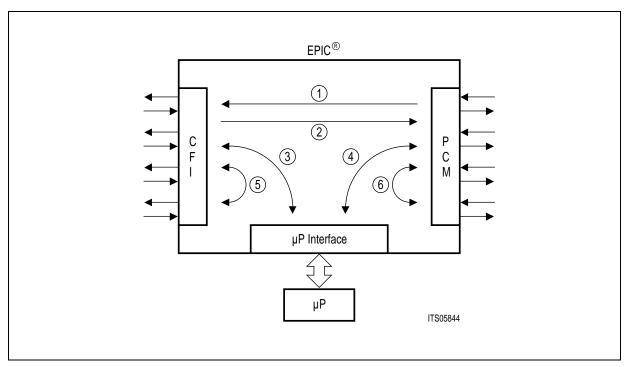

#### 3.4.3 Switching Functions

The major tasks of the EPIC part is to dynamically switch PCM data between the serial PCM interface, the serial configurable interface (CFI) and the parallel  $\mu P$  interface. All possible switching paths are shown in **figure 18**.

Figure 18

Switching Paths Inside the EPIC®-1

Note: The time slot selections in upstream direction are completely independent of the time slot selections in downstream direction.

Note: The same applies for the EPIC-S with the exception that only two CFI ports are provided.

# **CFI - PCM Time Slot Assignment**

Switching paths 1 and 2 of **figure 18** can be realized for a total number of 128 channels (EPIC-S: 64) per path, i.e. 128 (EPIC-S: 64) time slots in upstream and 128 (EPIC-S: 64) time slots in downstream direction. To establish a connection, the  $\mu P$  writes the addresses of the involved CFI and PCM time slots to the control memory. The actual transfer is then carried out frame by frame without further  $\mu P$  intervention.

The switching paths 5 and 6 can be realized by programming time slot assignments in the control memory. The total number for such loops is limited to the number of available time slots at the respective opposite interface, i.e. looping back a time slot from CFI to CFI requires a spare upstream PCM time slot and looping back a time slot from PCM to PCM requires a spare downstream and upstream CFI time slot.

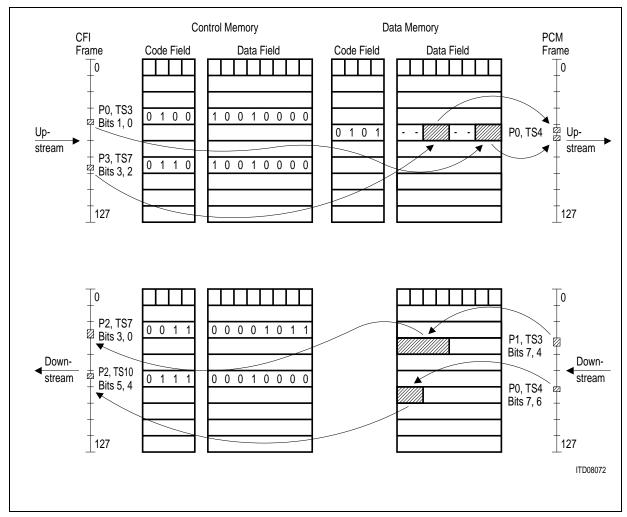

Time slot switching is always carried out on 8-bit time slots, the actual position and number of transferred bits can however be limited to 4-bit or 2-bit sub time slots within these 8-bit time slots. On the CFI side, only one sub time slot per 8-bit time slot can be switched, whereas on the PCM-interface up to 4 independent sub time slots can be switched.

Examples are given in **chapter 5.3**.

#### **Sub Time Slot Switching**

Sub time slot positions at the PCM-interface can be selected at random, i.e. each single PCM time slot may contain any mixture of 2- and 4-bit sub time slots. A PCM time slot may also contain more than one sub time slot. On the CFI however, two restrictions must be observed:

- Each CFI time slot may contain one and only one sub time slot.

- The sub-slot position for a given bandwidth within the time slot is fixed on a per port basis.

For more detailed information on sub-channel switching please refer to **chapter 5.4.2**.

#### μP Transfer

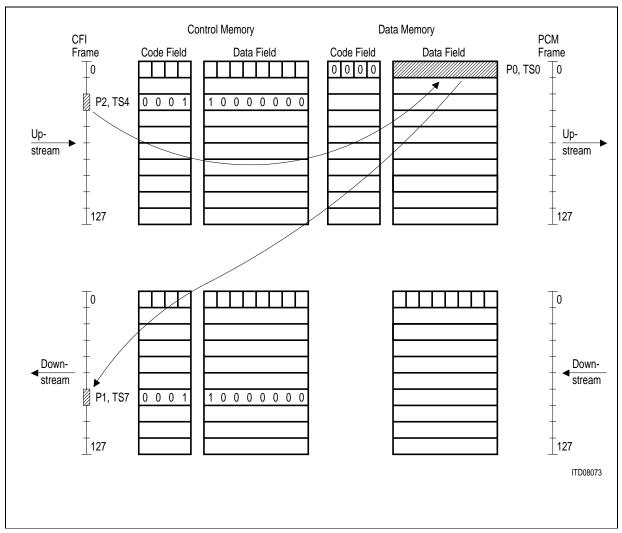

Switching paths 3 and 4 of **figure 18** can be realized for all available time slots. Path 3 can be implemented by defining the corresponding CFI time slots as " $\mu$ P channels" or as "pre-processed channels".

Each single time slot can individually be declared as " $\mu$ **P channel**". If this is the case, the  $\mu$ P can write a static 8-bit value to a downstream time slot which is then transmitted repeatedly in each frame until a new value is loaded. In upstream direction, the  $\mu$ P can read the received 8-bit value whenever required, no interrupts being generated.

The "pre-processed channel" option must always be applied to two consecutive time slots. The first of these time slots must have an even time slot number. If two time slots are declared as "pre-processed channels", the first one can be accessed by the monitor/feature control handler, which gives access to the frame via a 16-byte FIFO. Although this function is mainly intended for IOM- or SLD-applications, it could also be used to transmit or receive a "burst" of data to or from a 64-kbit/s channel. The second pre-processed time slot, the odd one, is also accessed by the  $\mu P.$  In downstream direction a 4-, 6- or 8-bit static value can be transmitted. In upstream direction the received 8-bit value can be read. Additionally, a change detection mechanism will generate an interrupt upon a change in any of the selected 4, 6 or 8 bits.

Pre-processed channels are usually programmed after Control Memory (CM) reset during device initialization. Resetting the CM sets all CFI time slots to unassigned channels (CM code "0000"). Of course, pre-processed channels can also be initialized or re-initialized in the operational phase of the device.

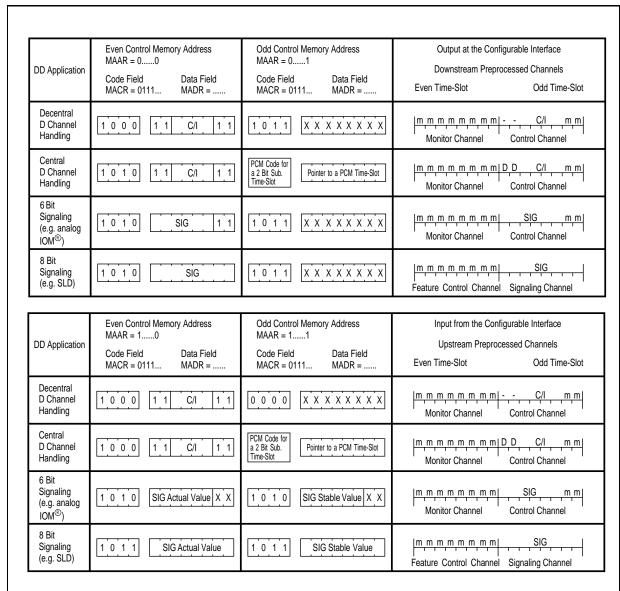

To program a pair of pre-processed channels the correct code for the selected handling scheme must be written to the CM. **Figure 19** gives an overview of the available pre-processing codes and their application. For further detail, please refer to **chapter 5.5**.

m: Monitor channel bits, these bits are treated by the monitor/feature control handler

ITD09544

Figure 19

Pre-processed Channel Codes

<sup>- :</sup> Inactive sub. time-slot, in downstream direction these bits are tristated (OMDR: COS = 0) or set to logical 1 (OMDR: COS = 1)

C/I: Command/Indication channel, these bits are exchanged between the CFI in/output and the CM data field. A change of the C/I bits in upstream direction causes an interrupt (ISTA:SFI). The address of the change is stored in the CIFIFO

$<sup>\</sup>label{eq:defD} D: D \ channel, these \ D \ channel \ bits \ are \ transparently \ switched \ to \ and \ from \ the \ PCM \ interface.$

SIG: Signaling Channel, these bits are exchanged between the CFI in/output and the CM data field. The SIG value which actual value was present in the last frame is stored as the actual value in the even address CM location. The stable value is updated stable value if a valid change in the actual value has been detected according to the last look algorithm. A change of the SIG stable value in upstream direction causes an interrupt (ISTA: CFI). The address of the change is stored in the CIFIFO.

#### **Synchronous Transfer**

For two channels, all switching paths of **figure 18** can also be realized using Synchronous Transfer. The working principle is that the  $\mu P$  specifies an input time slot (source) and an output time slot (destination). Both source and destination time slots can be selected independently from each other at either the PCM or CFI interfaces. In each frame, the EPIC first transfers the serial data from the source time slot to an internal data register from where it can be read and if required overwritten or modified by the  $\mu P$ . This data is then fed forward to the destination time slot.

**Chapter 5.7** provides examples of such transfers.

#### 3.4.4 Special Functions

#### **Hardware Timer**

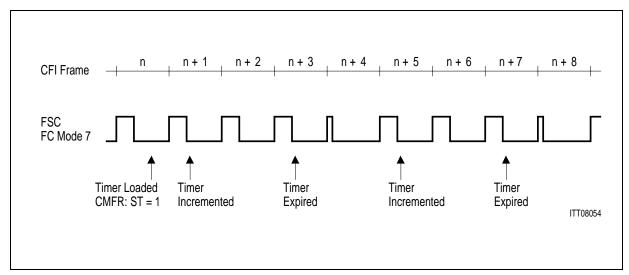

The EPIC-1 provides a hardware timer which continuously interrupts the  $\mu P$  after programmable time periods. The timer period can be selected in the range of 250  $\mu$ s up to 32 ms in multiples of 250  $\mu$ s. Beside the interrupt generation, the timer can also be used to determine the last look period for 6- and 8-bit signaling channels on IOM-2 and SLD interfaces and for the generation of an FSC multiframe signal (see **chapter 5.8.1**).

#### **Power and Clock Supply Supervision**

The Connection Memory CM is supervised to data falsification due to clock or power failure. If such an inappropriate clocking or power failure occurs, the  $\mu P$  is requested to reinitialize the device.

#### **Operational Description**

#### 3.5 Initialization Procedure

For proper initialization of the EPIC the following procedure is recommended:

#### 3.5.1 Hardware Reset

A reset pulse can be applied at the RES pin for at least 4 PDC clock cycles. The reset pulse sets all registers to their reset values (refer to **chapter 4.1**).

Note: In this state DCL and FSC do not provide any clock signals.

#### 3.5.2 EPIC® Initialization

#### 3.5.2.1 Register Initialization

The PCM and CFI configuration registers (PMOD, PBNR, ..., CMD1, CMD2, ...) have to be programmed to the values required for the application. The correct setting of the PCM and CFI registers is important in order to obtain a reference clock (RCL) which is consistent with the externally applied clock signals.

The state of the operation mode (OMDR:OMS1..0 bits) does not matter for this programming step.

PMOD = PCM-mode, timing characteristics, etc.

PBNR = Number of bits per PCM-frame

POFD = PCM-offset downstream POFU = PCM-offset upstream

PCSR = PCM-timing

CMD1 = CFI-mode, timing characteristics, etc.

CMD2 = CFI-timing

CBNR = Number of bits per CFI-frame

CTAR = CFI-offset (time slots)

CBSR = CFI-offset (bits)

CSCR = CFI-sub channel positions

## 3.5.2.2 Control Memory Reset

Since the hardware reset does not affect the EPIC memories (Control and Data Memories), it is mandatory to perform a "software reset" of the CM. The CM code "0000" $_{\rm B}$  (unassigned channel) should be written to each location of the CM. The data written to the CM data field is then don't care, e.g. FF $_{\rm H}$ .

OMDR:OMS1..0 must be to "00"<sub>B</sub> for this procedure (reset value).

$MADR = FF_H$   $MACR = 70_H$  Wait for STAR:MAC = "0"

The resetting of the complete CM takes 256 RCL clock cycles. During this time, the STAR:MAC-bit is set to logical "1".

#### 3.5.2.3 Initialization of Pre-processed Channels

After the CM reset, all CFI time slots are unassigned. If the CFI is used as a plain PCM interface, i.e. containing only switched channels (B channels), the initialization steps below are not required. The initialization of pre-processed channels applies only to IOM or SLD applications.

An IOM or SLD "channel" consists of four consecutive time slots. The first two time slots, the B channels need not be initialized since they are already set to unassigned channels by the CM reset command. Later, in the application phase of the software, the B channels can be dynamically switched according to system requirements. The last two time slots of such an IOM or SLD channel, the pre-processed channels must be initialized for the desired functionality. There are four options that can be selected:

Table 2

Pre-processed Channel Options at the CFI

| Even CFI Time Slot              | Odd CFI Time Slot                                                        | Main<br>Application                  |

|---------------------------------|--------------------------------------------------------------------------|--------------------------------------|

| Monitor/feature control channel | 4-bit C/I channel, D channel not switched (decentral D channel handling) | IOM-1 or IOM-2<br>digital subscriber |

| Monitor/feature control channel | 4-bit C/I channel, D channel switched (central D ch. handling)           | IOM-1 or IOM-2<br>digital subscriber |

| Monitor/feature control channel | 6-bit SIG channel                                                        | IOM-2, analog<br>subscriber          |

| Monitor/feature control channel | 8-bit SIG/channel                                                        | SLD, analog<br>subscriber            |

Also refer to **figure 19**.

#### Example

In CFI-mode 0 all four CFI-ports shall be initialized as IOM-2 ports with a 4-bit C/I-field and decentral D channel handling.

CFI time slots 0, 1, 4, 5, 8, 9 ... 28, 29 of each port are B channels and need not to be initialized.

CFI time slots 2, 3, 6, 7, 10, 11, ..., 30, 31 of each port are pre-processed channels and need to be initialized:

#### CFI-port 0, time slot 2 (even), downstream

MADR =  $FF_H$  ; the C/I-value "1111" will be transmitted upon CFI activation MAAR =  $08_H$  ; addresses ts 2 down MACR =  $78_H$  ; CM-code "1000"

Wait for STAR:MAC = 0

## CFI-port 0, time slot 3 (odd), downstream

$MADR = FF_H$ ; don't care

$MAAR = 09_{H}$ ; addresses ts 3 down MACR =  $7B_{H}$ ; CM-code "1011"

Wait for STAR:MAC = 0

## CFI-port 0, time slot 2 (even), upstream

MADR =  $FF_H$ ; the C/I-value "1111" is expected upon CFI activation

MAAR =  $88_H$  ; address ts 2 up MACR =  $78_H$  ; CM-code "1000"

Wait for STAR:MAC = 0

## CFI-port 0, time slot 3 (odd), upstream

$MADR = FF_H$ ; don't care

MAAR =  $89_H$  ; address ts 3 up MACR =  $70_H$  ; CM-code "0000"

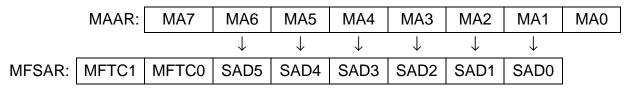

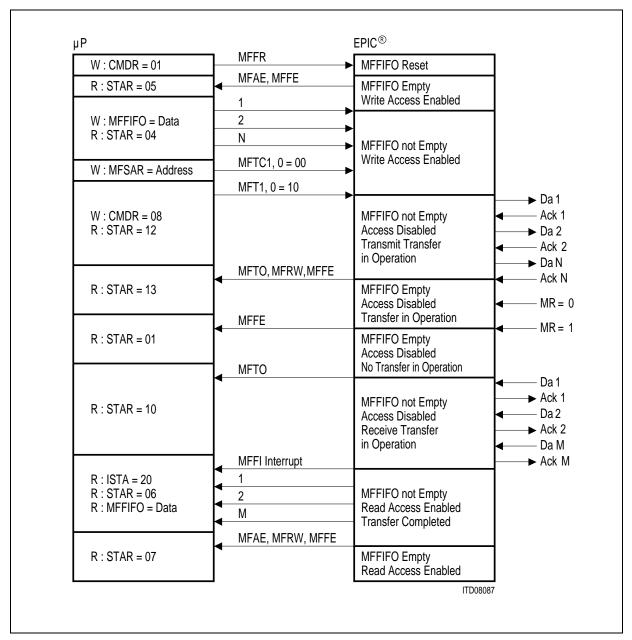

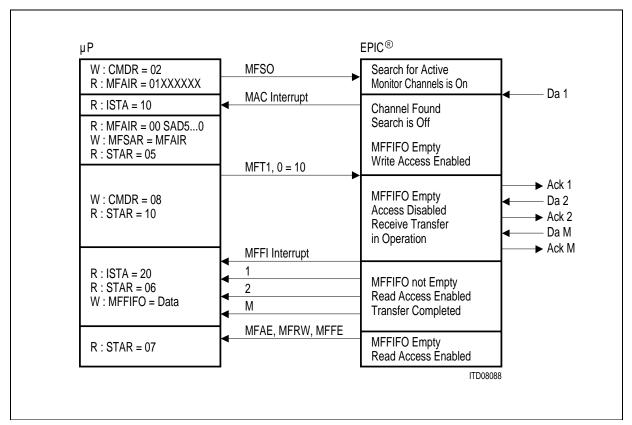

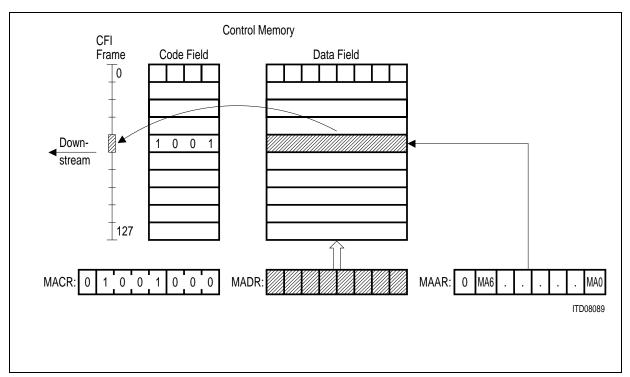

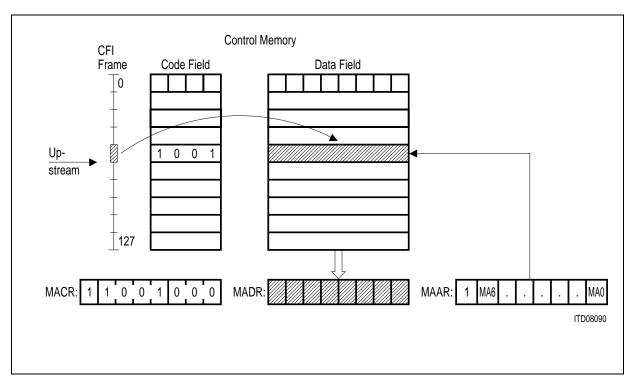

Wait for STAR:MAC = 0