Wired Communications

Never stop thinking.

#### **Edition March 2001**

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 2001.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Q-SMINT<sup>®</sup>O 2B1**Q S**econd Gen. **M**odular **I**SDN **NT** (**O**rdinary) PEF 80912/80913 Version 1.3

# Wired Communications

| Previous Version: Preliminary Data Sheet 10.00  Page Subjects (major changes since last revision)  All Editorial changes, addition of notes for clarification etc.  Table 1, Chapter 1.3  Chapter 2.4.5.1 S-transceiver NT state machine: added note: 'By setting the Test Mode pins TM0-2 to '010' / '011': Continuous Pulses / Single Pulses, the S-transceiver starts sending the corresponding test signal, but no state transition is invoked.'  Chapter 2.4.5.1 'DR'  Figure 16 Corrected figure: 'Complete Activation Initiated by Exchange': info4 is sent by the NT (not byTE)  Chapter 4.1 Absolute Maximum Ratings: Maximum Voltage on VDD: 4.2V (before: 4.6V)  Chapter 4.2 Input/output leakage current set to 10μA (before: 1μA)  Table 19 U-transceiver characteristics: enhanced S/N+D for 80913 and threshold level for 80912 and 80913 distinguished  Chapter 4.6.3 External circuitry for T-SMINT updated                                                                                                                                                                  | Revision History: |                                                                                                                             | March 2001                                                                |                          | DS 1           |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------|----------------|--|

| All Editorial changes, addition of notes for clarification etc.  Table 1, Chapter 1.3  Chapter 2.4.5.1 S-transceiver NT state machine: added note: 'By setting the Test Mode pins TM0-2 to '010' / '011': Continuous Pulses / Single Pulses, the S-transceiver starts sending the corresponding test signal, but no state transition is invoked.'  Chapter 2.4.5.1 C/I commands: removed 'unconditional command' from description C/I-command 'DR'  Figure 16 Corrected figure: 'Complete Activation Initiated by Exchange': info4 is sent by the NT (not byTE)  Chapter 4.1 Absolute Maximum Ratings: Maximum Voltage on VDD: 4.2V (before: 4.6V)  Chapter 4.1 Input/output leakage current set to 10μA (before: 1μA)  Table 19 U-transceiver characteristics: enhanced S/N+D for 80913 and threshold level for 80912 and 80913 distinguished  Chapter 4.6.3 Parameters of the UVD/POR Circuit: defined reduced range of hysteresis: min. 30mV/max. 90mV relaxed upper limit of Detection Threshold to 2.92V (before: 2.9V) defined max. rising VDD for power-on                             | Previous Version: |                                                                                                                             | Preliminary Data Sh                                                       | eet 10.00                |                |  |

| Table 1, Chapter 1.3  Chapter 2.4.5.1  S-transceiver NT state machine: added note: 'By setting the Test Mode pins TM0-2 to '010' / '011': Continuous Pulses / Single Pulses, the S-transceiver starts sending the corresponding test signal, but no state transition is invoked.'  Chapter 2.4.5.1  C/I commands: removed 'unconditional command' from description C/I-command 'DR'  Figure 16  Corrected figure: 'Complete Activation Initiated by Exchange': info4 is sent by the NT (not byTE)  Chapter 4.1  Absolute Maximum Ratings: Maximum Voltage on VDD: 4.2V (before: 4.6V)  Chapter 4.1  Refined references for ESD requirements:'(CDM), EIA/JESD22-A114B (HBM)'  Chapter 4.2  Input/output leakage current set to 10μA (before: 1μA)  Table 19  U-transceiver characteristics: enhanced S/N+D for 80913 and threshold level for 80912 and 80913 distinguished  Chapter 4.6.3  Parameters of the UVD/POR Circuit: defined reduced range of hysteresis: min. 30mV/max. 90mV relaxed upper limit of Detection Threshold to 2.92V (before: 2.9V) defined max. rising VDD for power-on | Page              | Subjects (ma                                                                                                                | ajor changes since la                                                     | st revision)             |                |  |

| <ul> <li>Chapter 1.3</li> <li>Chapter 2.4.5.1</li> <li>S-transceiver NT state machine:</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | All               | Editorial chan                                                                                                              | ges, addition of notes fo                                                 | r clarification etc.     |                |  |

| <ul> <li>added note: 'By setting the Test Mode pins TM0-2 to '010' / '011': Continuous Pulses / Single Pulses, the S-transceiver starts sending the corresponding test signal, but no state transition is invoked.'</li> <li>Chapter 2.4.5.1</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                 | introduced ne                                                                                                               | introduced new version 80913 with extended performance of the U-interface |                          |                |  |

| <ul> <li>2.4.5.1 'DR'</li> <li>Figure 16 Corrected figure: 'Complete Activation Initiated by Exchange': info4 is sent by the NT (not byTE)</li> <li>Chapter 4.1 Absolute Maximum Ratings: Maximum Voltage on VDD: 4.2V (before: 4.6V)</li> <li>Chapter 4.1 Refined references for ESD requirements:'(CDM), EIA/JESD22-A114B (HBM)'</li> <li>Chapter 4.2 Input/output leakage current set to 10μA (before: 1μA)</li> <li>Table 19 U-transceiver characteristics: enhanced S/N+D for 80913 and threshold level for 80912 and 80913 distinguished</li> <li>Chapter 4.6.3 defined reduced range of hysteresis: min. 30mV/max. 90mV relaxed upper limit of Detection Threshold to 2.92V (before: 2.9V) defined max. rising VDD for power-on</li> </ul>                                                                                                                                                                                                                                                                                                                                             | •                 | added note :<br>Pulses / Sing                                                                                               | 'By setting the Test M<br>le Pulses, the S-transo                         | eiver starts sending the |                |  |

| info4 is sent by the NT (not byTE)  Chapter 4.1 Absolute Maximum Ratings: Maximum Voltage on VDD: 4.2V (before: 4.6V)  Chapter 4.1 Refined references for ESD requirements:'(CDM), EIA/JESD22-A114B (HBM)'  Chapter 4.2 Input/output leakage current set to 10μA (before: 1μA)  Table 19 U-transceiver characteristics: enhanced S/N+D for 80913 and threshold level for 80912 and 80913 distinguished  Chapter Parameters of the UVD/POR Circuit: defined reduced range of hysteresis: min. 30mV/max. 90mV relaxed upper limit of Detection Threshold to 2.92V (before: 2.9V) defined max. rising VDD for power-on                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •                 |                                                                                                                             | •                                                                         |                          |                |  |

| <ul> <li>Chapter 4.1 Refined references for ESD requirements:'(CDM), EIA/JESD22-A114B (HBM)'</li> <li>Chapter 4.2 Input/output leakage current set to 10μA (before: 1μA)</li> <li>Table 19 U-transceiver characteristics: enhanced S/N+D for 80913 and threshold level for 80912 and 80913 distinguished</li> <li>Chapter Parameters of the UVD/POR Circuit: defined reduced range of hysteresis: min. 30mV/max. 90mV relaxed upper limit of Detection Threshold to 2.92V (before: 2.9V) defined max. rising VDD for power-on</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 16         | _                                                                                                                           | , ,                                                                       |                          |                |  |

| <ul> <li>Chapter 4.2 Input/output leakage current set to 10μA (before: 1μA)</li> <li>Table 19 U-transceiver characteristics: enhanced S/N+D for 80913 and threshold level for 80912 and 80913 distinguished</li> <li>Chapter 4.6.3 Parameters of the UVD/POR Circuit: defined reduced range of hysteresis: min. 30mV/max. 90mV relaxed upper limit of Detection Threshold to 2.92V (before: 2.9V) defined max. rising VDD for power-on</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Chapter 4.1       | Absolute Max                                                                                                                | Absolute Maximum Ratings: Maximum Voltage on VDD: 4.2V (before: 4.6V)     |                          |                |  |

| Table 19 U-transceiver characteristics: enhanced S/N+D for 80913 and threshold level for 80912 and 80913 distinguished  Chapter 4.6.3 Parameters of the UVD/POR Circuit: defined reduced range of hysteresis: min. 30mV/max. 90mV relaxed upper limit of Detection Threshold to 2.92V (before: 2.9V) defined max. rising VDD for power-on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Chapter 4.1       | Refined refere                                                                                                              | nces for ESD requireme                                                    | ents:'(CDM), EIA/JESD2   | 2-A114B (HBM)' |  |

| Chapter 4.6.3  Parameters of the UVD/POR Circuit: defined reduced range of hysteresis: min. 30mV/max. 90mV relaxed upper limit of Detection Threshold to 2.92V (before: 2.9V) defined max. rising VDD for power-on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Chapter 4.2       | Input/output le                                                                                                             | Input/output leakage current set to 10μA (before: 1μA)                    |                          |                |  |

| defined reduced range of hysteresis: min. 30mV/max. 90mV relaxed upper limit of Detection Threshold to 2.92V (before: 2.9V) defined max. rising VDD for power-on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Table 19          |                                                                                                                             |                                                                           |                          |                |  |

| Chapter 6.3 External circuitry for T-SMINT updated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •                 | defined reduced range of hysteresis: min. 30mV/max. 90mV relaxed upper limit of Detection Threshold to 2.92V (before: 2.9V) |                                                                           |                          |                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Chapter 6.3       | External circu                                                                                                              | External circuitry for T-SMINT updated                                    |                          |                |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

| Table of                                                                                                                                                                                                                   | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.7.1                                                                                                                                                                | Overview References Features PEF 80912 Features PEF 80913 Not Supported are Pin Configuration Block Diagram Pin Definitions and Functions Specific Pins System Integration                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2 3 4 5 6 7 10                                  |

| 2<br>2.1<br>2.2<br>2.2.1<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.5.1<br>2.3.5.2<br>2.3.5.3<br>2.3.5.4<br>2.3.5.5<br>2.3.5.5<br>2.3.5.5<br>2.3.6<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.5.1 | Functional Description  Reset Generation  IOM®-2 Interface  IOM,-2 Functional Description  U-Transceiver  2B1Q Frame Structure  Cyclic Redundancy Check / FEBE bit  Scrambling/ Descrambling  C/I Codes  State Machine for Line Activation / Deactivation  Notation  Standard NT State Machine (IEC-Q / NTC-Q Compatible)  Inputs to the U-Transceiver:  Outputs of the U-Transceiver:  Description of the NT-States  Metallic Loop Termination  S-Transceiver  Line Coding, Frame Structure  S/Q Channels, Multiframing  Data Transfer between IOM,-2 and S0  Loopback 2  State Machine  State Machine NT Mode | 13 14 15 15 18 19 20 21 22 24 27 30 32 34 34 34 |

| 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6                                                                                                                                                             | Operational Description  Layer 1 Activation/Deactivation  Complete Activation Initiated by Exchange  Complete Activation Initiated by TE  Complete Deactivation  Partial Activation  Activation from Exchange with U Active  Activation from TE with U Active                                                                                                                                                                                                                                                                                                                                                   | 41<br>41<br>42<br>43<br>44                      |

| Table of                                                                                                 | Contents                                                                                                                                                                                                                                                | Page                                         |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 3.1.7<br>3.1.8<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5 | Partial Deactivation with U Active Loop 2  Layer 1 Loopbacks Loopback No.2 Complete Loopback Loopback No.2 - Single Channel Loopbacks  External Circuitry Power Supply Blocking Recommendation U-Transceiver S-Transceiver Oscillator Circuitry General | 48<br>49<br>50<br>50<br>51<br>51<br>53       |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.6.1<br>4.6.2<br>4.6.3                                        | Electrical Characteristics Absolute Maximum Ratings DC Characteristics Capacitances Power Consumption Supply Voltages AC Characteristics IOM-2 Interface Reset Undervoltage Detection Characteristics                                                   | 57<br>58<br>60<br>60<br>61<br>62<br>63<br>63 |

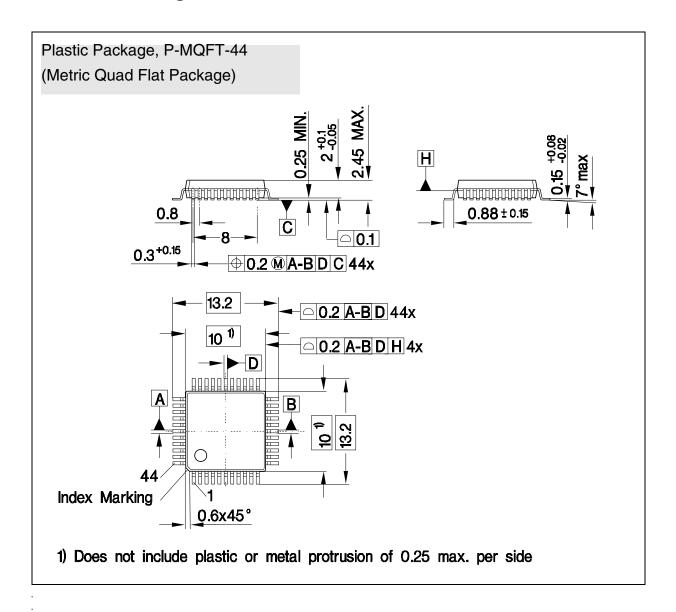

| 5                                                                                                        | Package Outlines                                                                                                                                                                                                                                        | 68                                           |

| 6<br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.3                                                        | Appendix: Differences between Q- and T-SMINT,O  Pinning  U-Transceiver  U-Interface Conformity  U-Transceiver State Machines  Command/Indication Codes  External Circuitry                                                                              | 69<br>70<br>70<br>71<br>73                   |

| 7                                                                                                        | Index                                                                                                                                                                                                                                                   | 76                                           |

| List of Fig | gures F                                                          | Page |

|-------------|------------------------------------------------------------------|------|

| Figure 1    | Pin Configuration                                                | 5    |

| Figure 2    | Block Diagram                                                    | 6    |

| Figure 3    | Application Example Q-SMINT,O: Standard NT1                      | . 12 |

| Figure 4    | IOM®-2 Frame Structure of the Q-SMINT,O                          | . 14 |

| Figure 5    | U-Superframe Structure                                           | . 15 |

| Figure 6    | U-Basic Frame Structure                                          |      |

| Figure 7    | U2B1Q Framer - Data Flow Scheme                                  | . 17 |

| Figure 8    | U2B1Q Deframer - Data Flow Scheme                                | . 18 |

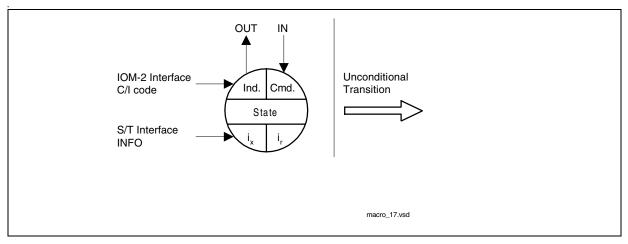

| Figure 9    | Explanation of State Diagram Notation                            | . 20 |

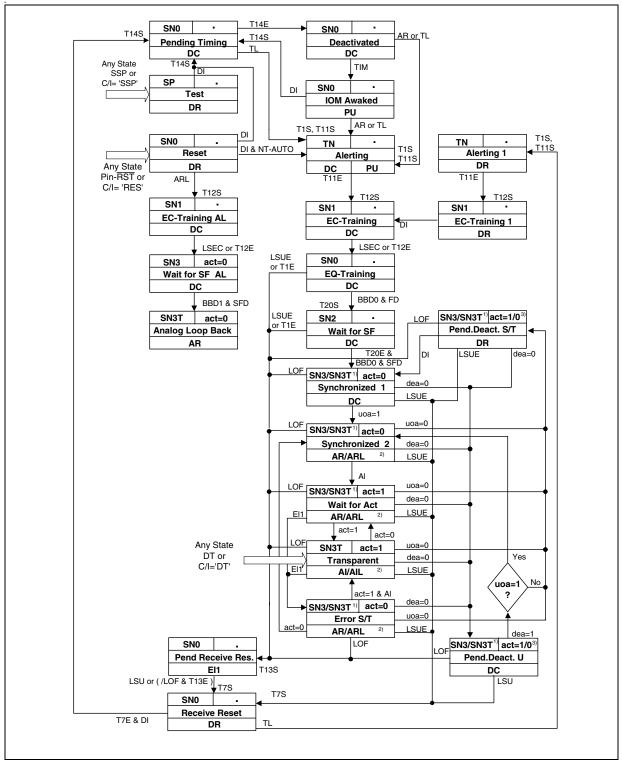

| Figure 10   | Standard NT State Machine (IEC-Q / NTC-Q Compatible) (Footnotes: | see  |

|             | "Dependence of Outputs" on Page 26)                              | 21   |

| Figure 11   | Pulse Streams Selecting Quiet Mode                               | . 31 |

| Figure 12   | S/T -Interface Line Code                                         | . 32 |

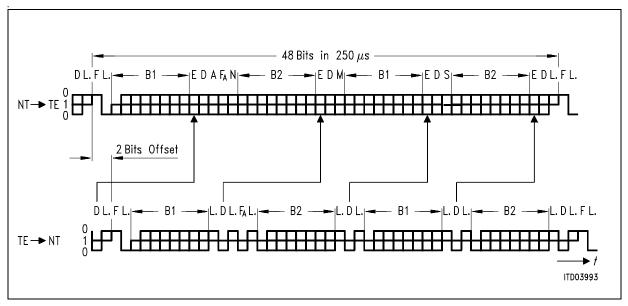

| Figure 13   | Frame Structure at Reference Points S and T (ITU I.430)          | . 33 |

| Figure 14   | State Diagram Notation                                           |      |

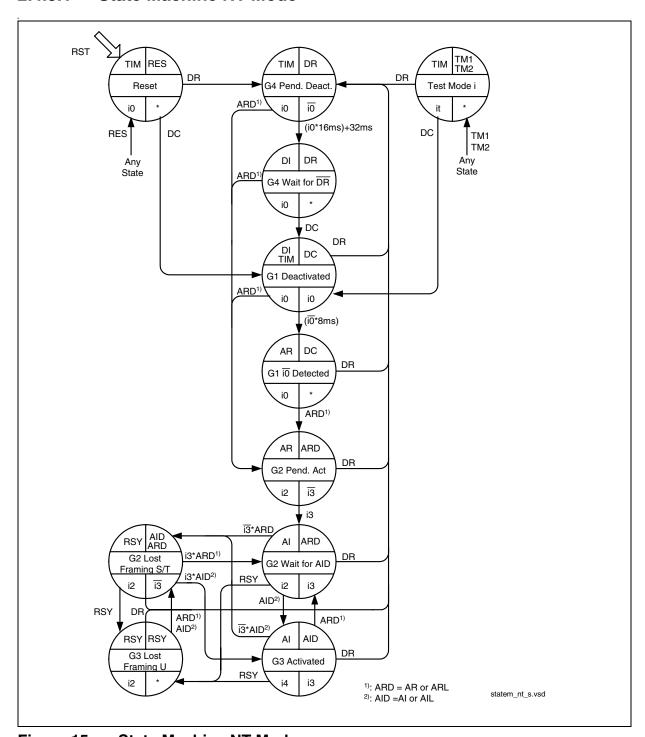

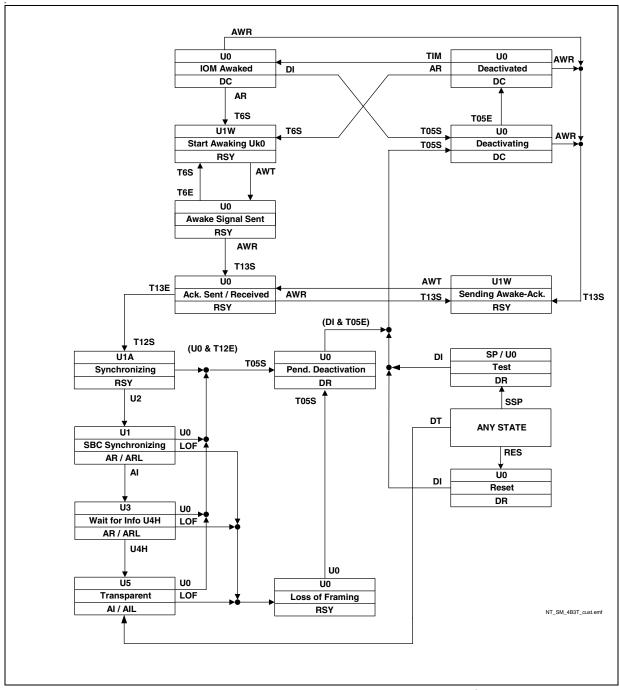

| Figure 15   | State Machine NT Mode                                            | . 37 |

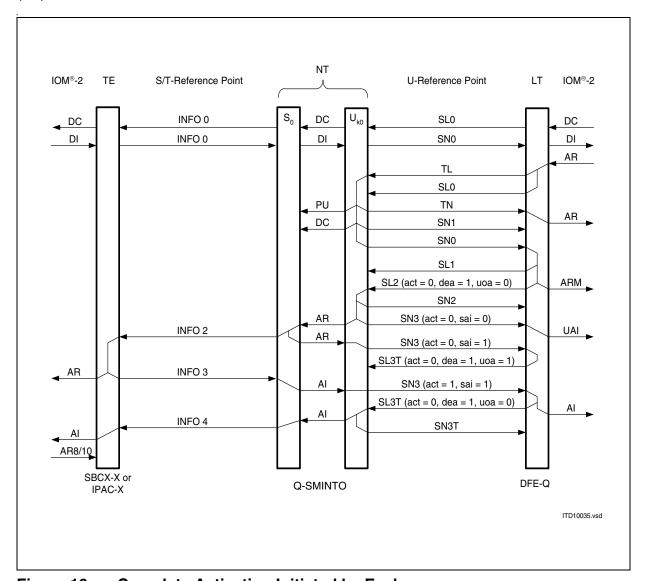

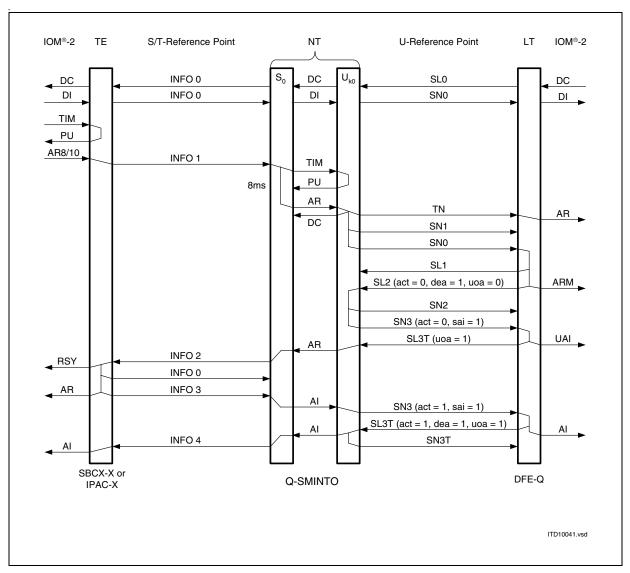

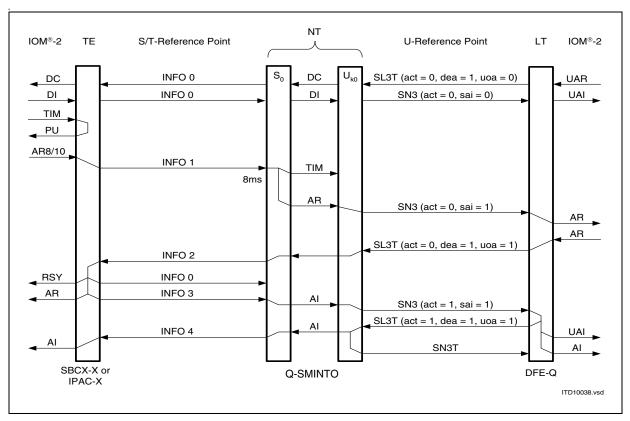

| Figure 16   | Complete Activation Initiated by Exchange                        |      |

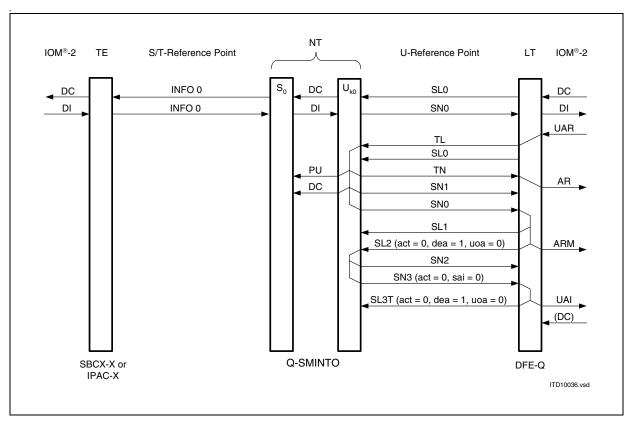

| Figure 17   | Complete Activation Initiated by TE                              | . 42 |

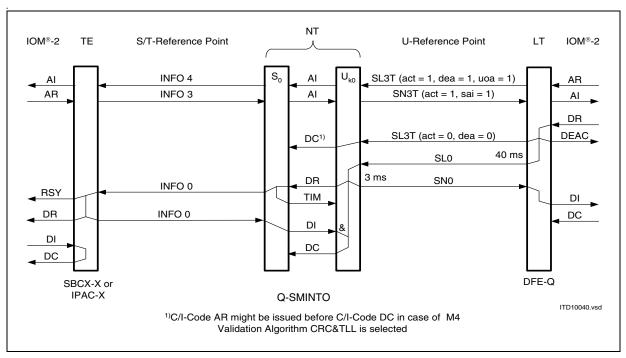

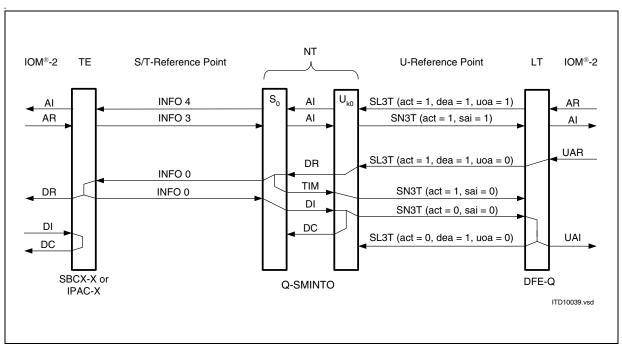

| Figure 18   | Complete Deactivation Initiated by Exchange                      | . 43 |

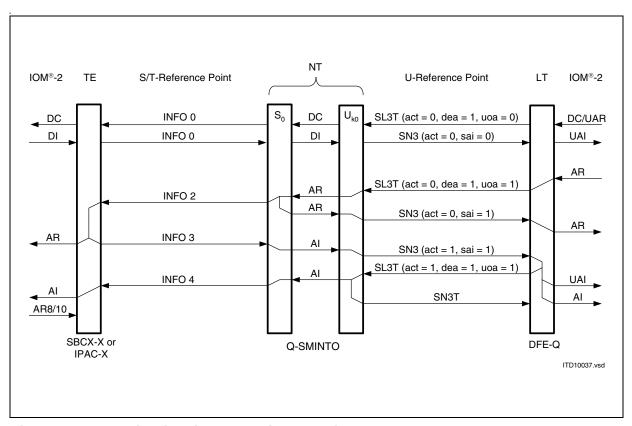

| Figure 19   | Partial Activation                                               | . 44 |

| Figure 20   | Activation from LT with U Active                                 | . 45 |

| Figure 21   | Activation from TE with U Active                                 | . 46 |

| Figure 22   | Partial Deactivation with U Active                               | . 47 |

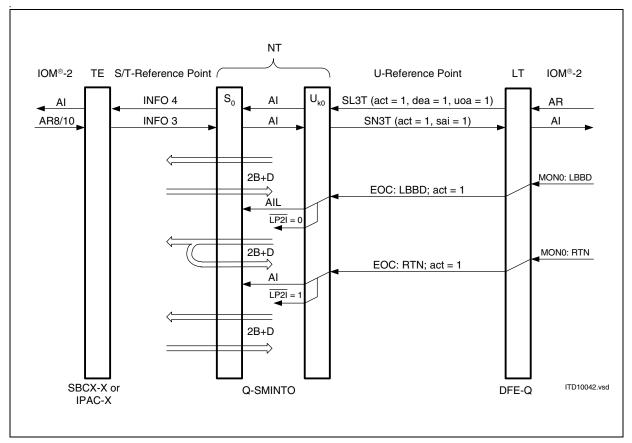

| Figure 23   | Loop 2                                                           | . 48 |

| Figure 24   | Test Loopbacks                                                   | . 49 |

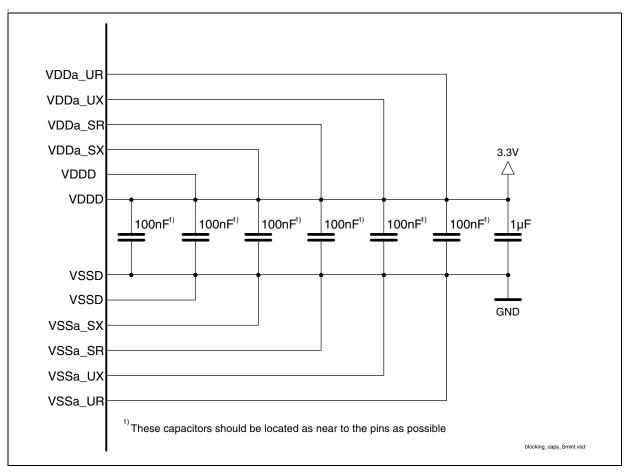

| Figure 25   | Power Supply Blocking                                            | . 51 |

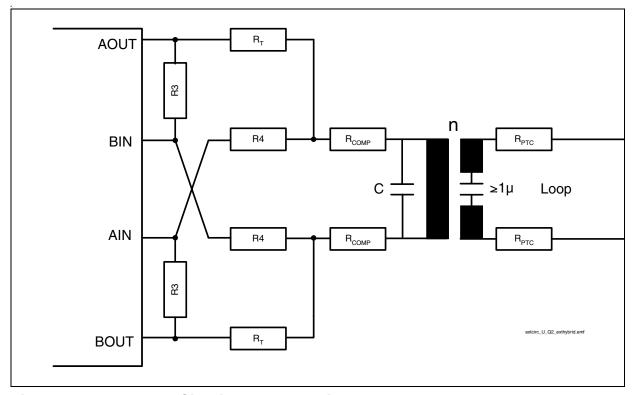

| Figure 26   | External Circuitry U-Transceiver                                 | . 52 |

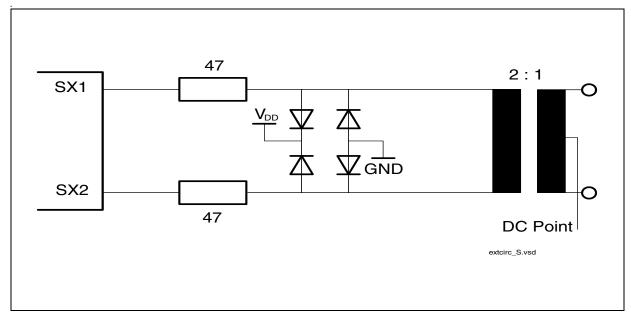

| Figure 27   | External Circuitry S-Interface Transmitter                       | . 54 |

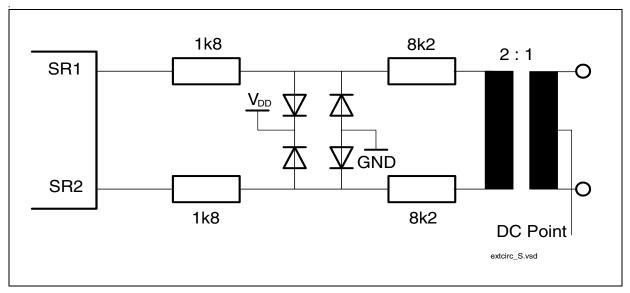

| Figure 28   | External Circuitry S-Interface Receiver                          | . 55 |

| Figure 29   | Crystal Oscillator                                               | . 55 |

| Figure 30   | Maximum Sinusoidal Ripple on Supply Voltage                      | . 61 |

| Figure 31   | Input/Output Waveform for AC Tests                               |      |

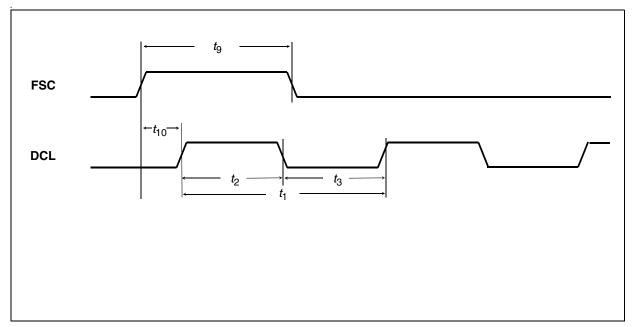

| Figure 32   | IOM®-2 Interface - Bit Synchronization Timing                    | . 63 |

| Figure 33   | IOM-2 Interface - Frame Synchronization Timing                   | . 63 |

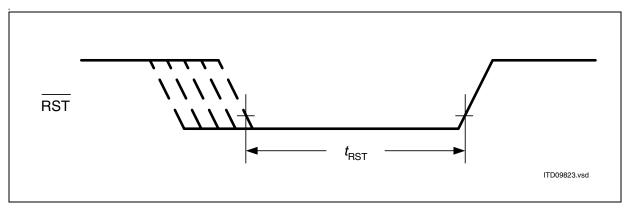

| Figure 34   | Reset Input Signal                                               | . 65 |

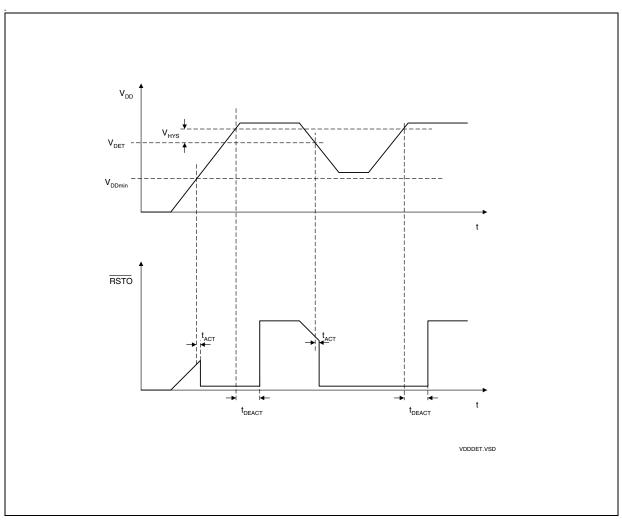

| Figure 35   | Undervoltage Control Timing                                      | . 66 |

| Figure 36   | NTC-Q Compatible State Machine Q-SMINT,O: 2B1Q                   | . 71 |

| Figure 37   | ·                                                                |      |

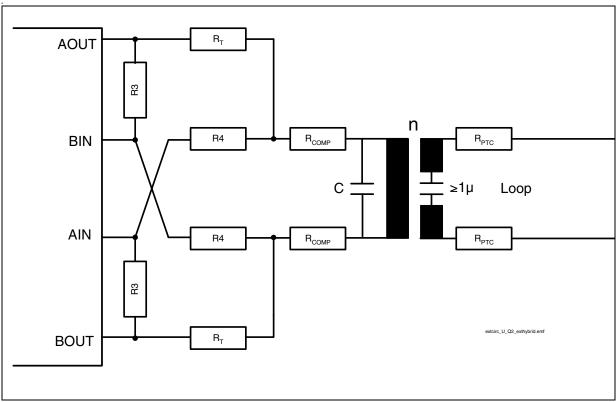

| Figure 38   | External Circuitry Q- and T-SMINT,O                              | . 74 |

| List of Tables | s                                      | Page |

|----------------|----------------------------------------|------|

| Table 1        | NT Products of the 2nd Generation      | 1    |

| Table 2        | Pin Definitions and Functions          | 7    |

| Table 3        | ACT States                             | . 10 |

| Table 4        | LP2I States                            | . 11 |

| Table 5        | Test Modes                             | . 11 |

| Table 6        | U-Superframe Format                    | . 16 |

| Table 7        | U - Transceiver C/I Codes              | . 19 |

| Table 8        | Timers Used                            | . 23 |

| Table 9        | U-Interface Signals                    | . 24 |

| Table 10       | States with Operational Data on IOM,-2 | . 26 |

| Table 11       | Signal Output on Uk0                   | . 26 |

| Table 12       | C/I-Code Output                        | . 27 |

| Table 13       | ANSI Maintenance Controller States     | . 30 |

| Table 14       | U-Transformer Parameters               | . 52 |

| Table 15       | S-Transformer Parameters               | . 54 |

| Table 16       | Crystal Parameters                     |      |

| Table 17       | Maximum Input Currents                 | . 57 |

| Table 18       | S-Transceiver Characteristics          | . 58 |

| Table 19       | U-Transceiver Characteristics          | . 59 |

| Table 20       | Pin Capacitances                       | . 60 |

| Table 21       | Reset Input Signal Characteristics     | . 65 |

| Table 22       | Parameters of the UVD/POR Circuit      | . 67 |

| Table 23       | Pin Definitions and Functions          | . 69 |

| Table 24       | Related Documents to the U-Interface   | . 70 |

| Table 25       | C/I Codes                              | . 73 |

| Table 26       | Dimensions of External Components      | . 75 |

# 1 Overview

The **PEF 80912 / 80913** (Q-SMINT®O) offers all NT1 features known from the PEB / PEF 8091 [11] and can hence replace the latter in all NT1 applications.

Table 1 summarizes the 2nd generation NT products.

Table 1 NT Products of the 2nd Generation

|                                                                                                                                 | PEF80912               | PEF80913 | PEF81912                      | PEF81913                      | PEF82912                                 | PEF82913               |  |

|---------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|-------------------------------|-------------------------------|------------------------------------------|------------------------|--|

|                                                                                                                                 | Q-SMINT <sup>®</sup> O |          | Q-SMI                         | Q-SMINT <sup>®</sup> IX       |                                          | Q-SMINT <sup>®</sup> I |  |

| Package                                                                                                                         | P-MQFP-44              |          |                               | P-MQFP-64<br>P-TQFP-64        |                                          | P-MQFP-64<br>P-TQFP-64 |  |

| Register access                                                                                                                 | no                     |          | U+S+HDLC+ IOM <sup>®</sup> -2 |                               | U+S+ IOM <sup>®</sup> -2                 |                        |  |

| Access via                                                                                                                      | n.a.                   |          |                               | or SCI or<br><sup>®</sup> -2) | parallel (or SCI or IOM <sup>®</sup> -2) |                        |  |

| MCLK,<br>watchdog<br>timer, SDS,<br>BCL, D-<br>channel<br>arbitration,<br>IOM®-2 access<br>and<br>manipulation<br>etc. provided | no                     |          | ує                            | es                            | ує                                       | es                     |  |

| HDLC controller                                                                                                                 | no                     |          | yes                           |                               | no                                       |                        |  |

| NT1 mode<br>available                                                                                                           | yes (only)             |          | n                             | 0                             | n                                        | 0                      |  |

| Extended U-<br>Performance<br>20kft                                                                                             | no                     | yes      | no                            | yes                           | no                                       | yes                    |  |

| 1.1  | References                                                                                                                                                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]  | TS 102 080, Transmission and Multiplexing; ISDN basic rate access; Digital transmission system on metallic local lines, ETSI, November 1998                                         |

| [2]  | T1.601-1998 (Revision of ANSI T1.601-1992), ISDN-Basic Access Interface for Use on Metallic Loops for Application on the Network Side of the NT (Layer 1 Specification), ANSI, 1998 |

| [3]  | ST/LAA/ELR/DNP/822, CNET, France                                                                                                                                                    |

| [4]  | RC7355E, 2B1Q Generic Physical Layer Specification, British Telecommunications plc., 1997                                                                                           |

| [5]  | FZA TS 0095/01:1997-10, Technische Spezifikationen für<br>Netzabschlußgeräte für den ISDN Basisanschluß (NT-BA), Post & Telekom<br>Austria, 1997                                    |

| [6]  | pr ETS 300 012 Draft, ISDN; Basic User Network Interface (UNI), ETSI, November 1996                                                                                                 |

| [7]  | T1.605-1991, ISDN-Basic Access Interface for S and T Reference Points (Layer 1 Specification), ANSI, 1991                                                                           |

| [8]  | I.430, ISDN User-Network Interfaces: Layer 1 Recommendations, ITU, November 1988                                                                                                    |

| [9]  | IEC-Q, ISDN Echocancellation Circuit, PEB 2091 V4.3, User's Manual 02.95, Siemens AG, 1995                                                                                          |

| [10] | SBCX, S/T Bus Interface Circuit Extended, PEB 2081 V3.4, User's Manual 11.96, Siemens AG, 1996                                                                                      |

| [11] | NTC-Q, Network Termination Controller (2B1Q), PEB / PEF 8091 V1.1, Data Sheet 10.97, Siemens AG, 1997                                                                               |

| [12] | INTC-Q, Intelligent Network Termination Controller (2B1Q), PEB / PEF 8191 V1.1, Data Sheet 10.97, Siemens AG, 1997                                                                  |

| [13] | IOM®-2 Interface Reference Guide, Siemens AG, 03.91                                                                                                                                 |

| [14] | SCOUT-S(X), Siemens Codec with S/T-Transceiver, PSB 2138x V1.3, Preliminary Data Sheet 8.99, Infineon Technologies, 1999                                                            |

| [15] | PITA, PCI Interface for Telephony/Data Applications V0.3, SICAN GmbH, September 1997                                                                                                |

| [16] | Dual Channel SLICOFI-2, HV-SLIC; DUSLIC; PEB3265, 4265, 4266; Data Sheet DS2, Infineon Technologies, July 2000.                                                                     |

# 2B1Q Second Gen. Modular ISDN NT (Ordinary) Q-SMINT®O

PEF 80912/80913

#### Version 1.3

#### 1.2 Features PEF 80912

#### Features known from the PEB / PEF 8091

- Single chip solution including U- and S-transceiver

- Perfectly suited for the NT1 in the ISDN

- Fully automatic activation and deactivation

- U-interface (2B1Q) conform to ETSI [1], ANSI [2] and CNET [3]:

- Meets all transmission requirements on all ETSI, ANSI and CNET loops with margin

- Conform to British Telecom's RC7355E [4]

- Compliant with ETSI 10 ms micro interruptions

- MLT input and decode logic (ANSI [2])

- S/T-interface conform to ETSI [6], ANSI [7] and ITU [8]

- Supports point-to-point and bus configurations

- Meets and exceeds all transmission requirements

- Pin programmable CSO-bit

- Optional IOM<sup>®</sup>-2 interface eases chip testing and evaluation

- Activation status LED supported

| Туре            | Package   |

|-----------------|-----------|

| PEF 80912/80913 | P-MQFT-44 |

#### **New Features**

- Reduced number of external components for external U-hybrid required

- Optional use of up to  $2x20\Omega$  resistors on the line side of the transformer (e.g. PTCs)

- Pin Uref and the according external capacitor removed

- Improved ESD (2 kV instead of <850 V)</li>

- Inputs accept 3.3 V and 5 V

- I/O (open drain) accepts pull-up to 3.3 V<sup>1)</sup>

- Pin compatible with T-SMINT®O (2nd Generation)

- LED indicates Loopback 2 (LBBD)

- Power-on reset and Undervoltage Detection with no external components

- · Lowest power consumption due to

- Low power CMOS technology (0.35μ)

- Newly optimized low power libraries

- High output swing on U- and S-line interface leads to minimized power consumption

- Single 3.3 Volt power supply

- 200 mW (NTC-Q: 285 mW) power consumption with random data over ETSI Loop 2.

- 15 mW typical power consumption in power down (NTC-Q: 28 mW)

#### 1.3 Features PEF 80913

The Q-SMINT®O PEF 80913 provides all features of the PEF 80912. Additionally, a significantly enhanced performance of the U-interface as compared to ETSI [1], ANSI [2] and CNET [3] requirements is guaranteed:

Transparent transmission on 20kft AWG26 with a BER < 10<sup>-7</sup> (without noise).

<sup>1)</sup> Pull-ups to 5 V must be avoided. A so-called 'hot-electron-effect' would lead to long term degradation.

# 1.4 Not Supported are ...

- Integrated U-hybrid

- 'NT-Star' with star point on the IOM<sup>®</sup>-2 bus (already not supported in NTC-Q).

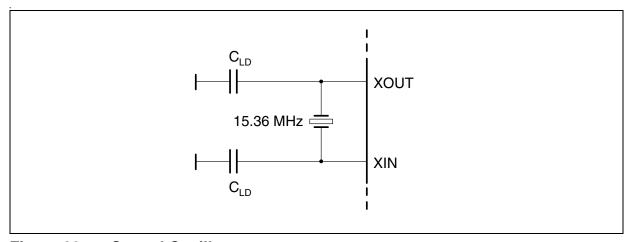

- The oscillator architecture was changed with respect to the NTC-Q to reduce power consumption. As a consequence, the Q-SMINT®O always needs a crystal and pin XIN can not be connected to an external clock as it was possible for IEC-Q and NTC-Q. This does not limit the use of the Q-SMINT®O in NTs since all NT designs use crystals anyway.

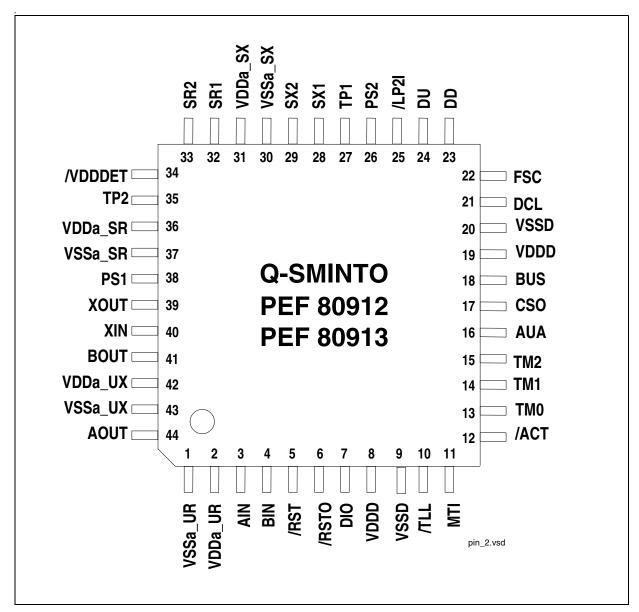

# 1.5 Pin Configuration

Figure 1 Pin Configuration

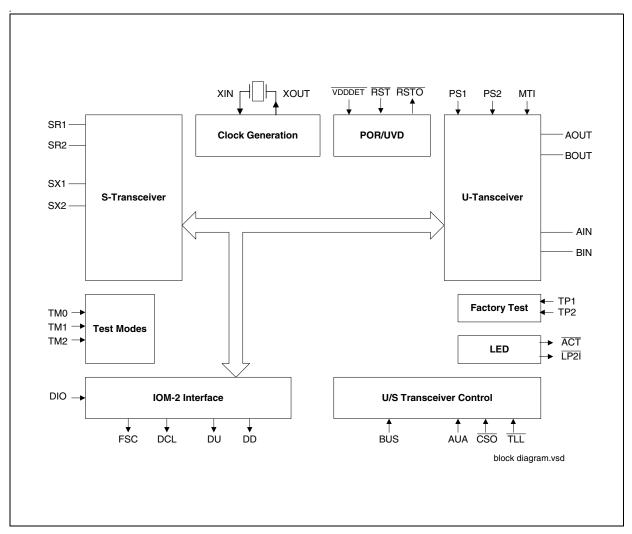

# 1.6 Block Diagram

Figure 2 Block Diagram

# 1.7 Pin Definitions and Functions

# **Table 2** Pin Definitions and Functions

| Symbol  | Type                                                                                                               | Function                                                                                                              |  |

|---------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| VDDa_UR | -                                                                                                                  | Supply voltage for U-Receiver (3.3 V $\pm$ 5 %)                                                                       |  |

| VSSa_UR | _                                                                                                                  | Analog ground (0 V) U-Receiver                                                                                        |  |

| VDDa_UX | -                                                                                                                  | Supply voltage for U-Transmitter (3.3 V $\pm$ 5 %)                                                                    |  |

| VSSa_UX | _                                                                                                                  | Analog ground (0 V) U-Transmitter                                                                                     |  |

| VDDa_SR | -                                                                                                                  | Supply voltage for S-Receiver (3.3 V $\pm$ 5 %)                                                                       |  |

| VSSa_SR | _                                                                                                                  | Analog ground (0 V) S-Receiver                                                                                        |  |

| VDDa_SX | -                                                                                                                  | Supply voltage for S-Transmitter (3.3 V $\pm$ 5 %)                                                                    |  |

| VSSa_SX | _                                                                                                                  | Analog ground (0 V) S-Transmitter                                                                                     |  |

| VDDD    | -                                                                                                                  | Supply voltage digital circuits (3.3 V $\pm$ 5 %)                                                                     |  |

| VSSD    | _                                                                                                                  | Ground (0 V) digital circuits                                                                                         |  |

| VDDD    | -                                                                                                                  | Supply voltage digital circuits (3.3 V $\pm$ 5 %)                                                                     |  |

| VSSD    | -                                                                                                                  | Ground (0 V) digital circuits                                                                                         |  |

|         |                                                                                                                    |                                                                                                                       |  |

| FSC     | 0                                                                                                                  | Frame Sync:<br>8-kHz frame synchronization signal                                                                     |  |

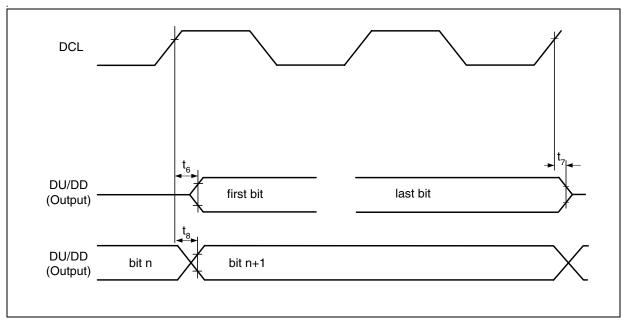

| DCL     | 0                                                                                                                  | Data Clock: IOM®-2 interface clock signal (double clock): 512 kHz                                                     |  |

| LP2I    | 0                                                                                                                  | Loopback 2 indication: Can directly drive a LED (4 mA). 0: LBBD received, Loopback 2 closed 1: Loopback 2 not closed. |  |

| DD      | 0                                                                                                                  | Data Downstream: Data on the IOM®-2 interface                                                                         |  |

| DU      | 0                                                                                                                  | <b>Data Upstream:</b> Data on the IOM®-2 interface                                                                    |  |

|         | VDDa_UR  VSSa_UR  VDDa_UX  VSSa_UX  VDDa_SR  VSSa_SR  VDDa_SX  VSSa_SX  VDDD  VSSD  VDDD  VSSD  TSC  DCL  LP2I  DD | VDDa_UR                                                                                                               |  |

**Table 2 Pin Definitions and Functions** (cont'd)

| Table 2 | Pili Definitions and Functions (Cont a) |      |                                                                                                                                                                                                                                                 |  |  |  |  |

|---------|-----------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin     | Symbol                                  | Type | Function                                                                                                                                                                                                                                        |  |  |  |  |

|         | •                                       |      |                                                                                                                                                                                                                                                 |  |  |  |  |

| 7       | DIO                                     | I    | Disable IOM®-2:  1: FSC, DCL, DU and DD high Z  0: FSC, DCL, DU and DD push-pull                                                                                                                                                                |  |  |  |  |

| 16      | AUA                                     | I    | Auto U Activation: 1: U-transceiver attempts one automatic activation after reset. Tie to '0' in applications that do not require auto-start after reset.                                                                                       |  |  |  |  |

| 17      | CSO                                     | I    | Cold Start Only:  '1' selects CSO-bit to '0'. (normal)  '0' selects CSO-bit to '1'. (special cases)  The pin only controls the CSO-bit in the U- frame. The U-transceiver itself is always a warm-start transceiver according to ANSI and ETSI. |  |  |  |  |

| 18      | BUS                                     | (PU) | Bus mode on S-interface: 1: passive S-bus (fixed timing) 0: point-to-point / extended passive S-bus (adaptive timing)                                                                                                                           |  |  |  |  |

| 5       | RST                                     | I    | Reset: Low active reset input. Schmitt-Trigger input with hysteresis of typical 360 mV. Tie to '1' if not used.                                                                                                                                 |  |  |  |  |

| 6       | RSTO                                    | OD   | Reset Output: Low active reset output.                                                                                                                                                                                                          |  |  |  |  |

| 10      | TLL                                     | I    | Triple-Last-Look Select validation algorithm for received M4 bit towards state machine: '0': CRC & TLL '1': CRC                                                                                                                                 |  |  |  |  |

| 13      | TMO                                     | I    | Test Mode 0 Selects test pattern (see Page 11).                                                                                                                                                                                                 |  |  |  |  |

| 14      | TM1                                     | I    | Test Mode 1 Selects test pattern (see Page 11).                                                                                                                                                                                                 |  |  |  |  |

| 15      | TM2                                     | I    | Test Mode 2 Selects test pattern (see Page 11).                                                                                                                                                                                                 |  |  |  |  |

**Table 2 Pin Definitions and Functions** (cont'd)

| Pin | Symbol | Туре | Function                                                                                                                                                                                                           |

|-----|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |        |      |                                                                                                                                                                                                                    |

| 28  | SX1    | 0    | S-Bus Transmitter Output (positive)                                                                                                                                                                                |

| 29  | SX2    | 0    | S-Bus Transmitter Output (negative)                                                                                                                                                                                |

| 32  | SR1    | I    | S-Bus Receiver Input                                                                                                                                                                                               |

| 33  | SR2    | I    | S-Bus Receiver Input                                                                                                                                                                                               |

|     |        |      |                                                                                                                                                                                                                    |

| 40  | XIN    | I    | Crystal 1:<br>Connected to a 15.36 MHz crystal                                                                                                                                                                     |

| 39  | XOUT   | 0    | Crystal 2:<br>Connected to a 15.36 MHz crystal                                                                                                                                                                     |

|     | ,      | •    |                                                                                                                                                                                                                    |

| 44  | AOUT   | 0    | Differential U-interface Output                                                                                                                                                                                    |

| 41  | BOUT   | 0    | Differential U-interface Output                                                                                                                                                                                    |

| 3   | AIN    | I    | Differential U-interface Input                                                                                                                                                                                     |

| 4   | BIN    | I    | Differential U-interface Input                                                                                                                                                                                     |

|     |        |      |                                                                                                                                                                                                                    |

| 34  | VDDDET | I    | VDD Detection: This pin selects if the V <sub>DD</sub> detection is active ('0') and reset pulses are generated on pin RSTO or whether it is deactivated ('1') and an external reset has to be applied on pin RST. |

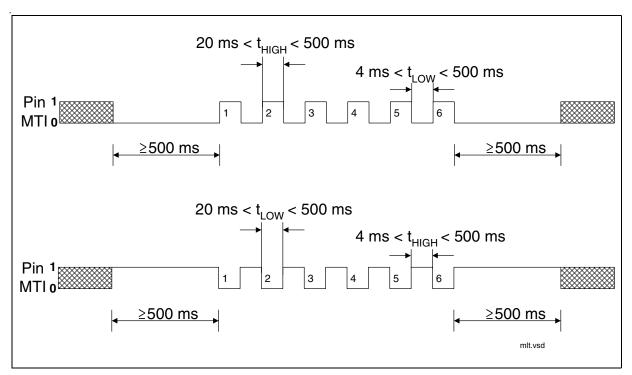

| 11  | MTI    | I    | Metallic Termination Input. Input to evaluate Metallic Termination pulses. Tie to '1' if not used.                                                                                                                 |

| 38  | PS1    | 1    | Power Status (primary). The pin status is passed to the overhead bit 'PS1' in the U frame to indicate the status of the primary power supply ('1' = ok).                                                           |

| 26  | PS2    | I    | Power Status (secondary).  The pin status is passed to the overhead bit 'PS2' in the U frame to indicate the status of the secondary power supply ('1' = ok).                                                      |

**Table 2 Pin Definitions and Functions** (cont'd)

| Pin | Symbol | Туре | Function                                                                                                  |

|-----|--------|------|-----------------------------------------------------------------------------------------------------------|

| 12  | ACT    | 0    | Activation LED. Indicates the activation status of U- and S-transceiver. Can directly drive a LED (4 mA). |

| 27  | TP1    | I    | Test Pin 1. Used for factory device test. Tie to V <sub>SS</sub>                                          |

| 35  | TP2    | I    | Test Pin 2. Used for factory device test. Tie to V <sub>SS</sub>                                          |

PU: Internal pull-up resistor (typ. 100 μA)

I: Input

O: Output (Push-Pull)

OD: Output (Open Drain)

# 1.7.1 Specific Pins

#### LED Pins ACT, LP2I

A LED can be connected to pin  $\overline{ACT}$  to display four different states (off, slow flashing, fast flashing, on). It displays the activation status of the U- and S-transceiver according to Table 3.

with:

Table 3 ACT States

| Pin ACT  | LED | U_Deactivated | U_Activated | S_Activated |

|----------|-----|---------------|-------------|-------------|

| $V_{DD}$ | off | 1             | x           | x           |

| 8Hz      | 8Hz | 0             | 0           | x           |

| 1Hz      | 1Hz | 0             | 1           | 0           |

| GND      | on  | 0             | 1           | 1           |

**U\_Deactivated**: 'Deactivated State' as defined in **Chapter 2.3.5.5**.

**U\_Activated**: 'Synchronized 1', 'Synchronized 2', 'Wait for ACT', 'Transparent', 'Error S/T', 'Pend. Deact. S/T', 'Pend. Deact. U' as defined in **Chapter 2.3.5.5**.

**S-Activated**: 'Activated State' as defined in **Chapter 2.4.5**.

Note: Optionally, pin ACT can drive a second LED with inverse polarity (connect this additional LED to 3.3 V only).

Another LED can be connected to pin **LP2I** to indicate an active Loopback 2 according to **Table 4**.

Table 4 LP2I States

| Pin LP2I | LED | EOC-Command LBBD                                                                                  |

|----------|-----|---------------------------------------------------------------------------------------------------|

| $V_{DD}$ | off | received no EOC-LBBD or received RTN after an LBBD command.                                       |

| GND      | on  | EOC-command LBBD (50) has been received. Complete analog loop is being closed on the S-interface. |

#### **Test Modes**

Different test patterns on the U- and S-interface can be generated via pins TM0-2 according to Table 5.

Table 5 Test Modes

| ТМО | TM1 | TM2 | U-transceiver                    | S-transceiver                          |

|-----|-----|-----|----------------------------------|----------------------------------------|

| 0   | 0   | 0   | Reserved for future use. N       | Normal operation in this               |

| 0   | 0   | 1   | version.                         |                                        |

| 0   | 1   | 0   | Normal operation                 | 96 kHz <sup>1)</sup> Continuous Pulses |

| 0   | 1   | 1   |                                  | 2 kHz <sup>2)</sup> Single Pulses      |

| 1   | 0   | 0   | Data Through <sup>3)</sup>       | Normal operation                       |

| 1   | 0   | 1   | Send Single Pulses <sup>4)</sup> |                                        |

| 1   | 1   | 0   | Quiet Mode <sup>5)</sup>         |                                        |

| 1   | 1   | 1   | normal operation                 |                                        |

<sup>1)</sup> The S-transceiver transmits pulses with alternating polarity at a rate of 192 kHz resulting in a 96 kHz envelope.

<sup>2)</sup> The S-transceiver transmits pulses with alternating polarity at a rate of 4 kHz resulting in a 2 kHz envelope.

<sup>3)</sup> Forces the U-transceiver into the state 'Transparent' where it transmits signal SN3T.

<sup>&</sup>lt;sup>4)</sup> Forces the U-transceiver to go into state 'Test' and to send single pulses. The pulses are issued at 1.5 ms intervals and have a duration of 12.5 μs.

<sup>5)</sup> The U-transceiver is hardware reset.

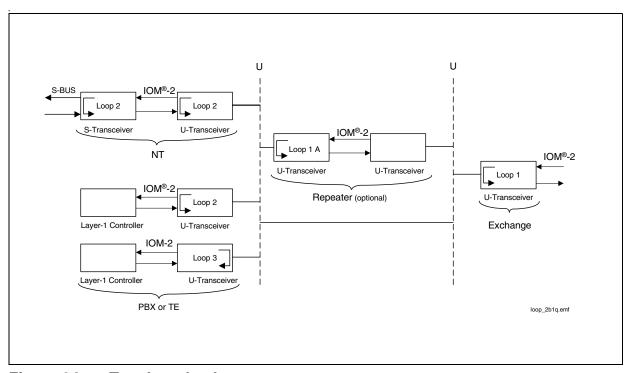

# 1.8 System Integration

The Q-SMINT®O provides NT1 functionality without a microcontroller being necessary. Special selections can be done via pin strapping (CSO,  $\overline{TLL}$ , BUS, etc.). The device has no  $\mu P$  interface.

The  $IOM^{\$}$ -2 Interface serves only for monitoring and debugging purposes. It can be regarded as a window to the internal  $IOM^{\$}$ -2.

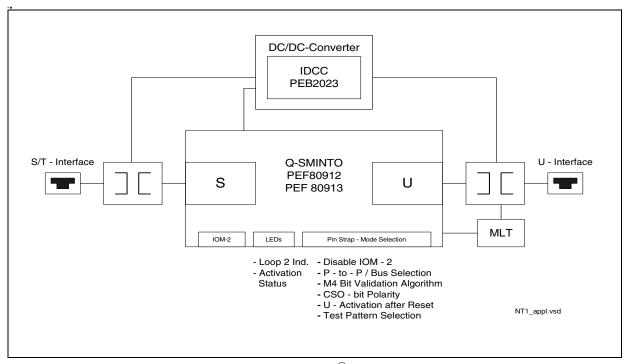

Figure 3 Application Example Q-SMINT®O: Standard NT1

# **2** Functional Description

#### 2.1 Reset Generation

#### **External Reset Input**

At the  $\overline{RST}$  input an external reset can be applied forcing the Q-SMINT®O in the reset state. This external reset signal is additionally fed to the  $\overline{RSTO}$  output.

#### **Reset Ouput**

If  $\overline{\text{VDDDET}}$  is active, then the deactivation of a reset output on  $\overline{\text{RSTO}}$  is delayed by  $t_{\text{DEACT}}$  (see **Table 22**).

#### **Reset Generation**

The Q-SMINT®O has an on-chip reset generator based on a Power-On Reset (POR) and Under Voltage Detection (UVD) circuit (see **Table 22**). The POR/UVD requires no external components.

The POR/UVD circuit can be disabled via pin VDDDET.

The requirements on V<sub>DD</sub> ramp-up during power-on reset are described in Chapter 4.6.3.

#### **Clocks and Data Lines During Reset**

During reset the data clock (DCL) and the frame synchronization (FSC) keep running. During reset DD and DU are high; with the exception of:

- The output C/I code from the U-Transceiver on DD is 'DR' = 0000

- The output C/I code from the S-Transceiver on DU is 'TIM' = 0000.

# 2.2 IOM®-2 Interface

The IOM®-2 interface always operates in NT mode according to the IOM®-2 Reference Guide [13].

# 2.2.1 IOM®-2 Functional Description

The IOM®-2 interface consists of four lines: FSC, DCL, DD, DU. The rising edge of FSC indicates the start of an IOM®-2 frame. The DCL clock signal synchronizes the data transfer on both data lines DU and DD. The DCL is twice the bit rate. The bits are shifted out with the rising edge of the first DCL clock cycle.

Note: It is not possible to write any data via IOM<sup>®</sup>-2 into the Q-SMINT<sup>®</sup>O.

The IOM®-2 interface can be enabled/disabled with pin DIO.

The FSC signal is an 8 kHz frame sync signal. The number of PCM timeslots on the transmit line is determined by the frequency of the DCL clock, with the 512 kHz clock 1 channel consisting of 4 timeslots is available.

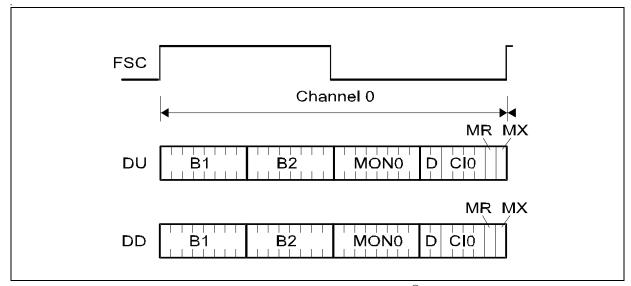

# IOM®-2 Frame Structure of the Q-SMINT®O

The frame structure on the IOM<sup>®</sup>-2 data ports (DU,DD) of the Q-SMINT<sup>®</sup>O with a DCL clock of 512 kHz is shown in **Figure 4.**

Figure 4 IOM®-2 Frame Structure of the Q-SMINT®O

The frame is composed of one channel:

Channel 0 contains 144-kbit/s of user and signaling data (2B + D), a MONITOR programming channel (not available in Q-SMINT $^{\otimes}$ O) and a command/indication channel (CI0) for control of e.g. the U-transceiver.

#### 2.3 U-Transceiver

The state machine of the U-Transceiver is based on the NT state machine in the PEB / PEF 8091 documentation [11].

Basic configurations are selected via pin strapping.

#### 2.3.1 2B1Q Frame Structure

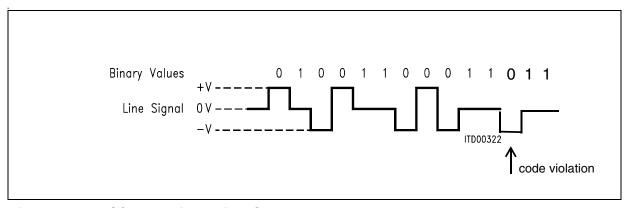

Transmission on the  $U_{2B1Q}$ -interface is performed at a rate of 80 kbaud. The code used is reducing two bits to one quaternary symbol (2B1Q).

Data is grouped together into U-superframes of 12 ms each. Each superframe consists of eight basic frames which begin with a synchronization word and contain 222 bits of information. The first basic frame of a superframe starts with an inverted synchword (ISW) compared to the other basic frames (SW). The structure of one U-superframe is illustrated in **Figure 5** and **Figure 6**.

| ISW     | 1. Basic Frame | SW | 2. Basic Frame | <br>SW | 8. Basic Frame |

|---------|----------------|----|----------------|--------|----------------|

| <12 ms> |                |    |                |        |                |

#### Figure 5 U-Superframe Structure

| (I) SW                | 12 × 2B + D         | M1 – M6                 |  |  |  |

|-----------------------|---------------------|-------------------------|--|--|--|

| (Inverted) Synch Word | User Data           | <u>Maintenance</u> Data |  |  |  |

| 18 Bit (9 Quat)       | 216 Bits (108 Quat) | 6 Bits (3 Quat)         |  |  |  |

| <1,5 ms>              |                     |                         |  |  |  |

#### Figure 6 U-Basic Frame Structure

Out of the 222 information bits 216 contain 2B + D data from 12  $IOM^{\textcircled{\tiny 8}}$ -frames, the remaining 6 bits are used to transmit maintenance information. Thus 48 maintenance bits are available per U-superframe. They are used to transmit two EOC-messages (24 bit), 12 Maintenance (overhead) bits and one checksum (12 bit).

Table 6 U-Superframe Format

|                  |                       | Fram-<br>ing | ,           |           |           |           |              |           |           |

|------------------|-----------------------|--------------|-------------|-----------|-----------|-----------|--------------|-----------|-----------|

|                  | Quat<br>Position<br>s | 1 – 9        | 10 –<br>117 | 118 s     | 118 m     | 119 s     | 119 m        | 120 s     | 120 m     |

|                  | Bit<br>Position<br>s  | 1 – 18       | 19 –<br>234 | 235       | 236       | 237       | 238          | 239       | 240       |

| Super<br>Frame # | Basic<br>Frame #      | Sync<br>Word | 2B +<br>D   | M1        | M2        | МЗ        | M4           | M5        | M6        |

| 1                | 1                     | ISW          | 2B +<br>D   | EOC<br>a1 | EOC<br>a2 | EOC<br>a3 | ACT/<br>ACT  | 1         | 1         |

|                  | 2                     | SW           | 2B +<br>D   | EOC<br>dm | EOC<br>i1 | EOC<br>i2 | DEA /<br>PS1 | 1         | FEBE      |

|                  | 3                     | SW           | 2B +<br>D   | EOC<br>i3 | EOC<br>i4 | EOC<br>i5 | SCO/<br>PS2  | CRC1      | CRC2      |

|                  | 4                     | SW           | 2B +<br>D   | EOC<br>i6 | EOC<br>i7 | EOC<br>i8 | 1/ NTM       | CRC3      | CRC4      |

|                  | 5                     | SW           | 2B +<br>D   | EOC<br>a1 | EOC<br>a2 | EOC<br>a3 | 1/ CSO       | CRC5      | CRC6      |

|                  | 6                     | SW           | 2B +<br>D   | EOC<br>dm | EOC<br>i1 | EOC<br>i2 | 1            | CRC7      | CRC8      |

|                  | 7                     | SW           | 2B +<br>D   | EOC<br>i3 | EOC<br>i4 | EOC<br>i5 | UOA /<br>SAI | CRC9      | CRC<br>10 |

|                  | 8                     | SW           | 2B +<br>D   | EOC<br>i6 | EOC<br>i7 | EOC<br>i8 | AIB /<br>NIB | CRC<br>11 | CRC<br>12 |

| 2,3              |                       |              |             |           |           |           |              |           |           |

|                  |                       |              |             | LT- to N  | NT dir. > | /         | < NT- to     | LT dir.   |           |

- ISW Inverted Synchronization Word (quad): -3-3+3+3+3-3-3-3- SW Synchronization Word (quad): +3+3-3-3-3+3+3+3

- CRC Cyclic Redundancy Check

EOC Embedded Operation Channel a = address bit

d/m = data / message bit

i = information (data / message)

ACT Activation bit

ACT = (1) -> Layer 2 ready for communication

```

DEA Deactivation bit

DEA = (0) -> LT informs NT that it will turn off

CSO = (1) -> NT-activation with cold start only

CSO Cold Start Only

UOA U-Only Activation

UOA = (0) -> U-only activated

SAI

S-Activity Indicator

SAI = (0) \rightarrow S-interface is deactivated

FEBE Far-end Block Error

FEBE = (0) -> Far-end block error occurred

PS1 Power Status Primary Source

PS1 = (1) \rightarrow Primary power supply ok

- PS2 Power Status Secondary Source PS2 = (1) -> Secondary power supply ok

NTM NT-Test Mode

NTM = (0) \rightarrow NT busy in test mode

AIB

Alarm Indication Bit

AIB = (0) -> Interruption (according to ANSI)

NIB

Network Indication Bit

NIB = (1) -> no function (reserved for network use)

SCO Start on Command only bit

- 1

(currently not defined by ANSI/ETSI)

```

can be accessed by the system interface for proprietary use

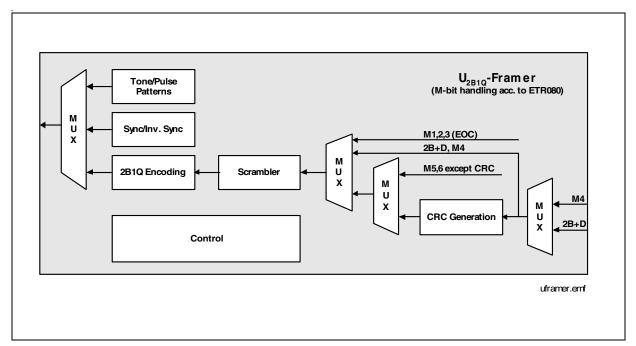

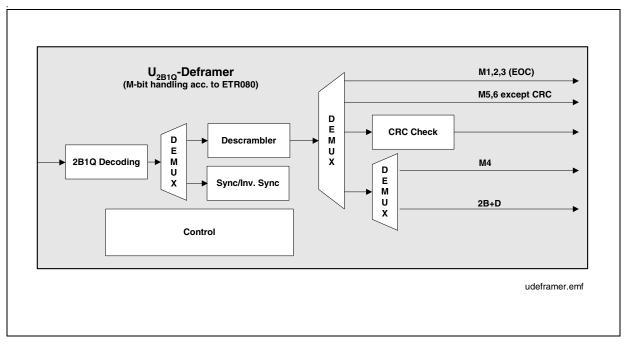

The principle signal flow is depicted in **Figure 7** and **Figure 8**. The data is first grouped in bits that are covered by the CRC and bits that are not. After the CRC generation the bits are arranged in the proper sequence according to the 2B1Q frame format, encoded and finally transmitted.

In receive direction the data is first decoded, descrambled, deframed and handed over for further processing.

Figure 7 U<sub>2B1Q</sub> Framer - Data Flow Scheme

Figure 8 U<sub>2B1O</sub> Deframer - Data Flow Scheme

# 2.3.2 Cyclic Redundancy Check / FEBE bit

An error monitoring function is implemented covering the 2B + D and M4 data transmission of a U-superframe by a Cyclic Redundancy Check (CRC).

The computed polynomial is:

G (u) =

$$u^{12} + u^{11} + u^3 + u^2 + u + 1$$

(+ modulo 2 addition)

The check digits (CRC bits CRC1, CRC2, ..., CRC12) generated are transmitted in the U-superframe. The receiver will compute the CRC of the received 2B + D and M4 data and compare it with the received CRC-bits generated by the transmitter.

A CRC-error will be indicated to both sides of the U-interface, as a NEBE (Near-end Block Error) on the side where the error is detected, as a FEBE (Far-end Block Error) on the remote side. The FEBE-bit will be placed in the next available U-superframe transmitted to the originator.

# 2.3.3 Scrambling/ Descrambling

The scrambling algorithm ensures that no sequences of permanent binary 0s or 1s are transmitted. The scrambling / descrambling process is controlled fully by the Q-SMINT®O. Hence, no influence can be taken by the user.

#### 2.3.4 **C/I Codes**

The operational status of the U-transceiver is controlled by the Control/Indicate channel (C/I-channel).

Table 7 presents all defined C/I codes.

An indication is issued permanently by the U-transceiver on DD until a new indication needs to be forwarded. Because a number of states issue identical indications it is not possible to identify every state individually.

Table 7 U - Transceiver C/I Codes

| Code | IN  | OUT |  |

|------|-----|-----|--|

| 0000 | TIM | DR  |  |

| 0001 | RES | -   |  |

| 0010 | -   | -   |  |

| 0011 | -   | -   |  |

| 0100 | EI1 | El1 |  |

| 0101 | SSP | -   |  |

| 0110 | DT  | _   |  |

| 0111 | -   | PU  |  |

| 1000 | AR  | AR  |  |

| 1001 | -   | -   |  |

| 1010 | ARL | ARL |  |

| 1011 | -   | -   |  |

| 1100 | Al  | Al  |  |

| 1101 | -   | _   |  |

| 1110 | -   | AIL |  |

| 1111 | DI  | DC  |  |

AI: Activation Indication

**AIL: Activation Indication Loop**

AR: Activation Request

ARL: Activation Request Local Loop

DC: Deactivation Confirmation

DI: Deactivation Indication

DR: Deactivation Request

DT: Data Through test mode

EI1: Error Indication 1

PU: Power-Up

**RES: Reset**

SSP: Send Single Pulses test mode

TIM: Timing request

#### 2.3.5 State Machine for Line Activation / Deactivation

#### 2.3.5.1 **Notation**

The state machines control the sequence of signals at the U-interface that are generated during the start-up procedure. The informations contained in the following state diagrams are:

- State name

- U-signal transmitted

- Overhead bits transmitted

- C/I-code transmitted

- Transition criteria

- Timers

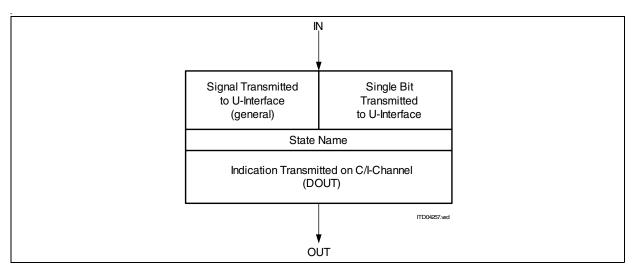

Figure 9 shows how to interpret the state diagrams.

Figure 9 Explanation of State Diagram Notation

Combinations of transition criteria are possible. Logical "AND" is indicated by "&" (TN & DC), logical "OR" is written "or" and for a negation "/" is used. The start of a timer is indicated with "TxS" ("x" being equivalent to the timer number). Timers are always started when entering the new state. The action resulting after a timer has expired is indicated by the path labelled "TxE".

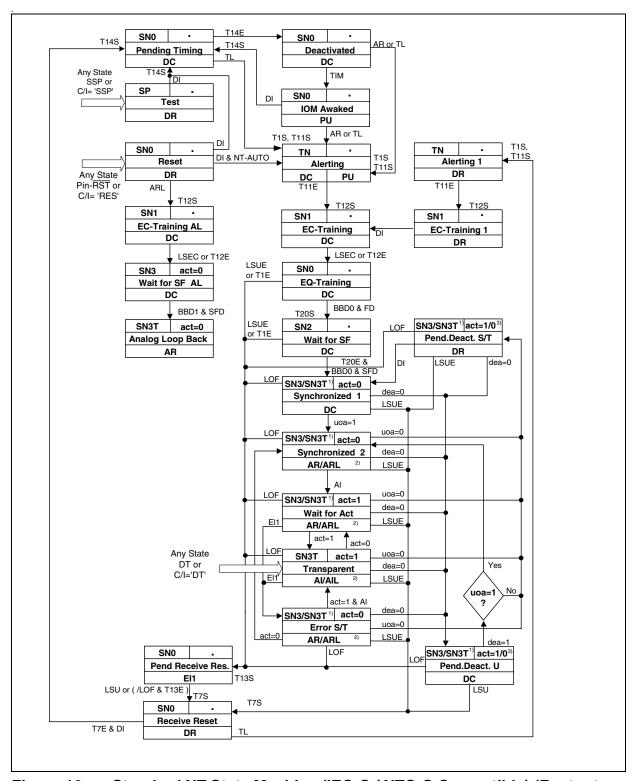

# 2.3.5.2 Standard NT State Machine (IEC-Q / NTC-Q Compatible)

Figure 10 Standard NT State Machine (IEC-Q / NTC-Q Compatible) (Footnotes: see "Dependence of Outputs" on Page 26)

Note: The test modes 'Data Through' (DT), 'Send Single Pulses' (SSP) and 'Quiet Mode' (QM) can be generated via pins TM0-2 according to **Table 5**.

If the Metallic Loop Termination is used, then the U-transceiver is forced into the states 'Reset' and 'Transparent' by valid pulse streams on pin MTI according to **Table 13**.

# 2.3.5.3 Inputs to the U-Transceiver:

#### C/I-Commands:

Al Activation Indication

The downstream device issues this indication to announce that its layer-1 is available. The U-transceiver informs the LT side by setting the "ACT" bit to "1".

AR Activation Request

The U-transceiver is requested to start the activation process by sending the wakeup signal TN.

ARL Activation Request Local Loop-back

The U-transceiver is requested to operate an analog loop-back (close to the U-interface) and to begin the start-up sequence by sending SN1 (without starting timer T1). This command may be issued only after the U-transceiver has been HW- or SW-reset. This eases that the EC- and EQ-coefficient updating algorithms converge correctly. The ARL-command has to be issued continuously as long as the loop-back is required.

DI Deactivation Indication

This indication is used during a deactivation procedure to inform the U-transceiver that it may enter the deactivated (power-down) state.

DT Data Through

This unconditional command is used for test purposes only and forces the U-transceiver into the "Transparent" state.

El1 Error Indication 1

The downstream device indicates an error condition (loss of frame alignment or loss of incoming signal). The U-transceiver informs the LT-side by setting the ACT-bit to "0" thus indicating that transparency has been lost.

RES Reset

Unconditional command which resets the U-transceiver.

SSP Send Single Pulses

Unconditional command which requests the transmission of single pulses on the

U-interface.

TIM Timing

The U-transceiver is requested to enter state 'IOM®-2 Awaked'.

#### **U-Interface Events:**

- ACT = 0/1 ACT-bit received from LT-side.