Wired Communications

Never stop thinking.

#### Edition 2003-07-31

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 8/4/03. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

DELIC-LC

**DELIC-PB**

DSP Embedded Line and Port Interface Controller

PEB 20570 Version 3.1

PEB 20571 Version 3.1

Wired Communications

| istory:    | 2003-07-31                          | DS 2.1             |

|------------|-------------------------------------|--------------------|

| ersion:    | DS2                                 |                    |

| Subjects ( | (major changes since last revision) |                    |

| Trademar   | ks updated                          |                    |

|            |                                     |                    |

|            |                                     |                    |

|            |                                     |                    |

|            |                                     |                    |

|            |                                     |                    |

|            |                                     |                    |

|            |                                     |                    |

|            |                                     |                    |

|            | istory:<br>ersion:<br>Subjects      | istory: 2003-07-31 |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

Note: OCEM<sup>®</sup> and OakDSPCore<sup>®</sup> (OAK<sup>®</sup>) are registered trademarks of ParthusCeva, Inc..

| Table of                                        | Contents                                                                                                                                                              | age                      |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4<br>1.4.1<br>1.4.2 | Introduction  DELIC-LC Key Features  DELIC-PB Key Features  Logic Symbol  Typical Applications  Applications for DELIC-LC  Applications for DELIC-PB                  | . 4<br>. 4<br>. 6<br>. 7 |

| 2<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5            | Pin Description Pin Diagram DELIC-LC Pin Diagram DELIC-PB Pin Definitions and Functions for DELIC-LC Pin Definitions and Functions for DELIC-PB Strap Pin Definitions | 10<br>11<br>12<br>24     |

| <b>3</b> 3.1                                    | Interface Description                                                                                                                                                 |                          |

| 3.2<br>3.2.1<br>3.2.2                           | IOM-2000 Interface                                                                                                                                                    | 41<br>41                 |

| 3.2.2.1<br>3.2.2.2<br>3.2.3                     | Data Interface                                                                                                                                                        | 42<br>45                 |

| 3.2.3.1<br>3.2.3.2                              | INFO Structure on the UPN Interface                                                                                                                                   | 48<br>50                 |

| 3.2.4<br>3.2.4.1<br>3.2.4.2                     | S/T State Machine                                                                                                                                                     | 55                       |

| 3.3<br>3.3.1                                    | IOM®-2 Interface                                                                                                                                                      | 63                       |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4         | μP Interface Intel/Infineon or Motorola Mode De-Multiplexed or Multiplexed Mode DMA or Non-DMA Mode DELIC External Interrupts                                         | 64<br>64<br>66           |

| 3.5<br>3.5.1<br>3.5.2                           | JTAG Test Interface                                                                                                                                                   | 67<br>67                 |

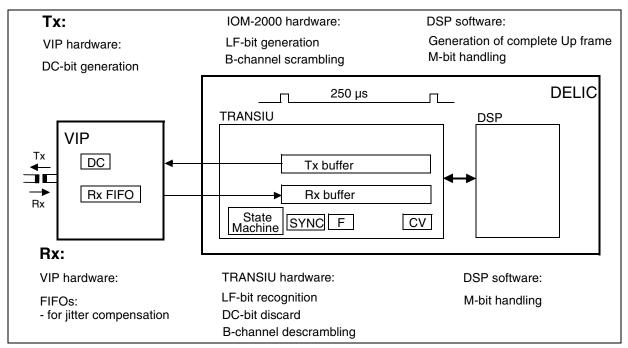

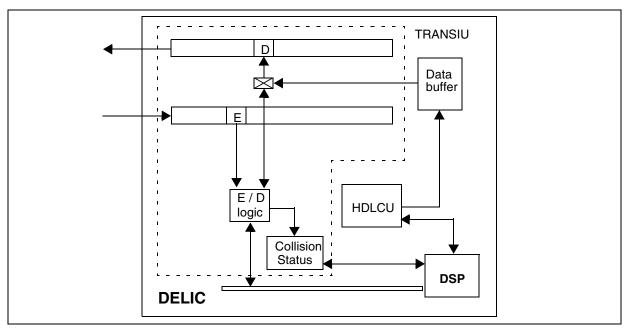

| 4.1<br>4.2<br>4.2.1<br>4.2.2                    | Functional Description  Functional Overview and Block Diagram  IOM-2000 Transceiver Unit (TRANSIU)  IOM-2000 Features  IOM-2000 Initialization                        | 70<br>71<br>71           |

| Table of | Contents                                             | Page |

|----------|------------------------------------------------------|------|

| 4.2.3    | Initialization of the VIP                            | 72   |

| 4.2.4    | IOM-2000 Command and Status Interface                | 72   |

| 4.2.4.1  | Initialization Mode Command Bits                     | 72   |

| 4.2.4.2  | Operational Mode Command/Status Bits                 |      |

| 4.2.4.3  | Command/Status Transmission                          |      |

| 4.2.4.4  | Command and Status format in the Data RAM            | 74   |

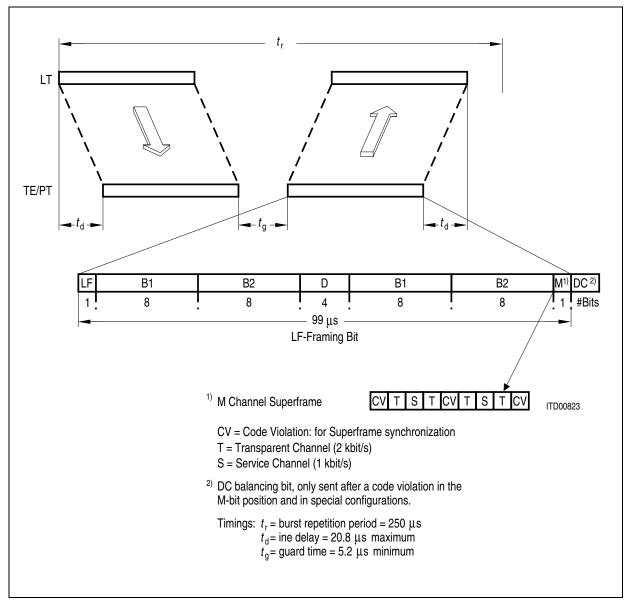

| 4.2.5    | UPN Mode Frame Structure                             | 76   |

| 4.2.6    | UPN Interface                                        | 79   |

| 4.2.7    | UPN Framing Bit Description                          | 80   |

| 4.2.7.1  | Framing Bit (LF-Bit)                                 | 80   |

| 4.2.7.2  | Multiframing Bit (M-Bit)                             | 80   |

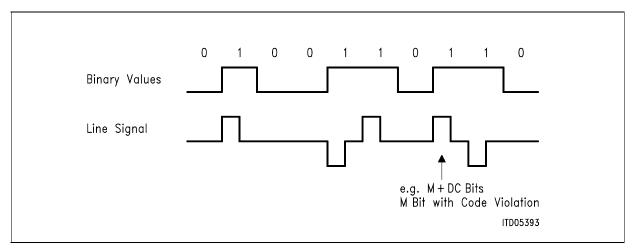

| 4.2.7.3  | DC-Balancing Bit                                     | 81   |

| 4.2.7.4  | UPN Mode Data Format                                 | 81   |

| 4.2.7.5  | UPN Scrambler/Descrambler                            | 82   |

| 4.2.8    | DECT Synchronization for UPN- Interface              | 82   |

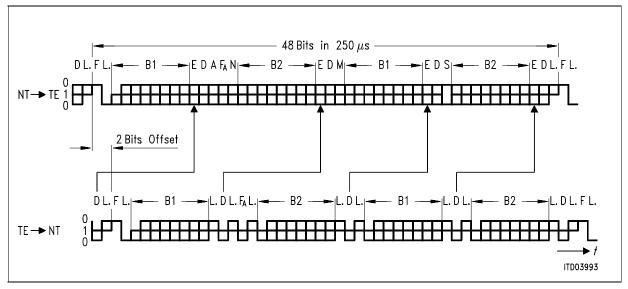

| 4.2.9    | S/T Interface Frame Structure                        | 83   |

| 4.2.9.1  | LT-S mode                                            | 86   |

| 4.2.9.2  | LT-T Mode                                            | 88   |

| 4.2.10   | S/T Mode Control and Framing Bits on IOM-2000        | 90   |

| 4.2.10.1 | Framing Bit (F-Bit)                                  | 90   |

| 4.2.10.2 | Multiframing Bits                                    | 90   |

| 4.2.10.3 | Fa/N Bit                                             | 92   |

| 4.2.10.4 | DC-Balancing Bit (L-Bit)                             | 93   |

| 4.2.11   | IOM-2000 Data Interface                              | 93   |

| 4.2.11.1 | S/T Mode Data Format                                 | 93   |

| 4.2.12   | Test Loop                                            | 94   |

| 4.3      | IOM-2 Unit                                           | 95   |

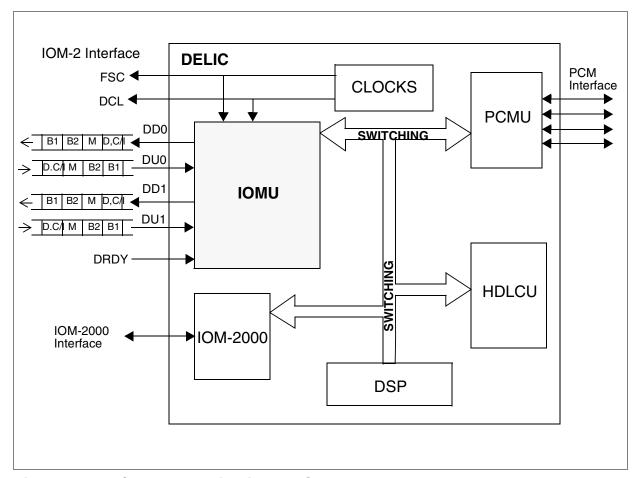

| 4.3.1    | IOMU Features                                        | 95   |

| 4.3.2    | IOMU Functional and Operational Description          | 96   |

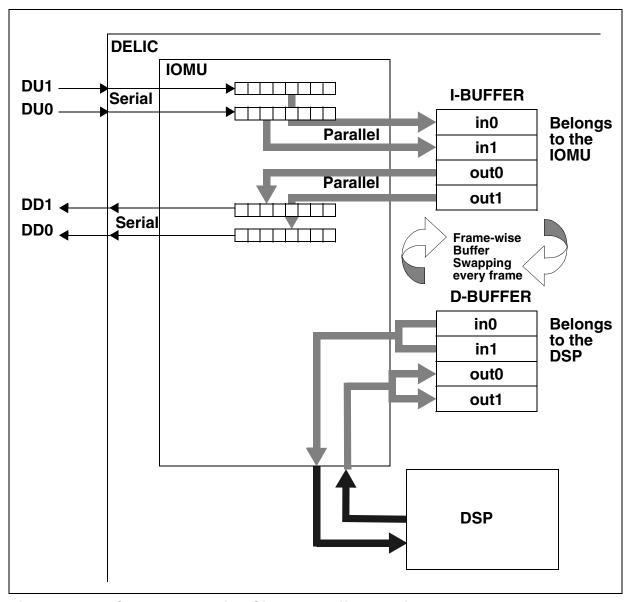

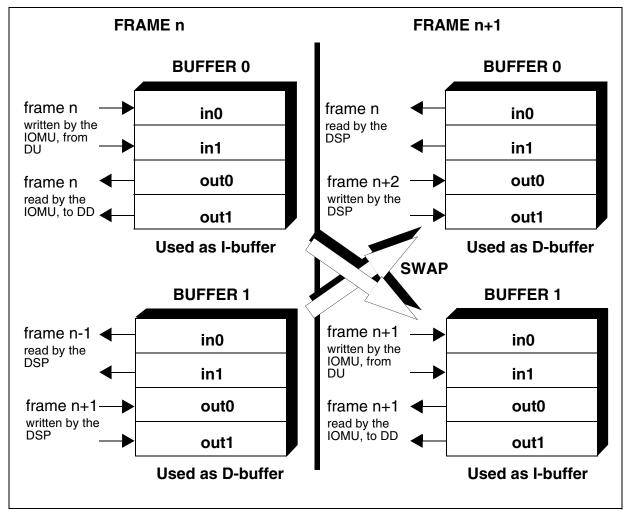

| 4.3.2.1  | Frame-Wise Buffer Swapping                           | 96   |

| 4.3.2.2  | DSP Inaccessible Buffer (I-buffer) Logical Structure |      |

| 4.3.2.3  | DSP Access to the D-Buffer                           |      |

| 4.3.2.4  | Circular Buffer Architecture                         | 98   |

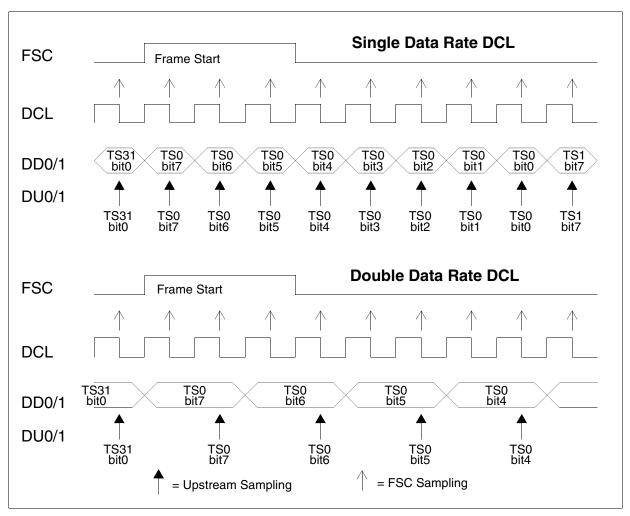

| 4.3.2.5  | IOM-2 Interface Data Rate Modes                      | 100  |

| 4.3.2.6  | IOMU Serial Data Processing                          | 101  |

| 4.3.2.7  | IOMU Parallel Data Processing                        | 101  |

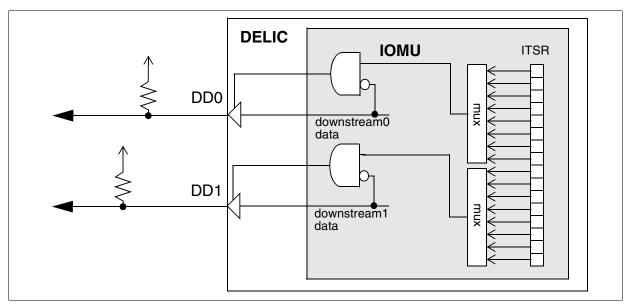

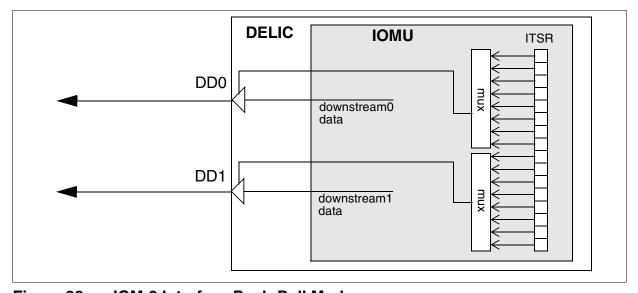

| 4.3.2.8  | IOM-2 Push-Pull and Open-Drain Modes                 | 102  |

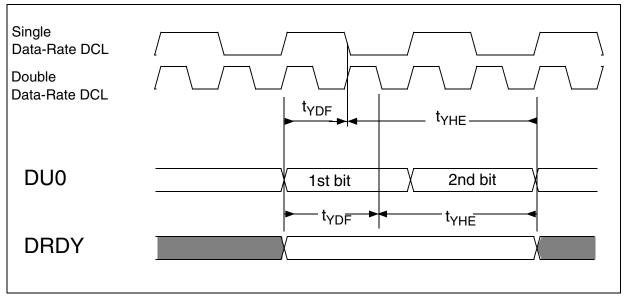

| 4.3.2.9  | Support of DRDY Signal from QUAT-S                   |      |

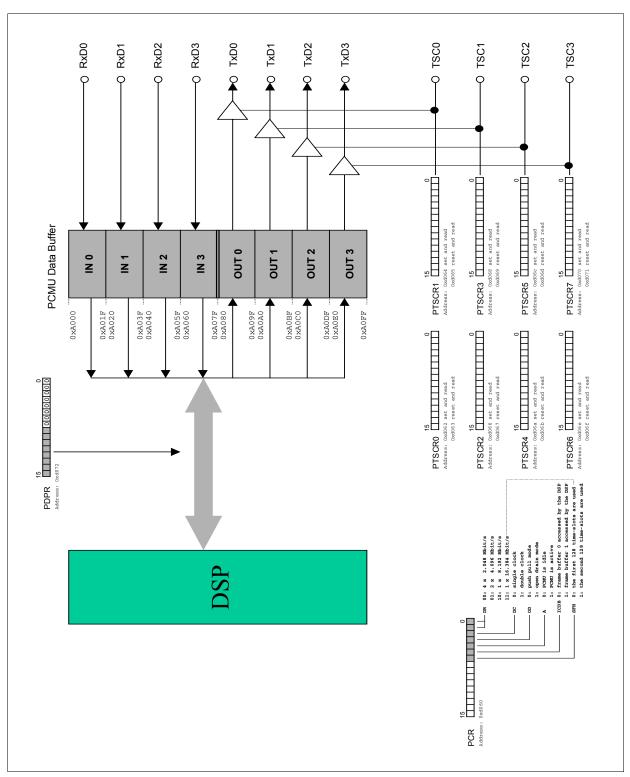

| 4.4      | PCM Unit                                             |      |

| 4.4.1    | PCMU Functional and Operational Description          |      |

| 4.4.1.1  | Frame-Wise Buffer Swapping                           |      |

| 4.4.1.2  | DSP Inaccessible Buffer (I-buffer)                   | 105  |

| Table of | Contents                                           | Page  |

|----------|----------------------------------------------------|-------|

| 4.4.1.3  | DSP Accessible Buffer (D-Buffer)                   | . 106 |

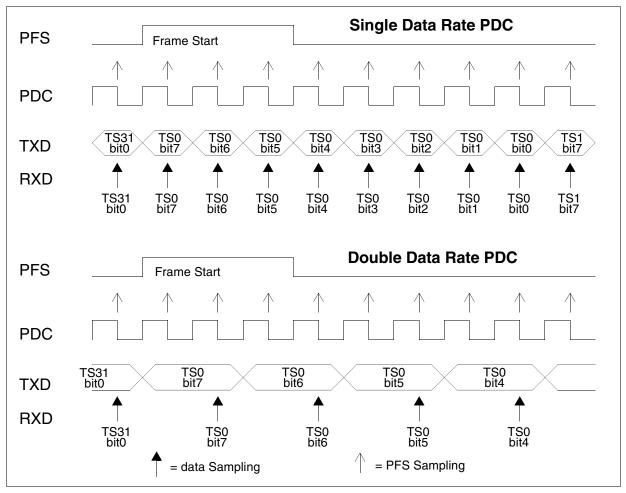

| 4.4.1.4  | PCMU Interface Data Rate Modes                     |       |

| 4.4.1.5  | PCMU Serial Data Processing                        | . 108 |

| 4.4.1.6  | PCMU Parallel Data Processing                      | . 108 |

| 4.4.1.7  | PCMU Tri-state Control Logic                       |       |

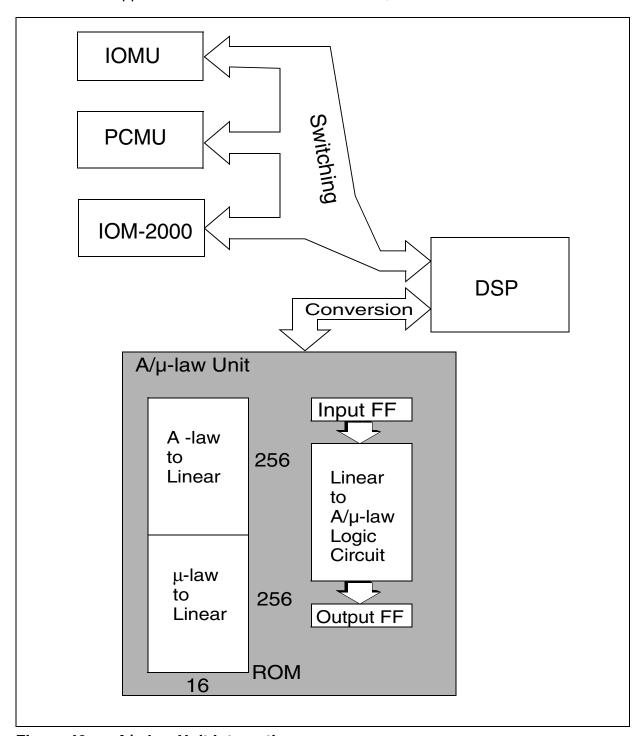

| 4.5      | A-/μ-law Conversion Unit                           |       |

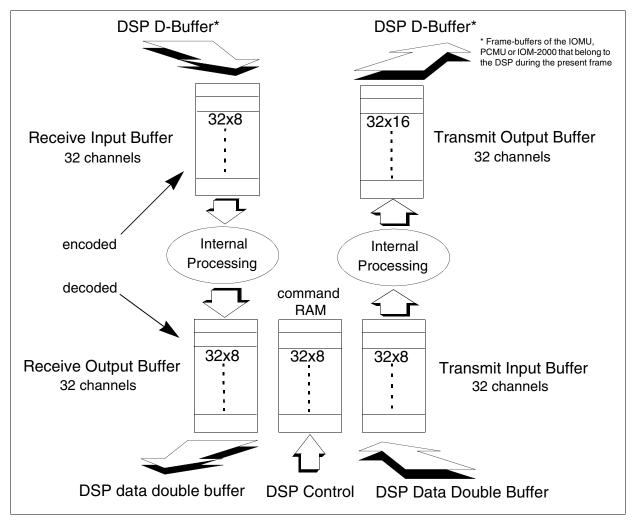

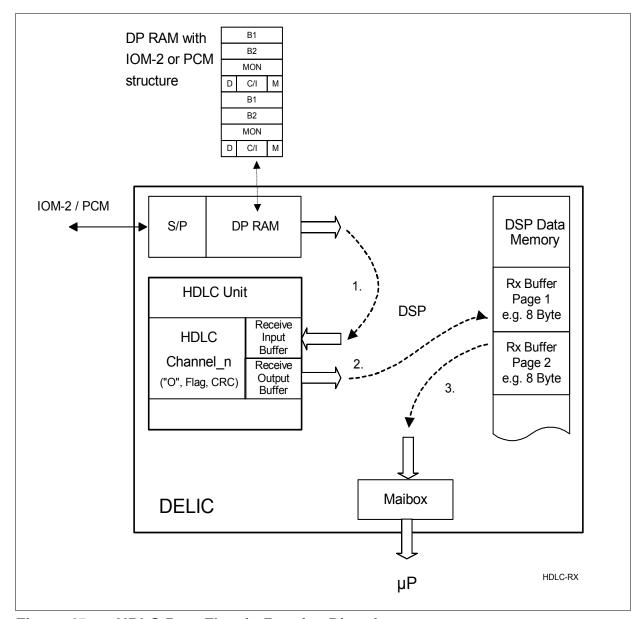

| 4.6      | HDLC Unit                                          |       |

| 4.6.1    | HDLC Overview                                      | . 113 |

| 4.6.2    | HDLCU Operation                                    | . 115 |

| 4.6.2.1  | Initialization of the HDLCU                        |       |

| 4.6.2.2  | Transmitting a Message                             | . 115 |

| 4.6.2.3  | Ending a Transmission                              |       |

| 4.6.2.4  | Aborting a Transmission                            | . 116 |

| 4.6.2.5  | DSP Access to the HDLCU Buffers                    | . 116 |

| 4.6.3    | Functionality                                      | . 116 |

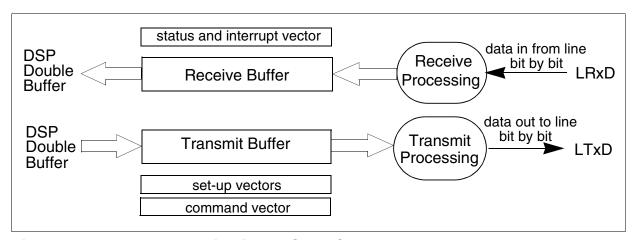

| 4.7      | GHDLC Unit                                         | . 119 |

| 4.7.1    | GHDLC Overview                                     | . 119 |

| 4.7.2    | GHDLC General Modes of Operation                   | . 119 |

| 4.7.3    | External Configuration and Handshaking in Bus Mode | . 120 |

| 4.7.3.1  | External Tri-State in Point-to-Multi-Point Mode    | . 120 |

| 4.7.3.2  | Arbitration Between Several GHDLCs                 | . 120 |

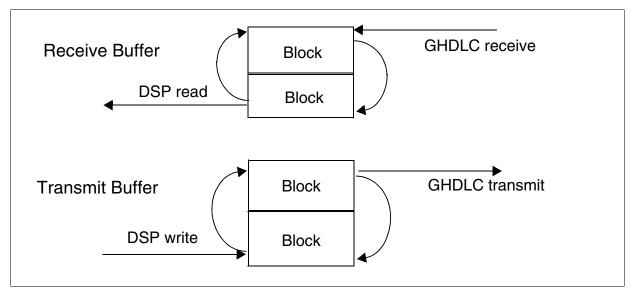

| 4.7.4    | GHDLC Memory Allocation                            | . 122 |

| 4.7.5    | GHDLC Interrupts                                   | . 124 |

| 4.7.6    | Operational Description                            | . 124 |

| 4.7.6.1  | GHDLC Initialization                               | . 124 |

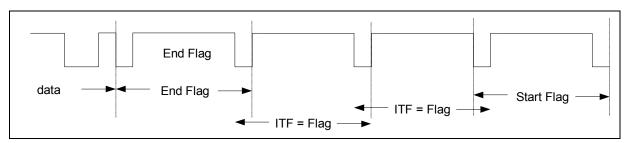

| 4.7.7    | GHDLC Protocol Features                            | . 125 |

| 4.7.8    | GHDLC possible Data Rates for the DELIC-LC/PB      | . 125 |

| 4.7.9    | GHDLC Using external DMA Controller                | . 126 |

| 4.8      | DSP Control Unit                                   | . 127 |

| 4.8.1    | General                                            |       |

| 4.8.2    | DSP Address Decoding                               |       |

| 4.8.3    | Interrupt Handling                                 |       |

| 4.8.4    | DSP Run Time Statistics                            |       |

| 4.8.5    | Data Bus and Program Bus Arbitration               |       |

| 4.8.6    | Boot Support                                       |       |

| 4.8.7    | Reset Execution and Boot Strap Pin Setting         |       |

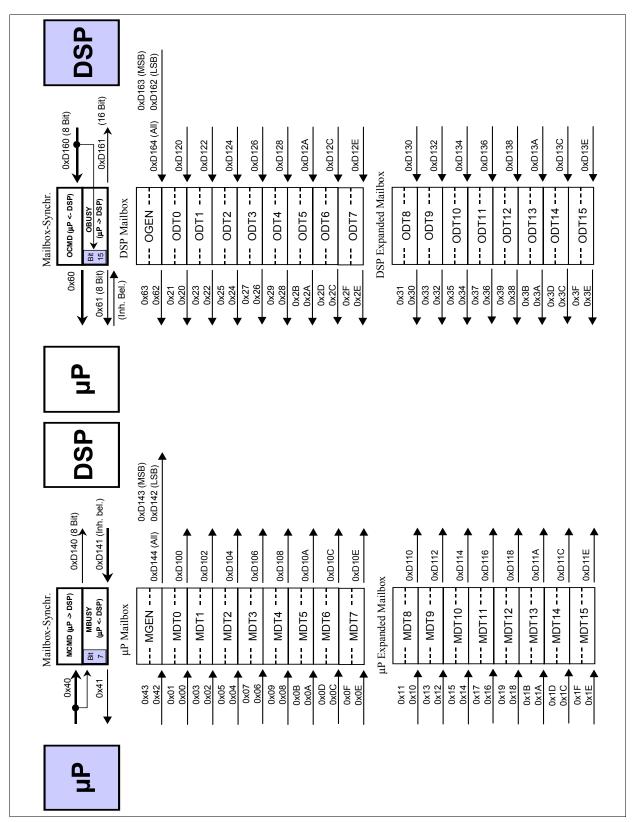

| 4.9      | General Mailbox                                    |       |

| 4.9.1    | Overview                                           |       |

| 4.9.2    | μP Mailbox                                         |       |

| 4.9.3    | OAK Mailbox                                        |       |

| 4.10     | DMA Mailbox (DELIC-PB only)                        |       |

| 4.10.1   | DMA Handshake                                      | . 136 |

| Table of                                                                                                                                   | Contents                                                                                                                                                                                                                                                                                                                                                                                    | Page                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 4.10.1.1<br>4.10.1.2<br>4.10.3<br>4.10.4<br>4.10.5<br>4.11<br>4.11.1<br>4.11.2<br>4.11.3<br>4.11.4<br>4.11.5<br>4.11.6<br>4.11.7<br>4.11.8 | Two-cycle DMA Transfer Mode Fly-by Mode PEC Mode. Transmit DMA Mailbox Receive DMA Mailbox FIFO Access Clock Generator Overview DSP Clock Selection PCM Master/Slave Mode Clocks Selection DELIC Clock System Synchronization IOM-2 Clock Selection IOM-2000 Clock Selection REFCLK Configuration GHDLC Clock Selection                                                                     | . 137<br>. 137<br>. 139<br>. 141<br>. 142<br>. 144<br>. 144<br>. 144<br>. 145<br>. 145 |

| 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.2                                                                                                 | DELIC Memory Structure  DSP Address Space  DSP Register Address Space  DSP Program Address Space  DSP Data Address Space  µP Address Space                                                                                                                                                                                                                                                  | . 146<br>. 146<br>. 146<br>. 147                                                       |

| 6<br>6.1<br>6.2<br>6.2.1<br>6.2.1.1<br>6.2.1.2<br>6.2.1.3<br>6.2.1.4<br>6.2.1.5<br>6.2.1.6<br>6.2.1.7                                      | Register Description  Register Map  Detailed Register Description  TRANSIU Register Description  TRANSIU IOM-2000 Configuration Register  TRANSIU Channel Configuration Registers  VIP Command Registers (VIPCMR0, VIPCMR1, VIPCMR2)  VIP Status Registers  TRANSIU Initialization Channel Command Register  TRANSIU Initialization Channel Status Register (TICSTR)  Up Test Loop Register | . 151<br>. 161<br>. 161<br>. 162<br>. 164<br>. 167<br>. 168<br>. 173                   |

| 6.2.1.8<br>6.2.1.9<br>6.2.2<br>6.2.2.1<br>6.2.2.2<br>6.2.2.3<br>6.2.2.4<br>6.2.2.5<br>6.2.3                                                | Scrambler Mode Register Scrambler Status Register  IOMU Register Description IOMU Control Register IOMU Status Register IOMU Tri-State Control Register IOMU DRDY Register IOMU Data Prefix Register PCMU Register Description                                                                                                                                                              | . 176<br>. 177<br>. 177<br>. 178<br>. 179<br>. 181<br>. 182                            |

| Table of Co | ontents                                             | Page |

|-------------|-----------------------------------------------------|------|

| 6.2.3.1     | PCMU Command Register                               | 183  |

| 6.2.3.2     | PCMU Status Register                                |      |

| 6.2.3.3     | PCMU Tri-state Control Registers                    | 185  |

| 6.2.3.4     | PCMU Data Prefix Register                           |      |

| 6.2.4       | A-/μ-law Unit Register Description                  |      |

| 6.2.4.1     | A/μ-law Unit Control Register                       | 188  |

| 6.2.4.2     | A/μ-law Input Register                              | 189  |

| 6.2.4.3     | A/μ-law Output Register                             | 190  |

| 6.2.5       | HDLCU Registers Description                         | 191  |

| 6.2.5.1     | HDLCU Control Register                              | 191  |

| 6.2.5.2     | HDLCU Status Register                               | 192  |

| 6.2.5.3     | Channel Command Vector                              | 193  |

| 6.2.5.4     | Channel Status Vector                               | 195  |

| 6.2.6       | GHDLC Register Description                          | 197  |

| 6.2.6.1     | GHDLC Test/ Normal Mode Register                    |      |

| 6.2.6.2     | GHDLC Channel Mode Register                         | 198  |

| 6.2.6.3     | GHDLC Interrupt Register                            |      |

| 6.2.6.4     | GHDLC FSC Interrupt Control Register                | 200  |

| 6.2.6.5     | GHDLC Receive Channel Status Registers 03           | 201  |

| 6.2.6.6     | GHDLC Receive Data and Status                       | 203  |

| 6.2.6.7     | GHDLC Mode Registers                                |      |

| 6.2.6.8     | GHDLC Channel Transmit Command Registers            |      |

| 6.2.6.9     | ASYNC Control Register                              |      |

| 6.2.6.10    | LCLK0 Control Register                              |      |

| 6.2.6.11    | LCLK1 Control Register                              | 209  |

| 6.2.6.12    | LCLK2 Control Register                              |      |

| 6.2.6.13    | LCLK3 Control Register                              |      |

| 6.2.6.14    | Muxes Control Register                              |      |

| 6.2.6.15    | GHDLCU Frame Frequency                              |      |

| 6.2.7       | DCU Register Description                            |      |

| 6.2.7.1     | Interrupt Mask Register                             |      |

| 6.2.7.2     | Status Event Register                               |      |

| 6.2.7.3     | Statistics Counter Register                         |      |

| 6.2.7.4     | Statistics Register                                 |      |

| 6.2.8       | μP Configuration Registers                          |      |

| 6.2.8.1     | μP Interface Configuration Register                 |      |

| 6.2.8.2     | Interrupt Vector Register                           |      |

| 6.2.9       | μP Mailbox Registers Description                    |      |

| 6.2.9.1     | μP Command Register                                 |      |

| 6.2.9.2     | μP Mailbox Busy Register                            |      |

| 6.2.9.3     | μP Mailbox Generic Data Register                    |      |

| 6.2.9.4     | μP Mailbox (General and DMA Mailbox) Data Registers | 224  |

| Table of  | Contents                                             | Page  |

|-----------|------------------------------------------------------|-------|

| 6.2.9.5   | DSP Command Register                                 | . 225 |

| 6.2.9.6   | DSP Mailbox Busy Register                            | . 226 |

| 6.2.9.7   | DSP Mailbox Generic Data Register                    | . 227 |

| 6.2.9.8   | DSP Mailbox (General and DMA Mailbox) Data Registers | . 228 |

| 6.2.10    | DMA Mailbox Registers Description                    | . 229 |

| 6.2.10.1  | DMA Mailbox Transmit Counter Register                | . 229 |

| 6.2.10.2  | DMA Mailbox Receive Counter Register                 | . 230 |

| 6.2.10.3  | DMA Mailbox Interrupt Status Register                | . 231 |

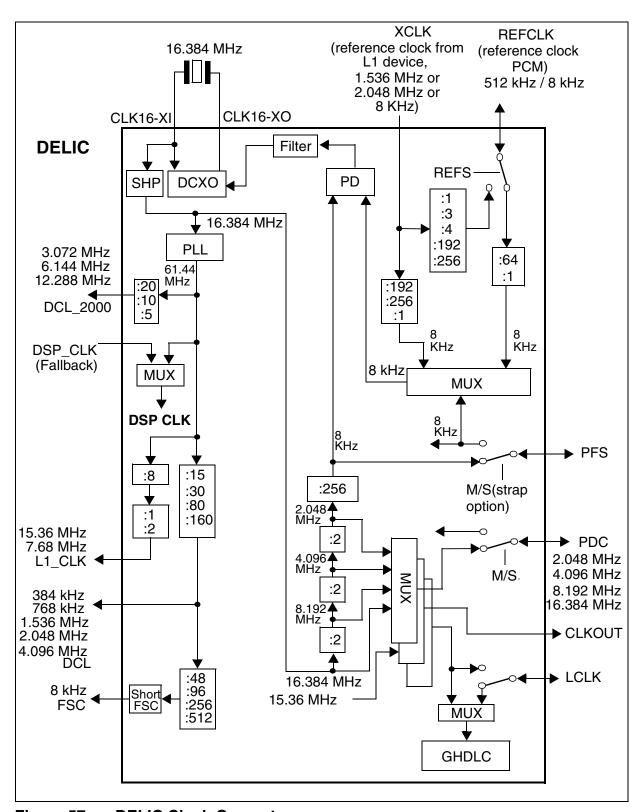

| 6.2.11    | Clock Generator Register Description                 | . 232 |

| 6.2.11.1  | PDC Control Register                                 | . 232 |

| 6.2.11.2  | PFS Control Register                                 |       |

| 6.2.11.3  | CLKOUT Control Register                              |       |

| 6.2.11.4  | DCXO Reference Clock Select Register                 |       |

| 6.2.11.5  | REFCLK Control Register                              |       |

| 6.2.11.6  | DCL_2000 Control Register                            |       |

| 6.2.11.7  | DCL Control Register                                 |       |

| 6.2.11.8  | FSC Control Register                                 |       |

| 6.2.11.9  | L1_CLK Control Register                              |       |

| 6.2.11.10 | , 5                                                  |       |

| 6.2.11.11 | Real-time Counter Register                           |       |

| 6.2.11.12 | Strap Status Register                                | . 243 |

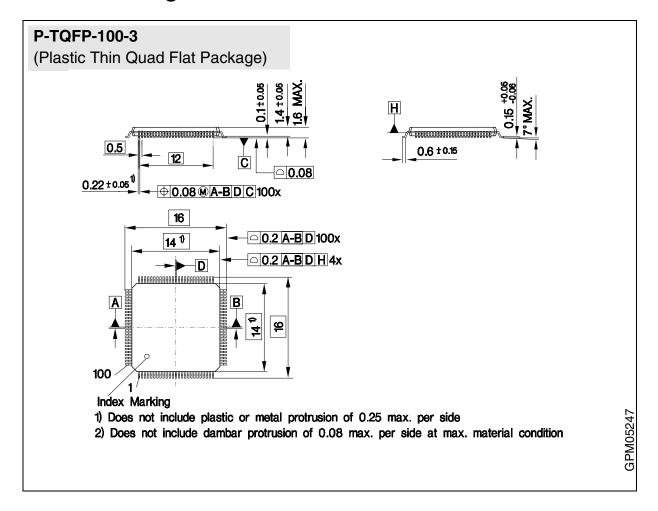

| 7         | Package Outlines                                     | . 244 |

| 8         | Electrical Characteristics and Timing Diagrams       | . 245 |

| 8.1       | Absolute Maximum Ratings                             | . 245 |

| 8.2       | Operating Range                                      | . 246 |

| 8.3       | DC Characteristics                                   | . 247 |

| 8.4       | Capacitances                                         |       |

| 8.5       | Recommended 16.384 MHz Crystal Parameters            | . 248 |

| 8.6       | AC Characteristics                                   |       |

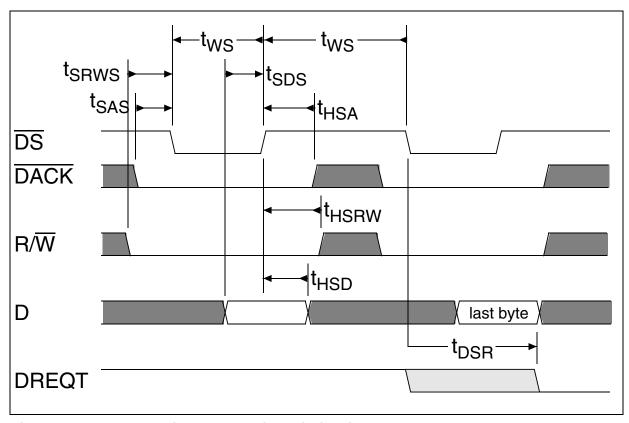

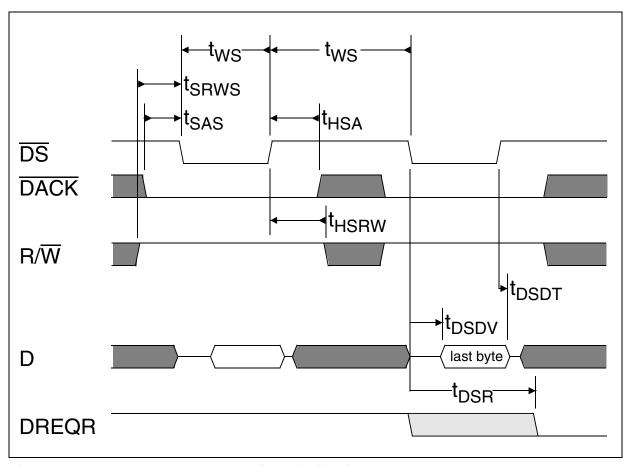

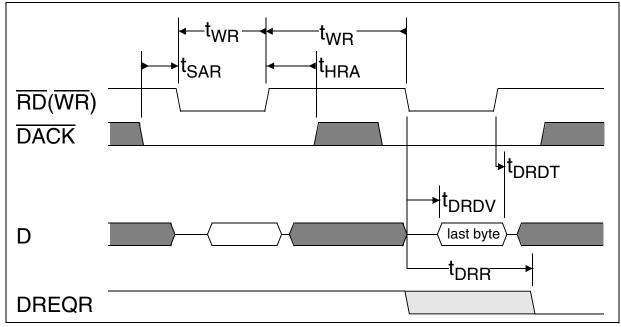

| 8.6.1     | DMA Access Timing                                    |       |

| 8.6.1.1   | DMA Access Timing In Motorola Mode                   |       |

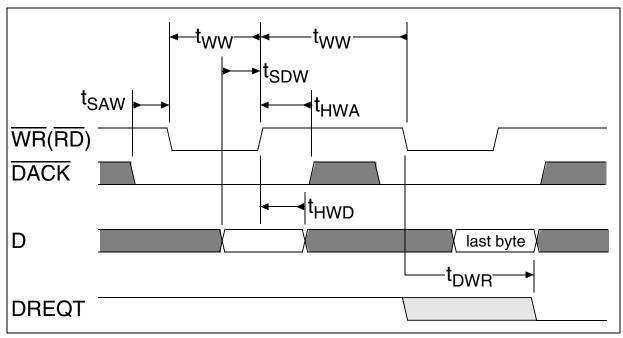

| 8.6.1.2   | DMA Access Timing In Intel/Infineon Mode             | . 252 |

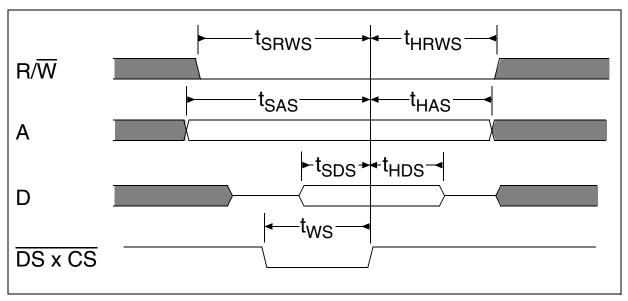

| 8.6.2     | mP Access Timing                                     |       |

| 8.6.2.1   | mP Access Timing in Motorola mode                    |       |

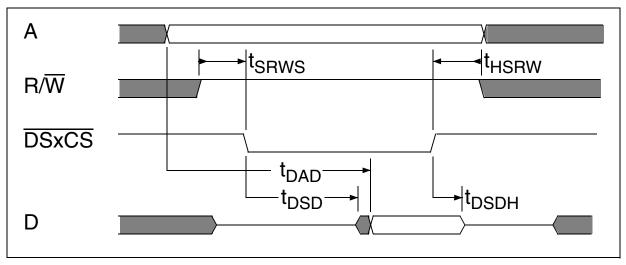

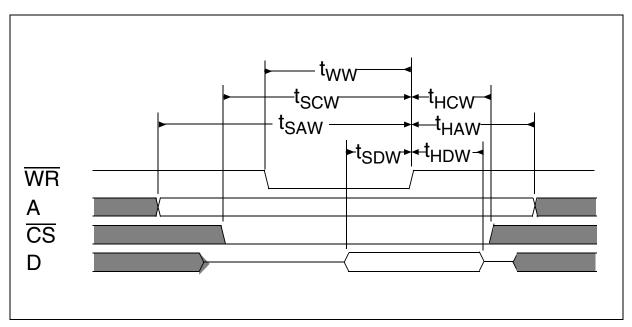

| 8.6.2.2   | mP Access Timing in Intel/Infineon Mode              |       |

| 8.6.3     | Interrupt Acknowledge Cycle Timing                   |       |

| 8.6.4     | IOM-2 Interface Timing                               |       |

| 8.6.5     | PCM Interface Timing                                 |       |

| 8.6.6     | IOM-2000 Interface Timing                            |       |

| 8.6.7     | LNC03 (Local Network Controller) Interface Timing    |       |

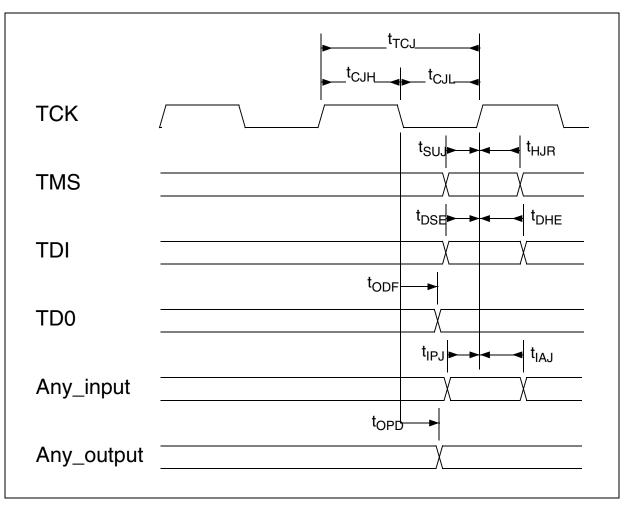

| 8.6.8     | JTAG and Emulation Interface Timing                  | . 277 |

| Table | of Contents                                  | Page |

|-------|----------------------------------------------|------|

| 9     | Application Hints                            | 282  |

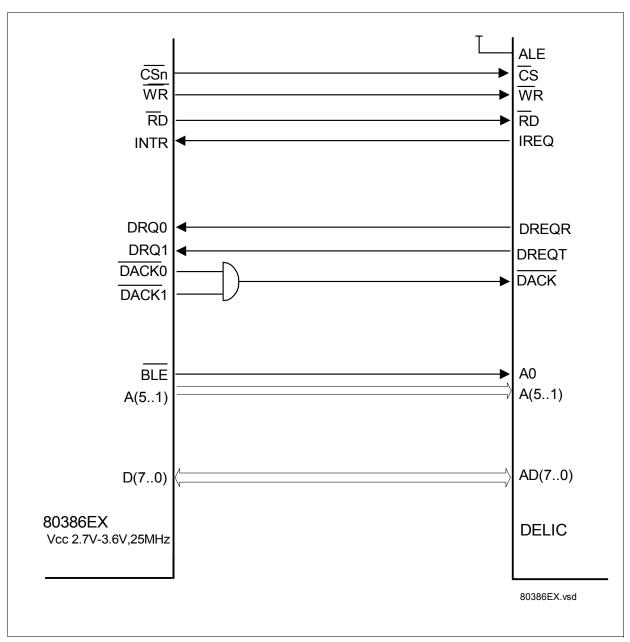

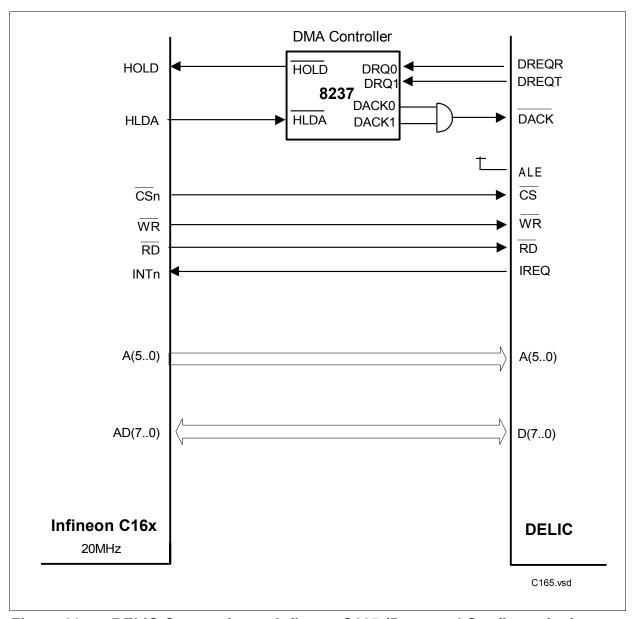

| 9.1   | DELIC Connection to External Microprocessors | 282  |

| 9.2   | DELIC Worksheets                             | 284  |

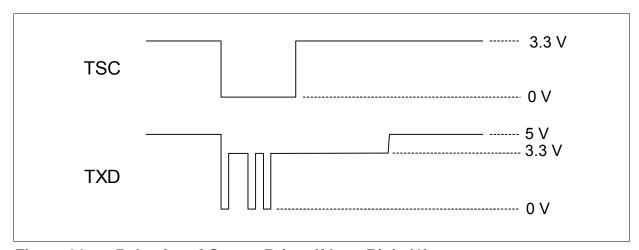

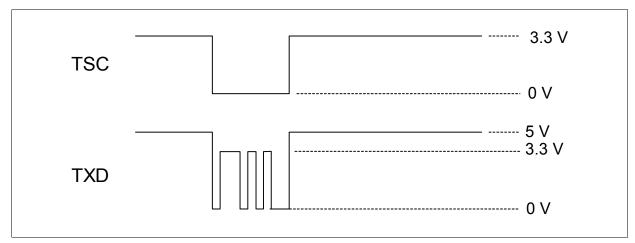

| 9.3   | PCM Output Driver Anomaly                    | 286  |

| 9.4   | Reset Behaviour                              | 287  |

| 10    | Glossary                                     | 288  |

| 11    | Index                                        | 290  |

| List of Figur          | es                                                               | Page |

|------------------------|------------------------------------------------------------------|------|

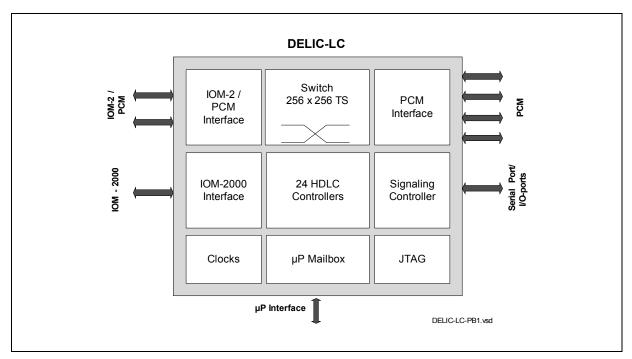

| Figure 1               | Block Diagram of the DELIC-LC                                    | 3    |

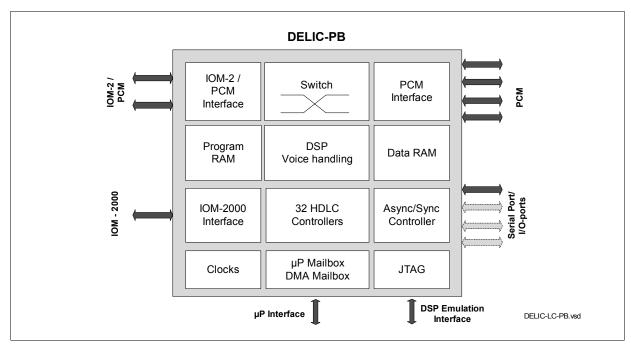

| Figure 2               | Block Diagram of the DELIC-PB                                    |      |

| Figure 3               | Logic Symbol                                                     |      |

| Figure 4               | DELIC-LC in S/T and UPN Line Cards (up to 8 S/T and 16 UPN)      | 7    |

| Figure 5               | DELIC-LC/PB in Uk0 Line Card for 16 Subscribers                  | 8    |

| Figure 6               | DELIC-PB in Analog Line Card for 16 Subscribers                  | 8    |

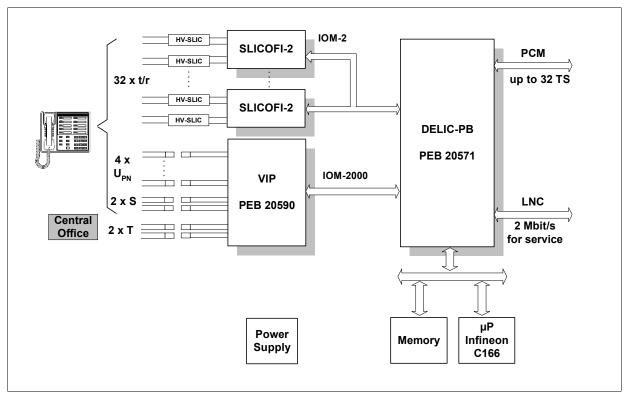

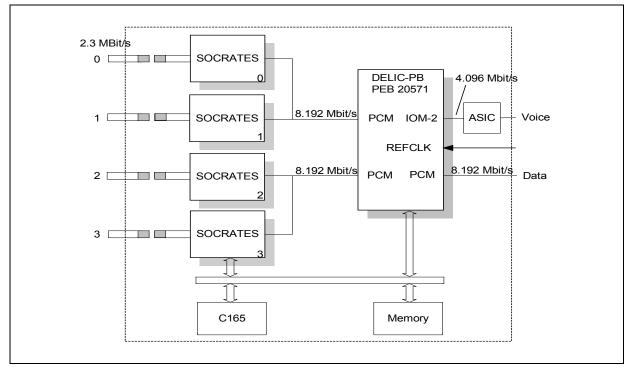

| Figure 7               | DELIC-PB in Small PBX                                            | 9    |

| Figure 8               | DELIC-PB in 4 Port SDSL Line Card                                | 9    |

| Figure 9               | Pin Configuration DELIC-LC                                       | 10   |

| Figure 10              | Pin Configuration DELIC-PB                                       | 11   |

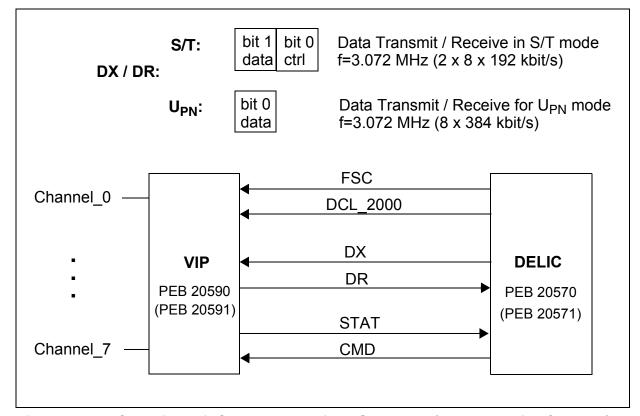

| Figure 11              | Overview of IOM-2000 Interface Structure (Example with One VIP). | 41   |

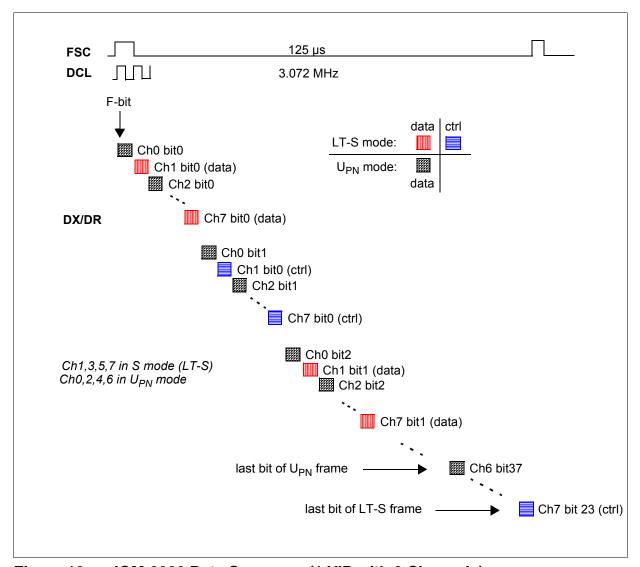

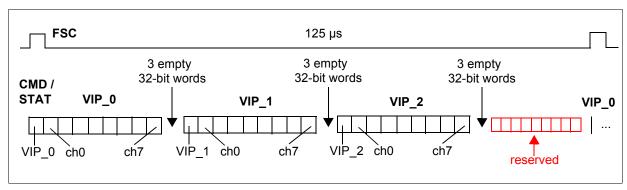

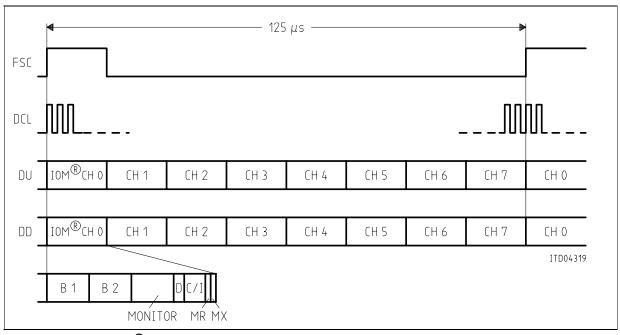

| Figure 12              | IOM-2000 Data Sequence (1 VIP with 8 Channels)                   | 43   |

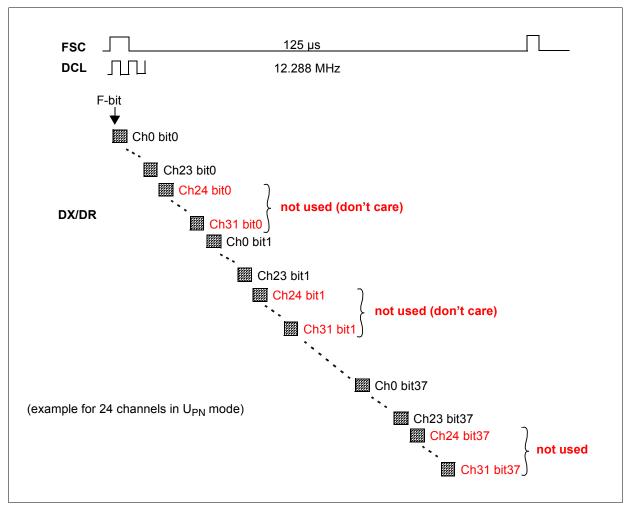

| Figure 13              | IOM-2000 Data Order (3 VIPs with 24 Channels)                    |      |

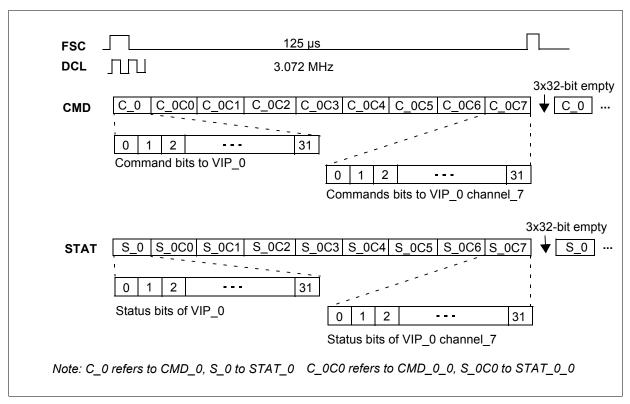

| Figure 14              | IOM-2000 CMD/STAT Handling (1 VIP with 8 Channels)               | 45   |

| Figure 15              | IOM-2000 Command/Status Sequence (3 VIPs with 24 Channels) .     | 45   |

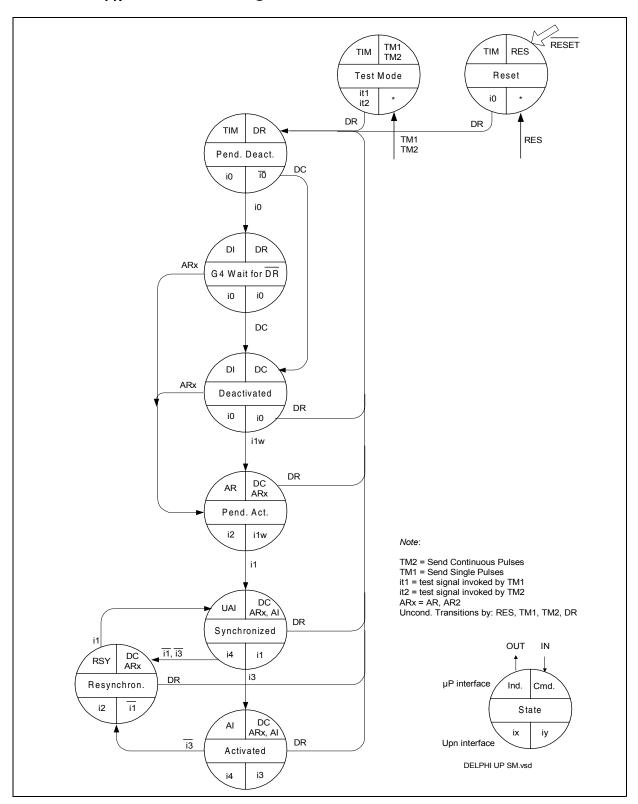

| Figure 16              | UPN State Diagram                                                |      |

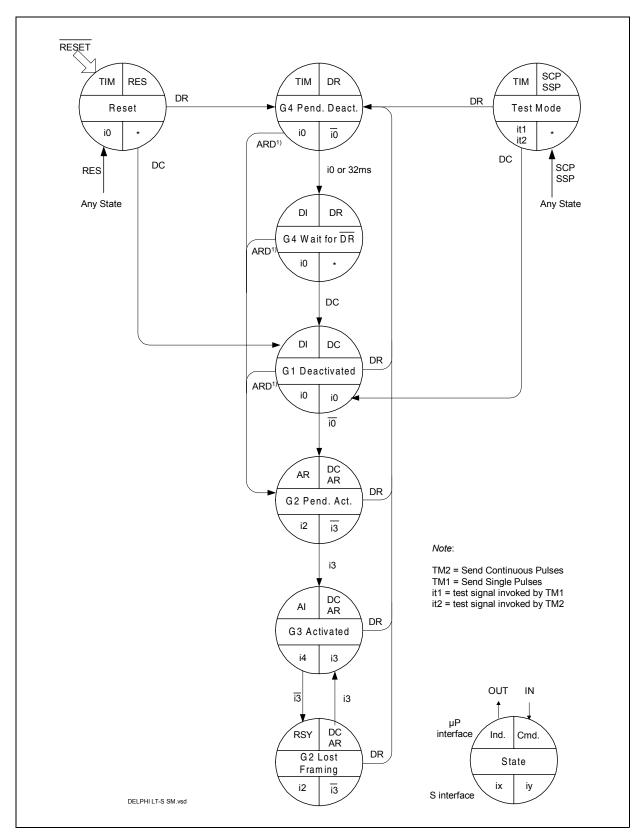

| Figure 17              | State Diagram of LT-S Mode                                       |      |

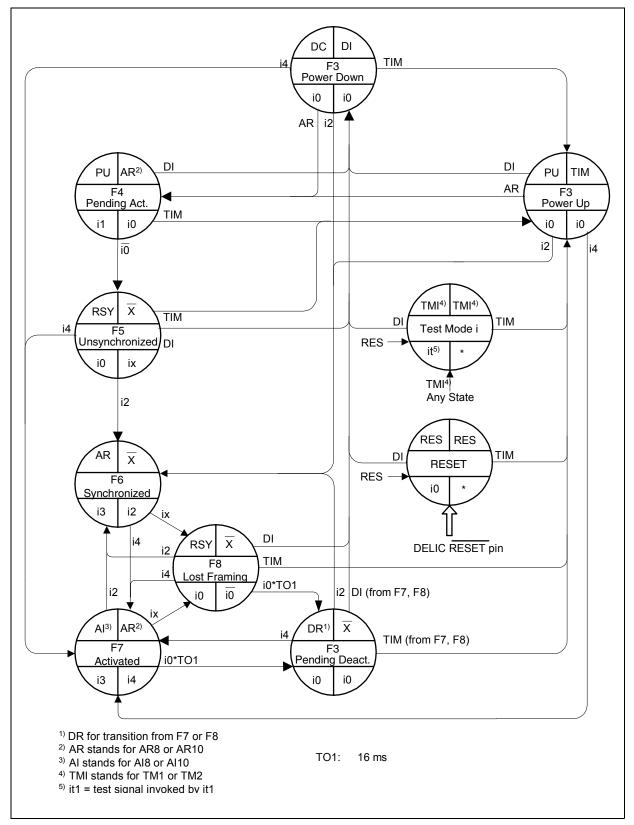

| Figure 18              | LT-T Mode State Diagram (Conditional and Unconditional States)   |      |

| Figure 19              | IOM®-2 Interface in Digital Line Card Mode                       |      |

| Figure 20              | DELIC in Multiplexed and in De-Multiplexed Bus Mode              |      |

| Figure 21              | Block Diagram                                                    |      |

| Figure 22              | U <sub>PN</sub> Interface Frame Structure                        |      |

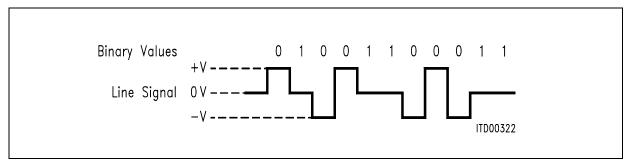

| Figure 23              | AMI Coding on the Up Interface                                   |      |

| Figure 24              | Handling of UPN Frame (one Channel)                              |      |

| Figure 25              | S/T Interface Line Code (without code violation)                 |      |

| Figure 26              | Frame Structure at Reference Points S and T (ITU I.430)          |      |

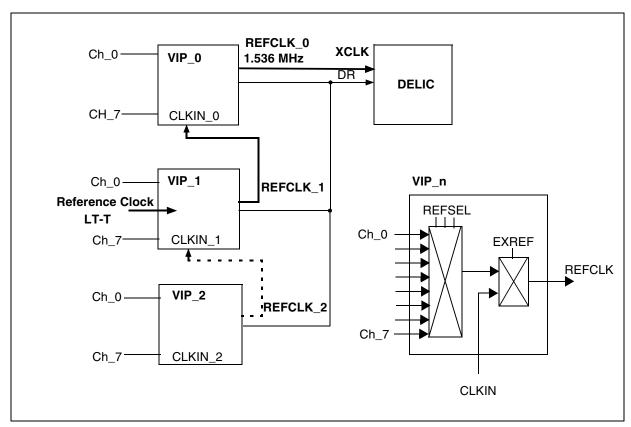

| Figure 27              | Reference Clock Selection for Cascaded VIPs on IOM-2000          |      |

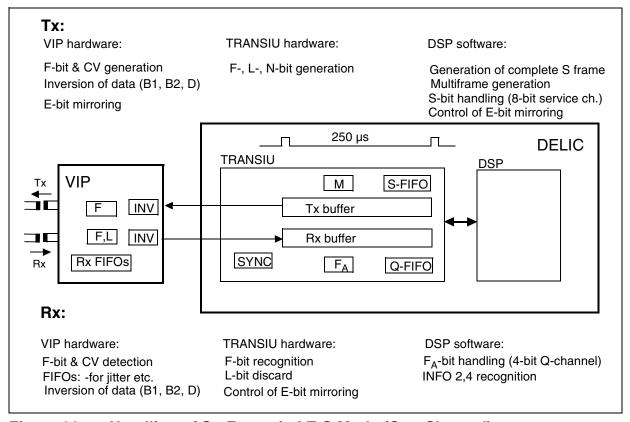

| Figure 28              | Handling of So Frame in LT-S Mode (One Channel)                  |      |

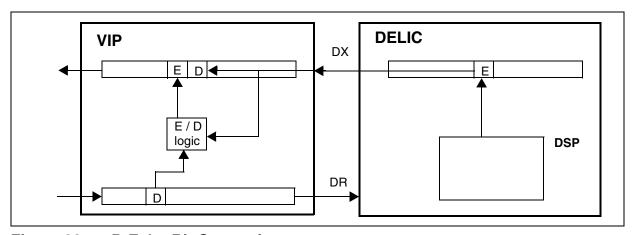

| Figure 29              | D-Echo Bit Generation                                            |      |

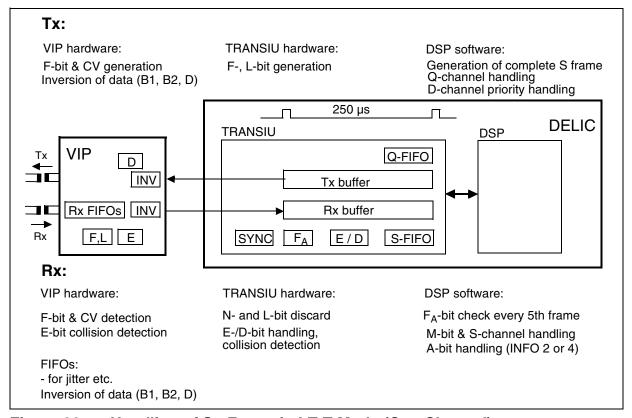

| Figure 30              | Handling of So Frame in LT-T Mode (One Channel)                  |      |

| Figure 31              |                                                                  |      |

| Figure 32<br>Figure 33 | S/Q Channel Assignment                                           |      |

| Figure 34              | IOMU Frame-Wise Circular-Buffer Architecture                     |      |

| Figure 35              | The Circular-Buffer During two Consecutive Frames                |      |

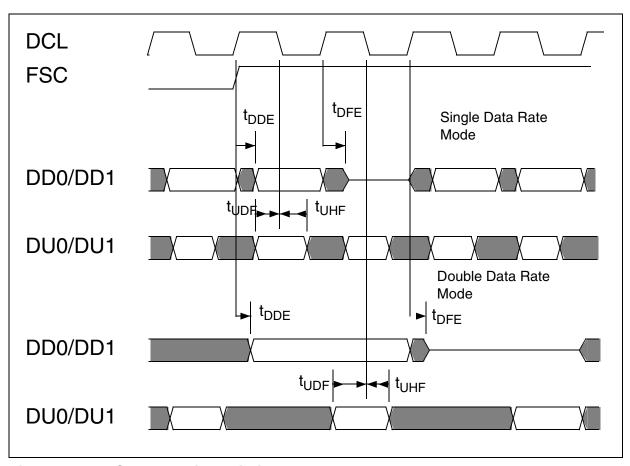

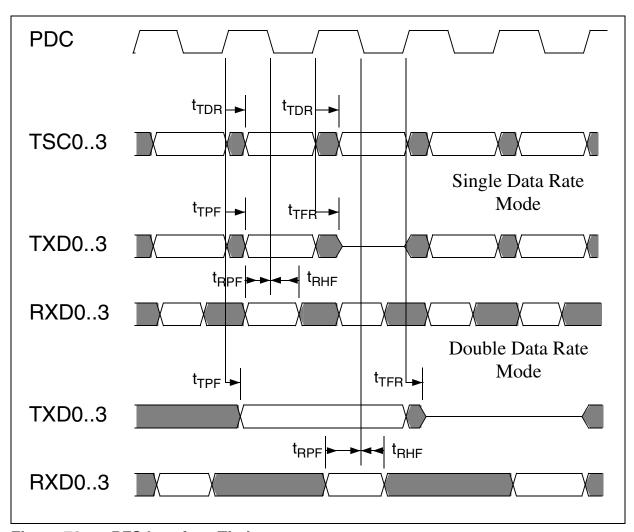

| Figure 36              | IOM-2 Interface Timing in Single/Double Clock Mode               |      |

| Figure 37              | IOM-2 Interface Open-Drain Mode                                  |      |

| Figure 38              | IOM-2 Interface Push-Pull Mode                                   |      |

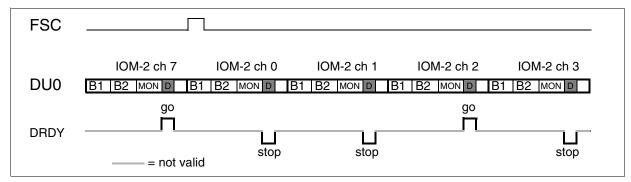

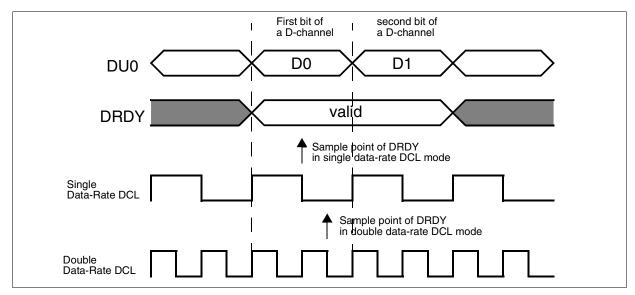

| Figure 39              | DRDY Signal Behavior                                             |      |

| Figure 40              | DRDY Sampling Timing                                             |      |

| Figure 41              | PCMU Integration in DELIC                                        |      |

| Figure 42              | IOM-2 Interface Timing in Single/Double Clock Mode               |      |

| List of Fig | gures Pa                                                             | age |

|-------------|----------------------------------------------------------------------|-----|

| Figure 43   | A/μ-law Unit Integration                                             | 111 |

| Figure 44   | HDLCU General Block Diagram                                          |     |

| Figure 45   | <del>-</del>                                                         | 117 |

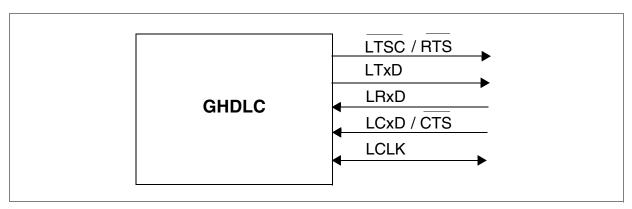

| Figure 46   | Data Processing in the GHDLC                                         | 119 |

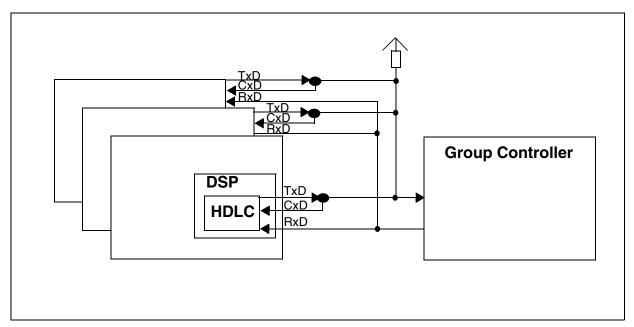

| Figure 47   |                                                                      | 120 |

| Figure 48   | Point-to-Multi Point Bus Structure                                   | 122 |

| Figure 49   | GHDLC Receive and Transmit Buffer Structure 1                        | 124 |

| Figure 50   | Interframe Time Fill with shared Zero                                | 125 |

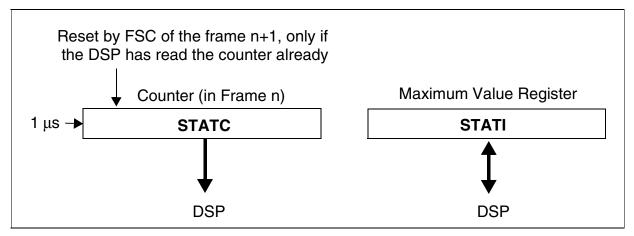

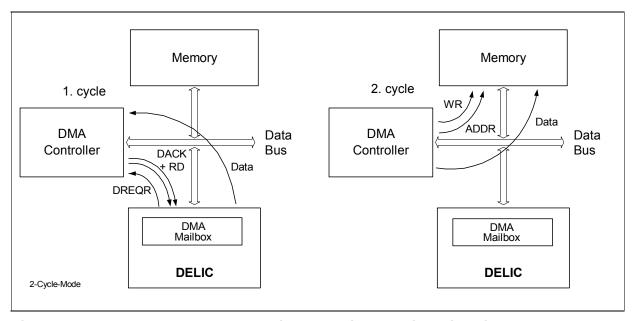

| Figure 51   | Statistics Registers                                                 | 128 |

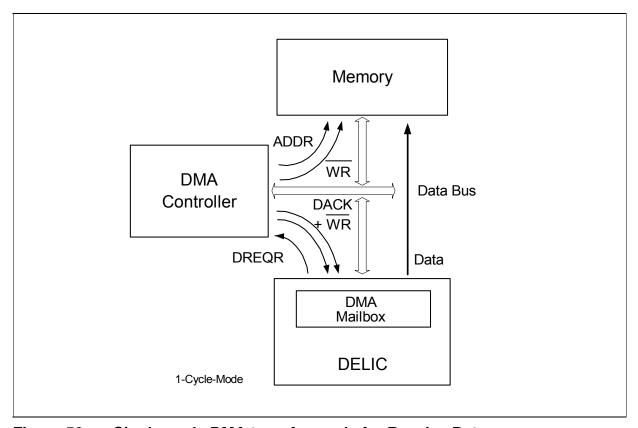

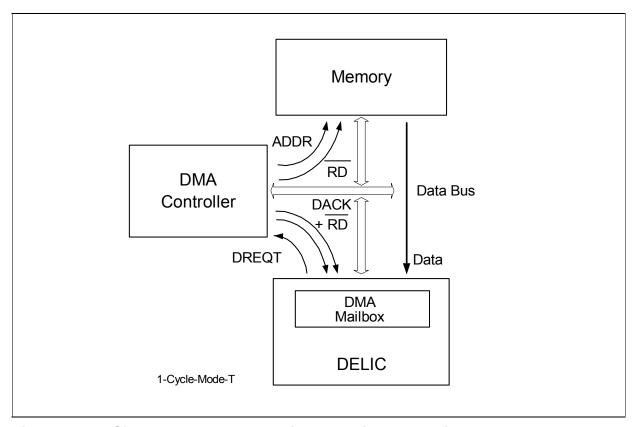

| Figure 52   | Two-cycle DMA Transfer Mode for Receive Direction                    | 134 |

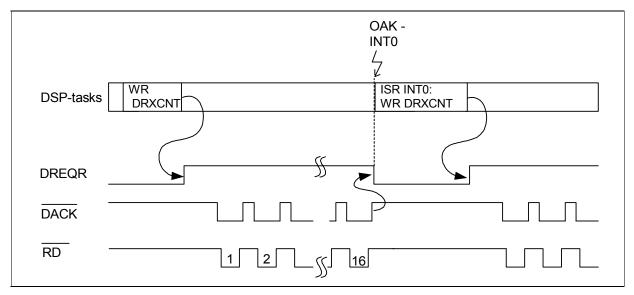

| Figure 53   | Single cycle DMA transfer mode for Receive Data                      | 135 |

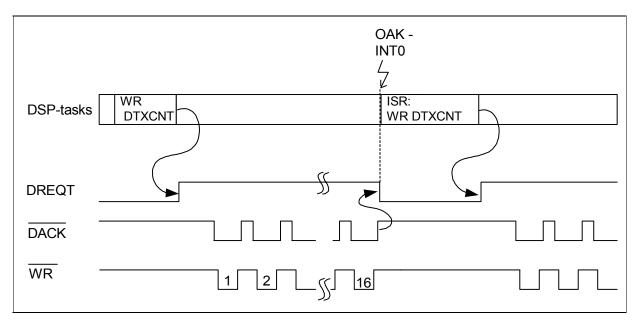

| Figure 54   | Single cycle DMA transfer mode for Transmit Data                     | 136 |

| Figure 55   | Timing in two-cycle DMA Mode for Transmit Direction and Infineon/In  | tel |

|             | Bus Type 138                                                         |     |

| Figure 56   | Timing in two-cycle DMA Mode for Receive Direction and Infineon/ Int | el  |

|             | Bus Type 140                                                         |     |

| Figure 57   | DELIC Clock Generator                                                | 143 |

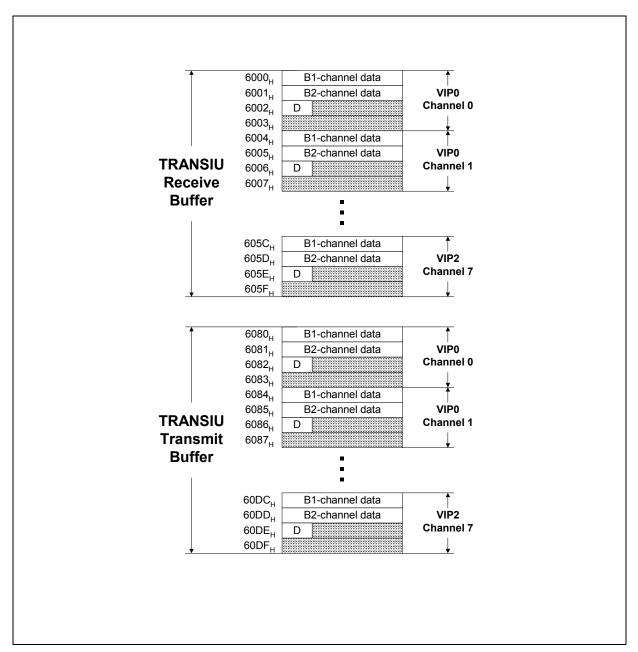

| Figure 58   | TRANSIU Buffer Addresses 1                                           | 149 |

| Figure 59   | DMA Write-Transaction Timing in Motorola Mode                        | 251 |

| Figure 60   | DMA Read-Transaction Timing in Motorola Mode                         | 252 |

| Figure 61   | DMA Write-Transaction Timing in Intel/Infineon Mode                  | 254 |

| Figure 62   | DMA Read-Transaction Timing in Intel/Infineon Mode                   | 254 |

| Figure 63   | Write Cycle Motorola Mode                                            | 256 |

| Figure 64   | Read Cycle Motorola Mode                                             | 257 |

| Figure 65   | Write Cycle Intel/Infineon Demultiplexed Mode                        |     |

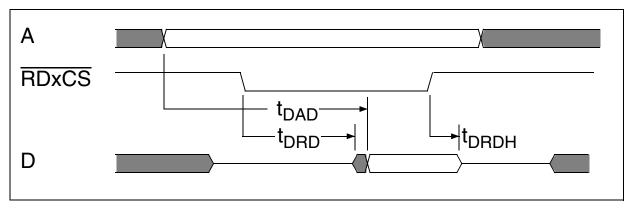

| Figure 66   | Read Cycle Intel/Infineon Demultiplexed Mode                         | 258 |

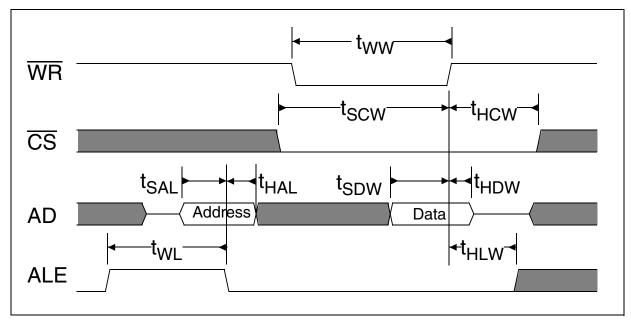

| Figure 67   | Write Cycle Intel/Infineon Multiplexed Mode                          |     |

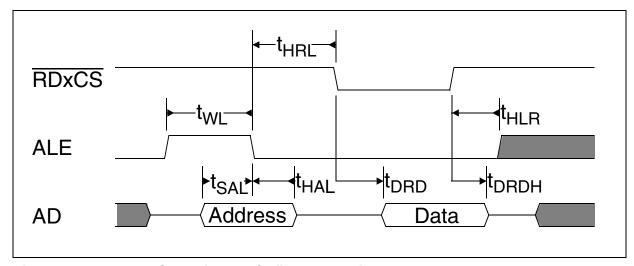

| Figure 68   | Read Cycle in Intel/Infineon Multiplexed Mode                        |     |

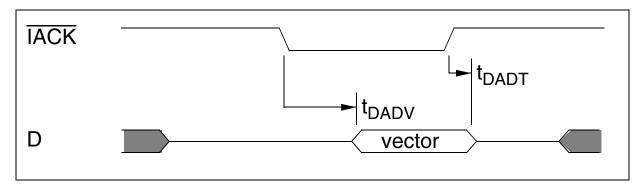

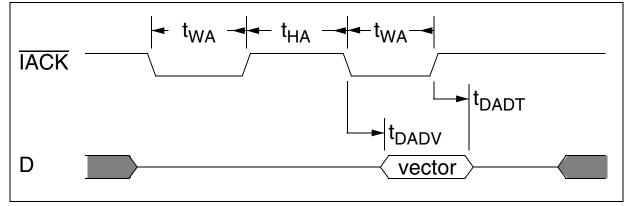

| Figure 69   | Interrupt Acknowledge Cycle Timing in Motorola Mode 2                |     |

| Figure 70   | Interrupt Acknowledge Cycle Timing in Intel/Infineon Mode 2          |     |

| Figure 71   | · · · · · · · · · · · · · · · · · · ·                                | 262 |

| Figure 72   | 9                                                                    | 263 |

| Figure 73   | 3                                                                    | 263 |

| Figure 74   | 3                                                                    | 264 |

| Figure 75   | <b>5</b>                                                             | 265 |

| Figure 76   | , ,                                                                  | 267 |

| Figure 77   |                                                                      | 267 |

| Figure 78   | 3                                                                    | 268 |

| Figure 79   |                                                                      | 269 |

| Figure 80   |                                                                      | 269 |

| Figure 81   | 9                                                                    | 271 |

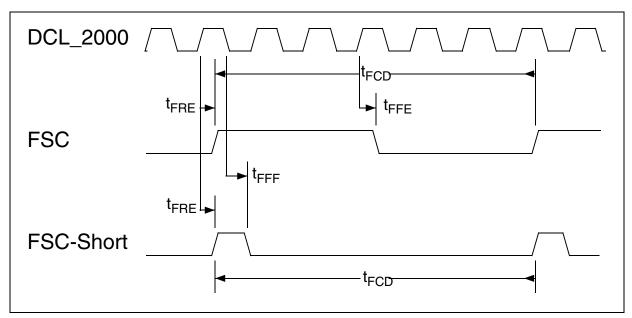

| Figure 82   | FSC Timing IOM-2000                                                  | 272 |

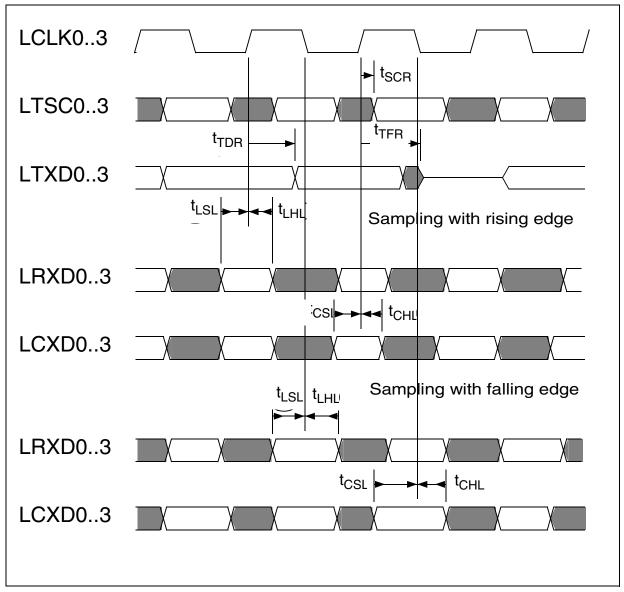

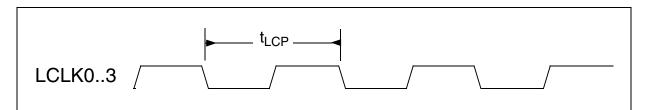

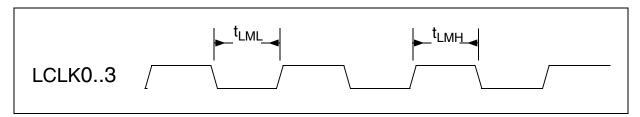

| LNC03 (Local Network Controller) Interface Timing         | 274                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCLK03 Timing in Output Mode                              | 275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LCLK03 Timing in Input Mode                               | 276                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Test-Interface (Boundary Scan) Timing                     | 278                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

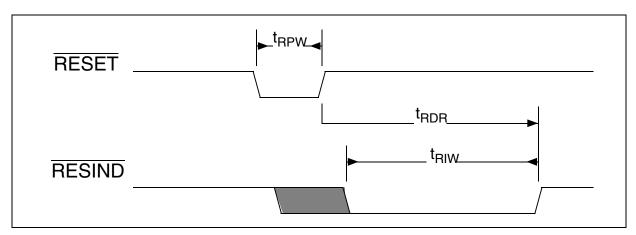

| Reset Indication Timing                                   | 279                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

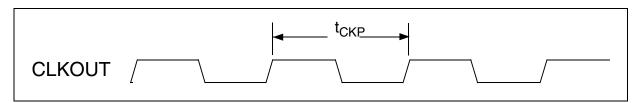

|                                                           | 279                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

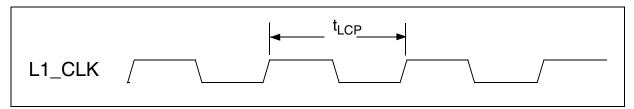

| L1_CLK Timing                                             | 280                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

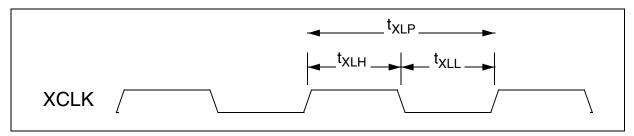

| XCLK Timing                                               | 280                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

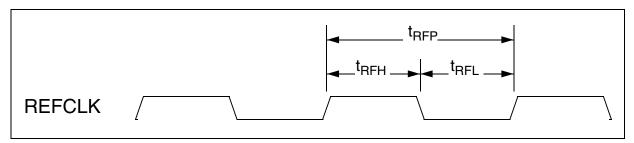

| REFCLK Timing                                             | 281                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DELIC Connection to Intel 80386EX (Demuxed Configuration) | 282                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DELIC Connection to Infineon C165 (Demuxed Configuration) | 283                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DELIC-LC PCM Unit Mode 0 (4 Ports with 2 MBit/s)          | 284                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Command/ Indication Handshake of General Mailbox          | 285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Behavior of Output Driver if Last Bit is '1'              | 286                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Behavior of Output Driver if Last Bit is '0'              | 286                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Guaranteed Reset Behaviour                                | 287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                           | LCLKO3 Timing in Input Mode  Test-Interface (Boundary Scan) Timing.  Reset Indication Timing.  CLOCKOUT Timing.  L1_CLK Timing.  XCLK Timing.  BEFCLK Timing.  DELIC Connection to Intel 80386EX (Demuxed Configuration)  DELIC Connection to Infineon C165 (Demuxed Configuration).  DELIC-LC PCM Unit Mode 0 (4 Ports with 2 MBit/s).  Command/ Indication Handshake of General Mailbox.  Behavior of Output Driver if Last Bit is '1'  Behavior of Output Driver if Last Bit is '0' |

| List of Tables | s Pag                                                                   | је             |

|----------------|-------------------------------------------------------------------------|----------------|

| Table 1        | IOM®-2 Interface Pins (DELIC-LC)                                        | 13             |

| Table 2        | IOM-2000 Interface / LNC Port 1 (DELIC-LC)                              |                |

| Table 3        | LNC Port 0 (DELIC-LC)                                                   |                |

| Table 4        |                                                                         | 16             |

| Table 5        |                                                                         | 18             |

| Table 6        | Clock Generator Pins (DELIC-LC) (additionally to IOM/PCM clocks) . 2    | 20             |

| Table 7        | Power Supply Pins (DELIC-LC)                                            | 21             |

| Table 8        | JTAG and Emulation Interface Pins (DELIC-LC)                            | 22             |

| Table 9        | Test Interface Pins (DELIC-LC)                                          | 23             |

| Table 10       | IOM®-2 Interface Pins (DELIC-PB)                                        | 25             |

| Table 11       | IOM-2000 Interface / LNC Port 1 (DELIC-PB)                              |                |

| Table 12       | LNC Port 0 (DELIC-PB)                                                   |                |

| Table 13       | Microprocessor Bus Interface Pins (DELIC-PB)                            | 28             |

| Table 14       |                                                                         | 31             |

| Table 15       | Clock Generator Pins (DELIC-PB) (Additionally to IOM/PCM Clocks). 3     | 34             |

| Table 16       | Power Supply Pins (DELIC-PB)                                            |                |

| Table 17       | JTAG and Emulation Interface Pins (DELIC-PB) 3                          | 36             |

| Table 18       | Test Interface Pins (DELIC-PB)                                          |                |

| Table 19       | Strap Pins (Evaluated During Reset)                                     | 38             |

| Table 20       | Control Bits in S/T Mode on DR Line                                     | 12             |

| Table 21       | Control Bits in S/T Mode on DX Line                                     | 12             |

| Table 22       | INFO Structure on UPN Interface                                         | 18             |

| Table 23       | UPN State Machine Codes                                                 | 52             |

| Table 24       | LT-S State Machine Codes                                                | 55             |

| Table 25       | LT-T Mode State Machine Codes (Conditional States)                      | 58             |

| Table 26       | TAP Controller Instruction Codes 6                                      | 37             |

| Table 27       | Differences Between DELIC-LC and DELIC-PB 6                             | 39             |

| Table 28       | D-Echo Bit                                                              | 37             |

| Table 29       | S/T Mode Multiframe Bit Positions 9                                     | <del>)</del> 2 |

| Table 30       | I-Buffer Logical Memory Mapping                                         | <del>)</del> 7 |

| Table 31       | D-Buffer Address Space                                                  | <del>)</del> 7 |

| Table 32       | DCL Frequency in Different IOM-2 Modes                                  | )()            |

| Table 33       | I-Buffer Logical Memory Mapping of Input Buffers 10                     | )6             |

| Table 34       | I-Buffer Logical Memory Mapping of Output Buffers                       | )6             |

| Table 35       | DSP Access to D-Buffer Input Blocks                                     | )6             |

| Table 36       | DSP Access to D-Buffer Output Blocks                                    | )7             |

| Table 37       | PCM TSC in 4 x 32 TS Mode (4 x 2 MBit/s)                                | )9             |

| Table 38       | PCM TSC in 2 x 64 TS Mode (2 x 4MBit/s)                                 | )9             |

| Table 39       | PCM TSC in 1 x 128 TS (1 x 8 MBit/s) and 1 x 256 TS (1 x 16 MBit/s) (1s | st             |

|                | Half) Mode 110                                                          |                |

| Table 40       | PCM TSC in 1 x 256 TS (1 x 16 MBit/s) (2nd Half) Mode 11                |                |

| Table 41       | GHDLCU Receive Buffer Configuration                                     | 23             |

| List of Table | s P                                                              | age  |

|---------------|------------------------------------------------------------------|------|

| Table 42      | Interrupt Map                                                    | 127  |

| Table 43      | Overview of Clock Signals                                        | 142  |

| Table 44      | DSP Registers Address Space                                      | 146  |

| Table 45      | DSP Program Address Space                                        | 146  |

| Table 46      | Occupied DSP Data Address Space                                  | 147  |

| Table 47      | OAK Memory Mapped Registers Address Space                        | 148  |

| Table 48      | μP Address Space Table                                           | 150  |

| Table 49      | TRANSIU Register Map                                             | 151  |

| Table 50      | Scrambler Register Map                                           | 152  |

| Table 51      | IOMU Register Map                                                | 152  |

| Table 52      | PCMU Register Map                                                | 152  |

| Table 53      | A-/μ-Law Unit Register Map                                       | 153  |

| Table 54      | HDLCU Register Map                                               | 154  |

| Table 55      | GHDLC Register Map                                               | 154  |

| Table 56      | DCU Register Map                                                 | 155  |

| Table 57      | μP Configuration Register Map                                    | 155  |

| Table 58      | General Mailbox Register Map                                     | 156  |

| Table 59      | DMA Mailbox Register Map                                         |      |

| Table 60      | Clock Generator Register Map                                     |      |

| Table 61      | Available ISDN Modes for Each VIP Channel                        | 162  |

| Table 62      | Tristate Control Assignment for IOM-2 Time Slots                 | 180  |

| Table 63      | R/W Behavior During DMA Transactions in Normal and in Fly-By Mo- | de . |

|               | 249                                                              |      |

| Table 64      | DMA Transaction timing in Motorola Mode                          | 250  |

| Table 65      | R/W Behavior During DMA Transactions in Normal and in Fly-By Mo  | des. |

|               | 253                                                              |      |

| Table 66      | DMA Transaction Timing in Intel/Infineon Mode                    | 253  |

| Table 67      | Timing for Write Cycle in Motorola Mode                          | 255  |

| Table 68      | Timing for Read Cycle In Motorola Mode                           | 256  |

| Table 69      | Timing for Write Cycle in Intel/Infineon Demultiplexed Mode      | 257  |

| Table 70      | Timing For Read Cycle in Intel/Infineon Demultiplexed Mode       | 258  |

| Table 71      | Timing for Write Cycle in Intel/Infineon Multiplexed Mode        | 259  |

| Table 72      | Timing For Read Cycle in Intel/Infineon Multiplexed Mode         | 260  |

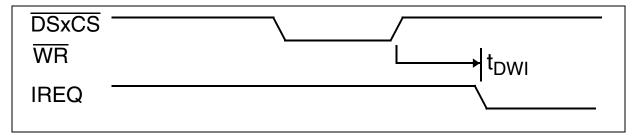

| Table 73      | Interrupt Acknowledge Cycle Timing                               |      |

| Table 74      | IOM-2 Interface Timing                                           |      |

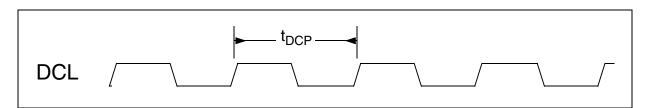

| Table 75      | DCL (IOM-2 Data Clock) Timing                                    |      |

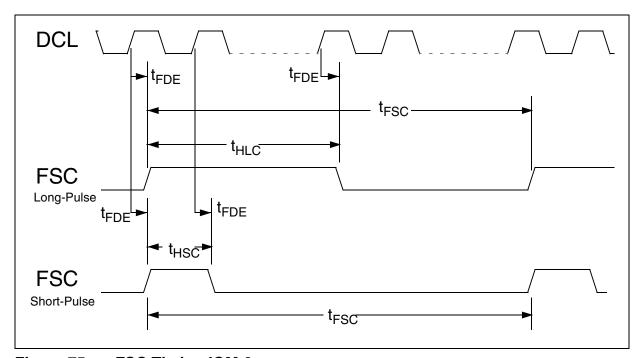

| Table 76      | FSC (IOM-2 and IOM-2000 Frame-Sync) Timing                       | 264  |

| Table 77      |                                                                  |      |

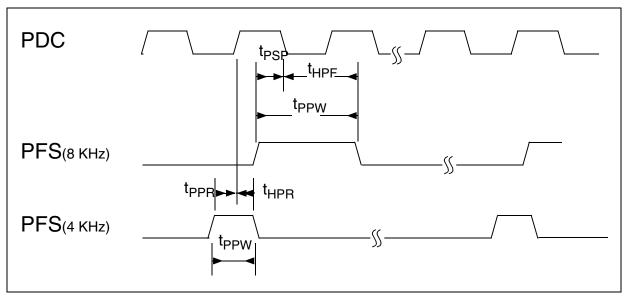

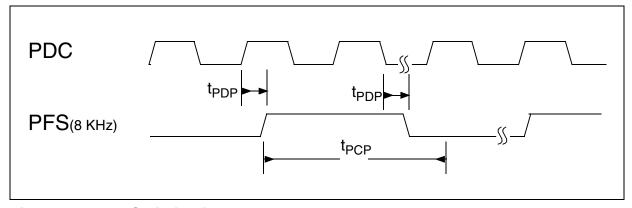

| Table 78      | , , ,                                                            |      |

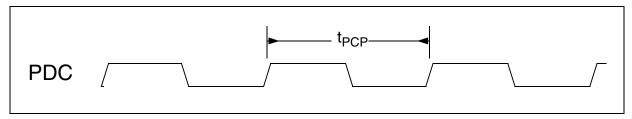

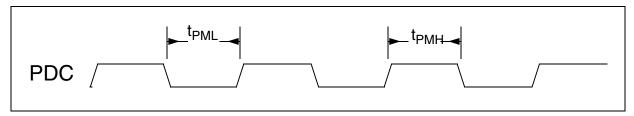

| Table 79      | PDC Timing in Input Mode                                         |      |

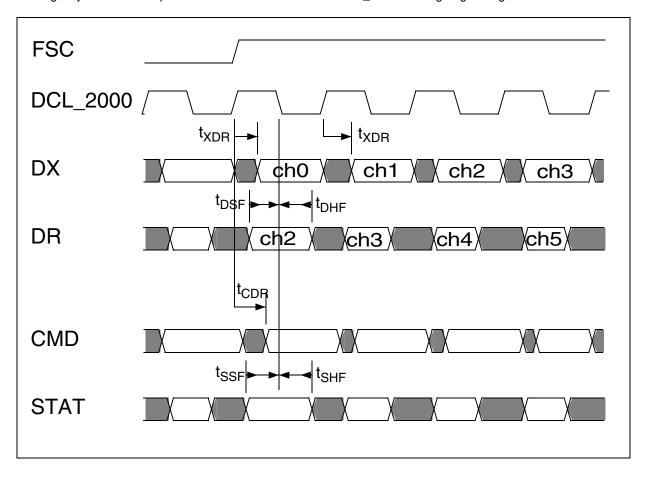

| Table 80      | IOM-2000 Interface Timing                                        |      |

| Table 81      | DCL_2000 (IOM-2000 Data Clock) Timing                            | 272  |

| List of Table | s                                          | Page  |

|---------------|--------------------------------------------|-------|

| Table 82      | LNC03 Interface Timing                     | . 273 |

| Table 83      | LCLK03 Timing in Output Mode               | . 275 |

| Table 84      | LCLK03 Timing in Input Mode                | . 275 |

| Table 85      | CLK_DSP Input Clock Timing                 | . 276 |

| Table 86      | Test Interface Timing                      | . 277 |

| Table 87      | Reset and RESIND (Reset Indication) timing | . 278 |

| Table 88      | CLOCKOUT Timing                            | . 279 |

| Table 89      | L1_CLK Timing                              | . 279 |

| Table 90      | XCLK Timing                                | . 280 |

| Table 91      | REFCLK Timing                              | . 281 |

#### **Preface**

This document provides reference information on the DELIC-LC/-PB Version 3.1.

#### **Organization of this Document**

This Data Sheet is divided into 11 chapters and appendices. It is organized as follows:

- Chapter 1 Introduction

- Gives a general description of the product and its family, lists the key features, and presents some typical applications.

- Chapter 2 Pin Description

- Lists pin locations with associated signals, categorizes signals according to function, and describes signals.

- Chapter 3 Interface Description

- Describes the DELIC external interfaces.

- Chapter 4 Functional Description

- Describes the features of the main functional blocks.

- Chapter 5 DELIC Memory Structure

- Containes the memory organisation of the OakDSPCore®.

- Chapter 6 Register Description

- Containes the detailed register description.

- Chapter 7 Package Outlines

- Chapter 8 Electrical Characteristics and Timing Diagrams

- Containes the DC specification.

- Contains the AC specification.

- Chapter 9 Application Hints

- Provides e.g. a worksheet

- Chapter 10 Glossary

- Chapter 11 Index

#### **Your Comments**

We welcome your comments on this document as we are continuously aiming at improving our documentation. Please send your remarks and suggestions by e-mail to sc.docu\_comments@infineon.com

Please provide in the subject of your e-mail:

device name (DELIC-LC/-PB), device number (PEB 20570/PEB 20571), device version (Version 3.1), or and in the body of your e-mail:

document type (Data Sheet), issue date (2003-07-31) and document revision number (DS 2.1).

#### 1 Introduction

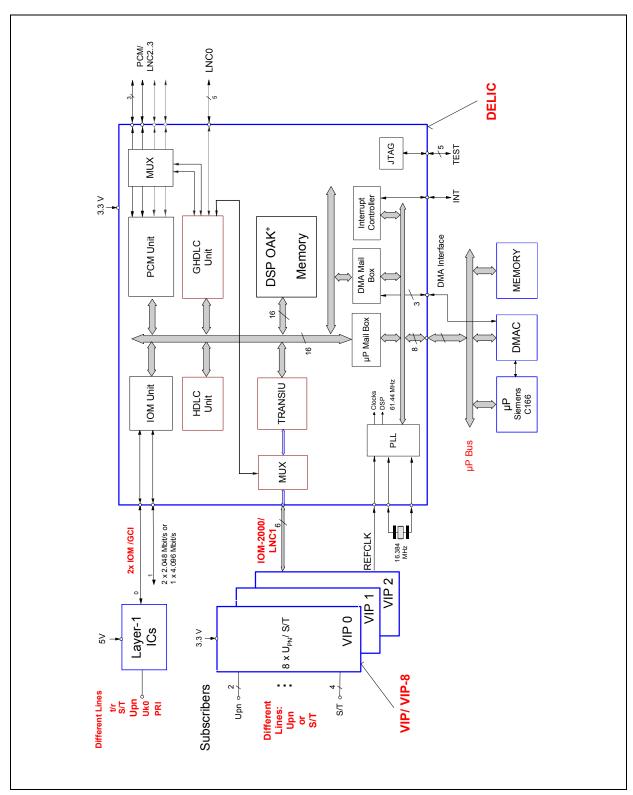

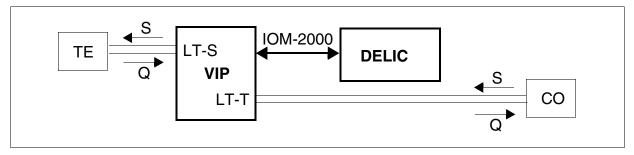

The DELIC and VIP chipset realizes multiple ISDN S/T and  $U_{PN}$  interfaces together with controller functionality typically needed in PBX or Central Office systems. This functionality comprises voice channel handling, signaling control, layer-1 control, and even signal processing tasks.

Moreover it provides a programmable master/slave clock generator with 2 PLLs, an universal  $\mu P$  interface and a DMA interface.

The controller part, **DELIC**, is available in two different versions:

- DELIC-LC (PEB 20570) is a line card controller providing voice channel switching, multiple HDLC and layer-1 control for up to three VIPs (24 ISDN channels). Other transceiver ICs (32 analog or 16 digital channels) may additionally be connected via IOM-2/GCI interface.

- DELIC-PB (PEB 20571) additionally provides a programmable telecom DSP including program and data RAM. This DSP can be used for layer-1 control, protocol support and signal processing. The flexibility gained by the programmability allows Infineon to offer different application specific solutions with the same silicon just by software configuration.

A configuration tool assists the user in finding a valid system configuration. Even more customer specific DSP-routines can be integrated with the assistance of Infineon.

The transceiver part, **VIP**, is available in two different versions:

VIP PEB 20590 is the first (8 channel) ISDN transceiver that implements multiple U<sub>PN</sub> and S/T interfaces within one device. The user can decide by programming in which mode a desired channel shall work.

A total of 8 channels are provided for layer-1 subscriber or trunk line characteristic. The VIP is programmed by the DELIC via the IOM-2000 interface. VIP's eight channels are programmable in the following maximum partitioning between  $U_{PN}$  and S/T channels:

|          | Max. number of U <sub>PN</sub> and S/T Channels |   |   |   |   |  |  |

|----------|-------------------------------------------------|---|---|---|---|--|--|

| $U_{PN}$ | 8                                               | 7 | 6 | 5 | 4 |  |  |

| S/T      | 0                                               | 1 | 2 | 3 | 4 |  |  |

VIP-8 PEB 20591 Additionally to the features of the VIP, the VIP-8 allows any combination of U<sub>PN</sub> S/T interface (i.e. each of the 8 channels may be programmed to S/T or U<sub>PN</sub> mode)

### **Block diagrams:**

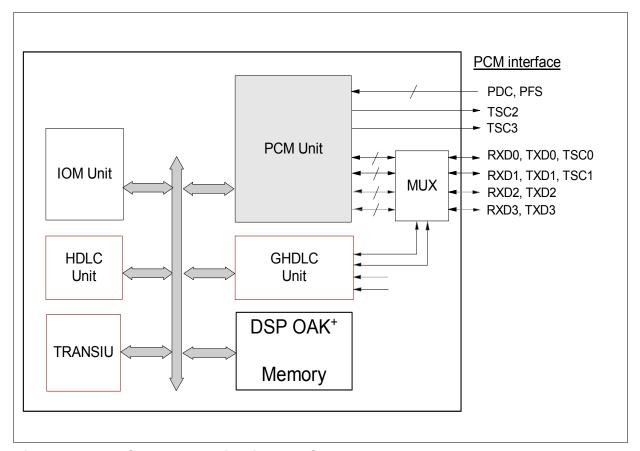

Figure 1 Block Diagram of the DELIC-LC

Figure 2 Block Diagram of the DELIC-PB

# DSP Embedded Line and Port Interface Controller DELIC-LC DELIC-PB

PEB 20570

PEB 20571

Version 3.1 CMOS

#### 1.1 DELIC-LC Key Features

DELIC-LC is optimized for line card applications:

- One IOM-2000 interface supporting three VIPs i.e. up to 24 ISDN channels

- Two IOM-2 (GCI) ports (configurable as PCM ports) supporting up to 16 ISDN channels or 32 analog subscribers

- Switching matrix 256 x 256 TS (8-bit switching)

- 24 HDLC controllers assignable to any D- or B-channel (at 16 kbit/s or 64 kbit/s)

- Serial communication controller: high-speed signaling channel for 2.048 Mbit/s

- General purpose I/O ports

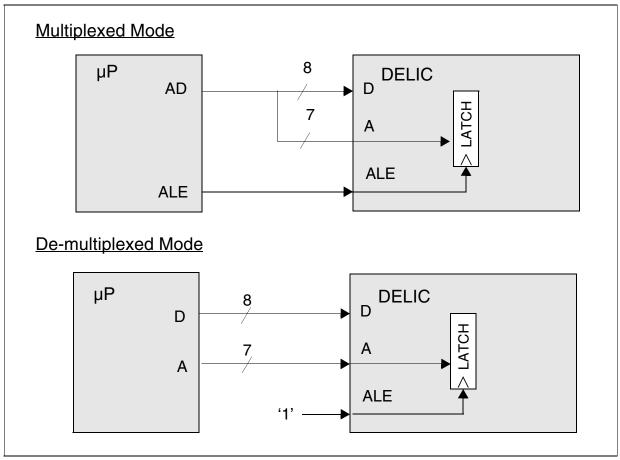

- Standard multiplexed and de-multiplexed µP interface: Infineon, Intel, Motorola

- Programmable PLL based Master/Slave clock generator, providing all system clocks from a single 16.384 MHz crystal source

- JTAG compliant test interface

- single 3.3 V power supply, 5 V tolerant inputs

# 1.2 DELIC-PB Key Features

Compared to the DELIC-LC, having a fixed functionality, the DELIC-PB provides a high degree of flexibility (in terms of selected number of ports or channels).

Additionally it features computing power for typical DSP-oriented PBX tasks like conferencing, DTMF etc.

A Microsoft Windows based configuration tool, the Configurator, enables to generate an application specific functionality. Its features are mainly determined by the firmware of the integrated telecom DSP.

| Туре                 | Package      |

|----------------------|--------------|

| PEB 20571/ PEB 20570 | P-TQFP-100-3 |

#### List of maximum available features:

- One IOM-2000 interface supporting up to three VIPs i.e. up to 24 ISDN channels

- Support of DASL mode

- Up to two IOM-2 (GCI) ports (also configurable as PCM ports) supporting up to 16 ISDN channels or 32 analog subscribers

- Up to four PCM ports with up to 4 x 2.048 Mbit/s (4 x 32 TS) or 2 x 4.096 Mbit/s or 1 x 8.192 Mbit/s

- Switching matrix 256 x 256 TS (switching of 4-/8- bit time slots)

- Up to 32 HDLC controllers assignable to any D- or B-channel (at 16 kbit/s or 64 kbit/s)

- Up to 4 serial communication controllers: one of them with up to 8.192 Mbit/s data rate

- General purpose I/O ports

- DECT synchronization support

- Standard multiplexed and de-multiplexed μP interface: Infineon, Intel, Motorola

- Dedicated DMA support mailbox for 2 DMA-channels

- Integrated DSP core OAK+ (60 MIPS for layer 1 control, signalling and DSP-algorithms)

- 4 kWord on-chip program memory

- 2 kWord on-chip data memory

- 2 kWord ROM

- DSP work load measurement for run-time statistics, DSP alive indication

- On chip debugging unit

- Serial DSP program debugging interface connected via JTAG port

- A-/µ-law conversion unit

- Programmable PLL based Master/Slave clock generator, providing all system clocks from a single 16.384 MHz crystal source

- JTAG compliant test interface

- single 3.3 V power supply, 5 V compatible inputs

Note: As each feature consumes system resources (DSP-MIPS, memory, port pins), the maximum available number of supported interfaces or HDLC channels is limited by the totally available resources. A System Configurator tool (see DELIC Software User's Manual) helps to determine a valid configuration.

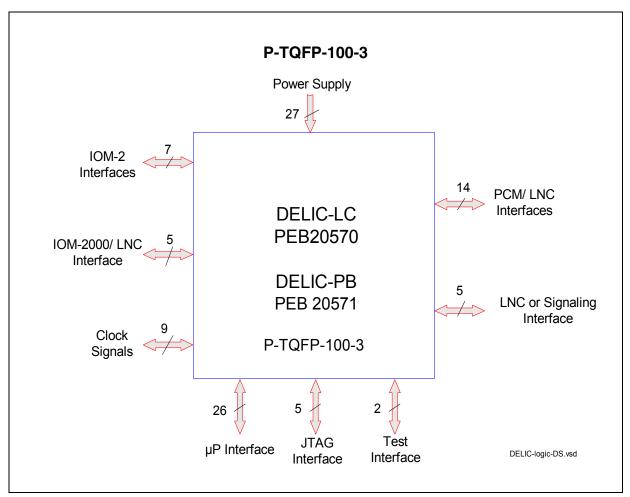

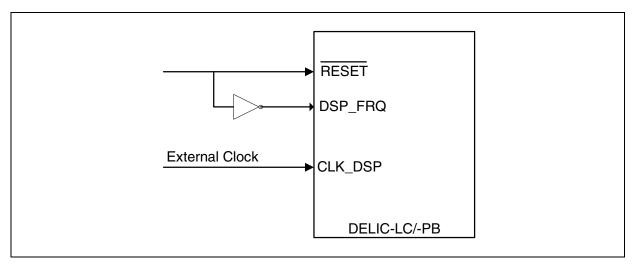

# 1.3 Logic Symbol

Figure 3 Logic Symbol

# 1.4 Typical Applications

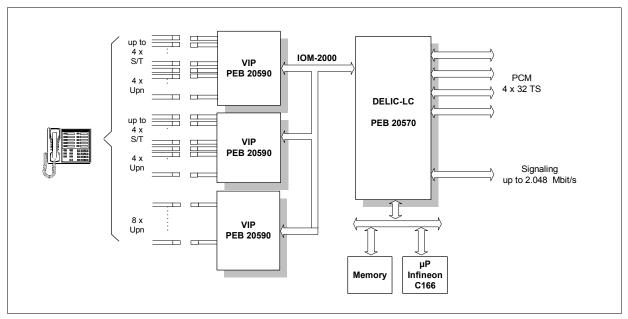

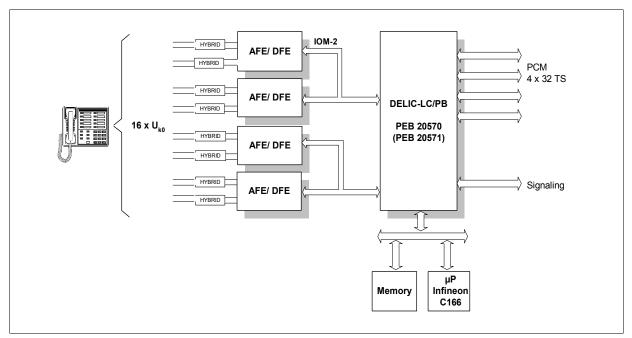

# 1.4.1 Applications for DELIC-LC

The following two figures show example configurations of DELIC-LC Line card applications for different ISDN interface standards.

In Figure 4, three VIP transceiver ICs are connected to the DELIC-LC via the IOM-2000 interface, whereas in Figure 5 and Figure 6 an IOM-2 (GCI) interface is used to connect other ISDN transceivers.

Figure 4 DELIC-LC in S/T and  $U_{PN}$  Line Cards (up to 8 S/T and 16  $U_{PN}$ )

Figure 5 DELIC-LC/PB in Uk0 Line Card for 16 Subscribers

Note: In this application DELIC-PB is also meaningful.

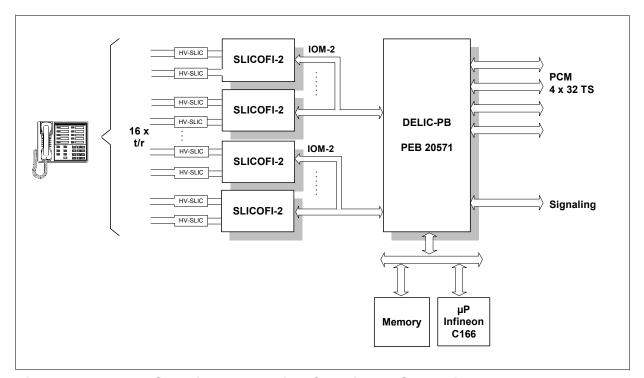

# 1.4.2 Applications for DELIC-PB

Figure 6 DELIC-PB in Analog Line Card for 16 Subscribers

Figure 7 DELIC-PB in Small PBX

Figure 8 DELIC-PB in 4 Port SDSL Line Card

# 2 Pin Description

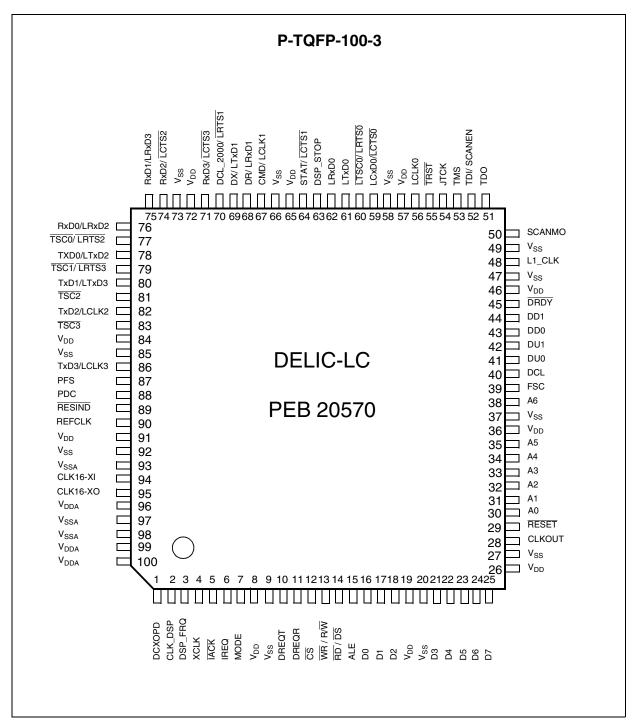

### 2.1 Pin Diagram DELIC-LC

(top view)

Figure 9 Pin Configuration DELIC-LC

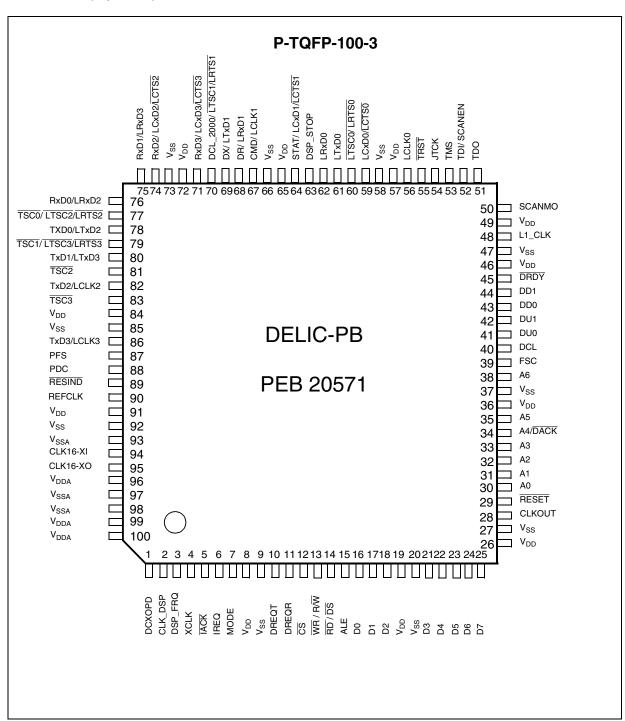

#### 2.2 Pin Diagram DELIC-PB

(top view)

Figure 10 Pin Configuration DELIC-PB

#### 2.3 Pin Definitions and Functions for DELIC-LC

Note: The column "During Reset" refers to the time period that starts with activation of RESET input and ends with the deactivation of the RESIND output. During this period, the DELIC strap pins (refer to Table 19) may be driven by external pull-down or pull-up resistors to define DELIC configuration. If external pull-down or pull-up resistors are not connected to the strap pins, the value of each strap pin during reset will be determined by an internal pull-up or pull-down resistor, according to the default strap value of each pin.

The user must ensure that connected circuits do not influence the sampling of the strap pins during reset.

The column "After Reset" describes the behavior of every pin, from the deactivation of the RESIND output until the DELIC registers are programmed.

Note: In order to garantee the reset behaviour of every pin please refer to the application hint "Reset Behaviour" on Page 287.

# Table 1 IOM®-2 Interface Pins (DELIC-LC)

| Pin<br>No. | Symbol | In (I)<br>Out(O) | During<br>Reset                                           | After<br>Reset | Function                                                                                                                                                                                                                   |

|------------|--------|------------------|-----------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39         | FSC    | 0                | 0                                                         | 0              | Frame Synchronization Clock (8 kHz) Used for both the IOM-2 and the IOM- 2000 interface                                                                                                                                    |

| 40         | DCL    | 0                | TEST-<br>Strap (3),<br>(pull-up),<br>refer to<br>Table 19 | 0              | IOM-2 Data Clock 2.048 MHz or 4.096 MHz                                                                                                                                                                                    |

| 43         | DD0    | O(OD)            | High Z                                                    | High Z         | Data Downstream IOM-2 Interface<br>Channel0                                                                                                                                                                                |

| 44         | DD1    | O(OD)            | High Z                                                    | High Z         | Data Downstream IOM-2 Interface<br>Channel1                                                                                                                                                                                |

| 41         | DU0    | 1                | I                                                         | I              | Data Upstream IOM-2 Interface<br>Channel 0                                                                                                                                                                                 |

| 42         | DU1    | I                | I                                                         | I              | Data Upstream IOM-2 Interface<br>Channel 1                                                                                                                                                                                 |

| 45         | DRDY   | I                |                                                           | I              | D- Channel Ready Stop/Go information for D-channel control on S/T interface in LT-T. Affects only IOM-2 port 0.  DRDY = 1 means GO  DRDY = 0 means STOP  If DRDY is not used, this pin has to be connected to 'High' level |

# Table 2 IOM-2000 Interface / LNC Port 1 (DELIC-LC)

| Pin<br>No. | Symbol     | In (I)<br>Out (O) | During<br>Reset | After<br>Reset | Function                                                                                                                            |

|------------|------------|-------------------|-----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 70         | DCL_2000 / | 0                 | 0               | 0              | IOM-2000 Data Clock<br>3.072, 6.144 or 12.288 MHz                                                                                   |

|            | LRTS1      | 0                 |                 |                | 'request-to-send' functionality (Async mode)                                                                                        |

| 69         | DX /       | 0                 | High Z          | High Z         | Data Transmit Transmits IOM-2000 data to VIP                                                                                        |

|            | LTxD1      | O (OD)            |                 |                | LNC Transmit Serial Data Port 1 (Async mode).                                                                                       |

| 68         | DR/        | I                 | I               | I              | Data Receive<br>Receives IOM-2000 data from VIP                                                                                     |

|            | LRxD1      | Ī                 |                 |                | LNC Receive Serial Data Port 1 (Async mode).                                                                                        |

| 67         | CMD /      | 0                 | High Z          | High Z         | IOM-2000 Command Transmits DELIC commands to VIP.                                                                                   |

|            | LCLK1      | I/O               |                 |                | LNC Clock Port 1. When configured as output may be driven at the following frequencies: 2.048 MHz, 4.096 MHz, 8.192 MHz, 16.384 MHz |

| 64         | STAT /     | I                 | I               | I              | IOM-2000 Status<br>Receives status information from VIP.                                                                            |

|            | LCTS1      | I                 |                 |                | LNC1 Clear to Send 'clear-to-send' functionality (Async mode)                                                                       |

Table 3 LNC Port 0 (DELIC-LC)

| Pin<br>No. | Symbol           | In (I)<br>Out (O) | During<br>Reset                                             | After<br>Reset | Function                                                                                                                                                                                                              |

|------------|------------------|-------------------|-------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 62         | LRxD0            | I                 | I                                                           | I              | LNC Receive Serial Data Port 0 (HDLC and Async mode).                                                                                                                                                                 |

| 61         | LTxD0            | O (OD)            | High Z                                                      | High Z         | LNC Transmit Serial Data Port 0 (HDLC and Async mode).                                                                                                                                                                |

| 60         | LTSC0 /<br>LRTS0 | 0                 | PLL-<br>Bypass"<br>strap.<br>Pull-up<br>refer to<br>Page 38 | H              | 2 modes per S/W selectable: 1) TxD output is valid (HDLC mode). Supplies a control signal for an external driver. ('low' when the corresponding TxD-output is valid). 2) 'request-to-send' functionality (Async mode) |

| 59         | LCxD0 /<br>LCTS0 | l                 | I                                                           | I              | LNC0 Collision Data / Clear to Send  2 modes per S/W selectable: 1) Collision Data (HDLC Mode). 2) 'clear-to-send' functionality (Async mode)                                                                         |

| 56         | LCLK0            | I/O               | I                                                           | I              | LNC Clock Port 0 When configured as output may be driven at the following frequencies: 2.048 MHz, 4.096 MHz, 8.192 MHz, 16.384 MHz                                                                                    |

Table 4 Microprocessor Bus Interface Pins (DELIC-LC)

|                                              | idble 4 Microprocessor bus interface i ins (DELIO-LO) |                                                                                                          |                                                                          |                |                                                                                                                                                                      |  |  |  |

|----------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin<br>No.                                   | Symbol                                                | In (I)<br>Out (O)                                                                                        | During<br>Reset                                                          | After<br>Reset | Function                                                                                                                                                             |  |  |  |

| 25<br>24<br>23<br>22<br>21<br>18<br>17<br>16 | D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0          | I/O The direction of these pins depends on the value of the following pins: CS, RD/DS, WR / R/W and MODE |                                                                          |                | Data Bus When operated in address/data multiplex mode, this bus is used as a multiplexed AD bus. The Address pins are externally connected to the AD bus.            |  |  |  |

| 38<br>35<br>34<br>33<br>32<br>31<br>30       | A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0                | I                                                                                                        | l                                                                        | I              | Address Bus (bits 6 0) When operated in address/data multiplex mode, this bus is used as a multiplexed AD bus. The Data pins are externally connected to the AD bus. |  |  |  |

| 11                                           | DREQR                                                 | 0                                                                                                        | CLOCK<br>MASTER<br>Strap (pull-<br>down),<br>refer to<br>Table 19        | L              | Strap pin                                                                                                                                                            |  |  |  |

| 10                                           | DREQT                                                 | 0                                                                                                        | EMUL-<br>ATION<br>BOOT<br>Strap (pull-<br>down),<br>refer to<br>Table 19 | L              | Strap pin                                                                                                                                                            |  |  |  |

| 12                                           | CS                                                    | I                                                                                                        | I                                                                        | I              | Chip Select A "low" on this line selects all registers for read/write operations.                                                                                    |  |  |  |

| 13                                           | WR/                                                   | I                                                                                                        | I                                                                        | I              | Write (Intel/Infineon Mode) Indicates a write access.  Read/Write (Motorola Mode) Indicates the direction of the data transfer                                       |  |  |  |

Table 4 Microprocessor Bus Interface Pins (DELIC-LC) (cont'd)

| Pin<br>No. | Symbol | In (I)<br>Out (O) | During<br>Reset | After<br>Reset | Function                                                                                                                                                                                                                                                                |

|------------|--------|-------------------|-----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14         | RD/    | I                 | I               | I              | Read (Intel/Infineon Mode) Indicates a read access.  Data Strobe (Motorola Mode) During a read cycle, DS indicates that the DELIC should place valid data on the bus. During a write access, DS indicates that valid data is on the bus.                                |

| 15         | ALE    | I                 | I               | I              | Address Latch Enable Controls the on-chip address latch in multiplexed bus mode. While ALE is 'high', the latch is transparent. The falling edge latches the current address. ALE is also evaluated to determine the bus mode ('low'=multiplexed, 'high'=demultiplexed) |

| 7          | MODE   | I                 | I               | I              | Bus Mode Selection<br>Selects the µP bus mode<br>('low'=Intel/Infineon, 'high'=Motorola)                                                                                                                                                                                |

| 6          | IREQ   | O<br>(OD)         | High Z<br>(OD)  | High Z<br>(OD) | Interrupt Request is programmable to push/pull (active high or low) or opendrain. This signal is activated when the DELIC requests a µP interrupt. When operated in open drain mode, multiple interrupt sources may be connected.                                       |

| 5          | ĪACK   | I                 | I               | I              | Interrupt Acknowledge                                                                                                                                                                                                                                                   |

| 29         | RESET  | I                 | I               | I              | System Reset DELIC is forced to go into reset state.                                                                                                                                                                                                                    |