Wired Communications

Never stop thinking.

Edition 2001-10-31

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 31. 10. 01. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# QIHPC QUAD ISDN/S(H)DSL High Voltage Power Controller

PEF 2426 Version 1.1

Wired Communications

# PEF 2426 Revision History: 2001-10-31 DS 1 Previous Version: 06.99 (Preliminary Data Sheet DS 1) Page Subjects (major changes since last revision) 6 feature-comparison IEPC vs. QIHPC for S-feeding 17 Updated proposal for the protection circuitry 22 Table 5 Item 5

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

# **PEF 2426**

| Table of                             | Contents                                                                                                                                              | Page                 |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4        | Overview Features Logic Symbol Typical Applications S/T-Feeding                                                                                       | 2<br>3               |

| <b>2</b><br>2.1<br>2.2               | Pin Descriptions         Pin Configuration         (top view)          Pin Definitions and Functions                                                  | 7                    |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Functional Description Functional Block Diagram Biasing Circuit Line Feed Control Circuit Line Current Control Circuit Relays Driver Circuit          | 10<br>11<br>12<br>13 |

| <b>4</b> 4.1 4.2 4.3 4.4             | Application Hints Resistor RS14 Resistor RF Capacitor CS14 Protection Circuitry                                                                       | 15<br>15<br>15       |

| 5                                    | Operational Description                                                                                                                               | 18                   |

| 6<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5 | Electrical Characteristics Absolute Maximum Ratings AC/DC-Characteristics Operating Range Static Thermal Resistance Testing the Electrical Parameters | 20<br>21<br>21       |

| 7                                    | Package Outlines                                                                                                                                      | 27                   |

# **PEF 2426**

| List of Figu | ires                                                              | Page  |

|--------------|-------------------------------------------------------------------|-------|

| Figure 1     | Logic Symbol                                                      | 3     |

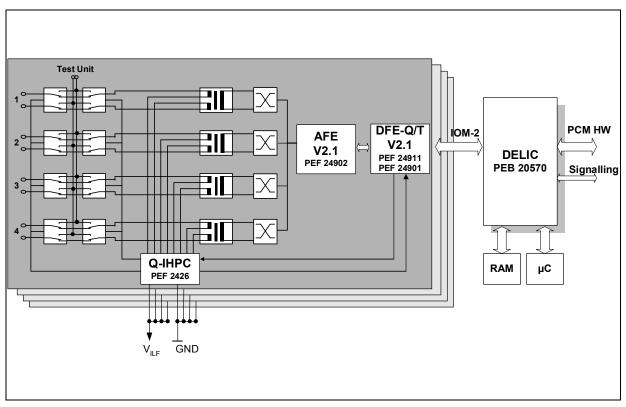

| Figure 2     | 16-Line Card Application with DELIC, DFE-Q/T and AFE              | 4     |

| Figure 3     | System integration                                                | 5     |

| Figure 4     | Pin Configuration                                                 | 7     |

| Figure 5     | Functional Block Diagram                                          | 10    |

| Figure 6     | Delay time tOC as a function of the value of CS14 (typical values | s) 16 |

| Figure 7     | Proposal for a Protection Circuitry                               | 17    |

| Figure 8     | Circuit with "LT Power Source Test Loads"                         | 18    |

| Figure 9     | Simultaneous Power Up Sequence                                    | 19    |

| Figure 10    | Supply Currents                                                   | 23    |

| Figure 11    | Line Currents and Delay Time tOC                                  | 24    |

| Figure 12    | DMOS-RON resistance                                               | 24    |

| Figure 13    | PF14, Logic Input Levels and NACK14, Logic Output Levels          | 25    |

| Figure 14    | RDin18, Relay Driver Inputs and RDout18 Relay Driver Outputs      | s 26  |

| Figure 15    | Test circuit for maximum DC-voltages, pulse voltages and impulse  | Э     |

|              | voltages on pins D14                                              | 26    |

Data Sheet 2001-10-31

# **PEF 2426**

| List of Tables | S .                                               | Page | е |

|----------------|---------------------------------------------------|------|---|

| Table 1        | Comparing the Power Feeeding IC's: IEPC vs. QIHPC | 6    | 6 |

| Table 2        | Pin Definitions and Functions                     | 8    | 8 |

| Table 3        | Thermal Detector Threshold Levels                 | 1    | 1 |

| Table 4        | Function Table for Controlling One Line           | 10   | 3 |

| Table 5        | DC Characteristics                                | 22   | 2 |

Data Sheet 2001-10-31

#### 1 Overview

The QUAD ISDN/S(H)DSL High Voltage Power Controller provides a power source for up to four U-line interfaces or S-interfaces. The power source to the device is a local battery or a centralized power supply.

Each powered line is individually controlled and monitored by the device interface. Line powering can be switched on or off by command. The QIHPC indicates, when the output current is above a threshold for longer than the programmable time  $t_{\rm OC}$ . At a second (higher) value the current is limited. The values of the current limitation and the overcurrent indication threshold are defined with external resistors, the overcurrent indication setup delay is selected by external capacitances.

The status information of each line (acknowledge of requested power feed) is returned to the system. The status information enables an easy detection of overloads and faults and a fast localization even on a large system.

The integrated intelligent chip temperature control guards the QIHPC in case of overloads.

Additionally eight drivers for external relays and their control logic are integrated on the QIHPC. These relay drivers provide open collector output stages with high current capability.

# QUAD ISDN/S(H)DSL High Voltage Power Controller QIHPC

**PEF 2426**

Version 1.1 SPT 170

#### 1.1 Features

- Supplies power for up to four ISDN or S(H)DSL transmission lines on Central Office and DSLAM Linecards

- ETSI TS 102 080 compatible

- TS 101 524 and ITU-T G.991.2 Annex B compatible

- Feediing of multiple S/T interfaces in IADs and PBXs.

- Line Feed Supply Voltage up to 130 V

- Separate Current Monitoring and Limiting for each line

- Current Limiting Level can be programmed by an external resistor

- Overcurrent indication threshold can be programmed with external resistors independently from the current limitation.

- The overcurrent indication setup delay can be programmed by external capacitors, separately for each line

- Intelligent Chip Temperature Control

- Automatically switching off lines in current limitation when expecting over temperature problems

- Automatically switching off all four lines in case of real overtemperature

- Integrated Relay Drivers and Relay Driver Controlling for eight relays

- Optimized for working in conjunction with PEB/F 24901 (DFE-T) and PEB/F 24911 (DFE-Q).

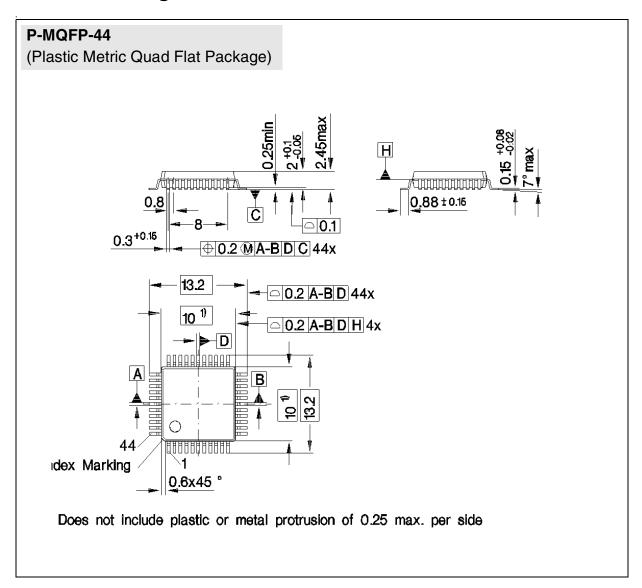

- Small P-MQFP-44 Package

- Reliable 170 V Smart Power Technology

| Туре     | Package   |

|----------|-----------|

| PEF 2426 | P-MQFP-44 |

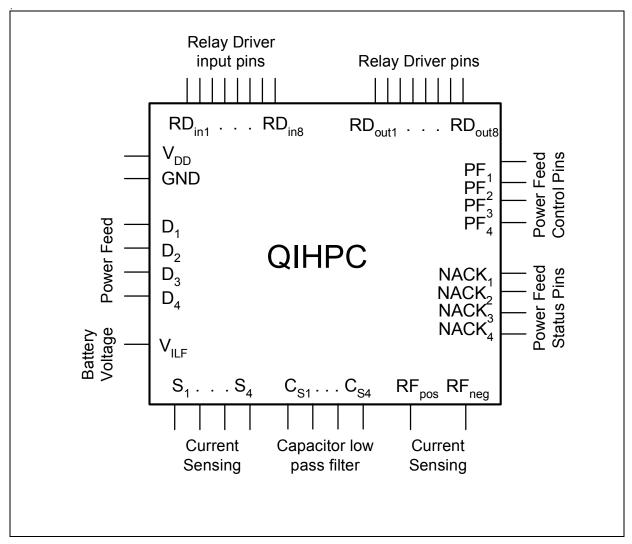

# 1.2 Logic Symbol

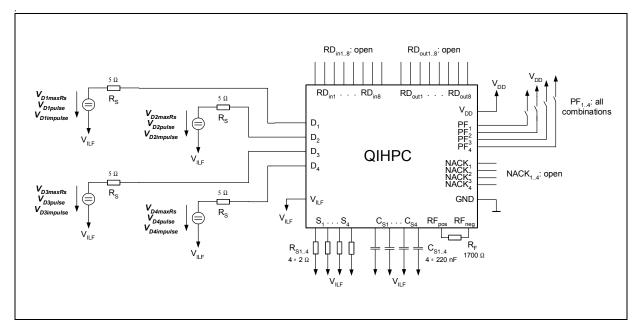

Figure 1 Logic Symbol

# 1.3 Typical Applications

The QIHPC is an integrated power controller especially designed for feeding two-wire ISDN/S(H)DSL-transmission lines. Four U interface lines can be powered by one QIHPC.

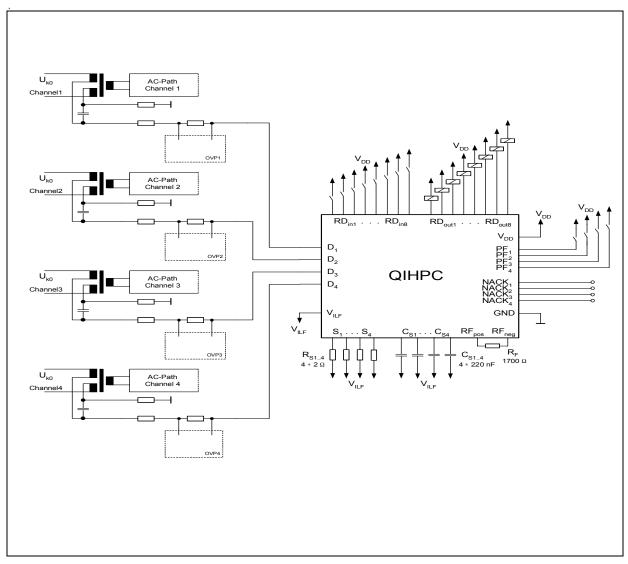

Figure 2 16-Line Card Application with DELIC, DFE-Q/T and AFE

Figure 3 System integration

Figure 3 gives general overview of the system integration of the QIHPC.

Due to the integrated "pull-down current-sinks" on the input pins  $PF_{1..4}$  and  $RD_{in1..8}$  only connections to  $V_{DD}$  are necessary to switch on power feeding to the lines or to switch on the relay drivers. When power feeding to a line is switched on, and this line is in a normal feeding condition (current less than the current limiting level), then the QIHPC shows a resistive connection from  $D_x$  to  $S_x$ .  $D_x$  and  $S_x$  are the drain and source of the integrated DMOS-transistor of channel x. The resistance value (DMOS- $R_{on}$ ) is typically 1.4  $\Omega$  with a total tolerance of about +/- 0.35  $\Omega$ .

# 1.4 S/T-Feeding

Due to its functional similarity to the PEB 2025 IEPC, the QIHPC can be used as a replacement for the PEB 2025 in applications such as current feeding at multiple S interfaces:

Table 1 Comparing the Power Feeeding IC's: IEPC vs. QIHPC

|                                                   | PEB 2025 IEPC                                     | PEF 2426 QIHPC                                           |

|---------------------------------------------------|---------------------------------------------------|----------------------------------------------------------|

| Vbat Range                                        | -60V to -12V                                      | -130V to - 30V                                           |

| Channels                                          | 4                                                 | 4                                                        |

| Vbat supply current (excl. Line feeding currents) | 0.2mA max.                                        | 1mA max                                                  |

| Dig. supply voltage                               | 4.75V to 5.25V                                    | +3V to +6V                                               |

| Dig. supply current (@ 5V)                        | 5mA typ.; 10mA max.                               | 0.7mA typ.; 1.5mA max.                                   |

| Feeding current control                           | System controlled turn-<br>on; automatic turn-off | Automatic current limitation; system controlled turn-off |

| Specified feeding current control settings        | 75mA; 152mA<br>(approx. <u>+</u> 25%)             | 67 up to 150mA (±12%) possible                           |

| Turn-on resistance                                | 70hm typ., 9 0hm max.                             | 1.4 Ohm typ., 2 Ohm max.                                 |

| System interface                                  | Parallel µP i/f (9 pins)                          | 8 I/O pins                                               |

| Relay drivers integrated                          | None                                              | 8                                                        |

| Operating temperature range                       | 0 to 70 °C                                        | -40 to +85°C (PEF)                                       |

| Package                                           | P-LCC-28; P-DIP-22                                | P-MQFP-44                                                |

**Pin Descriptions**

# 2 Pin Descriptions

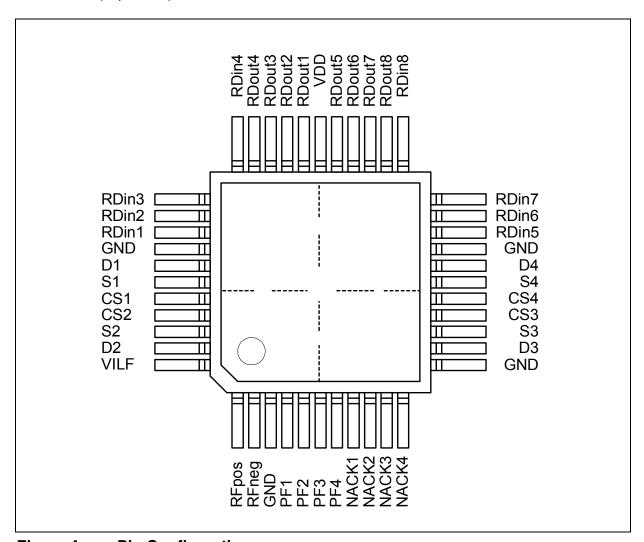

# 2.1 Pin Configuration

(top view)

Figure 4 Pin Configuration

# **Pin Descriptions**

# 2.2 Pin Definitions and Functions

# Table 2 Pin Definitions and Functions

| Pin No.              | Symbol                                                                   | Input (I)<br>Output (O) | Function                                                                                                                                                                                                  |

|----------------------|--------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28                   | V <sub>DD</sub>                                                          | Supply                  | Positive Supply Voltage, referred to GND. Operating Voltage Range from 3.0 V to 6.0 V.                                                                                                                    |

| 3<br>12<br>19<br>37  | GND                                                                      | Supply                  | Ground                                                                                                                                                                                                    |

| 44                   | V <sub>ILF</sub>                                                         | Supply                  | Line Feed Voltage, referred to GND. Operating Voltage Range from -130 V to -30 V.                                                                                                                         |

| 38<br>43<br>13<br>18 | D <sub>1</sub><br>D <sub>2</sub><br>D <sub>3</sub><br>D <sub>4</sub>     | 0                       | Drain Connections of the Output Transistors of Channels 14.  These pins have to be connected (via external resistors) to ISDN/S(H)DSL lines a (ring) of channels 14.                                      |

| 1 2                  | RF <sub>pos</sub><br>RF <sub>neg</sub>                                   | 0                       | Current limitation of Channels 14. These pins have to be connected to an external resistor $R_{\text{F}}$ . $R_{\text{F}}$ and $R_{\text{S14}}$ are defining the output current limit for all four lines. |

| 39<br>42<br>14<br>17 | S <sub>1</sub><br>S <sub>2</sub><br>S <sub>3</sub><br>S <sub>4</sub>     | 0                       | Overcurrent indication threshold.  These pins have to be connected via external resistors R <sub>S14</sub> to V <sub>ILF</sub> defining the overcurrent indication threshold of each line individually.   |

| 40<br>41<br>15<br>16 | C <sub>s1</sub><br>C <sub>s2</sub><br>C <sub>s3</sub><br>C <sub>s4</sub> | 0                       | External capacitors defining t <sub>oc</sub> -delays of Channels 14.  These pins have to be connected via external capacitors to V <sub>ILF</sub> defining the overcurrent indication delay.              |

| 4<br>5<br>6<br>7     | PF <sub>1</sub><br>PF <sub>2</sub><br>PF <sub>3</sub><br>PF <sub>4</sub> | PD                      | Power Feed Signal of Channels 14. Logic high on PF <sub>14</sub> switches on the power feeding to the line of channel 14.                                                                                 |

# **Pin Descriptions**

Table 2

Pin Definitions and Functions (Continued)

| Pin No. | Symbol                                 | Input (I)<br>Output (O) | Function                                                                                               |

|---------|----------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------|

| 8       | NACK <sub>1</sub><br>NACK <sub>2</sub> | 0                       | Not Acknowledged Signal of Channels 14. Logic low on NACK <sub>1 4</sub> signals that either the ISDN/ |

| 10      | NACK <sub>2</sub>                      |                         | S(H)DSL line of channel 14 is powered and in a                                                         |

| 11      | NACK <sub>4</sub>                      |                         | normal power on condition or that power feed is not requested                                          |

| 36      | RD <sub>in1</sub>                      | PD                      | Switch-On-Signal of Relay-Channels 18.                                                                 |

| 35      | RD <sub>in2</sub>                      |                         | Logic high on R <sub>in18</sub> switches on the relay driver npn-                                      |

| 34      | RD <sub>in3</sub>                      |                         | transistor of channel 18.                                                                              |

| 33      | RD <sub>in4</sub>                      |                         |                                                                                                        |

| 20      | RD <sub>in5</sub>                      |                         |                                                                                                        |

| 21      | RD <sub>in6</sub>                      |                         |                                                                                                        |

| 22      | RD <sub>in7</sub>                      |                         |                                                                                                        |

| 23      | RD <sub>in8</sub>                      |                         |                                                                                                        |

| 29      | RD <sub>out1</sub>                     | 0                       | Open Collector Output of Relay-Channels 18.                                                            |

| 30      | RD <sub>out2</sub>                     |                         | When the relay driver npn-transistor of channel 18 is                                                  |

| 31      | RD <sub>out3</sub>                     |                         | switched on, than this pin sinks a current of up to                                                    |

| 32      | RD <sub>out4</sub>                     |                         | 40 mA.                                                                                                 |

| 27      | RD <sub>out5</sub>                     |                         | An integrated zener diode guards the QIHPC against                                                     |

| 26      | RD <sub>out6</sub>                     |                         | inductive voltage peaks from the relay coil.                                                           |

| 25      | RD <sub>out7</sub>                     |                         |                                                                                                        |

| 24      | RD <sub>out8</sub>                     |                         |                                                                                                        |

# **3 Functional Description**

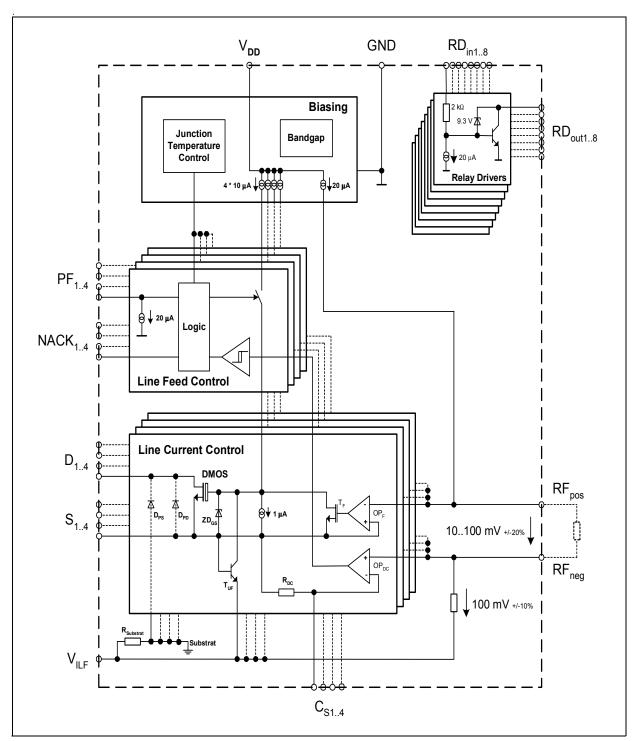

# 3.1 Functional Block Diagram

Figure 5 Functional Block Diagram

In the Functional Block Diagram, **Figure 5**, we can see four different types of circuit blocks: one biasing circuit, four line feed control circuits, four line current control circuits and eight relay driver circuits.

#### 3.2 Biasing Circuit

The bandgap circuit generates a constant voltage with respect to GND. This reference voltage is converted into a current of about 20  $\mu$ A which is necessary for level shifting. This current is converted back into 100 mV and 10..100 mV (depending on the value of the external resistor R<sub>F</sub>) reference voltages with respect to V<sub>ILF</sub>. These reference voltages and the external resistors connected between pins S<sub>1..4</sub> and V<sub>ILF</sub> defines the line current limit and the overcurrent indication threshold.

Currents of about 10  $\mu$ A are used for level shifting the power feed information. In the biasing block also all other biasing currents used on the chip are generated.

Intelligent junction temperature control in coordination with line current limiting protects the QIHPC against overloads. Also a fault condition on one line shall under no circumstance disturb a connection on another line. Therefore a junction temperature control circuit is necessary.

The junction temperature of the QIHPC will be monitored by an integrated thermal detector with three threshold levels, as defined in **Table 3**

| Table 3  | Thormal | Detector | Threshold | l avale |

|----------|---------|----------|-----------|---------|

| i abie 5 | inermai | Detector | inresnoia | Leveis  |

| Symbol          | Parameter Description              | <b>Test Conditions</b> | Limi | Limits |     |    |

|-----------------|------------------------------------|------------------------|------|--------|-----|----|

|                 |                                    |                        | Min  | Тур    | Max |    |

| T <sub>j1</sub> | 130 °C Thermal Detector threshold  | guaranteed by design   | 120  | 130    | 140 | °C |

| T <sub>h1</sub> | 130 °C Thermal Detector hysteresis | guaranteed by design   |      | 10     |     | °C |

| T <sub>j2</sub> | 170 °C Thermal Detector threshold  | guaranteed by design   | 160  | 170    | 180 | °C |

| T <sub>h2</sub> | 170 °C Thermal Detector hysteresis | guaranteed by design   |      | 10     |     | °C |

| T <sub>j3</sub> | 190 °C Thermal Detector threshold  | guaranteed by design   | 180  | 190    | 200 | °C |

| T <sub>h3</sub> | 190 °C Thermal Detector hysteresis | guaranteed by design   |      | 10     |     | °C |

Power on requests will only be executed if the junction temperature is below  $T_{j1}$  (typical 130 °C) and if no other line is in overcurrent condition. If the device junction temperature reaches the second threshold  $T_{i2}$  (typical 170 °C), then all the line drivers in the current-

overload condition will be switched off by the QIHPC. If the device junction temperature then still continues to increase to  $T_{j3}$  (typical 190 °C), all the line drivers will be turned off by the QIHPC.

The line(s) in current overload will be switched off sufficiently fast once the second threshold  $T_{j2}$  is reached, i.e. before the  $T_{j3}$  threshold is reached. This guarantees a disturbance free operation on lines not affected by a fault condition. Once a line had been switched off the relevant PF-pin has to be set to low and subsequently to high, for attempting to power this line again.

The internal protection mechanisms (current limiting and junction temperature control) already provide full protection of the  $D_{1..4}$  outputs against short circuits to a voltage between GND and  $V_{IIF}$ .

Note: The thermal protection mechanism of the QIHPC is a protection against instant damages due to overload at the outputs. Continuous high temperatures during operation, however, will reduce the life time of the QIHPC. Measures have to be taken to switch off the QIHPC in case of a short-circuit. E.g. if pin NACK<sub>x</sub> indicates an current overload condition, the QIHPC should be deactivated after few seconds using pin PF<sub>x</sub>.

#### 3.3 Line Feed Control Circuit

The QIHPC can supply the power for up to four transmission lines simultaneously. The exchange of activation commands and status information with the QIHPC will occur via a parallel interface, consisting of one input (PF) and one output (NACK) per line. The power switch can be controlled (PF) for each line individually. The status information (NACK) can be monitored for each line separately.

Integrated "pull-down current-sinks" are connected to the input pins  $PF_{1..4}$ . If one of these pins is not connected externally, the logic level at this pin is "0".

Logic level "0" means that the voltage on this pin is about 0 and logic level "1" means that the voltage level on this pin is about  $V_{\rm DD}$ .

A diagnostic of possible fault conditions is available on the status information pins (NACK) for each line separately.

The NACK pin is set to "1" when PF="1" and:

- Current on the line reaches the overcurrent indication threshold for longer than t<sub>oc</sub>.

- Over temperature  $(T_i > T_{i3})$  is detected.

- Power feed setting is not acknowledged by the QIHPC.

See also Table 4.

Table 4 Function Table for Controlling One Line

| PF           | current                                          | current                          | T <sub>i</sub>           | NACK | Comment                                                                                                                     |

|--------------|--------------------------------------------------|----------------------------------|--------------------------|------|-----------------------------------------------------------------------------------------------------------------------------|

|              | (other channels)                                 | (this channel)                   |                          |      |                                                                                                                             |

| 0            | don't care                                       | don't care                       | don't care               | 0    | line feeding not requested                                                                                                  |

| 0 → 1        | at least one<br>above<br>indication<br>threshold | don't care                       | don't care               | 1    | power feeding not<br>acknowledged and the line is<br>not powered as long as an<br>other line is in overcurrent<br>condition |

| <u>0</u> → 1 | don't care                                       | don't care                       | > T <sub>j1</sub>        | 1    | power feeding not<br>acknowledged and the line is<br>not powered, as long as the<br>junction temperature is to high         |

| 1            | don't care                                       | above indication threshold       | < T <sub>j2</sub>        | 1    | feeding: this line is in over current condition                                                                             |

| 1            | don't care                                       | below<br>indication<br>threshold | < <b>T</b> <sub>j3</sub> | 0    | normal line feeding                                                                                                         |

| 1            | don't care                                       | don't care                       | > T <sub>j3</sub>        | 1    | overtemperature condition, feeding is switched off                                                                          |

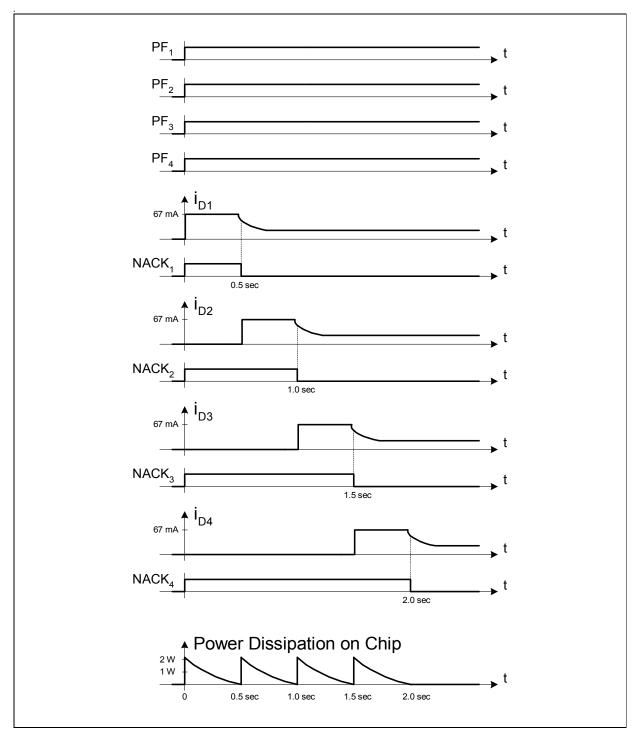

In case of simultaneous power up requests (PF<sub>1..4</sub>) the QIHPC take care of a proper start-up sequencing. The four channels have different priority. First priority for channel 1, second priority for channel 2 etc.

By simultaneous power up requests on more than one channel, the channel with the highest priority will be powered first, and will normally start with current limiting condition. When this channel is powered up and the drawn current drops below the current indication level, the next channel will be powered. And so on (see also figure 6 and table 3).

#### 3.4 Line Current Control Circuit

Two different current limiting circuits are integrated to control the DMOS power switch. An ultrafast and a fast current limiting circuit. See also **Figure 5**.

The ultrafast current limiting circuit consists of a bipolar npn-transistor  $T_{UF}$ . Note that bipolar npn-transistors are the fastest devices from the used technology. If the voltage

between  $S_{1..4}$  and  $V_{ILF}$  exceeds about 0.7 V the DMOS is switched off as fast as possible. 0.7 V divided by  $R_{S1..4} = 2~\Omega$  results in an ultrafast current limiting level of about 350 mA. This level has a strong temperature dependence (-40 °C junction temperature gives about 420 mA and +120 °C results in about 300 mA). The ultrafast current limiting circuit protects the QIHPC against short circuit on the line side with a resulting current rising as fast as 2 A/100 nsec.

The fast current limiting circuit keeps the voltage between  $S_{1..4}$  and  $V_{ILF}$  below a programmable voltage level. This results in a current limitation.

Zener diode ZD<sub>GS</sub> protects the DMOS-gate.

Diodes  $D_{PD}$  and  $D_{PS}$  are the parasitic drain-bulk-diode and drain-substrate-diode of the DMOS transistor (junction isolated technology). The diodes do not provide overvoltage protection, negative surges would pass through to  $S_{1..4}$  and  $V_{ILF}$  affecting the battery voltage. Extra overvoltage protection circuitry is necessary to conduct voltage surges form the line to ground, and to prevent that any current can flow into Diodes  $D_{PD}$  and  $D_{PS}$ .

Typical value of DMOS-on-resistance including internal wiring-resistance to the pins  $D_{1..4}$  and  $S_{1..4}$  is 1.4  $\Omega$ .

To identify overcurrent, the voltage between  $S_{1..4}$  and  $V_{ILF}$  is compared to 100 mV. If the voltage exceeds this level, this is indicated to the line current control circuits. A resistor and the external capacitor  $C_S$  define a lowpass filter (time delay) to suppress the changes on NACK due to short overcurrent surges. This enables to filter the effects of longitudinal AC current.

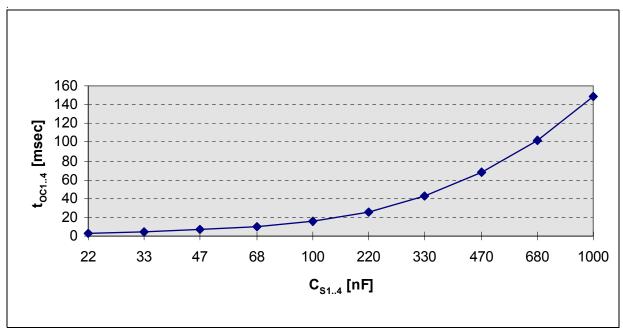

An external capacitor with a value of about 220 nF results in a delay time ( $t_{OC}$ ) of about 25 msec.

# 3.5 Relays Driver Circuit

The output transistor is a bipolar npn. The maximal collector current should not exceed 40 mA. When switching off an inductive load, zener diode and npn clamps the voltage level on pin RD<sub>out1..8</sub> at about 10 V. The 2 k $\Omega$  resistor limits the input current on pin RD<sub>in1..8</sub> and additionally the npn collector current.

If a pin  $\mathrm{RD}_{\mathrm{in1..8}}$  is not connected, the integrated "pull-down current-sink" holds the respective relay driver in switched-off condition.

**Application Hints**

# 4 Application Hints

# 4.1 Resistor R<sub>S1..4</sub>

The value of this resistor defines the overcurrent indication level. Note, that the value of this resistor must be considered for line symmetry. The typical overcurrent indication level I<sub>ind</sub> can be programmed by using the following formula.

$$I_{ind} = \frac{100mV}{R_{S1...4}}$$

If for any reason one or more ports of the QIHPC shall remain unused, the respective resistor  $R_{Sx}$  has to provided anyway. Pin  $D_x$ , however, can be left unconnected.

# 4.2 Resistor R<sub>F</sub>

The values of resistors  $R_F$  and  $R_{S1..4}$  define the current limiting level. The typical overcurrent limitation level  $I_{lim}$  can be programmed by using the following formula.

$$I_{lim} = \frac{100mV + R_F \cdot 20\mu A}{R_{S1...4}}$$

# 4.3 Capacitor C<sub>S1..4</sub>

The value of this capacitor define the resulting delay time  $t_{OC}$  for the overcurrent indication. For typical values of  $t_{OC}$  as a function of  $C_{S1..4}$  see **Figure 6**.

# **Application Hints**

Figure 6 Delay time  $t_{OC}$  as a function of the value of  $C_{S1..4}$  (typical values)

**Application Hints**

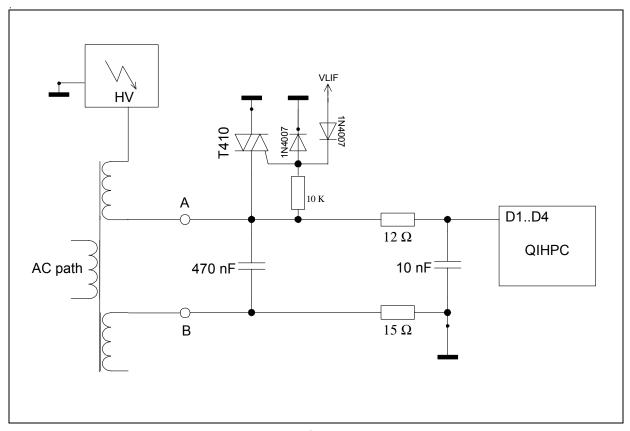

# 4.4 Protection Circuitry

Figure 7 Proposal for a Protection Circuitry

An external circuitry is needed to protect the QIHPC against damages due to high voltages from the line. High voltages can be caused by lightning surges or foreign voltage contact.

The protection element in this scheme is a Triac (T410). With positive going surges, the Triac will fire through a gate current flowing via diode 1N4107 to ground. With negative going surges, the gate current is supplied by VILF via the second 1N4007 diode. This circuit is capable to protect the QIHPC against damage with surges up to +/- 3kV (1.2/50µs and 10/700 µs pulse shape).

Shorting of voltage surges to GND is sensed by the QIHPC in the same way as a short-circuit at the line. It will react according to the programmed overcurrent indication and overcurrent limitation.

#### **Operational Description**

# **5** Operational Description

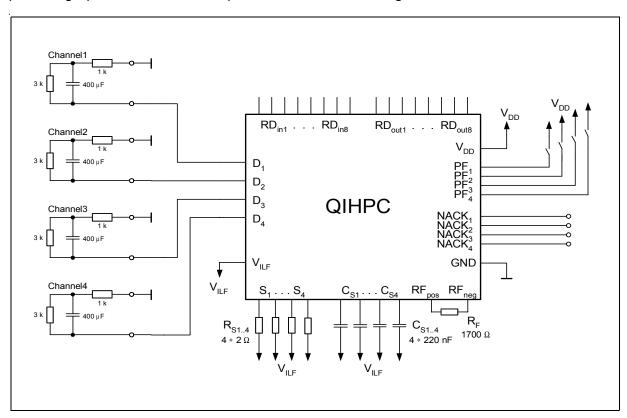

The QIHPC is compliant to the ETSITS 102 080 "Dynamic power feeding requirements" using the LT power test load (see **Figure 8**). There is no requirement for the order of powering up the lines, or for dependencies of controlling between the lines.

Figure 8 Circuit with "LT Power Source Test Loads"

With the LT power source test load from TS 102 080 the QIHPC can power up four U line interfaces within about 2 seconds "quasi simultaneous". The input sequence and expected output sequence with power dissipation diagram is shown in **Figure 9**. The power dissipation in the chip is quite small.

A fault condition (short circuit) on one line does not affect the power up of the other lines.

#### **Example:**

Assumed a short circuit on line 3. A simultaneous power up request is applied to the QIHPC. The power up of lines 1 and 2 will proceed as expected. When powering up line 3, the chip temperature control  $(T_{j2})$  will switch off this line. Lines 1 and 2 are still powered and remain in normal power on condition. When the junction temperature is decreased to  $T_{j1}$  the QIHPC will try to power up line 4. If there is no fault condition on line 4 the lines 1, 2 and 4 are finally in a normal power on condition. Line 3 is still in power off. To to repeat the trial to powering up line 3, the input signal PF<sub>3</sub> must set to "0" and "1" again.

# **Operational Description**

Figure 9 Simultaneous Power Up Sequence

# 6 Electrical Characteristics

# 6.1 Absolute Maximum Ratings

| Parameter                                                                                                                                                                                                 | Symbol                                  | Limit Values                     | Unit           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------|----------------|

| Operating ambient temperature range:                                                                                                                                                                      | $T_{A}$                                 | - 40 to 85                       | °C             |

| Storage temperature range                                                                                                                                                                                 | $T_{ m stg}$                            | - 65 to 125                      | °C             |

| Voltage on pin V <sub>DD</sub> with respect to ground                                                                                                                                                     | $V_{\scriptscriptstyle \sf DDmax}$      | - 0.4 to + 8                     | V              |

| Voltage on pin V <sub>ILF</sub> with respect to ground                                                                                                                                                    | $V_{\scriptscriptstyle \sf ILFmax}$     | $- 140 \text{ to } V_{DD} + 0.4$ | V              |

| Voltages on pins D <sub>14</sub> with respect to V <sub>ILF</sub>                                                                                                                                         | $V_{\scriptscriptstyle 	extsf{D14max}}$ | - 0.4 to + 150                   | V              |

| Voltages on pins $D_{14}$ with respect to $V_{ILF}$ with series resistor $R_S = 5 \Omega$ /figure 15                                                                                                      | $V_{	exttt{D14maxRs}}$                  | - 3 to + 150                     | V              |

| Pulse voltages on pins $D_{14}$ with respect to $V_{ILF}$ with series resistor $R_S = 5 \Omega$ /figure 15: $t = 200 \text{ msec}$ / $f = 50 \text{ Hz}$ or $t = 50 \text{ msec}$ / $f = 16.7 \text{ Hz}$ | $V_{	t D14 	t pulse}$                   | – 3 to + 150                     | V <sub>P</sub> |

| Impulse voltages on pins $D_{14}$ with respect to $V_{ILF}$ with series resistor $R_S = 5 \Omega$ /figure 15: $T_{dur} = 20 \mu sec / T_{rise} = 25 nsec / non repetitive$                                | $V_{	exttt{D14impulse}}$                | - 5 to + 160                     | V <sub>P</sub> |

| Voltages on pins S <sub>14</sub> with respect to V <sub>ILF</sub>                                                                                                                                         | $V_{ m S14max}$                         | - 0.4 to + 8                     | V              |

| Voltages on pins $D_{14}$ with respect to voltages on pins $S_{14}$                                                                                                                                       | $V_{	extsf{DS14max}}$                   | - 0.4 to + 140                   | V              |

| Voltages on pins C <sub>S14</sub> with respect to V <sub>ILF</sub>                                                                                                                                        | $V_{{\scriptscriptstyle CS14max}}$      | - 0.4 to + 8                     | V              |

| Voltages on pins PF <sub>14</sub> with respect to ground                                                                                                                                                  | $V_{	ext{PF14max}}$                     | $-0.4 \text{ to V}_{DD} + 0.4$   | V              |

| Voltages on pins NACK <sub>14</sub> with respect to ground                                                                                                                                                | $V_{\scriptscriptstyle{NA14max}}$       | $-0.4 \text{ to V}_{DD} + 0.4$   | V              |

| Voltages on pins R <sub>in14</sub> with respect to ground                                                                                                                                                 | $V_{	ext{Ri14max}}$                     | $-0.4 \text{ to V}_{DD} + 0.4$   | V              |

| Voltages on pins R <sub>out14</sub> with respect to ground                                                                                                                                                | $V_{	extsf{Ro14max}}$                   | $-0.4 \text{ to V}_{DD} + 0.4$   | V              |

| ESD-voltage, all pins (Human body model)                                                                                                                                                                  | $V_{\scriptscriptstyle{ESD-HBM}}$       | - 1 to + 1                       | kV             |

Note: Stresses above those listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

# 6.2 Operating Range

| Parameter                       | Symbol                      | Limit Values   | Unit |

|---------------------------------|-----------------------------|----------------|------|

| V <sub>DD</sub> supply voltage  | $V_{\scriptscriptstyle DD}$ | + 3.0 to + 6.0 | V    |

| V <sub>ILF</sub> supply voltage | $V_{\scriptscriptstyleILF}$ | - 130 to - 30  | V    |

Note: In the operating range the functions given in the circuit description are fulfilled.

#### 6.3 Static Thermal Resistance

| Parameter           | Symbol      | Limit Values | Unit |

|---------------------|-------------|--------------|------|

| Junction to ambient | $R_{th,jA}$ | < 62.9       | K/W  |

| Junction to case    | $R_{th,jC}$ | < 14.6       | K/W  |

#### 6.4 AC/DC-Characteristics

**General Test Conditions (if not indicated otherwise):**

$$R_{\rm S1..4} = 2~\Omega~\pm 0.1~\%~~C_{\rm S1..4}$$

=220 nF  $~\pm 1~\%$ (63 V)  $R_{\rm F} = 1700~\Omega~\pm 0.1~\%$

Supply voltages for typical characteristics:

$$V_{\scriptscriptstyle

m DD}$$

= 5 V  $\pm$  1 %  $V_{\scriptscriptstyle

m ILF}$  =-100 V  $\pm$  1 %

Note: The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_{\rm A}$  = 25 °C and the given supply voltage

| Table 5 | DC Characteristics   |

|---------|----------------------|

| IUDICO  | DO Olidiadici istics |

| No.             | Parameter                                   | Symbol                           | Limit Values                             |       |                     | Unit   | <b>Test Condition</b>                                                          | Test |

|-----------------|---------------------------------------------|----------------------------------|------------------------------------------|-------|---------------------|--------|--------------------------------------------------------------------------------|------|

|                 |                                             |                                  | min.                                     | typ.  | max.                |        |                                                                                | Fig. |

| Supp            | oly Currents                                |                                  |                                          |       |                     |        |                                                                                |      |

| 1               | $V_{\scriptscriptstyle 	extsf{DD}}$ current | $I_{	extsf{DD}}$                 |                                          | 0.7   | 1.5                 | mA     |                                                                                | 10   |

| 2               | $V_{\scriptscriptstyle \rm ILF}$ current    | $I_{ILF}$                        |                                          | 0.4   | 1                   | mA     | excluding line currents                                                        | 10   |

| Line            | Currents, Delay                             | Time t <sub>oc</sub> a           | nd DM                                    | IOS-R | <sub>ON</sub> resis | stance |                                                                                | •    |

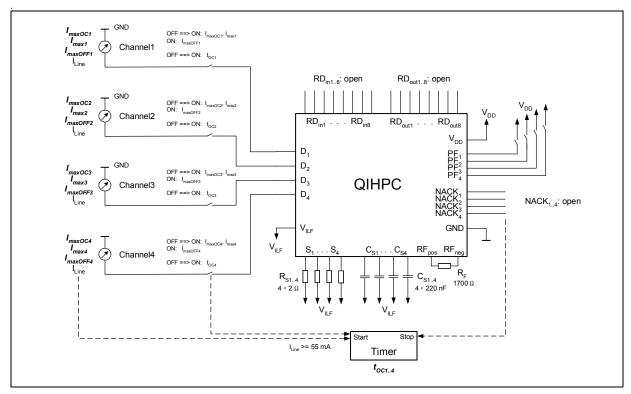

| 3               | Overcurrent Indication Level                | $I_{maxOC14}$                    | 45                                       | 50    | 55                  | mA     | PF <sub>14</sub> = "1"                                                         | 11   |

| 4               | Current Limiting<br>Level                   | $I_{maxL14}$                     | 59                                       | 67    | 75.5                | mA     | PF <sub>14</sub> = "1"                                                         | 11   |

| 5               | Line Current in "on"-condition              | $I_{maxON14}$                    |                                          |       | 168                 | mA     | $PF_{14} = "1"$<br>if $I_{\text{maxL1}4} > I_{\text{maxON1}4}$                 | 11   |

| 6               | Line Current in "off"-condition             | $I_{maxOFF14}$                   |                                          | 0     | 10                  | μΑ     | PF <sub>14</sub> = "0"                                                         | 11   |

| 7               | Delay Time t <sub>OC</sub>                  | t <sub>OC14</sub>                | 10                                       | 25    | 40                  | msec   | PF <sub>14</sub> = "1",<br>I <sub>Line</sub> >= 55 mA                          | 11   |

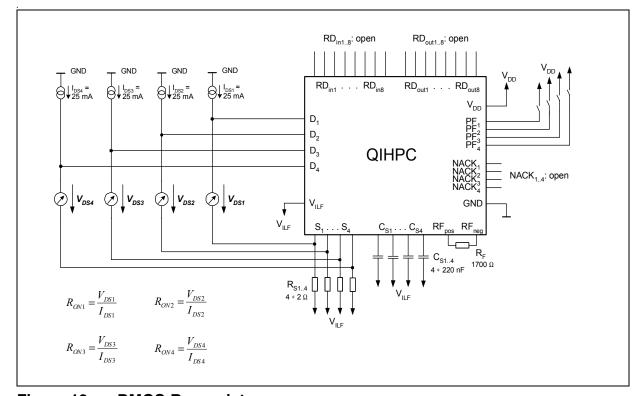

| 8               | DMOS-R <sub>ON</sub> resistance             | $R_{ON14}$                       | 0.8                                      | 1.4   | 2.0                 | Ω      | PF <sub>14</sub> = "1",<br>I <sub>Line</sub> = 25 mA                           | 12   |

| PF <sub>1</sub> | 4, Logic Input Lev                          | vels                             |                                          |       |                     |        |                                                                                |      |

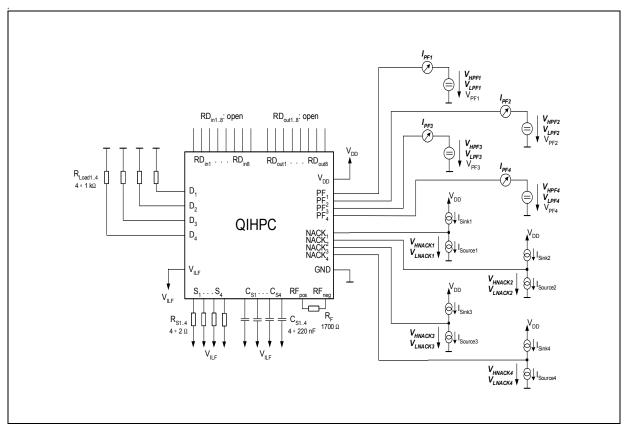

| 9               | "1" - Input<br>Voltage                      | $V_{HPF14}$                      | 2                                        |       |                     | V      |                                                                                | 13   |

| 10              | "0" - Input<br>Voltage                      | $V_{LPF14}$                      |                                          |       | 0.8                 | V      |                                                                                | 13   |

| 11              | pull down<br>Input Current                  | $I_{PF14}$                       | 10                                       | 20    | 30                  | μΑ     | $\begin{array}{c} {\rm 0.8 \; V < V_{\rm PF14} <} \\ {V_{\rm DD}} \end{array}$ | 13   |

| NAC             | K <sub>14</sub> , Logic Outp                | ut Levels                        |                                          |       | •                   | •      |                                                                                | •    |

| 12              | "1" - Output<br>Voltage                     | $V_{\sf HNACK14}$                | $V_{\scriptscriptstyle 	extsf{DD}}-$ 0.4 |       |                     | V      | $I_{\text{Source}_{14}} = 100 \mu\text{A}$                                     | 13   |

| 13              | "0" - Output<br>Voltage                     | $V_{\scriptscriptstyle LNACK14}$ |                                          |       | 0.4                 | V      | $I_{\text{Sink14}} = 100  \mu\text{A}$                                         | 13   |

Table 5

DC Characteristics (Continued)

| No.                  | Parameter                      | Symbol                | Limit Values |      |                  | Unit | Test Condition                                                         | Test |

|----------------------|--------------------------------|-----------------------|--------------|------|------------------|------|------------------------------------------------------------------------|------|

|                      |                                |                       | min.         | typ. | max.             |      |                                                                        | Fig. |

| $\overline{RD_{in}}$ | 18, Relay Driver               | Inputs                |              |      |                  |      |                                                                        |      |

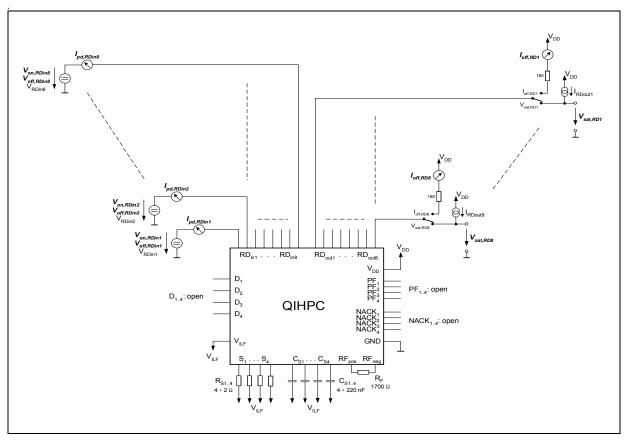

| 14                   | "ON" - Input<br>Voltage        | $V_{ m on,RDin18}$    | 2.0          |      | $V_{	extsf{DD}}$ | V    |                                                                        | 14   |

| 15                   | "OFF" - Input<br>Voltage       | $V_{{ m off,RDin18}}$ |              |      | 0.4              | V    |                                                                        | 14   |

| 16                   | pull down<br>Input Current     | $I_{ m pd,RDin18}$    |              | 20   | 30               | μΑ   | $0 < V_{\text{RDin18}} < 0.4 \text{ V}$                                | 14   |

| RD                   | <sub>ut18</sub> , Relay Drive  | r Outputs             |              |      |                  |      |                                                                        |      |

| 17                   | Saturation<br>Voltage          | $V_{{\sf sat1,RD18}}$ |              | 0.25 | 0.4              | V    | $V_{ m RDin18} = 2,4 \text{ V}, \ I_{ m RDout18} = 33 \text{ mA}$      | 14   |

| 18                   | Saturation<br>Voltage          | $V_{ m sat2,RD18}$    | 0.2          | 0.4  | 0,5              | V    | $V_{\rm RDin18} = 2.4 \text{ V},$<br>$I_{\rm RDout18} = 40 \text{ mA}$ | 14   |

| 19                   | Current in "off"-<br>condition | $I_{ m off,RD18}$     |              | 0    | 20               | μΑ   | $V_{\text{RDin18}} = 0.4 \text{ V}$                                    | 14   |

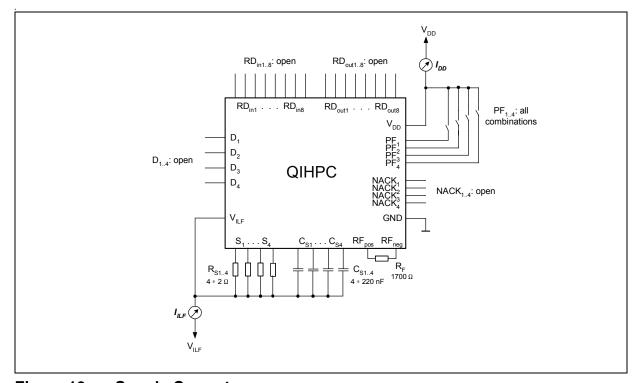

# 6.5 Testing the Electrical Parameters

Figure 10 Supply Currents

Figure 11 Line Currents and Delay Time toc

Figure 12 DMOS-R<sub>ON</sub> resistance

Figure 13 PF<sub>1..4</sub>, Logic Input Levels and NACK<sub>1..4</sub>, Logic Output Levels

Figure 14 RD<sub>in1..8</sub>, Relay Driver Inputs and RD<sub>out1..8</sub> Relay Driver Outputs

Figure 15 Test circuit for maximum DC-voltages, pulse voltages and impulse voltages on pins  $D_{1..4}$

#### **Package Outlines**

# 7 Package Outlines

# Sorts of Packing

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device

Dimensions in mm

# Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results.

Better operating results and business excellence mean less idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

http://www.infineon.com