# Microcomputer Components

Standalone Full-CAN Controller

SAE 81C90/91

Data Sheet 01.97 Preliminary

# SIEMENS

# Stand Alone Full CAN Controller

# **SAE 81C90/91**

- Full CAN controller for data rate up to 1 Mbaud

- Complies with CAN specification V2.0 part A (part B passive)

- Up to 16 messages simultaneous (each with maximum data length)

- Message identifier reprogrammable "on the fly"

- Several transmit jobs can be sent with a single command

- Transmit check

- Basic CAN feature

- Time stamp for eight messages

- Two host interfaces (parallel and serial)

- User-configurable outputs for different bus concepts

- Programmable clock output

- Two 8 bit I/O-Port extension (P-LCC-44-1 package only)

The device comes in two versions:

**SAE 81C90** in a P-LCC-44-1 package with two 8-bit I/O ports, and **SAE 81C91** in a P-LCC-28-1 package without I/O ports.

| SAE 81C90/91<br>Revision History: |                                                                       | Version 01.97        |

|-----------------------------------|-----------------------------------------------------------------------|----------------------|

| Previous Rele                     | eases:                                                                | 06.95                |

|                                   |                                                                       | 05.94 (Copy version) |

| Page                              | Subjects                                                              |                      |

| 1056                              | Figure 1 corrected.                                                   |                      |

| 1057                              | Figure 2 corrected.                                                   |                      |

| 1059                              | Notes updated.                                                        |                      |

| 1065 - 1084                       | Register description and arrangement improved.                        |                      |

| 1066, 1069                        | New register                                                          | maps.                |

| 1093                              | $t_{\text{AVLL}}, t_{\text{LLAX}}, t_{\text{DVWH}}$ changed to 10 ns. |                      |

| 1093                              | t <sub>WHDX</sub> changed                                             | d to 5 ns.           |

Controller Area Network (CAN): License of Robert Bosch GmbH

#### Introduction

The Siemens Stand Alone Full CAN (SFCAN) circuit incorporates all the parts for completely autonomous transmission and reception of messages using the CAN protocol. The flexible, programmable interface allows hookup to different implementations of the physical layer. The link to a host controller can be made either by a multiplexed 8-bit address/data bus or by a high-speed, serial synchronous interface.

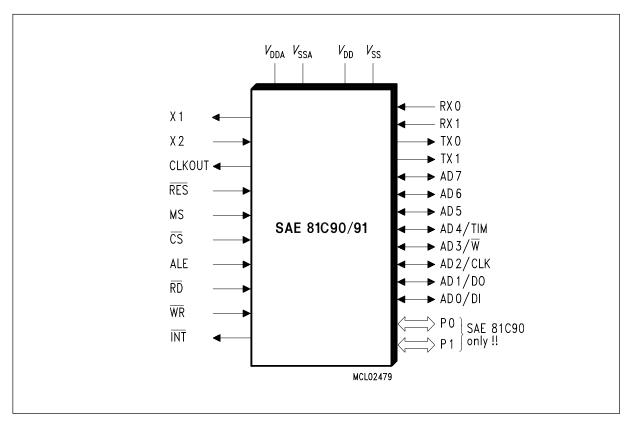

Figure 1 Logic Symbol

# **Ordering Information**

| Туре      | Ordering Code | Package    | Function                                                              |

|-----------|---------------|------------|-----------------------------------------------------------------------|

| SAE 81C91 | Q67121-F0001  | P-LCC-28-1 | Stand Alone Full CAN Controller<br>Temperature range - 40 to + 110 °C |

| SAE 81C90 | Q67121-H9038  | P-LCC-44-1 | Stand Alone Full CAN Controller<br>Temperature range - 40 to + 110 °C |

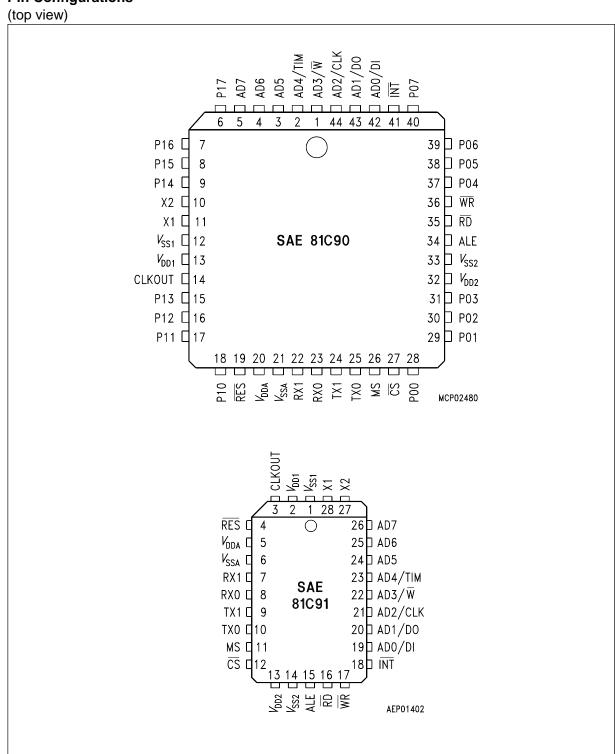

# **Pin Configurations**

Figure 2

# **Pin Definitions and Functions**

| Symbol           | Pin Numb                                | er      | Input (I)  | Function                                                                        |  |  |  |

|------------------|-----------------------------------------|---------|------------|---------------------------------------------------------------------------------|--|--|--|

|                  | PLCC-48                                 | PLCC-28 | Output (O) | Crystal assillator output                                                       |  |  |  |

| X1 <sup>1)</sup> | 11                                      | 28      | 0          | Crystal oscillator output.  Must be unconnected for external clock input.       |  |  |  |

| X2 <sup>1)</sup> | 10                                      | 27      | 1          | Crystal oscillator input. Used for external clock input.                        |  |  |  |

| CLKOUT 1)        | 14                                      | 3       | 0          | Clock output                                                                    |  |  |  |

| RES              | 19                                      | 4       | I          | Reset. (Schmitt trigger characteristic)                                         |  |  |  |

| AD0/DI           | 42                                      | 19      | I/O        | PI: Address / Data bus / SI: Data input                                         |  |  |  |

| AD1/DO           | 43                                      | 20      | I/O        | PI: Address / Data bus / SI: Data output                                        |  |  |  |

| AD2/CLK          | 44                                      | 21      | I/O        | PI: Address / Data bus / SI: Clock input                                        |  |  |  |

| AD3/W            | 1                                       | 22      | I/O        | PI: Address / Data bus / SI: Write select                                       |  |  |  |

| AD4/TIM          | 2                                       | 23      | I/O        | PI: Address / Data bus / SI:<br>TIM = 0: Timing A; TIM = 1: Timing B            |  |  |  |

| AD5              | 3                                       | 24      | I/O        | PI: Address/Data bus                                                            |  |  |  |

| AD6              | 4                                       | 25      | I/O        | PI: Address/Data bus                                                            |  |  |  |

| AD7              | 5                                       | 26      | I/O        | PI: Address/Data bus                                                            |  |  |  |

| RD               | 35                                      | 16      | I          | PI: Read / SI: no Function                                                      |  |  |  |

| WR               | 36                                      | 17      | I          | PI: Write / SI: no Function                                                     |  |  |  |

| ALE              | 34                                      | 15      | I          | PI: Address Latch Enable / SI:no Function                                       |  |  |  |

| CS               | 27                                      | 12      | I          | Chip Select                                                                     |  |  |  |

| INT              | 41                                      | 18      | 0          | Interrupt                                                                       |  |  |  |

| MS               | 26                                      | 11      | I          | Mode Select (PI $\leftrightarrow$ SI)                                           |  |  |  |

| P00 P03,         | 28, 29,<br>30, 31,<br>37, 38,<br>39, 40 | -       | I/O<br>I/O | Port 0 These pins provide internal pullup resistors of about 10200 k $\Omega$ . |  |  |  |

| P10 P13,         | 18, 17,<br>16, 15,                      | _       | I/O        | Port 1 These pins provide internal pullup resistors of                          |  |  |  |

| P14 P17          | 9, 8, 7, 6                              | _       | I/O        | about 10200 kΩ.                                                                 |  |  |  |

| TX0              | 25                                      | 10      | 0          | Transmitter output 0                                                            |  |  |  |

| TX1              | 24                                      | 9       | 0          | Transmitter output 1                                                            |  |  |  |

| RX0              | 23                                      | 8       | I          | Comparator input 0 / Digital input 2)                                           |  |  |  |

| RX1              | 22                                      | 7       | I          | Comparator input 1 <sup>2)</sup>                                                |  |  |  |

| $V_{DDA}$        | 20                                      | 5       | I          | Analog power supply for comparator (may be unconnected using the digital mode)  |  |  |  |

# Pin Definitions and Functions (cont'd)

| Symbol                       | Pin Numb | er      | Input (I)  | Function                                                      |  |  |

|------------------------------|----------|---------|------------|---------------------------------------------------------------|--|--|

|                              | PLCC-48  | PLCC-28 | Output (O) |                                                               |  |  |

| $\overline{V_{	extsf{SSA}}}$ | 21       | 6       | I          | Analog power ground for comparator (must always be connected) |  |  |

| $\overline{V_{	extsf{DD1}}}$ | 13       | 2       | I          | Digital power supply 3)                                       |  |  |

| $\overline{V_{	extsf{DD2}}}$ | 32       | 13      | I          | Digital power supply                                          |  |  |

| $\overline{V_{	extsf{SS1}}}$ | 12       | 1       | I          | Digital power ground 3)                                       |  |  |

| $\overline{V_{	t SS2}}$      | 33       | 14      | I          | Digital power ground                                          |  |  |

<sup>1)</sup> For best results keep the crystal circuitry connections as short as possible and keep the CLKOUT line away from it.

- 2) If the bus lines work according to the ISO specification, additional circuitry is necessary for interconnection of the input comparator to the bus lines. The digital mode is enabled by setting bit DI in register BL2. When using the digital mode pin RX1 should be on V<sub>SS</sub>.

- <sup>3)</sup> It is recommended to decouple these supply pins close to the device using a 10 pF capacitor in addition to the standard 100 nF capacitor.

# **Functional Description**

The Siemens stand-alone Full-CAN (SFCAN) circuit is a large-scale-integrated peripheral device that executes the entire protocol of an automobile or industrial network.

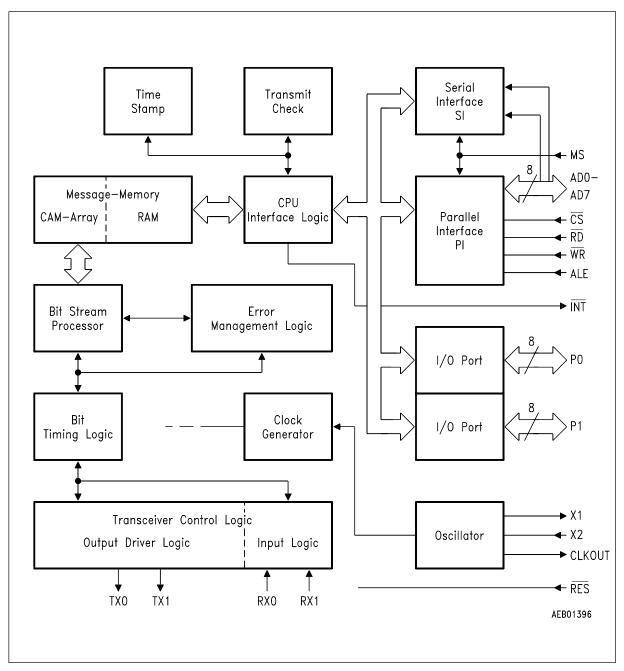

Figure 3 Block Diagram

Bus communication is based on the controller-area-network (CAN) protocol. With features like short message length, guaranteed reaction time for messages of appropriate priority, which is defined by the message identifiers. Also included are powerful error detection and treatment capabilities plus ease of operation. The CAN protocol is especially designed for the requirements of automobile and industrial electronic networks.

The SFCAN circuit incorporates all the parts for completely independent transmission and reception of messages using the CAN protocol. The flexible, programmable interface allows connection to different implementations of the physical layer. The link to a host controller can be made either by a multiplexed 8-bit address/data bus or by a high-speed, serial synchronous interface.

#### **Message Memory**

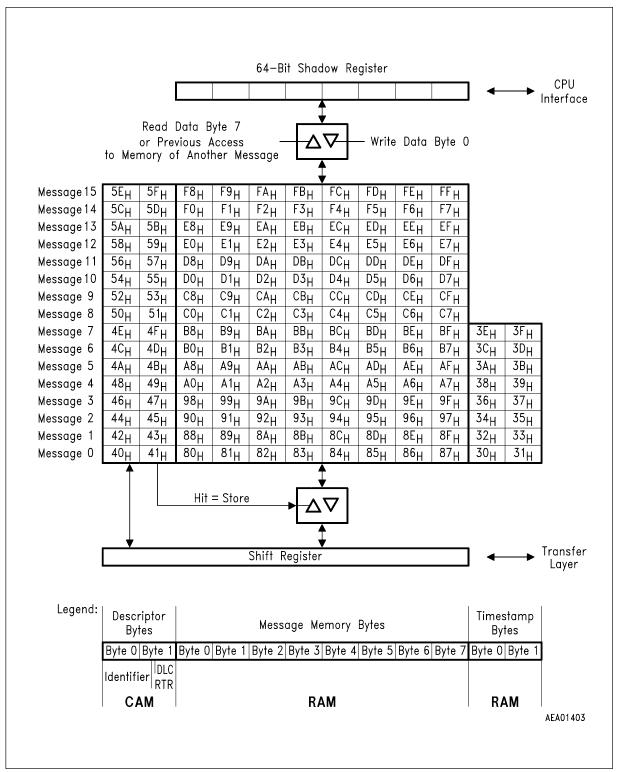

The SFCAN circuit filters incoming messages with an associative memory (CAM = content-addressable memory). For this the identifier and RTR bits of the required message must be written to the appropriate memory location.

The identifier of each incoming message is compared with the identifiers stored in the CAM. Upon a match the received data bytes are written into the RAM buffer of the matching message. At the same time the corresponding receive-ready bit is set and a receive interrupt is generated, if it is enabled. If no match is detected, the received message is rejected.

Identifiers can be reprogrammed at any time, although it is possible that data of the old or new identifier may be lost during reprogramming.

An incoming transmit request will only be satisfied automatically by the hardware if the RTR bit of the particular identifier is set in CAM.

**To ensure data consistency** when reading or writing several data bytes of a specific message the message objects are not accessed directly but via a 64-bit shadow register (see figure below). This shadow register stores the complete data field of a certain message object for both reading and writing.

For read accesses the message's data field is copied to the shadow register...

- ...with the 1st read access to the respective data field (e.g. 80<sub>H</sub> ... 87<sub>H</sub> for message 0), or

- ...with any read access to byte 7 of the respective data field (e.g. 87<sub>H</sub> for message 0).

This ensures that all bytes read via the shadow register belong to the same message, even though a new one might have been received in the meantime.

For write accesses the shadow register is copied to the respective message data field...

...with any write access to byte 0 of the respective data field (e.g. 80<sub>H</sub> for message 0).

This ensures that only completely updated message are transmitted.

It is therefore recommended to begin all read and write accesses with the most-significant data byte of a message and end with data byte 0. This ensures operations on consistent data and correct transfers between the shadow register and the message RAM.

**Note:** For these reasons it is absolutely essential to ensure that the writing of data is not interrupted by a read operation and vice versa, a read operation should not be interrupted by a write.

Figure 4

CAM, Message Memory and Time-Stamp Registers

# **Bit Stream Processor (BSP)**

The bit-stream processor controls the entire protocol, differentiates between the frames types and detects frame errors.

#### **Error Management Logic (EML)**

The error-management logic receives error messages from the BSP and, in turn, sends back information about error state to the BSP and CIL.

# **Bit Timing Logic (BTL)**

The bit-timing logic determines the timing of the bits and synchronizes with the edges of the bit stream on the CAN bus.

# **Transceiver Control Logic (TCL)**

The transceiver-control logic consists of programmable output driver, input comparator and input multiplexer.

#### **Clock Generator (CG)**

The clock generator consists of an oscillator and a programmable divider. The oscillator can be fed from an external quartz crystal, ceramic resonator or an external timing source. The permissible crystal frequency is 1 to 20 MHz, and the external clock may be between 0 and 20 MHz. A programmable frequency, dependent on the crystal clock, is available with the CLKOUT pin, e.g. for the clocking of a host controller.

#### **CPU Interface Logic (CIL)**

The CPU interface logic controls the access of the host via the parallel or serial interface, interprets the commands and outputs status and interrupt information.

#### **Transmit Check**

The CAN protocol ensures a very high integrity for the data transferred over the bus. The on-chip path from the data stored in parallel to the serial bit stream is not protected by the protocol. To eliminate any possible uncertainties at this point too, the SFCAN circuit incorporates a transmitcheck unit. This unit reads back a transmitted message via the normal receive path from the bus interface and compares the data with those written into the message memory by the host controller. If any inconsistency of the data is detected, the current message will be invalidated by an error frame.

The transmit-check error counter TCEC is then incremented by 1. If this counter reaches 4 an error interrupt (bit TCI in the INT register) is generated, provided that this has not been masked (bit ETCI in the IMSK register). This count will also produce the Bus Off status.

The TCEC is set to 0 after a reset and can be read and also written for test purposes at any time.

**Note:** The transmit-check is an additional feature of the Siemens Full CAN Chip and is not part of the CAN protocol.

# **Time Stamp**

It is impossible to determine from the received data in the message memory when they were received. So the host controller is unable to derive any information about the actuality or the repetition rate of the data.

To enable an indication of the time of reception for at least some of the messages, a 16-bit timer is implemented on the SAE 81C90/91. The content of this gets written into the time-stamp registers of the particular message when it is received (for the messages 0 through 7). There are two time-stamp bytes for each of the messages 0 through 7, and these hold the value of the 16-bit timer.

The actuality of a message is determined by subtracting the old time-stamp of a message, stored in the host controller, from the new one, with respect to the timer overflow bit.

Overflow of the timer can be detected by bit TSOV in the CTRL register. This bit does not trigger an interrupt and has to be reset by the host controller. Depending on the setting of bitfield TSP in register CTRL, the counter is fed with 1/32, 1/64, 1/128 or 1/256 of the bus clock. The momentary timer status can be read and set at any time. The timer starts at 0 after a reset and cannot be stopped.

#### I/O-Ports

There are two parallel I/O ports in the SAE 81C90, each with eight pins. These ports are configured pin by pin as input or output, depending on the contents of the port-direction register.

The output data for the port pins can be written (latched) into the port-latch register. Reading this register reproduces the contents of the latch. The levels on the port pins can be read from the port-pin register.

For the SAE 81C91 in its P-LCC-28-1 package, the pads of the I/O ports are not bonded and therefore unavailable to the user.

**Note:** Registers PxPDR and PxPL may be used for general purpose storage if the ports are not used.

# **Device Control and Registers**

The operation of the SAE 81C90/91 is controlled via a number of registers. These registers allow initialization and function control, provide status information and configure the message objects. The upper part of the address space provides access to the data buffers of the message objects. The data buffers are ordered sequentially as shown in the table below.

The register map on the next page summarizes the other registers (i.e. except the data registers) ordered by their address, while the following pages describe these registers in more detail from a functional point of view.

**Note:** Locations marked "*Reserved*" in the register map must not be written in initialization mode. This also applies to locations 60<sub>H</sub> through 7F<sub>H</sub>.

# **Data Registers**

| Address         | Function |            |

|-----------------|----------|------------|

| 80 <sub>H</sub> | Byte 0   | Message 0  |

| 81 <sub>H</sub> | Byte 1   |            |

| 82 <sub>H</sub> | Byte 2   |            |

| 83 <sub>H</sub> | Byte 3   |            |

| 84 <sub>H</sub> | Byte 4   |            |

| 85 <sub>H</sub> | Byte 5   |            |

| 86 <sub>H</sub> | Byte 6   |            |

| 87 <sub>H</sub> | Byte 7   |            |

| 88 <sub>H</sub> | Byte 0   | Message 1  |

| 89 <sub>H</sub> | Byte 1   |            |

| :               | :        | :          |

| F6 <sub>H</sub> | Byte 6   | Message 14 |

| F7 <sub>H</sub> | Byte 7   |            |

| F8 <sub>H</sub> | Byte 0   | Message 15 |

| F9 <sub>H</sub> | Byte 1   |            |

| FA <sub>H</sub> | Byte 2   |            |

| FB <sub>H</sub> | Byte 3   |            |

| FC <sub>H</sub> | Byte 4   |            |

| FD <sub>H</sub> | Byte 5   |            |

| FE <sub>H</sub> | Byte 6   |            |

| FF <sub>H</sub> | Byte 7   |            |

# Register Map (ordered by address)

| Addr.           | Reg. Name | Reset           | Addr.           | Reg. Name | Reset           | Addr.           | Reg. Name | Reset           |

|-----------------|-----------|-----------------|-----------------|-----------|-----------------|-----------------|-----------|-----------------|

| 00 <sub>H</sub> | BL1       | 00 <sub>H</sub> | 20 <sub>H</sub> | Reserved  |                 | 40 <sub>H</sub> | DR0H      | UU <sub>H</sub> |

| 01 <sub>H</sub> | BL2       | 00 <sub>H</sub> | 21 <sub>H</sub> | Reserved  |                 | 41 <sub>H</sub> | DR0L      | UU <sub>H</sub> |

| 02 <sub>H</sub> | ОС        | 00 <sub>H</sub> | 22 <sub>H</sub> | Reserved  |                 | 42 <sub>H</sub> | DR1H      | UU <sub>H</sub> |

| 03 <sub>H</sub> | BRP       | 00 <sub>H</sub> | 23 <sub>H</sub> | Reserved  |                 | 43 <sub>H</sub> | DR1L      | UU <sub>H</sub> |

| 04 <sub>H</sub> | RRR1      | 00 <sub>H</sub> | 24 <sub>H</sub> | Reserved  |                 | 44 <sub>H</sub> | DR2H      | UU <sub>H</sub> |

| 05 <sub>H</sub> | RRR2      | 00 <sub>H</sub> | 25 <sub>H</sub> | Reserved  |                 | 45 <sub>H</sub> | DR2L      | UU <sub>H</sub> |

| 06 <sub>H</sub> | RIMR1     | 00 <sub>H</sub> | 26 <sub>H</sub> | Reserved  |                 | 46 <sub>H</sub> | DR3H      | UU <sub>H</sub> |

| 07 <sub>H</sub> | RIMR2     | 00 <sub>H</sub> | 27 <sub>H</sub> | Reserved  |                 | 47 <sub>H</sub> | DR3L      | UU <sub>H</sub> |

| 08 <sub>H</sub> | TRS1      | 00 <sub>H</sub> | 28 <sub>H</sub> | P0PDR     | 00 <sub>H</sub> | 48 <sub>H</sub> | DR4H      | UU <sub>H</sub> |

| 09 <sub>H</sub> | TRS2      | 00 <sub>H</sub> | 29 <sub>H</sub> | P0PR      | XX <sub>H</sub> | 49 <sub>H</sub> | DR4L      | UU <sub>H</sub> |

| 0A <sub>H</sub> | IMSK      | 00 <sub>H</sub> | 2A <sub>H</sub> | P0LR      | 00 <sub>H</sub> | 4A <sub>H</sub> | DR5H      | UU <sub>H</sub> |

| 0B <sub>H</sub> | Reserved  |                 | 2B <sub>H</sub> | Reserved  |                 | 4B <sub>H</sub> | DR5L      | UU <sub>H</sub> |

| 0C <sub>H</sub> | Reserved  |                 | 2C <sub>H</sub> | P1PDR     | 00 <sub>H</sub> | 4C <sub>H</sub> | DR6H      | UU <sub>H</sub> |

| 0D <sub>H</sub> | Reserved  |                 | 2D <sub>H</sub> | P1PR      | XX <sub>H</sub> | 4D <sub>H</sub> | DR6L      | UU <sub>H</sub> |

| 0E <sub>H</sub> | Reserved  |                 | 2E <sub>H</sub> | P1LR      | 00 <sub>H</sub> | 4E <sub>H</sub> | DR7H      | UU <sub>H</sub> |

| 0F <sub>H</sub> | Reserved  |                 | 2F <sub>H</sub> | Reserved  |                 | 4F <sub>H</sub> | DR7L      | UU <sub>H</sub> |

| 10 <sub>H</sub> | MOD       | 00 <sub>H</sub> | 30 <sub>H</sub> | TSR0H     | UU <sub>H</sub> | 50 <sub>H</sub> | DR8H      | UU <sub>H</sub> |

| 11 <sub>H</sub> | INT       | 00 <sub>H</sub> | 31 <sub>H</sub> | TSR0L     | UU <sub>H</sub> | 51 <sub>H</sub> | DR8L      | UU <sub>H</sub> |

| 12 <sub>H</sub> | CTRL      | 00 <sub>H</sub> | 32 <sub>H</sub> | TSR1H     | UU <sub>H</sub> | 52 <sub>H</sub> | DR9H      | UU <sub>H</sub> |

| 13 <sub>H</sub> | Reserved  |                 | 33 <sub>H</sub> | TSR1L     | UU <sub>H</sub> | 53 <sub>H</sub> | DR9L      | UUH             |

| 14 <sub>H</sub> | СС        | 01 <sub>H</sub> | 34 <sub>H</sub> | TSR2H     | UU <sub>H</sub> | 54 <sub>H</sub> | DR10H     | UUH             |

| 15 <sub>H</sub> | TCEC      | 00 <sub>H</sub> | 35 <sub>H</sub> | TSR2L     | UUH             | 55 <sub>H</sub> | DR10L     | UUH             |

| 16 <sub>H</sub> | TCD       | XXH             | 36 <sub>H</sub> | TSR3H     | UUH             | 56 <sub>H</sub> | DR11H     | UU <sub>H</sub> |

| 17 <sub>H</sub> | Reserved  |                 | 37 <sub>H</sub> | TSR3L     | UUH             | 57 <sub>H</sub> | DR11L     | UUH             |

| 18 <sub>H</sub> | TRR1      | 00 <sub>H</sub> | 38 <sub>H</sub> | TSR4H     | UU <sub>H</sub> | 58 <sub>H</sub> | DR12H     | UU <sub>H</sub> |

| 19 <sub>H</sub> | TRR2      | 00 <sub>H</sub> | 39 <sub>H</sub> | TSR4L     | UU <sub>H</sub> | 59 <sub>H</sub> | DR12L     | UU <sub>H</sub> |

| 1A <sub>H</sub> | RRP1      | 00 <sub>H</sub> | 3A <sub>H</sub> | TSR5H     | UU <sub>H</sub> | 5A <sub>H</sub> | DR13H     | UU <sub>H</sub> |

| 1B <sub>H</sub> | RRP2      | 00 <sub>H</sub> | 3B <sub>H</sub> | TSR5L     | UU <sub>H</sub> | 5B <sub>H</sub> | DR13L     | UU <sub>H</sub> |

| 1C <sub>H</sub> | TSCH      | 00 <sub>H</sub> | 3C <sub>H</sub> | TSR6H     | UU <sub>H</sub> | 5C <sub>H</sub> | DR14H     | UU <sub>H</sub> |

| 1D <sub>H</sub> | TSCL      | 00 <sub>H</sub> | 3D <sub>H</sub> | TSR6L     | UU <sub>H</sub> | 5D <sub>H</sub> | DR14L     | UU <sub>H</sub> |

| 1E <sub>H</sub> | Reserved  |                 | 3E <sub>H</sub> | TSR7H     | UU <sub>H</sub> | 5E <sub>H</sub> | DR15H     | UU <sub>H</sub> |

| H               | 110001100 |                 | 11              |           | 11              | ''              |           | 1.1             |

**Note:** The locations marked "UU $_H$ " are not changed upon a reset. After a power on reset they are undefined (XX $_H$ ), of course.

# **Descriptor Registers**

A descriptor register is available for each message object and contains the eleven bits of the message identifier (ID.0 through ID.10), the remote-transmission-request bit (RTR) and the data length code (DLC) of a message.

| DRnH                         | 7     | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------------------------------|-------|------|------|------|------|------|------|------|

| Address: XX <sub>H</sub>     | ID.10 | ID.9 | ID.8 | ID.7 | ID.6 | ID.5 | ID.4 | ID.3 |

| Reset Value: UU <sub>H</sub> | rw    | rw   | rw   | rw   | rw   | rw   | rw   | rw   |

|                              |       |      |      |      |      |      |      |      |

| DRnL                         | 7     | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| Address: XX <sub>H</sub>     | ID.2  | ID.1 | ID.0 | RTR  |      | DI   | -C   |      |

| Reset Value: UU <sub>H</sub> | rw    | rw   | rw   | rw   | rw   | rw   | rw   | rw   |

| Bit(field) | Function                                                                                                                                                         |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DLC        | Data Length Code Defines the number of data bytes of message n. Defined values are 00001000, i.e. 08 bytes. Other values are not permitted.                      |

| RTR        | Remote Transmission Request Bit '0': This message operates as a data frame. '1': This message operates as a remote frame. Note: See description and table below. |

| ID.10-0    | Identifier Identifier associated with message n, controls the acceptance of received frames and is inserted into transmitted frames.                             |

n = 0...15

Bit RTR determines the function of the corresponding message object when it is transmitted, and its reaction on a received data frame or remote frame.

The table below summarizes the message object's behaviour in the different cases.

| RTR bit                         | Object is transmitted                                                 | Matching Data Frame received                    | Matching Remote Frame received              |

|---------------------------------|-----------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------|

| ' <b>0</b> '<br>(data<br>frame) | The message object is transmitted as a standard data frame.           | The data frame is stored in the message object. | The remote frame is ignored.                |

| '1'<br>(remote<br>frame)        | The message object is transmitted as a remote frame (i.e. a request). | The data frame is ignored and not stored.       | The message object is sent as a data frame. |

**Note:** For the transmission of remote frames (RTR = 1) the data-length-code should be set to '0'.

# **Descriptor Register Arrangement**

| Address         | Function  |                                           |

|-----------------|-----------|-------------------------------------------|

| 40 <sub>H</sub> | High Byte | Descriptor Register for Message Object 0  |

| 41 <sub>H</sub> | Low Byte  |                                           |

| 42 <sub>H</sub> | High Byte | Descriptor Register for Message Object 1  |

| 43 <sub>H</sub> | Low Byte  |                                           |

| :               | :         | · ·                                       |

| 5C <sub>H</sub> | High Byte | Descriptor Register for Message Object 14 |

| 5D <sub>H</sub> | Low Byte  |                                           |

| 5E <sub>H</sub> | High Byte | Descriptor Register for Message Object 15 |

| 5F <sub>H</sub> | Low Byte  |                                           |

# **Control Register Summary**

| Register Name | Address         | Function                          | Reset<br>Value  | Read<br>Write <sup>1)</sup> |

|---------------|-----------------|-----------------------------------|-----------------|-----------------------------|

| OC            | 02 <sub>H</sub> | Output-control register           | 00 <sub>H</sub> | r/w, I                      |

| CC            | 14 <sub>H</sub> | Clock-control register            | 01 <sub>H</sub> | wo                          |

| CTRL          | 12 <sub>H</sub> | Control register                  | 00 <sub>H</sub> | r/w                         |

| MOD           | 10 <sub>H</sub> | Mode/status register              | 00 <sub>H</sub> | r/w                         |

| INT           | 11 <sub>H</sub> | Interrupt register                | 00 <sub>H</sub> | r/w                         |

| IMSK          | 0A <sub>H</sub> | Interrupt-mask register           | 00 <sub>H</sub> | r/w                         |

| BL1           | 00 <sub>H</sub> | Bit-length register 1             | 00 <sub>H</sub> | r/w, I                      |

| BL2           | 01 <sub>H</sub> | Bit-length register 2             | 00 <sub>H</sub> | r/w, I                      |

| BRP           | 03 <sub>H</sub> | Baud-rate prescaler               | 00 <sub>H</sub> | wo, I                       |

| RRR1          | 04 <sub>H</sub> | Receive-ready register 1          | 00 <sub>H</sub> | r/w                         |

| RRR2          | 05 <sub>H</sub> | Receive-ready register 2          | 00 <sub>H</sub> | r/w                         |

| RIMR1         | 06 <sub>H</sub> | Receive-interrupt-mask register 1 | 00 <sub>H</sub> | r/w                         |

| RIMR2         | 07 <sub>H</sub> | Receive-interrupt-mask register 2 | 00 <sub>H</sub> | r/w                         |

| TRSR1         | 08 <sub>H</sub> | Transmit-request-set register 1   | 00 <sub>H</sub> | r/w                         |

| TRSR2         | 09 <sub>H</sub> | Transmit-request-set register 2   | 00 <sub>H</sub> | r/w                         |

| TRRR1         | 18 <sub>H</sub> | Transmit-request-reset register 1 | 00 <sub>H</sub> | wo                          |

| TRRR2         | 19 <sub>H</sub> | Transmit-request-reset register 2 | 00 <sub>H</sub> | wo                          |

| RRPR1         | 1A <sub>H</sub> | Remote-request-pending register 1 | 00 <sub>H</sub> | ro                          |

| RRPR2         | 1B <sub>H</sub> | Remote-request-pending register 2 | 00 <sub>H</sub> | ro                          |

| TSCH          | 1C <sub>H</sub> | Time-Stamp counter high byte      | 00 <sub>H</sub> | r/w                         |

| TSCL          | 1D <sub>H</sub> | Time-Stamp counter low byte       | 00 <sub>H</sub> | r/w                         |

| TCEC          | 15 <sub>H</sub> | Transmit-check error counter      | 00 <sub>H</sub> | r/w                         |

| TCD           | 16 <sub>H</sub> | Transmit-check data register      | XX              | ro                          |

| P0PDR         | 28 <sub>H</sub> | Port 0 port-direction register    | 00 <sub>H</sub> | r/w                         |

| P1PDR         | 2C <sub>H</sub> | Port 1 port-direction register    | 00 <sub>H</sub> | r/w                         |

| P0LR          | 2A <sub>H</sub> | Port 0 latch register             | 00 <sub>H</sub> | r/w                         |

| P1LR          | 2E <sub>H</sub> | Port 1 latch register             | 00 <sub>H</sub> | r/w                         |

| P0PR          | 29 <sub>H</sub> | Port 0 pin register               | XX <sub>H</sub> | ro                          |

| P1PR          | 2D <sub>H</sub> | Port 1 pin register               | XX <sub>H</sub> | ro                          |

Note: 1) ro: read only, r/w: read and write access, wo: write only, I: access only with bit IM set.

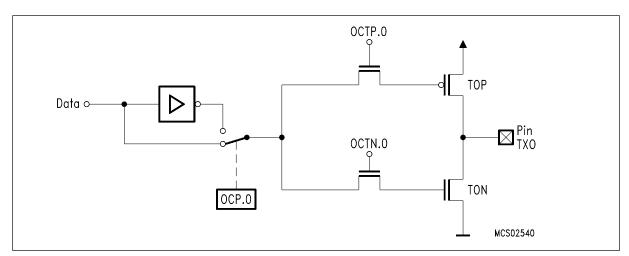

# **Output-Control Register**

The output drivers of the SAE 81C90/91's transmit pins (TXn) can be individually configured. Thus they can be adapted to the requirements of the external bs system.

| OC                           | 7     | 6     | 5    | 4     | 3     | 2    | 1  | 0  |  |

|------------------------------|-------|-------|------|-------|-------|------|----|----|--|

| Address: 02 <sub>H</sub>     | OCTP1 | OCTN1 | OCP1 | OCTP0 | OCTN0 | OCP0 | oc | M  |  |

| Reset Value: 00 <sub>H</sub> | rw    | rw    | rw   | rw    | rw    | rw   | rw | rw |  |

| Bit(field) | Function                                                                                                                                                                         |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ОСМ        | Output Mode  '0X': Normal Mode: TX0 = Bit Sequence, TX1 = Bit Sequence.  '10': Test Mode: TX0 = Bit Sequence, TX1 = RX0.  '11': Clock Mode: TX0 = Bit Sequence, TX1 = Bit Clock. |  |  |  |  |  |

| OCPn       | Output Polarity '0': Output is driven directly with CAN data. '1': Output is driven with inverted CAN data.                                                                      |  |  |  |  |  |

| OCTNn      | Negative Output Transistor Control '0': The low side output transistor TnN is disabled. '1': The low side output transistor TnN drives the pin according to data.                |  |  |  |  |  |

| OCTPn      | Positive Output Transistor Control '0': The high side output transistor TnP is disabled. '1': The high side output transistor TnP drives the pin according to data.              |  |  |  |  |  |

n = 0, 1

Note: This register can only be written when bit IM (MOD.0) is set.

Figure 5

Output Control Circuitry

# **Output Programming**

| OCTP.n | OCTN.n | OCP.n | Data          | TnP | TnN | TXn-Level |

|--------|--------|-------|---------------|-----|-----|-----------|

| 0      | 0      | 0     | 0 = dominant  | OFF | OFF | float     |

| 0      | 0      | 0     | 1 = recessive | OFF | OFF | float     |

| 0      | 0      | 1     | 0             | OFF | OFF | float     |

| 0      | 0      | 1     | 1             | OFF | OFF | float     |

| 0      | 1      | 0     | 0             | OFF | ON  | LOW       |

| 0      | 1      | 0     | 1             | OFF | OFF | float     |

| 0      | 1      | 1     | 0             | OFF | OFF | float     |

| 0      | 1      | 1     | 1             | OFF | ON  | LOW       |

| 1      | 0      | 0     | 0             | OFF | OFF | float     |

| 1      | 0      | 0     | 1             | ON  | OFF | HIGH      |

| 1      | 0      | 1     | 0             | ON  | OFF | HIGH      |

| 1      | 0      | 1     | 1             | OFF | OFF | float     |

| 1      | 1      | 0     | 0             | OFF | ON  | LOW       |

| 1      | 1      | 0     | 1             | ON  | OFF | HIGH      |

| 1      | 1      | 1     | 0             | ON  | OFF | HIGH      |

| 1      | 1      | 1     | 1             | OFF | ON  | LOW       |

TnP is the output transistor switching to  $V_{\rm DD}$ , TnN switches to  $V_{\rm SS}$ .

TXn is the output level at the transmit pin.

# **Clock Control Register**

The Clock Control Register determines the output frequency at pin CLKOUT which is derived from the oscillator frequency.

| CCR                          | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------|---|---|---|---|---|---|---|---|

| Address: 14 <sub>H</sub>     | - | - | - | - |   | С | C |   |

| Reset Value: 01 <sub>H</sub> | - | - | - | - | W | W | W | W |

| Bit(field) | Function                                                         |

|------------|------------------------------------------------------------------|

| CC         | Clock Output Control                                             |

|            | '0000': $f_{CLKOUT} = f_{OSC}$                                   |

|            | '0001': $f_{CLKOUT} = f_{OSC} / 2$                               |

|            | '0010': $f_{CLKOUT} = f_{OSC} / 4$                               |

|            | '0011': $f_{CLKOUT} = f_{OSC} / 6$                               |

|            | '0100': $f_{CLKOUT} = f_{OSC} / 8$                               |

|            | '0101': $f_{CLKOUT} = f_{OSC} / 10$                              |

|            | '0110': $f_{CLKOUT} = f_{OSC} / 12$                              |

|            | '0111': $f_{CLKOUT} = f_{OSC} / 14$                              |

|            | '1XXX': f <sub>CLKOUT</sub> = LOW (clock output is switched off) |

The Clock Control Register requires a special protocol for writing in order to prevent the clock output from being changed inadvertently:

- Step 1: Write 80<sub>H</sub> to CC

- Step 2: Write desired value to CC (bits 7...4 must be '0000')

Note: Not defined bit positions must be '0' for write accesses.

# **Control Register**

| CTRL                         | 7  | 6   | 5  | 4    | 3    | 2   | 1   | 0  |   |

|------------------------------|----|-----|----|------|------|-----|-----|----|---|

| Address: 12 <sub>H</sub>     | RX | TST | TS | SP . | TSOV | SME | TCE | ММ |   |

| Reset Value: 00 <sub>H</sub> | rw | rw  | rw | rw   | rw   | rw  | rw  | rw | _ |

| Bit(field) | Function                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ММ         | Monitor Mode  '0': Message object 0 operates like all other objects.  '1': Message object 0 receives all identifiers that are not accepted by other objects (corresponds to a Basic CAN receive register).                                                                                                                                            |  |  |  |  |  |

| TCE        | Transmit Check Enable  '0': If the transmit check detects an error, there is no intervention.  '1': If the transmit check detects an error, the message is invalidated by an error frame and the error counter TCEC is incremented by 1.  If the counter reaches 4, the Bus Off status is initiated and, if enabled, an interrupt (TCI) is generated. |  |  |  |  |  |

| SME        | Sleep Mode Enable  '0': Normal operation.  '1': The sleep mode is enabled: the crystal oscillator is deactivated, all other activities are inhibited.  The wake up is done by a reset signal or by an active signal at the CS pin or by an input edge going from recessive to dominant at pin Rx0 or Rx1.                                             |  |  |  |  |  |

| TSOV       | Time Stamp Overflow '0': There has been no overflow '1': There was at least one overflow of the time-stamp timer.                                                                                                                                                                                                                                     |  |  |  |  |  |

| TSP        | <b>Time Stamp Prescaler</b> (Defines the input clock of the time-stamp timer) '00': $f_{\rm BL}$ / 32 '01': $f_{\rm BL}$ / 64 '10': $f_{\rm BL}$ / 128 '11': $f_{\rm BL}$ / 256 (For $f_{\rm BL}$ see baud-rate prescaler BRP).                                                                                                                       |  |  |  |  |  |

| TST        | Time Stamp Test  '0': The prescaler is activated.  '1': The time-stamp prescaler is deactivated.  (Only for testing purposes, bit IM = MOD.0 must be set to '1').                                                                                                                                                                                     |  |  |  |  |  |

| RX         | Input Monitor RX This bit monitors the actual state of the digital input pin RX0.                                                                                                                                                                                                                                                                     |  |  |  |  |  |

# Mode/Status-Register

| MOD                          | 7   | 6  | 5  | 4   | 3   | 2  | 1   | 0  |   |

|------------------------------|-----|----|----|-----|-----|----|-----|----|---|

| Address: 10 <sub>H</sub>     | ADE | RS | TC | TWL | RWL | BS | RES | IM | ] |

| Reset Value: 00 <sub>H</sub> | rw  | r  | r  | r   | r   | r  | rw  | rw | _ |

| Bit(field) | Function                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| IM         | Init Mode  '0': Normal mode.  '1': Initialization mode: write access to the configuration registers BL1, BL2, OC, BRP is enabled. If the bit stays set, the chip enters the normal mode, with enabled access to the configuration registers. If this bit is set in conjunction with bit RES a hard software reset is activated. |  |  |  |  |  |  |

| RES        | Reset Request '0': Normal mode. '1': The chip enters the reset state: - if bit IM = '0' a soft software reset takes place if bit IM = '1' a hard software reset takes place. Further details see below.                                                                                                                         |  |  |  |  |  |  |

| BS         | Bus State (read only) '0': Normal mode. '1': Bus Off state, the IC does not participate in bus activities.                                                                                                                                                                                                                      |  |  |  |  |  |  |

| RWL        | Receiver Warning Level (read only)  '0': Receive-error counter below 96.  '1': Receive-error counter equal or above 96.                                                                                                                                                                                                         |  |  |  |  |  |  |

| TWL        | Transmit Warning Level (read only) '0': Transmit-error counter below 96. '1': Transmit-error counter equal or above 96.                                                                                                                                                                                                         |  |  |  |  |  |  |

| тс         | Transmission Complete (read only)  '0': The last transmission request is not yet executed successfully.  '1': The last transmission request was executed successfully.                                                                                                                                                          |  |  |  |  |  |  |

| RS         | Receive State (read only)  '0': No reception active.  '1': Currently the SAE 81C90/91 is in receive mode.                                                                                                                                                                                                                       |  |  |  |  |  |  |

| ADE        | Auto Decrement Enable  '0': No automatic address decrement.  '1': With every read or write access using the serial synchronous interface SI the address is automatically decremented by one. So data can be accessed sequentially without the need of writing a new address.                                                    |  |  |  |  |  |  |

#### **Notes on Bit TC**

Scanning this bit is particularly useful if only one transmission is active. If there are several transmission jobs at the same time, it is better to scan the transmit-request register, because bit TC may possibly only be set very briefly between acknowledgment of the previous message and the start of the next one.

#### Notes on Bit RES and IM and reset modes

There are three different reset modes implemented in the SAE 81C90/91:

hardware reset (activated by low level on pin RES)

hard software reset (activated by setting both bits RES and IM to 1)

soft software reset (activated by setting bit RES to 1 and bit IM to 0)

The only difference between hardware and hard software reset affect bits RES and IM, that are not changed by software reset.

With soft software reset the registers RRR1, RRR2, TRSR1, TRSR2, RRPR1 and RRPR2 are cleared, all bus activities are stopped, the error counters are <u>not</u> cleared, the Bus Off state is cancelled only after 128 idle phases (according to the CAN protocol 1 idle phase = 11 recessive bits in sequence). Simply spoken a soft software reset interrupts and cancels all bus activities and - if necessary - recovers from Bus Off state.

#### **Notes on Bit RS**

Bit RS directly reflects the internal status.

RS is '0' during transmission or when the SAE 81C90/91 is idle.

RS is '1' during reception or during the synchronization after a reset.

# **Interrupt Register**

| INT                          | 7   | 6   | 5   | 4    | 3   | 2   | 1  | 0  |   |

|------------------------------|-----|-----|-----|------|-----|-----|----|----|---|

| Address: 11 <sub>H</sub>     | TCI | EPI | BOI | WUPI | RFI | WLI | TI | RI |   |

| Reset Value: 00 <sub>H</sub> | rw  | rw  | rw  | rw   | rw  | rw  | rw | rw | _ |

| Bit(field) | Function                                                                                                                                                                                           |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RI         | Receive Interrupt After a valid message has been received and filed, this bit is set and an interrupt generated. This bit will remain set until all bits of the registers RRR1 and RRR2 are reset. |

| TI         | Transmit Interrupt This bit is set and an interrupt generated as soon as a transmit request has been processed.                                                                                    |

| WLI        | Warning Level Interrupt If at least one of the two error counters is greater than or equals 96, this bit is set and an interrupt generated.                                                        |

| RFI        | Remote Frame Interrupt This interrupt is generated after reception of a remote frame.                                                                                                              |

| WUPI       | Wake Up Interrupt After a wake-up this bit is set and an interrupt generated.                                                                                                                      |

| BOI        | Bus Off Interrupt This bit is set and an interrupt generated when the Bus Off status is entered.                                                                                                   |

| EPI        | Error Passive Interrupt If at least one of the two error counters is greater than or equals 128, this bit is set and an interrupt generated.                                                       |

| TCI        | Transmit Check Interrupt If the transmit-check error counter reaches 4, this bit is set and an interrupt generated.                                                                                |

**Note:** All bits of this register must be reset by software. This is done by writing '0' to the respective bit location, writing '1' has no effect.

An interrupt is only generated if the respective IMSK bit is set. The bits in this register are set independent of register IMSK (see below).

The interrupt output is active for at least one bit time. The interrupt output is deactivated when all enabled request bits are cleared. A request bit is enabled by setting its corresponding mask bit. Masked request bits do not activate the interrupt output.

# Interrupt-Mask Register

These mask bits determine if an event activates the INT pin. They do not influence the INT register.

| IMSK                         | 7    | 6    | 5    | 4     | 3    | 2    | 1   | 0   |   |

|------------------------------|------|------|------|-------|------|------|-----|-----|---|

| Address: 0A <sub>H</sub>     | ETCI | EEPI | EBOI | EWUPI | ERFI | EWLI | ETI | ERI |   |

| Reset Value: 00 <sub>H</sub> | rw   | rw   | rw   | rw    | rw   | rw   | rw  | rw  | - |

| Bit(field) | Function                                                                                                                                   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| ERI        | Enable Receive Interrupt '0': No receive interrupt enabled. '1': Receive interrupts are enabled.                                           |

| ETI        | Enable Transmit Interrupt '0': No transmit interrupt enabled. '1': Completed transmit jobs generate interrupts.                            |

| EWLI       | Enable Warning Level Interrupt '0': No warning level interrupt enabled. '1': There is an interrupt when the warning level is reached.      |

| ERFI       | Enable Remote Frame Interrupt '0': No remote frame interrupt enabled. '1': A receive interrupt is generated after receiving a remote frame |

| EWUPI      | Enable Wake Up Interrupt '0': No wake up interrupt enabled. '1': Wake-up interrupt is enabled.                                             |

| EBOI       | Enable Bus Off Interrupt '0': No bus off interrupt enabled. '1': Bus off interrupt is enabled.                                             |

| EEPI       | Enable Error Passive Interrupt '0': No error passive interrupt enabled. '1': Error passive interrupt is enabled.                           |

| ETCI       | Enable Transmit Check Error Interrupt '0': No transmit check interrupt enabled. '1': Transmit-check error interrupt is enabled.            |

# **Bit-Length Registers**

| BL1                          | 7   | 6  | 5   | 4  | 3  | 2  | 1          | 0  |

|------------------------------|-----|----|-----|----|----|----|------------|----|

| Address: 00 <sub>H</sub>     | SAM |    | TS2 |    |    | TS | <b>S</b> 1 |    |

| Reset Value: 00 <sub>H</sub> | rw  | rw | rw  | rw | rw | rw | rw         | rw |

| Bit(field) | Function                                                                                                                                                                    |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TS1        | Length of Timing Segment 1 (TSeg1). $t_{TSeg1} = (TS1 + 1) \times t_{SCL}$ . For $t_{SCL}$ see baud-rate prescaler BRP.                                                     |

| TS2        | Length of Timing Segment 2 (TSeg2). $t_{TSeg2} = (TS2 + 1) \times t_{SCL}$ . For $t_{SCL}$ see baud-rate prescaler BRP.                                                     |

| SAM        | Sample Rate '0': Input signal is sampled once per bit. '1': Input signal is sampled three times per bit. Note: Bit SAM should only be set to '1' using very low baud rates. |

| BL2                          | 7    | 6  | 5 | 4 | 3 | 2  | 1  | 0  |

|------------------------------|------|----|---|---|---|----|----|----|

| Address: 01 <sub>H</sub>     | IPOL | DI | _ | _ | _ | SM | SJ | IW |

| Reset Value: 00 <sub>H</sub> | rw   | rw | - | - | - | rw | rw | rw |

| Bit(field) | Function                                                                                                                                                                                                       |  |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| SJW        | Maximum Synchronization Jump Width. $t_{\text{SJWidth}} = (\text{SJW} + 1) \times t_{\text{SCL}}$ . For $t_{\text{SCL}}$ see baud-rate prescaler BRP.                                                          |  |  |  |  |  |  |

| SM         | Speed Mode (Defines edge used for synchronization)  '0': Recessive to dominant is used.                                                                                                                        |  |  |  |  |  |  |

|            | '1': Both edges are used.  Note: According to the CAN specification this bit should not be set to '1'.                                                                                                         |  |  |  |  |  |  |

| DI         | Digital Input '0': The input signal is applied to the input comparator. $^{1)}$ '1': The input signal on pin RX0 is evaluated digitally. The input comparator is inactive. Pin RX1 should be on $V_{\rm SS}$ . |  |  |  |  |  |  |

| IPOL       | Input Polarity '0': The input level remains unaltered. '1': The input level is inverted.                                                                                                                       |  |  |  |  |  |  |

Note: Not defined bit positions must be '0' for write accesses.

The Bit Length Registers BL1 and BL2 can only written while bit IM (MOD.0) is set.

<sup>&</sup>lt;sup>1)</sup> If the bus lines work according to the ISO specification, additional circuitry is necessary for interconnection of the input comparator to the bus lines.

# **Baud Rate Prescaler Register**

The register is not readable and can only be written when bit IM (MOD.0) is set.

| BRPR                         | 7 | 6 | 5 | 4 | 3  | 2  | 1 | 0 |

|------------------------------|---|---|---|---|----|----|---|---|

| Address: 03 <sub>H</sub>     | _ | _ |   |   | ВГ | RP |   |   |

| Reset Value: 00 <sub>H</sub> | - | - | W | W | W  | W  | W | W |

| Bit(field) | Function                                                                            |

|------------|-------------------------------------------------------------------------------------|

| BRP        | Baud Rate Prescaler                                                                 |

|            | This prescaler determines the period of the system clock:                           |

|            | $t_{SCL} = (BRP + 1) \times 2 \times t_{OSC}$ , where $t_{OSC} = 1 / f_{crystal}$ . |

Note: Not defined bit positions must be '0' for write accesses.

The bit length  $t_{\rm BL}$  is computed as follows:

$$t_{\text{BL}} = t_{\text{TSeg1}} + t_{\text{TSeg2}} + 1 t_{\text{SCL}}$$

The baudrate BR can be computed with the following formula:

$$BR = f_{crystal} / (2 x (BRP + 1) x (TS1 + TS2 + 3))$$

Note: BRP see Baud Rate Prescaler Register

TS1 see Bit Length Register 1

TS2 see Bit Length Register 1

# **Receive-Ready Registers**

| RRR2                         | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   |

|------------------------------|------|------|------|------|------|------|-----|-----|

| Address: 05 <sub>H</sub>     | RR15 | RR14 | RR13 | RR12 | RR11 | RR10 | RR9 | RR8 |

| Reset Value: 00 <sub>H</sub> | rw   | rw   | rw   | rw   | rw   | rw   | rw  | rw  |

| RRR1                         | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   |

| Address: 04 <sub>H</sub>     | RR7  | RR6  | RR5  | RR4  | RR3  | RR2  | RR1 | RR0 |

| Reset Value: 00 <sub>H</sub> | rw   | rw   | rw   | rw   | rw   | rw   | rw  | rw  |

| Bit(field) | Function                                                     |

|------------|--------------------------------------------------------------|

| RRn        | Receive Ready Bit                                            |

|            | '0': No new message received in object n.                    |

|            | '1': A new message has been received and stored in object n. |

These register bits can be reset by writing '0' to the respective bit, writing '1' has no effect. Bit RRn is set when a message has arrived and been written into the memory location of message n. Setting this bit by hardware can generate a receive interrupt, which can be blocked by bit RIMn in the receive-interrupt-mask register.

Bits RRn must be reset by software.

#### **Receive-Interrupt-Mask Registers**

Setting bit RIMn enables a receive interrupt to be generated if the receive-ready bit RRn has been set, i.e. a message has arrived and was written into the memory location of message n.

| RIMR2                        | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|------------------------------|-------|-------|-------|-------|-------|-------|------|------|

| Address: 07 <sub>H</sub>     | RIM15 | RIM14 | RIM13 | RIM12 | RIM11 | RIM10 | RIM9 | RIM8 |

| Reset Value: 00 <sub>H</sub> | rw    | rw    | rw    | rw    | rw    | rw    | rw   | rw   |

| RIMR1                        | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

| Address: 06 <sub>H</sub>     | RIM7  | RIM6  | RIM5  | RIM4  | RIM3  | RIM2  | RIM1 | RIM0 |

| Reset Value: 00 <sub>H</sub> | rw    | rw    | rw    | rw    | rw    | rw    | rw   | rw   |

| Bit(field) | Function                                                                 |

|------------|--------------------------------------------------------------------------|

| RIMn       | Receive Interrupt Mask Bit                                               |

|            | '0': No interrupt upon reception of object n.                            |

|            | '1': When a new message is stored in object n an interrupt is generated. |

**Note:** Bit ERI in the interrupt-mask register IM blocks all receive interrupts, even if bits RIMn are set.

# **Transmit Request Registers**

The Transmit Request Set Registers provide a transmission request bit (TRSn) for each message object. Setting a transmission request bit causes the respective message x to be transmitted. The bit is cleared by hardware after transmission. Several bits can be set simultaneously. In this way all messages whose request bits are set are transmitted in turn, starting with the memory location with the highest number.

**Note:** A transmission request bit is set by writing '1' to the respective bit location (TRSn). Writing '0' has no effect.

| TRSR2                        | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|------------------------------|-------|-------|-------|-------|-------|-------|------|------|

| Address: 09 <sub>H</sub>     | TRS15 | TRS14 | TRS13 | TRS12 | TRS11 | TRS10 | TRS9 | TRS8 |

| Reset Value: 00 <sub>H</sub> | rw    | rw    | rw    | rw    | rw    | rw    | rw   | rw   |

|                              |       |       |       |       |       |       |      |      |

| TRSR1                        | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

| Address: 08 <sub>H</sub>     | TRS7  | TRS6  | TRS5  | TRS4  | TRS3  | TRS2  | TRS1 | TRS0 |

| Reset Value: 00 <sub>H</sub> | rw    | rw    | rw    | rw    | rw    | rw    | rw   | rw   |

| Bit(field) | Function                                               |

|------------|--------------------------------------------------------|

| TRSn       | Transmit Request Set Bit                               |

|            | '0': No change of the respective transmit request bit. |

|            | '1': The respective transmit request bit is cleared.   |

n = 0...15

**The Transmit Request Reset Registers** provide a transmit request reset bit (TRRn) for each transmit request bit TRSn, i.e. for each message object.

Writing '1' to a TRRn bit clears the corresponding transmission request bit TRSn. This causes a transmission request, initiated by the corresponding bit TRSn, to be cancelled, provided that it is not currently processed.

This scheme avoids conflicts when writing to register bits while they are cleared by hardware because of a completed transmission.

Note: Registers TRRRx cannot be read.

| TRRR2                        | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|------------------------------|-------|-------|-------|-------|-------|-------|------|------|

| Address: 19 <sub>H</sub>     | TRR15 | TRR14 | TRR13 | TRR12 | TRR11 | TRR10 | TRR9 | TRR8 |

| Reset Value: 00 <sub>H</sub> | W     | W     | W     | W     | W     | W     | W    | W    |

|                              |       |       |       |       |       |       |      |      |

| TRRR1                        | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

| Address: 18 <sub>H</sub>     | TRR7  | TRR6  | TRR5  | TRR4  | TRR3  | TRR2  | TRR1 | TRR0 |

| Reset Value: 00 <sub>H</sub> | W     | W     | W     | W     | W     | W     | W    | W    |

| Bit(field) | Function                                               |

|------------|--------------------------------------------------------|

| TRRx       | Transmit Request Reset Bit                             |

|            | '0': No change of the respective transmit request bit. |

|            | '1': The respective transmit request bit is cleared.   |

# **Remote-Request-Pending Registers**

| RRPR2                        | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|------------------------------|-------|-------|-------|-------|-------|-------|------|------|

| Address: 1B <sub>H</sub>     | RRP15 | RRP14 | RRP13 | RRP12 | RRP11 | RRP10 | RRP9 | RRP8 |

| Reset Value: 00 <sub>H</sub> | r     | r     | r     | r     | r     | r     | r    | r    |

|                              |       |       |       |       |       |       |      |      |

| RRPR1                        | 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

| Address: 1A <sub>H</sub>     | RRP7  | RRP6  | RRP5  | RRP4  | RRP3  | RRP2  | RRP1 | RRP0 |

| Reset Value: 00 <sub>H</sub> | r     | r     | r     | r     | r     | r     | r    | r    |

| Bit(field) | Function                                                                       |  |  |  |  |  |  |

|------------|--------------------------------------------------------------------------------|--|--|--|--|--|--|

| RRPn       | Remote Request Pending Bit                                                     |  |  |  |  |  |  |

|            | '0': No remote request pending.                                                |  |  |  |  |  |  |

|            | '1': A remote request (remote frame) for message n was received but is not yet |  |  |  |  |  |  |

|            | answered by the transmission of the corresponding data frame.                  |  |  |  |  |  |  |

n = 0...15

# **Message Time Stamp**

This mechanism stores the time at which a specific message was received, i.e. it assigns a time stamp to that message. For this purpose the contents of the free-running time stamp counter TSC is copied to the time stamp register TSRn of the respective message object upon reception of this message.

The Time Stamp Counter Registers provide access to the free-running time stamp counter.

| TSCH                         | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|------------------------------|--------|--------|--------|--------|--------|--------|-------|-------|

| Address: 1C <sub>H</sub>     | TSC.15 | TSC.14 | TSC.13 | TSC.12 | TSC.11 | TSC.10 | TSC.9 | TSC.8 |

| Reset Value: 00 <sub>H</sub> | rw     | rw     | rw     | rw     | rw     | rw     | rw    | rw    |

| TSCL                         | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

| Address: 1D <sub>H</sub>     | TSC.7  | TSC.6  | TSC.5  | TSC.4  | TSC.3  | TSC.2  | TSC.1 | TSC.0 |

| Reset Value: 00 <sub>H</sub> | rw     | rw     | rw     | rw     | rw     | rw     | rw    | rw    |

| Bit(field) | Function                                                 |

|------------|----------------------------------------------------------|

| TSC        | Time Stamp Counter                                       |

|            | Current contents of the free running time stamp counter. |

**The Time-Stamp Registers** are available for each of message objects 0...7 (see table below) and contain the time-stamp of the corresponding message. These registers can only be read.

| TSRnH                        | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|------------------------------|--------|--------|--------|--------|--------|--------|-------|-------|

| Address: 3X <sub>H</sub>     | TSn.15 | TSn.14 | TSn.13 | TSn.12 | TSn.11 | TSn.10 | TSn.9 | TSn.8 |

| Reset Value: UU <sub>H</sub> | r      | r      | r      | r      | r      | r      | r     | r     |

|                              |        |        |        |        |        |        |       |       |

| TSRnL                        | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

| Address: 3X <sub>H</sub>     | TSn.7  | TSn.6  | TSn.5  | TSn.4  | TSn.3  | TSn.2  | TSn.1 | TSn.0 |

| Reset Value: UU <sub>H</sub> | r      | r      | r      | r      | r      | r      | r     | r     |

| Bit(field) | Function                                                             |

|------------|----------------------------------------------------------------------|

| TSn        | Time Stamp n                                                         |

|            | A 16-bit timer value to identify the time of reception of message n. |

n = 0...7

# **Time Stamp Register Table**

| Address         | Function  |              |

|-----------------|-----------|--------------|

| 30 <sub>H</sub> | High Byte | Time-Stamp 0 |

| 31 <sub>H</sub> | Low Byte  |              |

| 32 <sub>H</sub> | High Byte | Time-Stamp 1 |

| 33 <sub>H</sub> | Low Byte  |              |

| :               | :         | :            |

| 3C <sub>H</sub> | High Byte | Time-Stamp 6 |

| 3D <sub>H</sub> | Low Byte  |              |

| 3E <sub>H</sub> | High Byte | Time-Stamp 7 |

| 3F <sub>H</sub> | Low Byte  |              |

# **Transmit Check Error Counter**

| TCEC                         | 7 | 6 | 5 | 4 | 3 | 2  | 1     | 0  |

|------------------------------|---|---|---|---|---|----|-------|----|

| Address: 15 <sub>H</sub>     | - | - | - | - | - |    | TCECV |    |

| Reset Value: 00 <sub>H</sub> | - | - | - | - | - | rw | rw    | rw |

| Bit(field) | Function                                                                      |

|------------|-------------------------------------------------------------------------------|

| TCECV      | Transmit Check Error Counter Value                                            |

|            | Number of errors detected by the transmit check unit.                         |

|            | When a count of 4 is reached an interrupt is generated if enabled.            |

|            | If bit TCE (CTRL.1) is set to '1' the Bus Off status is entered in this case. |

Note: Not defined bit positions must be '0' for write accesses.

# **Transmit Check Data Register**

This register supports an error analysis when a transmit check error is encountered. Reading TCD provides the byte which was actually being sent when the error occurred.

| TCD                          | 7 | 6 | 5 | 4    | 3    | 2 | 1 | 0 |  |

|------------------------------|---|---|---|------|------|---|---|---|--|

| Address: 16 <sub>H</sub>     |   |   |   | Data | Byte |   |   |   |  |

| Reset Value: XX <sub>H</sub> | r | r | r | r    | r    | r | r | r |  |

| Bit(field) | Function                                                                                   |

|------------|--------------------------------------------------------------------------------------------|

| Data Byte  | The data byte which was attempted to be sent while a transmit check error was encountered. |

# **Port Control Registers**

These registers control the parallel ports P0 and P1 which are provided in the SAE 81C90.

**The Port Direction Registers PxPDR** select each port pin separately for input (PxPDR.n='0') or output (PxPDR.n='1'). After reset the ports are switched as inputs.

| P1PDR                        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Address: 2C <sub>H</sub>     | P1PD.7 | P1PD.6 | P1PD.5 | P1PD.4 | P1PD.3 | P1PD.2 | P1PD.1 | P1PD.0 |

| Reset Value: 00 <sub>H</sub> | rw     |

| P0PDR                        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

| Address: 28 <sub>H</sub>     | P0PD.7 | P0PD.6 | P0PD.5 | P0PD.4 | P0PD.3 | P0PD.2 | P0PD.1 | P0PD.0 |

| Reset Value: 00 <sub>H</sub> | rw     |

The Port Latch Registers PxLR store the output data for those port pins that are switched to output.

| P1LR                         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address: 2E <sub>H</sub>     | P1L.7 | P1L.6 | P1L.5 | P1L.4 | P1L.3 | P1L.2 | P1L.1 | P1L.0 |

| Reset Value: 00 <sub>H</sub> | rw    |

| P0LR                         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| Address: 2A <sub>H</sub>     | P0L.7 | P0L.6 | P0L.5 | P0L.4 | P0L.3 | P0L.2 | P0L.1 | P0L.0 |

| Reset Value: 00 <sub>H</sub> | rw    |

**The Port Pin Registers PxPR** provide the current level of the port pins. These registers can only be read.

| P1PR                         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address: 2D <sub>H</sub>     | P1P.7 | P1P.6 | P1P.5 | P1P.4 | P1P.3 | P1P.2 | P1P.1 | P1P.0 |

| Reset Value: 00 <sub>H</sub> | r     | r     | r     | r     | r     | r     | r     | r     |

| P0PR                         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| Address: 29 <sub>H</sub>     | P0P.7 | P0P.6 | P0P.5 | P0P.4 | P0P.3 | P0P.2 | P0P.1 | P0P.0 |

| Reset Value: 00 <sub>H</sub> | r     | r     | r     | r     | r     | r     | r     | r     |

In parallel to the standard CMOS structure there are additional internal pullup devices of about  $10...200 \ k\Omega$  at each port pin.

**Note:** Registers PxPDR and PxPL may be used for general purpose storage if the ports are not used.

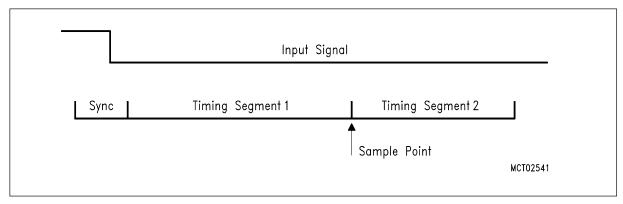

# **Bit Timing**

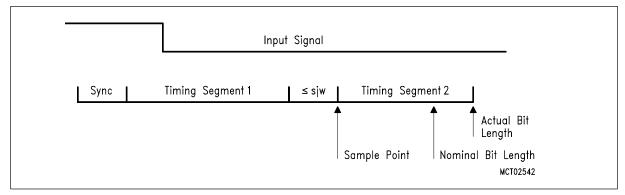

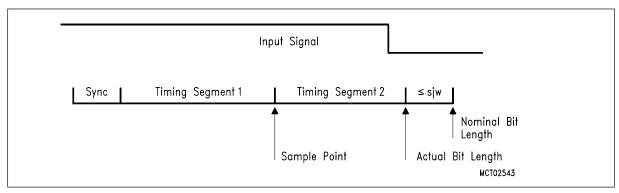

A regular bit period is composed of the following three segments:

- synchronization segment

- timing segment 1

- timing segment 2.

The sampling point is between timing segment 1 and timing segment 2.

Figure 6

Bit Time Segments

#### **Synchronization**

The edge of the input signal is expected during the sync segment (duration = 1 system clock cycle = 1  $t_{SCL}$ ).

# **Timing Segment 1 (TSeg1)**

Timing segment 1 determines the sampling point within a bit period. This point is always at the end of segment 1. The segment is programmable from 1 to 16  $t_{SCL}$  (see bit-length register BL1).

# **Timing Segment 2 (TSeg2)**

Timing segment 2 provides extra time for internal processing after the sampling point. The segment is programmable from 1 to 8  $t_{SCL}$  (see bit-length register BL1).

# Synchronization Jump Width (SJW)

To compensate for phase shifts between the oscillator frequencies of the different bus stations, each CAN controller must be able to synchronize to the relevant signal edge of the incoming signal. The synchronization jump width (SJW) determines the maximum number of system clock pulses by which the bit period can be lengthened or shortened for resynchronization. The synchronization jump width is programmable from 1 to 4  $t_{\rm SCL}$  (see bit-length register BL2).

Figure 7 Lengthening a Bit Period

Figure 8 Shortening a Bit Period

#### **Delay Times**

The total delay is calculated from the following single delays:

- 2 × physical bus  $t_{Bus}$  (max. 100 ns acc. to CAN specification)

- $2 \times \text{input comparator } t_{\text{Comp}}$  (depends on application circuit)

- 2 × output driver  $t_{Driver}$  (depends on application circuit)

- 1 × input to output of CAN controller  $t_{InOut}$  (max. 1  $t_{SCL}$  + 80 ns)

$$t_{\text{Delay}} = 2 \times (t_{\text{Bus}} + t_{\text{Comp}} + t_{\text{Driver}}) + t_{\text{InOut}}$$

#### Recommendations

On the premise of the stated conditions, there are the following essential requirements to be maintained:

$$t_{\text{TSeg1}} \geq t_{\text{Seg2}}$$

$t_{\text{TSeg1}} \geq t_{\text{Delay}}$

$t_{\text{TSeg2}} > t_{\text{SJW}}$

$t_{\text{TSeg2}} \geq 3 \times t_{\text{SCL}} + t_{\text{SJW}}$  if bit SAM = 1 (otherwise bit recognition does not work).

#### **Host Interfaces**

There are two different host interfaces implemented in the SAE 81C90/91.

Data and addresses on a multiplexed 8-bit bus, compatible with Siemens microcontrollers (C5xx, C16x), can be transferred via the parallel interface (PI). Using the serial synchronous interface (SI), any host controller with a serial three-lead interface can be connected with.

The interface is selected by hardware through the wiring of the MS (Mode Select) pin. This pin may not be switched during operation. If there is a High level on the MS pin, the SI and thus pins DI, DO, CLK,  $\overline{W}$  and TIM are activated, while pins AD5 through AD7,  $\overline{RD}$ ,  $\overline{WR}$  and ALE are inactive. A Low level on the MS pin switches to the PI and thus activates pins AD0 through AD7,  $\overline{RD}$ ,  $\overline{WR}$  and ALE.

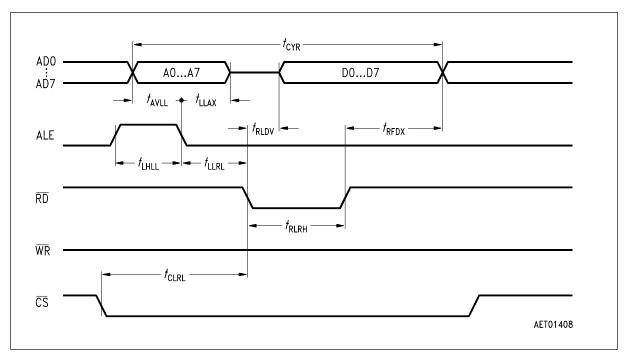

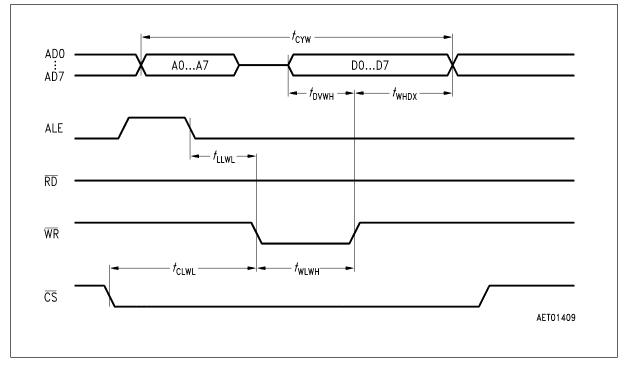

#### Parallel Interface PI

The parallel interface uses a multiplexed 8-bit address/data bus. First the address of the required register is applied to the pins AD0 through AD7. A falling edge on pin ALE means that this address is transferred to an on-chip latch. After this, data can either be written into the selected register (pin  $\overline{WR} = 0$ ) or read from it (pin  $\overline{RD} = 0$ ) via the address/data bus. Pin  $\overline{CS}$  must be 0 for the entire duration of the  $\overline{RD/WR}$  active time so that the circuit is activated.

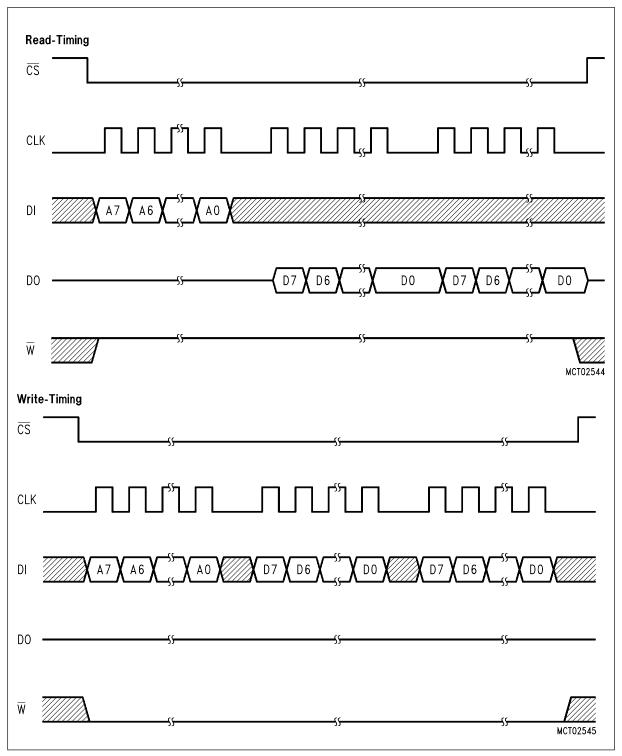

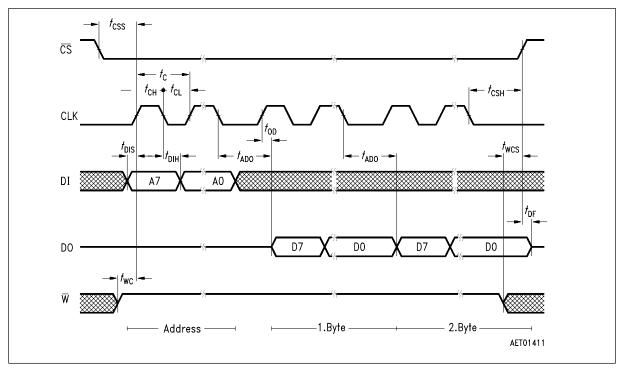

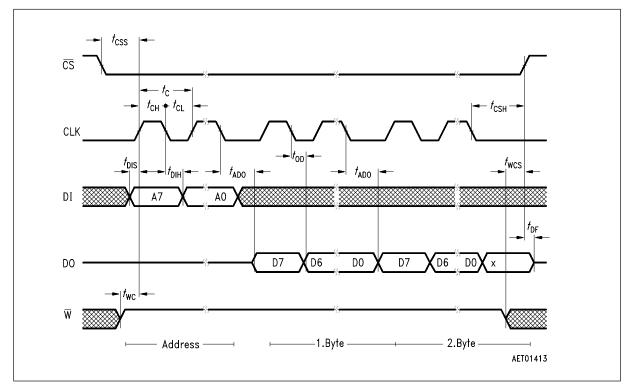

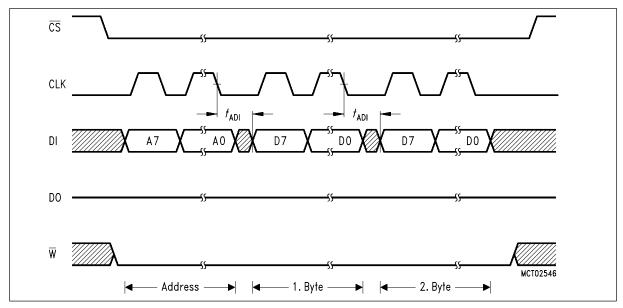

# Serial Synchronous Interface SI

If the SI is used the unused pins of PI must be set to inactive levels ( $\overline{RD}$ ,  $\overline{WR}$  to  $V_{DD}$  and ALE, AD5, AD6, AD7 to  $V_{SS}$ ).

Communication on the SI is accomplished according to the following procedure: