## **AD8116 Evaluation Board**

## **EVAL-AD8116EB**

### **BOARD DESCRIPTION**

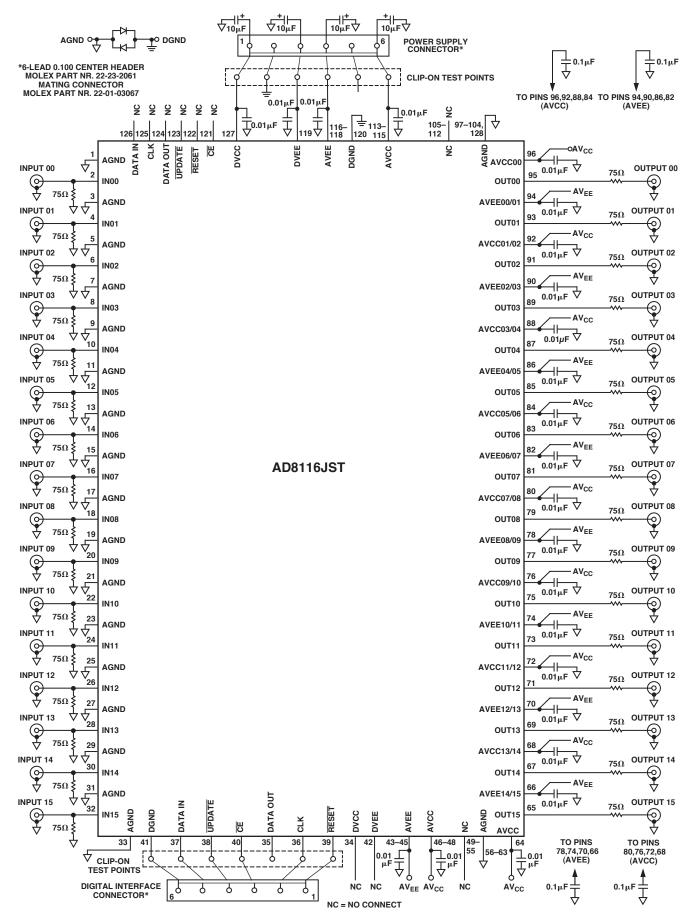

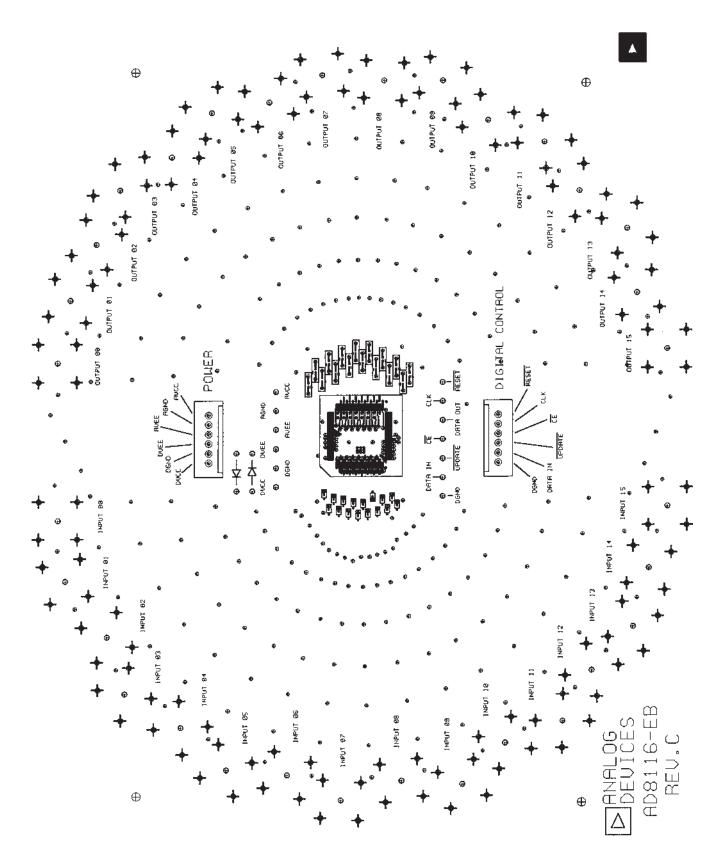

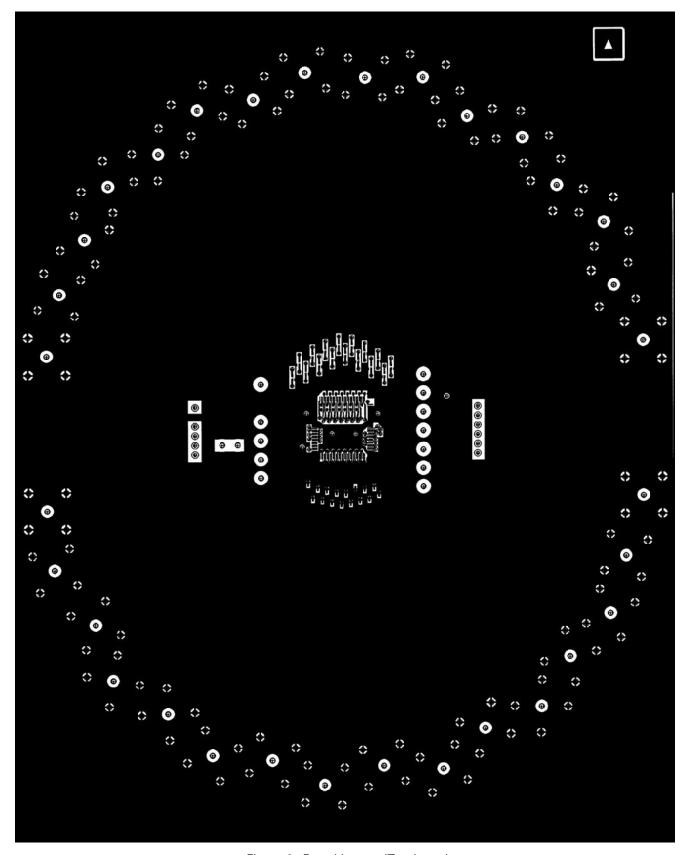

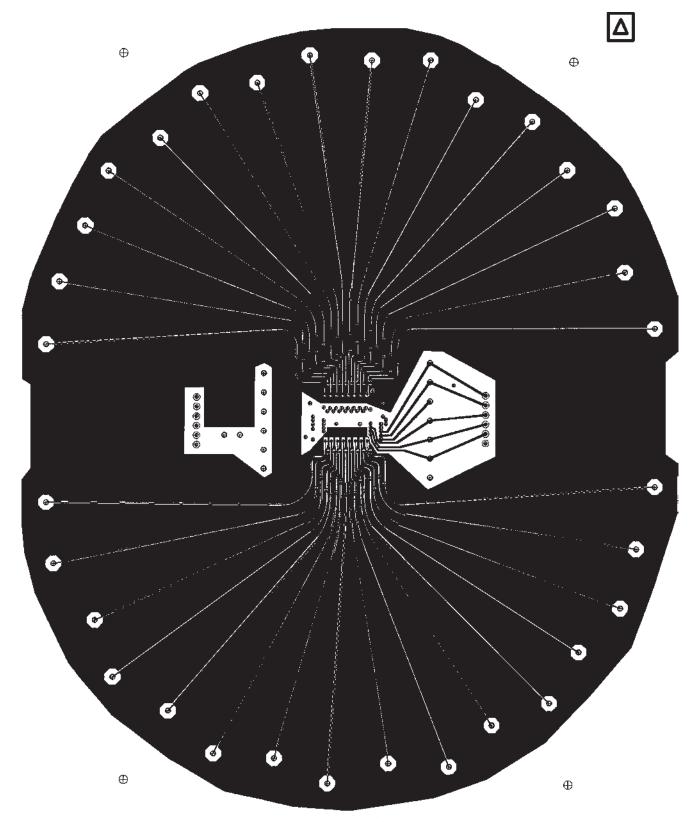

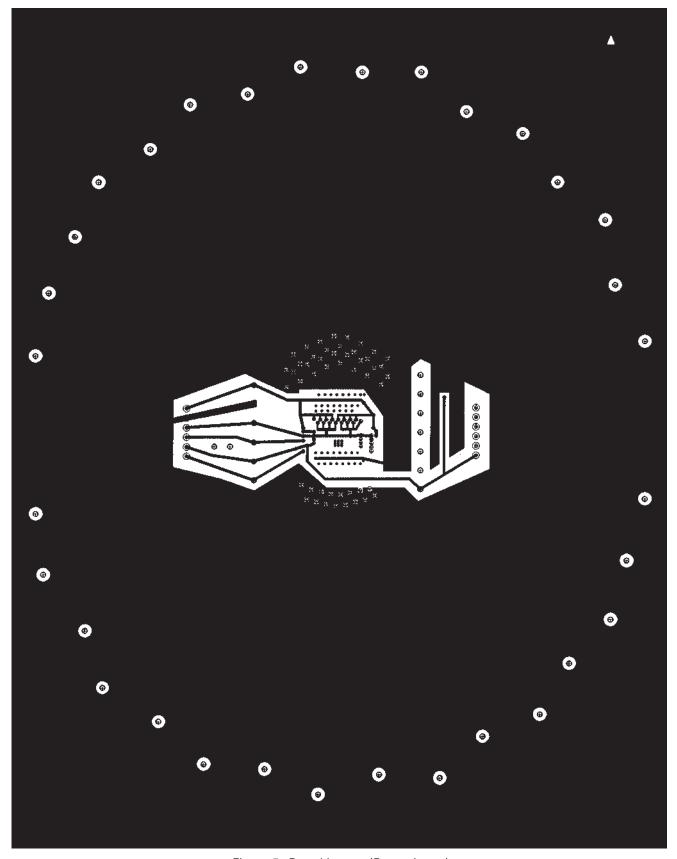

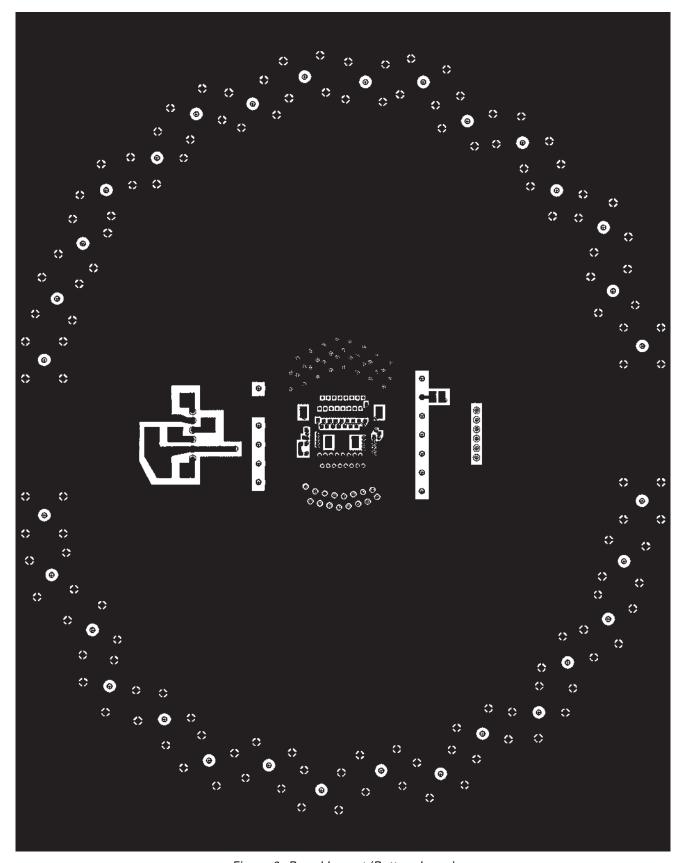

The AD8116 evaluation board has been carefully laid out and tested to demonstrate the specified high speed performance of the device. Figure 1 shows the schematic of the evaluation board. Figure 2 shows the component side silkscreen. The layouts of the board's four layers are given in Figures 3–6.

The evaluation board package includes the following:

- Fully populated board with BNC-type connectors

- Windows<sup>®</sup> based software for controlling the board from a PC via the printer port

- · Custom cable to connect evaluation board to PC

- · Disk containing Gerber files of board layout

### **ORDERING GUIDE**

| Model     | Package Description |

|-----------|---------------------|

| AD8116-EB | Evaluation Board    |

#### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the EVAL-AD8116EB features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2002 Analog Devices, Inc. All rights reserved.

Figure 1. Evaluation Board Schematic

Figure 2. Component Side Silkscreen

REV. 0 -3-

Figure 3. Board Layout (Top Layer)

-4- REV. 0

Figure 4. Board Layout (Signal Layer)

REV. 0 -5-

Figure 5. Board Layout (Power Layer)

-6- REV. 0

Figure 6. Board Layout (Bottom Layer)

REV. 0 -7-

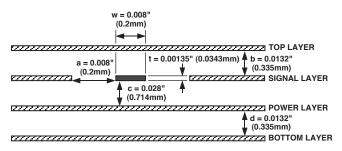

Optimized for video applications, all signal inputs and outputs are terminated with 75  $\Omega$  resistors. Figure 7 shows a cross section of one of the input or output tracks along with the arrangement of the PCB layers. It should be noted that unused regions of the four layers are filled up with ground planes. As a result, the input and output traces, in addition to having controlled impedances, are well shielded.

Figure 7. Cross Section of Input and Output Traces

The board has 32 BNC type connectors: 16 inputs and 16 outputs. The connectors are arranged in two crescents around the device. As can be seen from Figure 4, this results in all 16 input signal traces and all 16 output signal traces having the same length. This is useful in tests such as All-Hostile Crosstalk where the phase relationship and delay between signals needs to be maintained from input to output.

The four power supply pins AVCC, DVCC, AVEE, and DVEE should be connected to good quality, low noise,  $\pm 5$  V supplies. Where the same  $\pm 5$  V power supplies are used for analog and digital, separate cables should be run for the power supply to the evaluation board's analog and digital power supply pins.

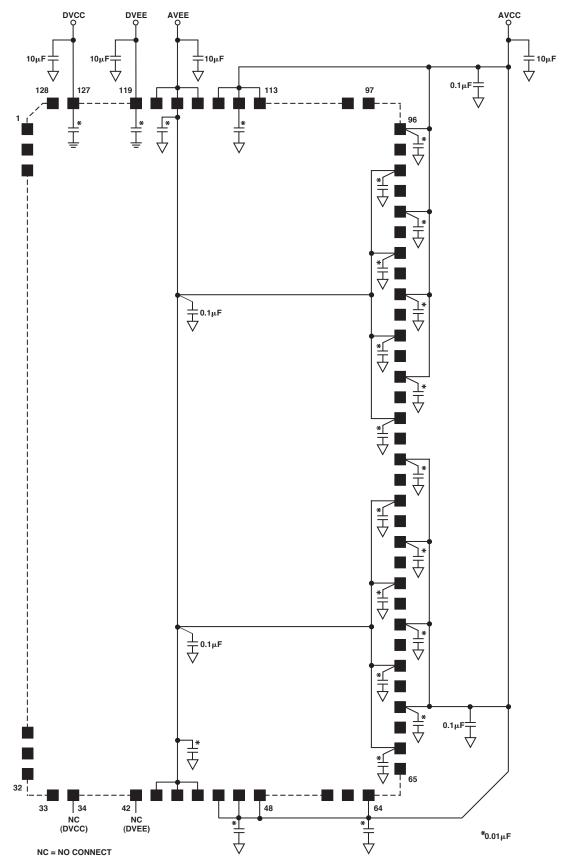

As can be seen in Figure 8, there is extensive power supply decoupling on the evaluation board. Figure 8 shows the location of all the decoupling capacitors relative to the AD8116's pins. Four large 10 µF capacitors are located near the evaluation board's power supply connection terminals. These decouple the AVCC, DVCC, AVEE, and DVEE supplies. Because it is required that the voltage difference between DGND and AGND never exceed 0.7 V, these grounds are connected by two antiparallel diodes. On the output side of the device (Pin 65 to Pin 96), the 16 output pins are interleaved with the AVCC and AVEE power supply pins. Each of these pins is locally decoupled with a 0.01 µF capacitor. These pins are also decoupled in groups of four with 0.1 µF capacitors. Due to space constraints, the power supply Pins 34 (DVCC) and 42 (DVEE) are neither connected nor decoupled. These pins are, however, internally connected to DVCC and DVEE (Pins 127 and 119).

As a general rule, each power supply pin (or group of adjacent power supply pins) should be locally decoupled with a 0.01  $\mu F$  capacitor. If there is a space constraint, it is more important to decouple analog power supply pins before digital power supply pins. A 0.1  $\mu F$  capacitor, located reasonably close to the pins, can be used to decouple a number of power supply pins. Finally, a 10  $\mu F$  capacitor should be used to decouple power supplies as they come onto the board.

-8- REV. 0

Figure 8. Detail of Decoupling on Evaluation Board

### Controlling the Evaluation Board from a PC

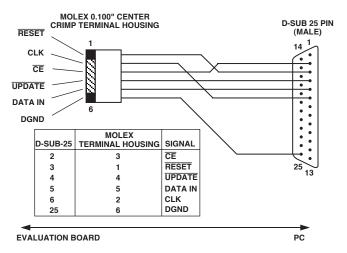

The evaluation board includes Windows based control software and a custom cable that connects the board's digital interface to the printer port of the PC. The wiring of this cable is shown in Figure 9. The software requires Windows 3.1 or later to operate. To install the software, insert the disk labeled "Disk #1 of 2" in the PC and run the file called SETUP.EXE. Additional installation instructions will be given on-screen. Before beginning installation, it is important to terminate any other Windows applications that are running.

Figure 9. Evaluation Board PC Connection Cable

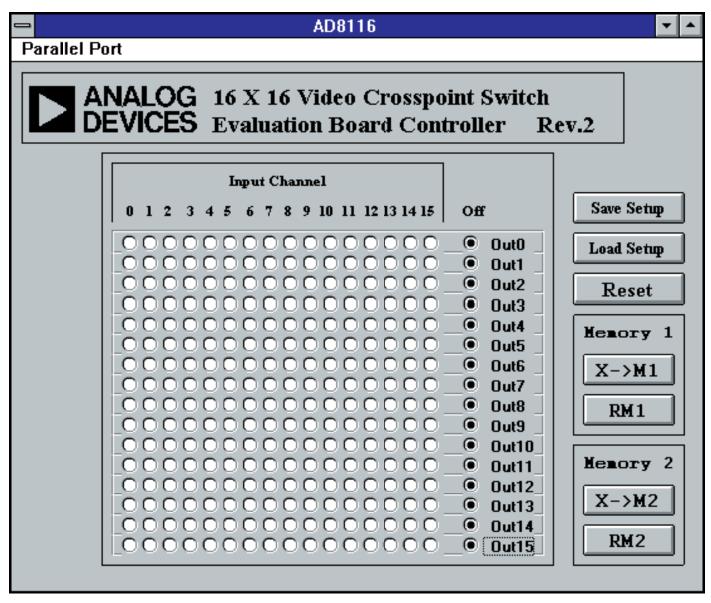

When you launch the crosspoint control software, you will be asked to select the printer port you are using. Most modern PCs have only one printer port, usually called LPT1; however, some laptop computers use the PRN port.

Figure 10 shows the main screen of the control software in its initial reset state (all outputs off). Using the mouse, any input can be connected with one or more outputs by simply clicking on the appropriate radio buttons in the  $16\times16$  on-screen array. Each time a button is clicked on, the software automatically sends and latches the required 80-bit data stream to the evaluation board. An output can be turned off by clicking the appropriate button in the Off column. To turn off all outputs, click RESET.

The software offers volatile and nonvolatile storage of configurations. For volatile storage, up to two configurations can be stored and recalled using the Memory 1 and Memory 2 buffers. These function in an identical fashion to the memory on a pocket calculator. For nonvolatile storage of a configuration, the Save Setup and Load Setup functions can be used. This stores the configuration as a data file on disk.

#### Overshoot on PC Printer Ports' Data Lines

The data lines on some printer ports have excessive overshoot. Overshoot on the pin that is used as the serial clock (Pin 6 on the D-Sub-25 connector) can cause communication problems. This overshoot can be eliminated by connecting a capacitor from the CLK line on the evaluation board to ground. A pad has been provided on the solder-side of the evaluation board to allow this capacitor to be soldered into place. Depending upon the overshoot from the printer port, this capacitor may need to be as large as 0.01 µF.

-10- REV. 0

Figure 10. Screen Display of Control Software

REV. 0 -11-