**DATA SHEET**

Ed. 3, November 1999

## FEATURES I

- UTOPIA and 16-Bit (ATM or PHY) Layer cell interfaces

- Inlet-side address translation and routing header insertion, using external SRAM of up to 256 kB

- Programmable OAM-cell and RM-cell routing

- CellBus bus access request, grant reception and bus transmission

- CellBus bus cell reception and address recognition

- · Outlet cell queuing: various modes

- · Ability to insert GFC field in real time

- Ability to insert FECN indication, under programmable conditions

- Ability to send and receive cells for control purposes over same CellBus bus

- Cell insertion and extraction via microprocessor port

- Master bus arbiter and frame pulse generator included in each CUBIT-Pro, with enabling pin

- Internal GTL transceivers for CellBus bus connection

- Interface port to translation table in SRAM

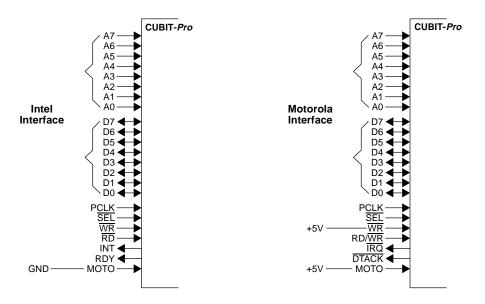

- Microprocessor control port, selectable for Intel or Motorola interface

- +5 V and +3.3 V power supplies

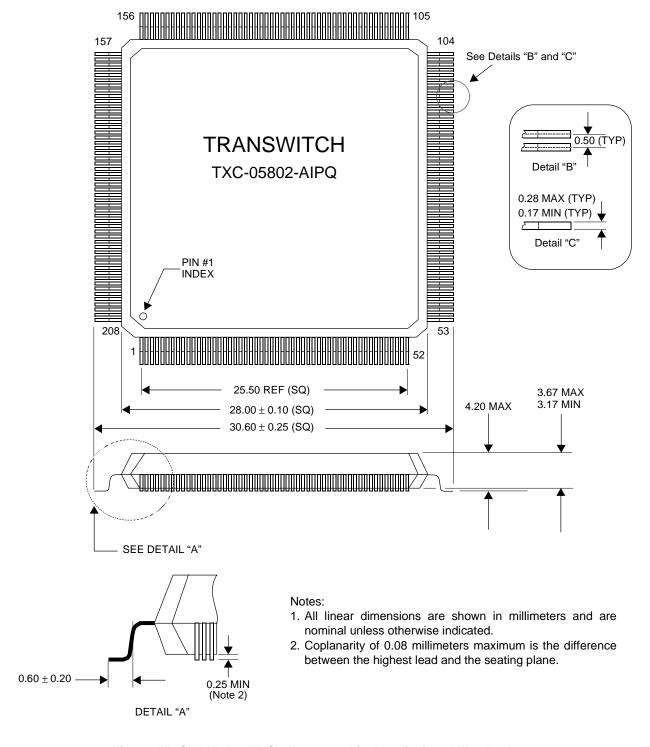

- 208-pin plastic quad flat package

## **DESCRIPTION**

CUBIT-*Pro*<sup>TM</sup> is a single-chip solution for implementing cost effective ATM access systems. It is based on the *CellBus*<sup>TM</sup> Bus Architecture (*CellBus*). Such systems are constructed from a number of CUBIT-*Pro* devices, all interconnected by a 37-line common bus, the *CellBus* bus. When operating at a 38 MHz clock rate, a *CellBus* bus system can handle 1 Gbit/s of net ATM cell bandwidth. CUBIT-*Pro* supports unicast and multicast transfers, and has all necessary functions for implementing a switch: cell address translation, cell routing, and outlet cell queuing.

# **APPLICATIONS**

- · xDSL Access Multiplexer

- · Remote Access Equipment

- Cable Modem Access Multiplexer

- ATM LAN hub

- ATM multiplexer/concentrator

- Small-stand-alone ATM switch

- Add-Drop Ring Switch

- Edge switching equipment

TranSwitch Corporation • 3 Enterprise Drive • Shelton, Connecticut 06484 • USA Tel: 203-929-8810 • Fax: 203-926-9453 • www.transwitch.com

TranSwitch, TXC, CellBus, CUBIT, SALI-25C and SARA are registered trademarks of TranSwitch Corporation

# **TABLE OF CONTENTS**

| SECTION                                                  | <u>PAGE</u> |

|----------------------------------------------------------|-------------|

| List of Figures                                          | 3           |

| Block Diagram                                            | 5           |

| Operation                                                | 6-40        |

| Introduction to CellBus Bus Architecture                 | 6           |

| CellBus Bus Operation                                    | 6           |

| CellBus Bus Cell Routing                                 | 8           |

| CellBus Bus Status Signals and Monitoring                | 10          |

| CUBIT-Pro Cell Inlet and Outlet Ports                    |             |

| 8-Bit UTOPIA Mode - ATM and PHY Layer Emulation          |             |

| ALI-25 Mode                                              |             |

| Back-to-Back Mode                                        | 15          |

| Byte Ordering for UTOPIA, ALI-25 and Back-to-Back Modes  |             |

| 16-Bit Cell Interface Mode - ATM and PHY Layer Emulation |             |

| Word Ordering for 16-Bit Cell Interface Mode             |             |

| Traffic Management Functions                             |             |

| Dynamic Generic Flow Control (GFC) Field Insertion       |             |

| Forward Explicit Congestion Notification (FECN)          |             |

| Congestion Indication from CellBus Bus to Cell Inlet     |             |

| Paralleling Cell Inlet/Outlet Ports for Redundancy       |             |

| Inlet-Side Translation                                   |             |

| Introduction                                             |             |

| Translation RAM Connections                              |             |

| Translation RAM Control                                  |             |

| Translation RAM Organization                             |             |

| Translation Procedure                                    |             |

| Translation Record Formats                               |             |

| Multicast Number Memory                                  |             |

| The CellBus Bus Interface                                |             |

| Operation with Internal GTL Transceivers                 |             |

| Clock Source                                             |             |

| Bus Arbiter Selection                                    |             |

| Outlet-Side Queue Management                             |             |

| Single Queue Operation                                   |             |

| Split-Queue Operation                                    |             |

| Microprocessor Interface                                 |             |

| General Description                                      |             |

| Intel Mode                                               |             |

| Motorola Mode                                            |             |

| Interrupts                                               |             |

| Control Queue Send and Receive                           |             |

| Loopback Cell Send, Receive and Relay                    |             |

| Memory Map Reset States                                  |             |

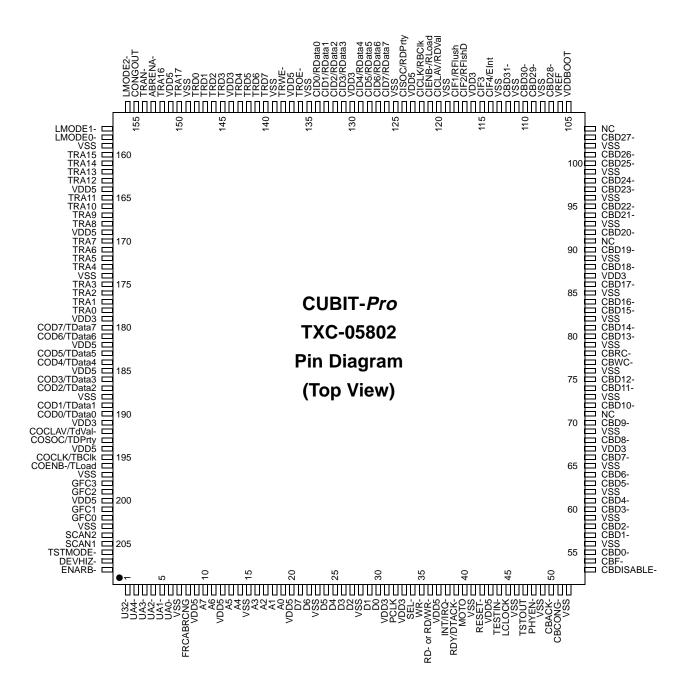

| Pin Diagram                                              |             |

| Pin Descriptions                                         |             |

| Absolute Maximum Ratings and Environmental Limitations   |             |

| Thermal Characteristics                                  |             |

| Power Requirements                                       |             |

| Input, Output and I/O Parameters                         |             |

| Timing Characteristics                                   |             |

| Memory Man                                               | 75          |

| Memory Map Descriptions                  | 77 |

|------------------------------------------|----|

| Package Information                      | 83 |

| Ordering Information                     | 84 |

| Related Products                         | 84 |

| Standards Documentation Sources          | 86 |

| List of Data Sheet Changes               | 88 |

| Documentation Update Registration Form * | 91 |

# **LIST OF FIGURES**

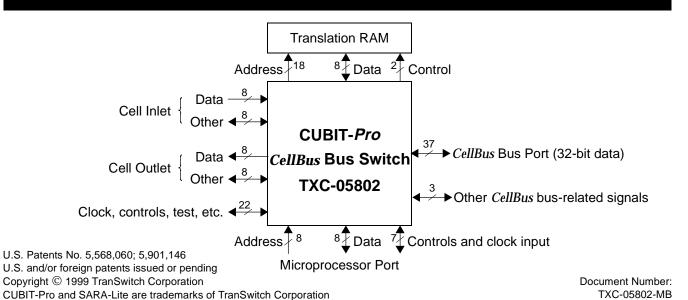

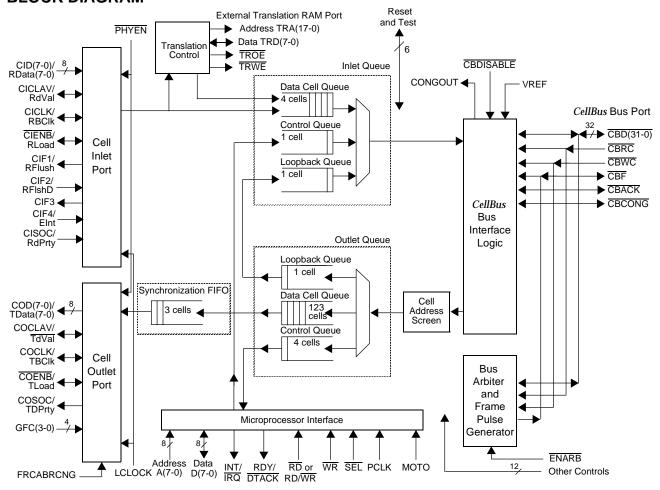

| Figure 1.  | CUBIT-Pro TXC-05802 Block Diagram                                                     | 5  |

|------------|---------------------------------------------------------------------------------------|----|

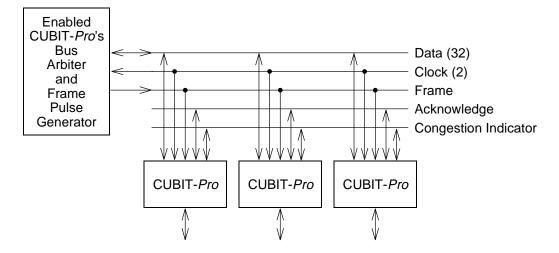

| Figure 2.  | CellBus Bus Structure                                                                 | 6  |

| Figure 3.  | CellBus Bus Frame Format                                                              | 7  |

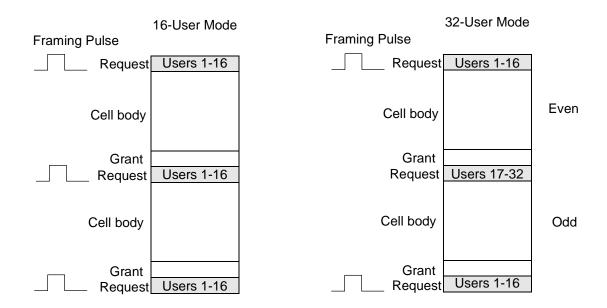

| Figure 4.  | CellBus Bus 16/32-User Modes - Frame Formats                                          | 8  |

| Figure 5.  | CellBus Bus Routing Header Formats                                                    | 9  |

| Figure 6.  | ATM Layer Emulation 8-Bit UTOPIA Mode Signal Connections and Operating Mode Selection | 12 |

| Figure 7.  | PHY Layer Emulation 8-Bit UTOPIA Mode Signal Connections and Operating Mode Selection |    |

| Figure 8.  | ALI-25 Mode Signal Connections and Operating  Mode Selection                          |    |

| Figure 9.  | Back-to-Back Mode Signal Connections and Operating Mode Selection                     | 15 |

| Figure 10. | Byte Ordering on Cell Inlet and Outlet in UTOPIA, ALI-25 and Back-to-Back Modes       | 16 |

| Figure 11. | ATM Layer Emulation 16-Bit Mode Signal Connections and Operating Mode Selection       |    |

| Figure 12. | PHY Layer Emulation 16-Bit Mode Signal Connections and Operating Mode Selection       |    |

| Figure 13. | Word Ordering on Cell Inlet and Outlet in 16-Bit Mode                                 |    |

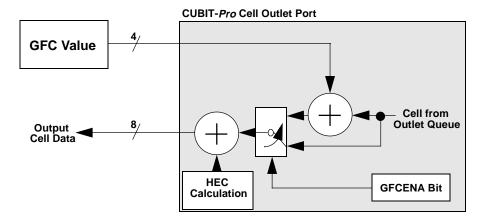

| Figure 14. | GFC Insertion on the Outlet Queue (GFCENA = 1)                                        | 19 |

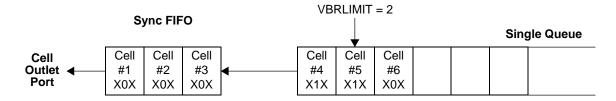

| Figure 15. | Example of Congestion Indication in Single-Queue Mode (QM=0)                          | 20 |

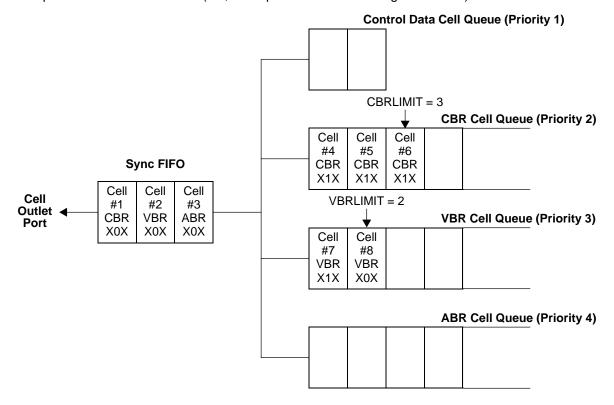

| Figure 16. | Example of Congestion Indication in Split-Queue Mode (QM=1)                           | 21 |

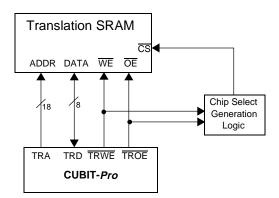

| Figure 17. | Translation RAM Connections                                                           | 23 |

| Figure 18. | Translation RAM Organization                                                          | 25 |

| Figure 19. | VCI Page 0 Organization (Bit OAMRMEN=1)                                               | 25 |

| Figure 20. | VPI Translation Record Formats                                                        | 28 |

| Figure 21. | VCI Translation Record Formats                                                        | 29 |

| Figure 22. | OAM F5 and RM-VCC Cell Routing (Bit OAMRMEN=1)                                        | 30 |

| Figure 23. | OAM F4 and RM-VPC Cell Routing (Bit OAMRMEN=1)                                        | 31 |

| Figure 24. | OAM/RM-Cells Translation Record Formats                                               | 31 |

| Figure 25. | Multicast Number Memory                                                               | 32 |

| Figure 26. | External Circuit Requirements for GTL Transceivers                                    | 33 |

| Figure 27. | Microprocessor Port Interface Connections                                             | 35 |

| Figure 28. | CUBIT-Pro Status Register at Address 05H                                              | 36 |

| Figure 29. | CUBIT-Pro Status Register at Address 08H                                              | 37 |

<sup>\*</sup> Please note that TranSwitch provides documentation for all of its products. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

# <u>TranSwitch</u>

| Figure 31. Loading the Loopback Registers                                  | . 39 |

|----------------------------------------------------------------------------|------|

| Figure 32. CUBIT-Pro TXC-05802 Pin Diagram                                 | . 41 |

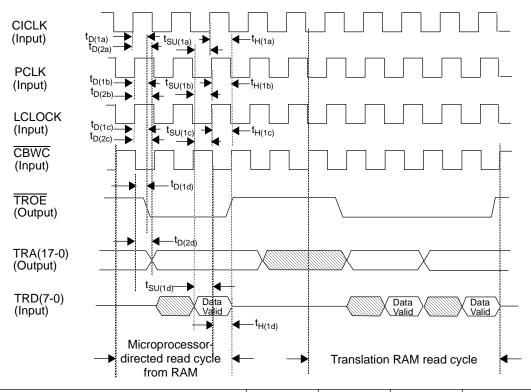

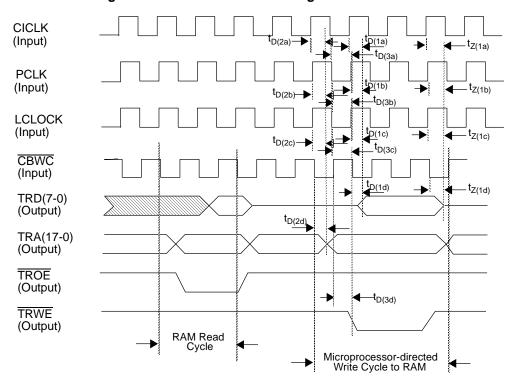

| Figure 33. Translation RAM Timing - Read from RAM                          | . 53 |

| Figure 34. Translation RAM Timing - Write to RAM                           | . 54 |

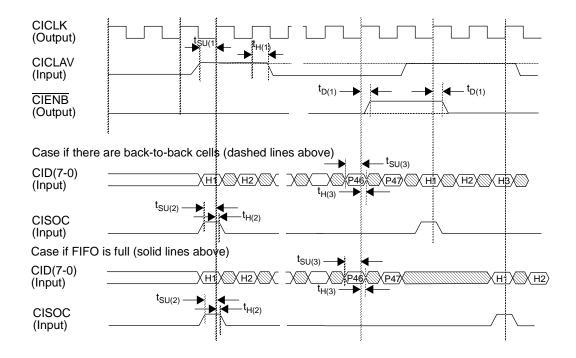

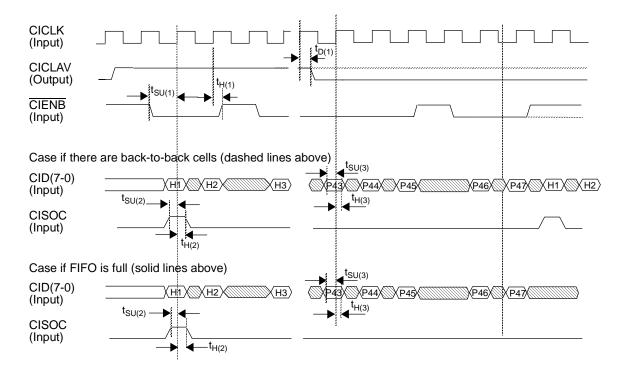

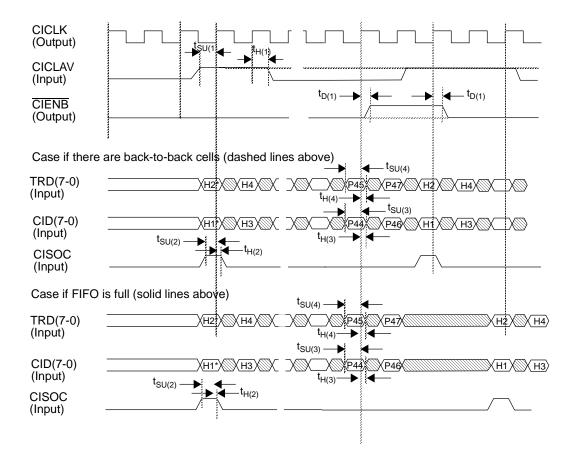

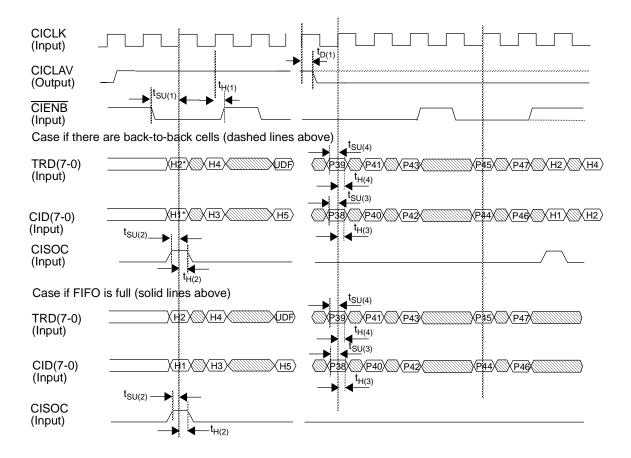

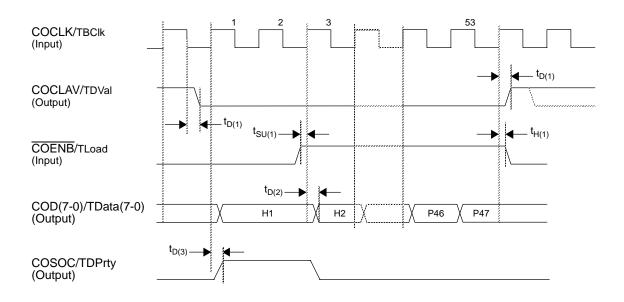

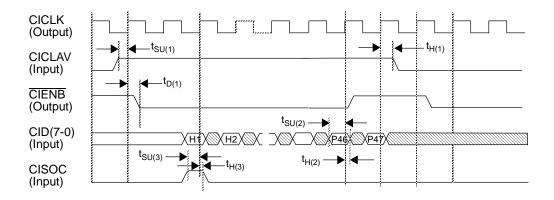

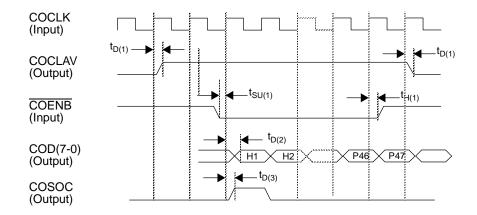

| Figure 35. Timing of UTOPIA (ATM Layer Emulation) Cell Inlet Interface     | . 55 |

| Figure 36. Timing of UTOPIA (PHY Layer Emulation) Cell Inlet Interface     | . 56 |

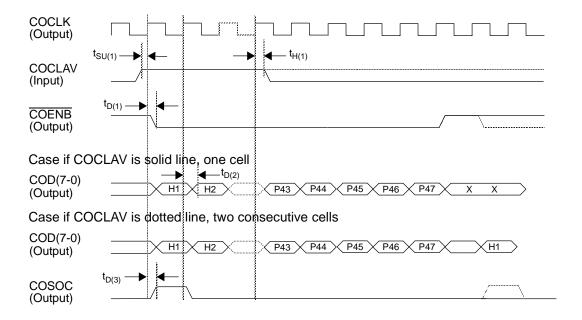

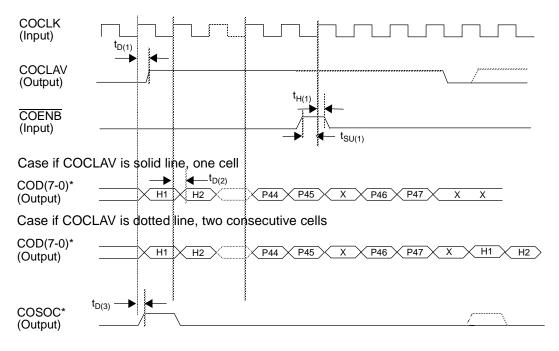

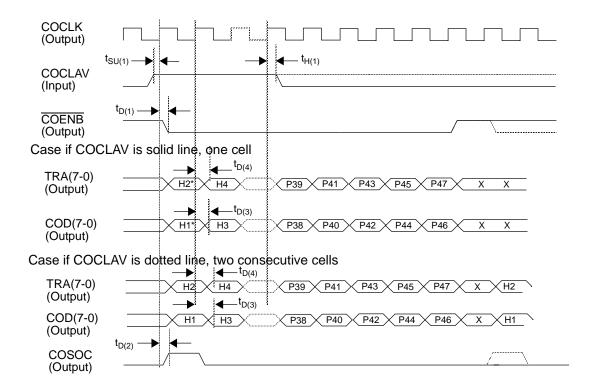

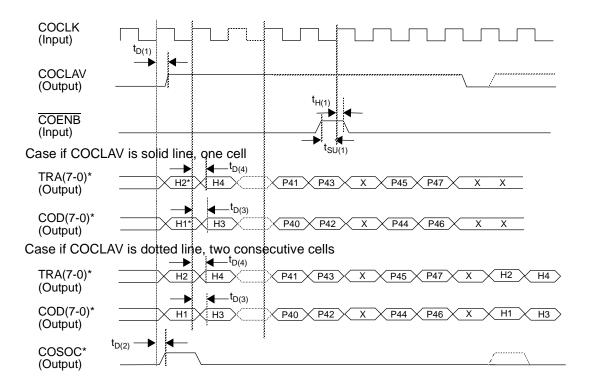

| Figure 37. Timing of UTOPIA (ATM Layer Emulation) Cell Outlet Interface    | . 57 |

| Figure 38. Timing of UTOPIA (PHY Layer Emulation) Cell Outlet Interface    | . 58 |

| Figure 39. Timing of 16-Bit (ATM Layer Emulation) Cell Inlet Interface     | . 59 |

| Figure 40. Timing of 16-Bit (PHY Layer Emulation) Cell Inlet Interface     | . 60 |

| Figure 41. Timing of 16-Bit (ATM Layer Emulation) Cell Outlet Interface    | . 61 |

| Figure 42. Timing of 16-Bit (PHY Layer Emulation) Cell Outlet Interface    | . 62 |

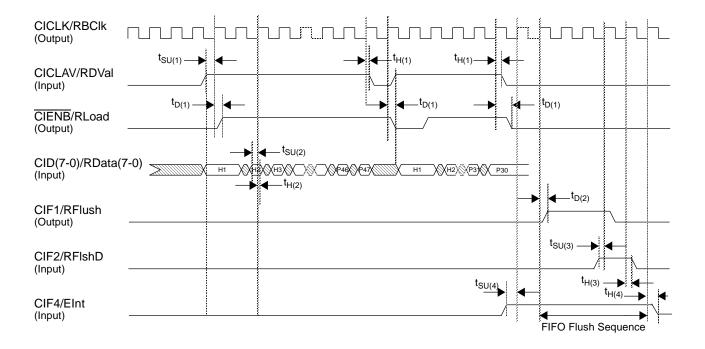

| Figure 43. Timing of ALI-25 Cell Receive Interface                         | . 63 |

| Figure 44. Timing of ALI-25 Cell Transmit Interface                        | . 64 |

| Figure 45. Timing of Back-to-Back Cell Receive Interface                   | . 65 |

| Figure 46. Timing of Back-to-Back Cell Transmit Interface                  | . 66 |

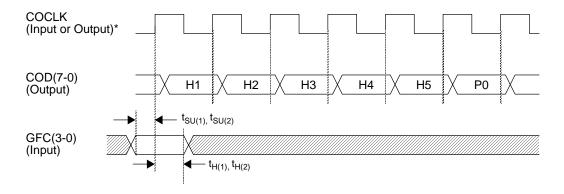

| Figure 47. GFC Field Insertion Timing                                      | . 67 |

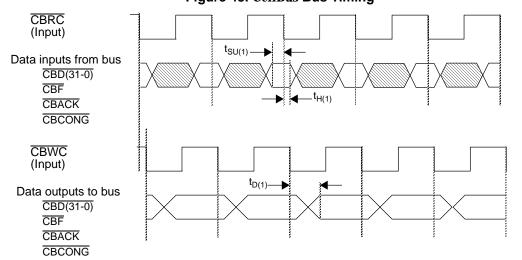

| Figure 48. CellBus Bus Timing                                              | . 68 |

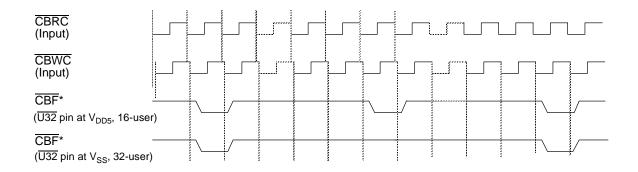

| Figure 49. CellBus Bus Frame Position, 16-User and 32-User Applications    | . 69 |

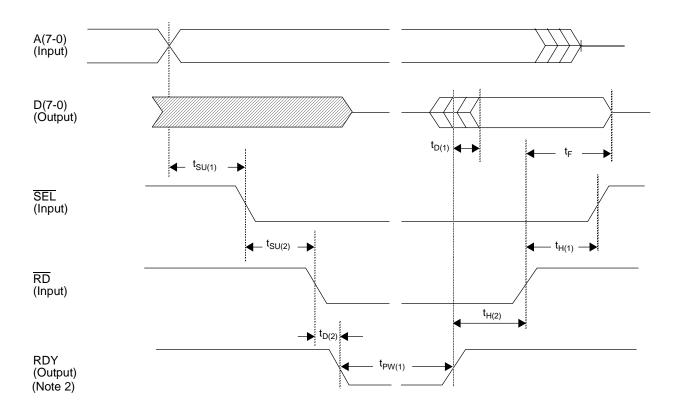

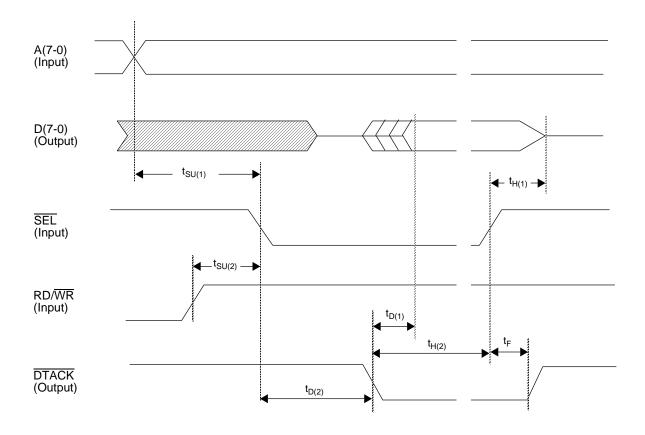

| Figure 50. Intel Microprocessor Read Cycle Timing                          | . 70 |

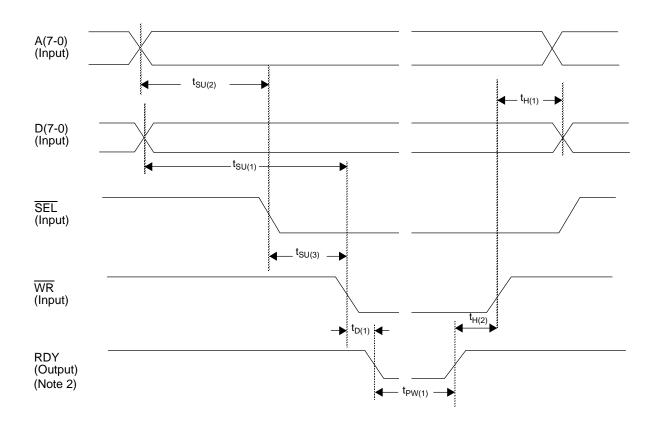

| Figure 51. Intel Microprocessor Write Cycle Timing                         | . 71 |

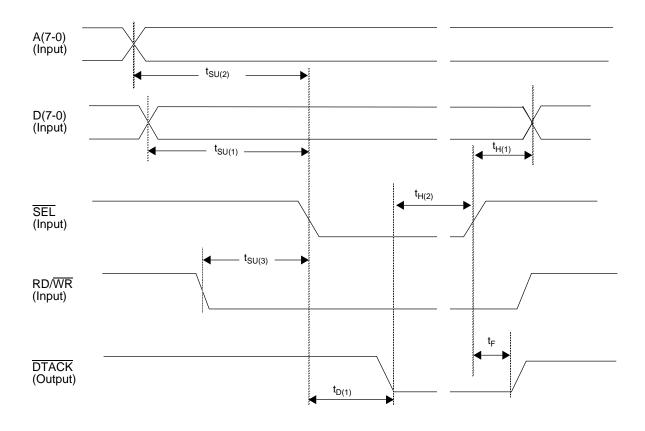

| Figure 52. Motorola Microprocessor Read Cycle Timing                       | . 72 |

| Figure 53. Motorola Microprocessor Write Cycle Timing                      | . 73 |

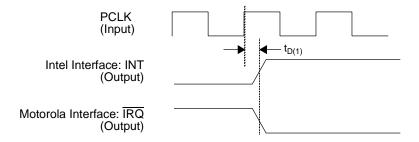

| Figure 54. Microprocessor Interrupt Timing                                 | . 74 |

| Figure 55. CUBIT-Pro TXC-05802 208-Pin Plastic Quad Flat Package           | . 83 |

| Figure 56. CUBIT- <i>Pro</i> TXC-05802 and Related Product Applications in | 85   |

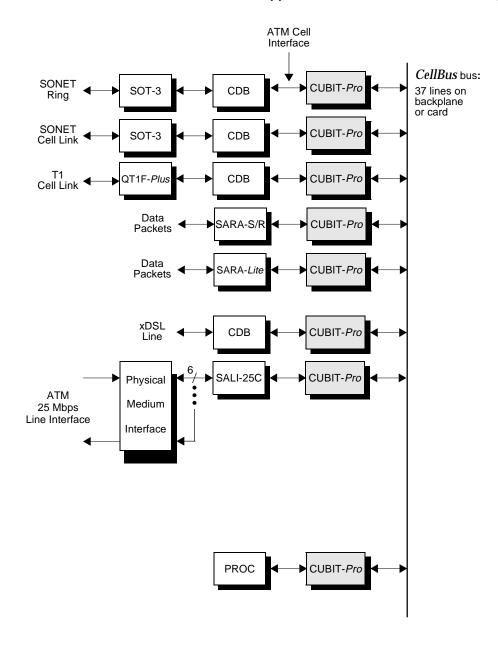

# **BLOCK DIAGRAM**

Figure 1. CUBIT-Pro TXC-05802 Block Diagram

A block diagram of the CUBIT-*Pro* device is shown in Figure 1. Further information on device operation and the interfaces to external circuits is provided below in the following Operation section.

On the cell inlet side of the CUBIT-Pro is circuitry associated with accepting cells from the line and passing them to the CellBus bus with an appropriate header. The Cell Inlet Port block is pin-selectable to be compliant with either the ATM Forum UTOPIA (Universal Test and Operations Physical Interface for ATM) interface, a TranSwitch 16-Bit interface, or the TranSwitch ALI-25 device interface. Incoming cells may carry a CellBus Routing Header and translated outgoing VPI/VCI address, the translation function having been performed externally, or this address translation and routing header insertion may be done by the CUBIT-Pro Translation Control block. Translation and routing header tables to support this function are contained in an external static RAM (up to 256k x 8 bits). They support VPI and/or VPI/VCI address translation. The incoming cells then pass through a FIFO gueue in the Inlet Queue block to the CellBus Bus Port via the CellBus Bus Interface Logic block. When there is a cell in this 4-cell data cell queue, the CUBIT-Pro makes a bus access request, and waits for a grant from the Bus Arbiter and Frame Pulse Generator block of the one CUBIT-Pro device attached to the bus that has been enabled to perform these two functions. When a bus access grant is received, the CUBIT-Pro sends the cell to the bus, in standard CellBus bus format. The cell can then be received by any connected CUBIT-Pro or CUBIT-Pros. In addition to these incoming data cells, the CUBIT-Pro can also send Control cells from the local microprocessor to the bus via the Microprocessor Interface block. Special cells of Loopback type received from the bus may also be returned to the bus, re-directed back to the CUBIT-Pro which launched the original Loopback cell. Both the Control cells and the Loopback cells have 1-cell inlet queues.

On the cell outlet side, cells of proper unicast address, broadcast address or selected multicast address, received from the bus via the *CellBus* Bus Interface Logic block, are recognized by the Cell Address Screen block and routed into a FIFO structure in the Outlet Queue block. The unicast address is unique per device, set by device straps. Each CUBIT-*Pro* may be programmed to accept cells associated with multicast sessions. From zero up to the full 256 multicast sessions may be accepted independently by each CUBIT-*Pro* on the bus. Data cells from the bus go into a 123-cell outlet data cell queue structure. Control cells and Loopback cells arriving from the bus are routed to the 4-cell outlet control queue, and the 1-cell outlet loopback queue, respectively. The outlet data cell FIFO structure can be treated as a single 123-cell queue, or it can be subdivided into four individual queues for traffic of different service types. The four-queue split is typically into high-speed control data cells, CBR cells, VBR cells, and ABR cells, in decreasing order of outlet service priority. This allows for delay minimization of critical service types, and for more efficient traffic management. At the cell outlet, provisions are made for insertion of an outgoing Generic Flow Control (GFC) field and an Explicit Forward Congestion Indication (EFCI) bit.

## **OPERATION**

#### INTRODUCTION TO CellBus BUS ARCHITECTURE

## CellBus Bus Operation

The CUBIT-*Pro* is a versatile CMOS VLSI device for implementing ATM switching functions. Various ATM cell switching or multiplexing structures can be formed by interconnection of a number of CUBIT-*Pro* devices over a 37-line parallel bus with 32 data bits, the *CellBus* bus. Since the interconnect structure is a bus, communications between any of the devices on the bus is possible. Each cell placed onto the *CellBus* bus by a CUBIT-*Pro* device can be routed either to one single CUBIT-*Pro* (unicast addressing), or to multiple CUBIT-*Pro* devices (multicast or broadcast addressing). Depending upon the needs of an application, up to 32 CUBIT-*Pro* devices may be interconnected on one *CellBus* bus. With a maximum bus frequency of more than 38 MHz, the raw bandwidth of the *CellBus* bus exceeds 1 Gbit/s.

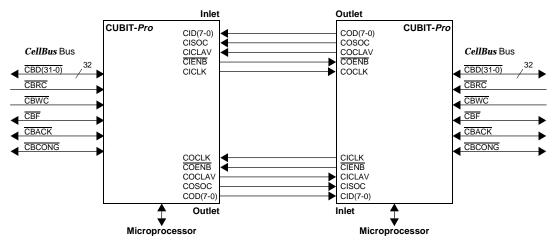

Figure 2. CellBus Bus Structure

The *CellBus* bus, shown in Figure 2, is a shared bus, and can be implemented either on a single circuit card, or in a backplane configuration among multiple circuit cards. Since multiple CUBIT-Pros share the same bus, bus access contention must be resolved. This access contention is resolved by use of a central arbitration function. CUBIT-Pros will request bus access, and the central Bus Arbiter will grant access back, in response. The circuitry for this Bus Arbiter is included inside the CUBIT-*Pro* device. Any one CUBIT-*Pro* in a system may be selected to perform the bus arbitration function by setting its ENARB pin low.

| Cycle<br>Number |           |                     |                     |                  |                      |                 |         |                               |                    |  |  |  |

|-----------------|-----------|---------------------|---------------------|------------------|----------------------|-----------------|---------|-------------------------------|--------------------|--|--|--|

|                 | √ 31 1615 |                     |                     |                  |                      |                 |         |                               |                    |  |  |  |

| Request         | 0         | 16161515<br>b a b a | 14141313<br>b a b a |                  | 10 10 9 9<br>b a b a |                 |         | 4 4 3 3<br>b a b a            | 2 2 1 1<br>b a b a |  |  |  |

| $\bigwedge$     | 1         | Ce                  | <i>llBus</i> Rou    | ting Head        | ler                  | Tandem Rou      | iting H | Header (C                     | optional)          |  |  |  |

|                 | 2         | GFC                 | V                   | PI               |                      | VCI             |         |                               | PT L               |  |  |  |

|                 | 3         | Byt                 | e 0                 | Byt              | te 1                 | Byte 2          |         | Byt                           | e 3                |  |  |  |

|                 | 4         | Byt                 | e 4                 | Byt              | te 5                 | Byte 6          |         | Byt                           | e 7                |  |  |  |

|                 | 5         | Byte 8              |                     | Byte 9           |                      | Byte 10         |         | Byte                          | e 11               |  |  |  |

|                 | 6         | Byte 12             |                     | Byte 13          |                      | Byte 14 Byte 15 |         | e 15                          |                    |  |  |  |

| Cell<br>Body    | 7         | Byte                | Byte 16             |                  | e 17                 | Byte 18         |         | Byte                          | e 19               |  |  |  |

| (14 cycles)     | 8         | Byte                | e 20                | Byte 21          |                      | Byte 22 Byte 23 |         | e 23                          |                    |  |  |  |

| 1               | 9         | Byte                | e 24                | Byte 25          |                      | Byte 26 Byte 27 |         | e 27                          |                    |  |  |  |

|                 | 10        | Byte 28             |                     | Byte 29          |                      | Byte 30         |         | Byte                          | e 31               |  |  |  |

|                 | 11        | Byte                | e 32                | Byte 33          |                      | Byte 34         |         | Byte 35                       |                    |  |  |  |

|                 | 12        | Byte                | e 36                | Byte             | e 37                 | Byte 38         |         | Byte 39                       |                    |  |  |  |

|                 | 13        | Byte 40             |                     | Byte             | e 41                 | Byte 42         |         | Byte                          | e 43               |  |  |  |

|                 | 14        | Byte                | e 44                | Byte             | e 45 Byte 46         |                 | Byte 47 |                               |                    |  |  |  |

| Grant           | 15        | BIF                 | P-8                 | Unused P E Termi |                      |                 |         | Granted<br>Terminal<br>Number |                    |  |  |  |

Figure 3. CellBus Bus Frame Format

The CellBus bus has a framed format 16 clock cycles long and 32 bits wide, which is illustrated in Figure 3. The first cycle of each frame is the Request cycle (Cycle 0), during which those CUBIT-Pros which have a cell to send to the bus each make an access request by asserting one or two assigned bits on the bus. The CBF, CBACK and CBCONG signals are asserted during a Request cycle. The device address assigned to each CUBIT-Pro by device straps ( $\overline{UA(4-0)}$  at pins 2-6) uniquely specifies which two bits it may assert during the bus Request cycle time. For example,  $\overline{UA(4-0)} = HHHHH$  selects bits 1a and 1b. By asserting one of its assigned bits, or the other, or both, access requests of three different priorities may be made (controlled via bits P1, P0 in memory address 0AH). A central Bus Arbiter accepts these access requests, executes an arbitration algorithm (highest priority served first, round-robin within each priority), and issues a bus access grant during the final cycle of the frame, the Grant cycle (Cycle 15). Each grant issued by the arbiter is for one CUBIT-Pro to send one cell to the bus. Whichever CUBIT-Pro is issued a grant during a Grant cycle will transmit its cell during the 14 Cell Body clock cycles of the next bus frame, and will also drive an 8-bit cell parity check during the Grant cycle of that bus frame. Each cell sent can be of unicast, multicast, or broadcast type. CUBIT-Pros will accept single-address cells routed to an address defined by their address straps, all broadcast cells, and selected multicast cells. Thus, cells may be sent from any one CUBIT-Pro to any one CUBIT-Pro or to multiple CUBIT-Pros.

The CUBIT-Pro can be operated in either 16-user or 32-user mode, selectable via the  $\overline{\text{U32}}$  pin, as shown in Figure 4. For the 16-user mode the CellBus bus frame is identical to Figure 3. However, in 32-user mode the frame is duplicated, so that an odd and even frame are provided. The distinction between the two frames is given by the location of the frame pulse. The cycles for both frames are the same, except for the meaning of the Request cycle. The Request cycle in the even frame coincides with the frame pulse, whereas in the odd frame the pulse is not present. Furthermore, in the even frame CUBIT-Pros 0-15 (lower 16 users) request access to the bus and in the odd frame CUBIT-Pros 16-31 (upper 16 users) request access to the bus. The full bus bandwidth is available to be shared among all the users on the bus in either 16 or 32-user mode.

Figure 4. CellBus Bus 16/32-User Modes - Frame Formats

To detect *CellBus* bus errors, a BIP-8 (Bit Interleave Parity byte) is calculated over the 54-byte data field that extends from the first Tandem Routing Header byte through the final payload data byte, Byte 47. The BIP-8 is generated by the transmitting CUBIT-*Pro* using the following algorithm. The first byte of the Tandem Routing Header is exclusive-or gated with an all-ones byte, creating a starting seed value. This seed value is then exclusive-or gated with the second byte of the Tandem Routing Header. The result is then exclusive-or gated with the next byte in the cell. This process is repeated with every successive byte in the cell, through Byte 47 of the payload, and the final result is transmitted as the BIP-8 byte in cycle 15. The receiving CUBIT-*Pro* performs the same process and compares the generated BIP-8 with the received BIP-8. If no errors are detected the receiving CUBIT-*Pro* pulls CBACK low, acknowledging receipt of a cell. The *CellBus* Routing Header has its own CRC-4 field and is not included in the BIP-8 calculation. A cell with a BIP-8 or CRC-4 error is discarded.

The only signals required to operate the bus which are not sourced by a CUBIT-*Pro* device are two transfer clocks: write clock (CBWC) and read clock (CBRC). These clock signals are of the same frequency, but may be slightly phase-offset to allow for reliable bus operation. The framing pulse used to define the bus frame cycle is sent out by one of the CUBIT-*Pro*s, and the arbitration function is also performed by the same CUBIT-*Pro*. Each CUBIT-*Pro* contains the circuitry for both the Bus Arbiter and the Frame Pulse Generator. Only one CUBIT-*Pro* will have this circuitry enabled, by setting control pin ENARB.

# CellBus Bus Cell Routing

The *CellBus* bus architecture allows several types of cell routing from any one inlet port to the outlet ports of the CUBIT-Pros on the *CellBus* bus:

- Point-to-Point Routing: In Unicast or Single Address cell routing a cell coming into an inlet port is transferred

to a single outlet port. The CUBIT-Pro can address a cell to itself, effectively implementing both the inlet and

outlet ports.

- Point-to-Multipoint (Broadcast): A cell coming into the inlet port can be routed to the outlet ports of all the CUBIT-Pros on the CellBus bus.

- Point-to-Multipoint (Multicast): In multicast routing the cell arriving at the inlet port is sent to the subset of outlet ports that belong to the specific multicast session by means of selection in the receiving CUBIT-Pros.

For each of the routing methods the cells can be sent to different output queues according to whether the cell is used as a data cell or as control/loopback cell. Furthermore, data cells can be selected to go to four different data outlet queues: Control Data queue, Constant Bit Rate (CBR) queue, Variable Bit Rate (VBR) queue, and Available Bit Rate (ABR) queue. The CUBIT-*Pro* can be programmed to receive cells into separate queues (split-queue mode) or not (single-queue mode).

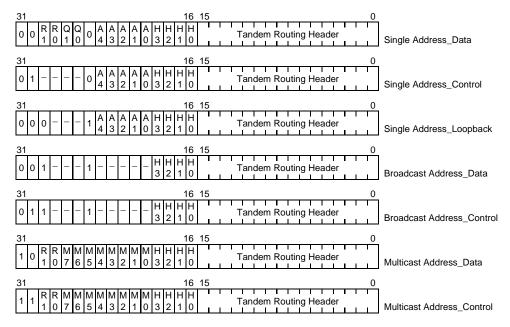

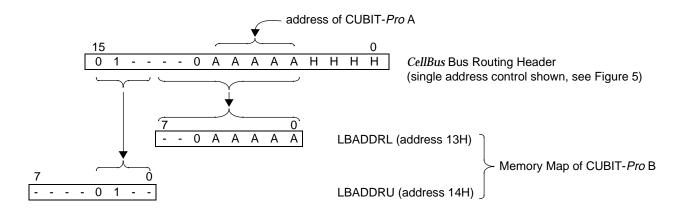

The encoding rules for the two-byte *CellBus* Bus Routing Header in Bits 31-16 of Cycle 1 are summarized in Figure 5.

Figure 5. CellBus Bus Routing Header Formats

# CellBus Bus Routing Header Format

The CellBus Bus Routing Header contains the following fields, as shown in Figure 5:

- R: Multi-PHY selector field (2 bits). Not interpreted by CUBIT-*Pro* currently (passed through intact). This field is ignored.

- **Q**: Queue selection field for split-queue mode (2 bits). 00 is outlet Control Data queue, 01 is Constant Bit Rate (CBR) queue, 10 is Variable Bit Rate (VBR) queue, 11 is Available Bit Rate (ABR) queue. This coding is only valid for data cells which contain Q1,Q0 fields in the header. For multicast and broadcast cell routing, cells are routed to the VBR and CBR queues, respectively, when using split-queue mode.

- **A**: CUBIT-*Pro* single address field (5 bits, for 32 addresses). A0 is the LSB. For example, A(4-0)=00000 is the address value for the CUBIT whose five device identity straps  $\overline{UA(4-0)}$  are all tied high (HHHHH).

- M: Multicast number field (8 bits, for 256 multicast sessions). M0 is the LSB.

**H**: CRC-4 field. This 4-bit field (H3-H0) provides Routing Header error protection across the *CellBus* bus in both directions. It is calculated over the 12-bit word (X11-X0) in bits 31-20 of the Routing Header using the following logic:

$H3 = \overline{(X7 \oplus X9 \oplus X3 \oplus X10 \oplus X8 \oplus X5 \oplus X2)}$

$H2 = (X6 \oplus X8 \oplus X2 \oplus X9 \oplus X7 \oplus X4 \oplus X1)$

$H1 = \overline{(X5 \oplus X7 \oplus X1 \oplus X8 \oplus X6 \oplus X3 \oplus X0)}$

$H0 = (X8 \oplus X10 \oplus X11 \oplus X4 \oplus X9 \oplus X6 \oplus X3 \oplus X0)$

where  $\oplus$  represents logical exclusive-or. For cells arriving from the *CellBus* bus, the CUBIT-*Pro* automatically calculates the corresponding CRC-4 and sets to 1 the status bit CRCF (bit 7 in register 08H) if it is not the same as that in bits H3-H0 of the received Routing Header. This status bit may be enabled to cause an interrupt signal to the microprocessor by setting to 1 the enable bit INTEN7 (bit 7 in register 09H). For cells supplied to the cell inlet interface from an external source for transmission via the *CellBus* bus, the CRC-4 may either be supplied in the input signal by use of external logic (as is required for the CUBIT device) or it may be generated internally and inserted into the Routing Header by the CUBIT-*Pro*. Setting control bit CRC4EN to 1 (bit 3 in register 0EH) activates the internal CRC-4 insertion for all incoming cells (i.e., not only data cells, but also control cells and loopback cells). When control bit CRC4I (bit 4 in register 0EH) is set to 1 the internally generated CRC-4 is inverted for testing purposes. This bit has no effect on an externally-supplied CRC-4. For operation in the CUBIT TXC-05801 mode with an externally-supplied CRC-4, bit CRC4EN should be set to 0, which is the default at power-up/reset.

## **Tandem Routing Header Format**

The two-byte Tandem Routing Header format in Bits 15-0 of Cycle 1 is the same as the *CellBus* Bus Routing Header format, if it is to be used by a cascaded *CellBus* bus, or may conform to a different specification if it is used by another system. The Tandem Routing Header is passed unchanged through the *CellBus* bus.

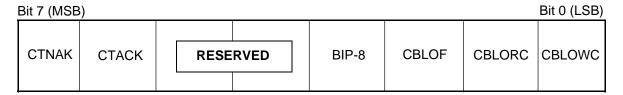

## CellBus Bus Status Signals and Monitoring

The CUBIT-*Pro* provides the capability to monitor the activity on the *CellBus* bus. The essential signals that determine whether the bus is active (in the absence of any cell traffic) are the clock signals and the frame pulse.

The *CellBus* bus clocks (read and write) are generated externally to the CUBIT-*Pro*. If either of these clocks fails, the entire bus will cease operation. The CUBIT-*Pro* provides the capability to detect the absence of clock signal for more than the equivalent of 32 processor clock (PCLK) cycles. The failure detection is performed independently for the *CellBus* Bus Read Clock (CBRC) and the *CellBus* Bus Write Clock (CBWC).

Two bits (register 05H bits CBLORC and CBLOWC) in the CUBIT-*Pro* memory map are used to indicate the clock loss event. Once the event is detected, these bits in register 05H will remain set to one until the microprocessor reads the register, at which point the register will be cleared. These events can be used to generate a microprocessor interrupt provided that the appropriate bits in the interrupt enable register (address 06H, bits INTENA1 and INTENA0) are 1.

The second monitoring function concerns the detection of loss of frame. The detection mechanism looks for two consecutive missing CellBus bus frame pulses in 32-user mode ( $\overline{U32} = Low$ ), and four consecutive missing CellBus bus frame pulses in 16-user mode. The CellBus Bus Read Clock must be present to detect Loss of Frame Pulse. If CellBus Bus Read Clock is present and CellBus Bus Write Clock is not, then both CBLOWC and CBLOF will be set. CBLOF can generate an interrupt to the microprocessor assuming that the appropriate interrupt enable bit is 1 (register 06H, bit 2: INTENA2).

#### **CUBIT-Pro CELL INLET AND OUTLET PORTS**

The Cell Inlet and Outlet ports constitute the main interfaces for the cell traffic between the CUBIT-*Pro* and other devices in either the upper ATM or Physical (PHY) Layers. Several interfaces are supported by the device: UTOPIA 8-bit mode, TranSwitch 16-Bit mode, TranSwitch ALI-25 device interface mode, and Back-to-Back (CUBIT-*Pro*-to-CUBIT-*Pro* interface).

The CUBIT-Pro can provide address translation if selected via the input pin  $\overline{TRAN}$  (pin 154). If no translation is selected, the external hardware must provide the CellBus Bus Routing Header, the Tandem Routing Header (optional), and the ATM cell. If translation mode is selected, the hardware is required only to provide the ATM cell and the CUBIT-Pro will perform the translation based on the information programmed into the attached translation SRAM.

For all the modes the cell size is selectable via external pins <u>LMODE2</u>, <u>LMODE1</u> and <u>LMODE0</u> (pins 156, 157, and 158, respectively), as described below. This feature permits the CUBIT-*Pro* to accommodate the requirements for different designs.

Additionally, the UTOPIA and 16-Bit modes can be selected to behave as either the master (ATM layer device) or the slave (PHY layer device). The selection between ATM and PHY layer device for the UTOPIA and 16-Bit modes is made via the PHYEN pin (pin 48), where a low enables PHY layer device operation.

The CUBIT-*Pro* allows the selection of the clock for the cell Inlet/Outlet operation from three different sources: *CellBus* bus clocks (CBRC, pin 78 and CBWC, pin 77), processor clock (PCLK, pin 32), or an externally supplied clock (LCLOCK, pin 45). The clock selected will be used for the UTOPIA and 16-Bit ATM layer device modes, the ALI-25 (cell inlet clock) mode, and the Back-to-Back (cell inlet clock) mode, for which the CUBIT-*Pro* sources the interface clock. For all other modes the clock is an input to the CUBIT-*Pro*. The selection of the clock source for the cell interfaces is performed via two control bits in register 0BH: CLKS1, CLKS0. The coding for the clock selection is as follows:

CLKS1, CLKS0 = 0,0: Cell interface clock = CellBus bus clock divided by  $2^{LINEDIV}$  CLKS1, CLKS0 = 0,1: Cell interface clock = LCLOCK clock divided by  $2^{LINEDIV}$  CLKS1, CLKS0 = 1,0: Cell interface clock = PCLK clock divided by  $2^{LINEDIV}$  CLKS1, CLKS0 = 1,1: Reserved, do not use

## 8-Bit UTOPIA Mode - ATM and PHY Layer Emulation

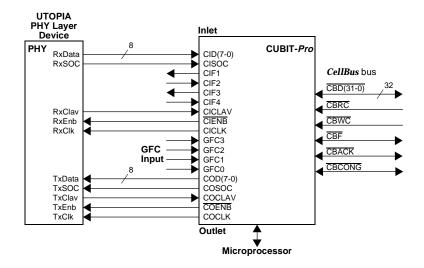

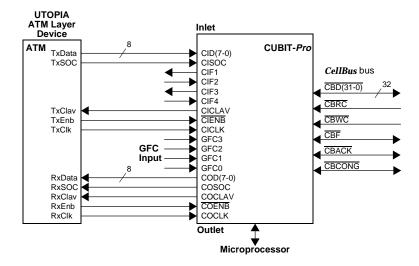

Typical signal connections for the CUBIT-*Pro* when operating in UTOPIA mode are illustrated in Figures 6 and 7, for ATM Layer and PHY Layer cell level handshake modes, respectively. The operating mode options for UTOPIA mode are controlled by the input pins TRAN, PHYEN, LMODE2, LMODE1 and LMODE0, as indicated in the tables of Figures 6 and 7. TRAN selects the internal translation mode, if asserted. In UTOPIA mode, PHYEN determines whether the CUBIT-*Pro* emulates an ATM or PHY device. LMODE2, LMODE1 and LMODE0 determine the cell inlet/outlet cell size.

When internal translation is used, the cell I/O is exactly that defined by UTOPIA, with 53-byte inlet cells. For applications in which the internal translation function is not used, the timing and logical flow of the cell I/O is still identical to that of UTOPIA, except that 57-byte or 55-byte inlet cells are used, instead of 53. The additional bytes are the Routing Header bytes which would be inserted by the CUBIT-*Pro* if the translation function were used, but are instead added by an external translation function. The pin connections and the different inlet and outlet byte counts per cell in the various modes are shown in the table of Figure 6 for ATM Layer emulation. Similarly, Figure 7 shows the pin connections and byte counts for PHY Layer emulation.

The ABRENA pin must be held high or left floating (it has internal pull-up) for proper UTOPIA mode operation.

Figure 6. ATM Layer Emulation 8-Bit UTOPIA Mode Signal Connections and Operating Mode Selection

| PHYEN | TRAN | LMODE2 | LMODE1 | LMODE0 | Operating Mode: Inlet                                                                                 | Operating Mode: Outlet                                  |

|-------|------|--------|--------|--------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| High  | High | High   | Х      | High   | UTOPIA, 57 bytes: cell plus <i>CellBus</i> Bus Routing Header plus two bytes of Tandem Routing Header | UTOPIA, 53-byte cell                                    |

| High  | High | High   | High   | Low    | UTOPIA, 57 bytes: cell plus <i>CellBus</i> Bus Routing Header plus two bytes of Tandem Routing Header | UTOPIA, 55 bytes: cell<br>plus Tandem Routing<br>Header |

| High  | High | Low    | Low    | High   | UTOPIA, 55 bytes: cell plus <i>CellBus</i> Bus Routing Header                                         | UTOPIA, 53-byte cell                                    |

| High  | High | Low    | Low    | Low    | UTOPIA, 55 bytes: cell plus <i>CellBus</i> Bus Routing Header                                         | UTOPIA, 55 bytes: cell<br>plus Tandem Routing<br>Header |

| High  | Low  | High   | High   | High   | UTOPIA, 53-byte cell                                                                                  | UTOPIA, 53-byte cell                                    |

| High  | Low  | High   | High   | Low    | UTOPIA, 53-byte cell                                                                                  | UTOPIA, 55 bytes: cell<br>plus Tandem Routing<br>Header |

| High  | High | Low    | High   | High   | Reserved                                                                                              | Reserved                                                |

| High  | Low  | Low    | High   | High   | Reserved                                                                                              | Reserved                                                |

| High  | Low  | Low    | High   | Low    | Reserved Reserved                                                                                     |                                                         |

| High  | Low  | Low    | Low    | High   | Reserved                                                                                              | Reserved                                                |

Note: High =  $V_{DD5}$  = +5V; Low =  $V_{SS}$  = Ground; X = Don't Care

Figure 7. PHY Layer Emulation 8-Bit UTOPIA Mode Signal Connections and Operating Mode Selection

| PHYEN | TRAN | LMODE2 | LMODE1 | LMODE0 | Operating Mode: Inlet                                                                                 | Operating Mode: Outlet                                  |

|-------|------|--------|--------|--------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Low   | High | High   | Х      | High   | UTOPIA, 57 bytes: cell plus <i>CellBus</i> Bus Routing Header plus two bytes of Tandem Routing Header | UTOPIA, 53-byte cell                                    |

| Low   | High | High   | High   | Low    | UTOPIA, 57 bytes: cell plus <i>CellBus</i> Bus Routing Header plus two bytes of Tandem Routing Header | UTOPIA, 55 bytes: cell<br>plus Tandem Routing<br>Header |

| Low   | High | Low    | Low    | High   | UTOPIA, 55 bytes: cell plus <i>CellBus</i> Bus Routing Header                                         | UTOPIA, 53-byte cell                                    |

| Low   | High | Low    | Low    | Low    | UTOPIA, 55 bytes: cell plus <i>CellBus</i> Bus Routing Header                                         | UTOPIA, 55 bytes: cell<br>plus Tandem Routing<br>Header |

| Low   | Low  | High   | High   | High   | UTOPIA, 53-byte cell                                                                                  | UTOPIA, 53-byte cell                                    |

| Low   | Low  | High   | High   | Low    | UTOPIA, 53-byte cell                                                                                  | UTOPIA, 55 bytes: cell<br>plus Tandem Routing<br>Header |

| Low   | High | Low    | High   | High   | Reserved                                                                                              | Reserved                                                |

| Low   | Low  | Low    | High   | High   | Reserved Reserved                                                                                     |                                                         |

| Low   | Low  | Low    | High   | Low    | Reserved Reserved                                                                                     |                                                         |

| Low   | Low  | Low    | Low    | High   | Reserved                                                                                              | Reserved                                                |

#### **ALI-25 Mode**

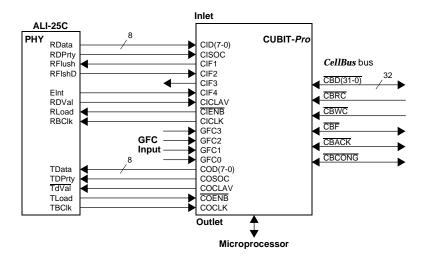

The CUBIT-*Pro* supports the ALI-25 interface devices, and connects directly to the ALI-25C with no glue logic, as shown in Figure 8. In ALI-25 mode there is always translation, because the ALI-25C device cannot produce a *CellBus* Bus Routing Header or Tandem Routing Header. Two exception conditions in the ALI-25C are supported through CUBIT-*Pro* pins CIF1, CIF2 and CIF4. The output pin CIF1 connects directly to the RFlush input pin of the ALI-25C. If, due to an error condition in the ALI-25C, RDVal is unexpectedly de-asserted at its CICLAV input, the CUBIT-*Pro* will assert CIF1 to flush the ALI-25C and declare a start-of-cell (SOC) error. The ALI-25C uses its RFlshD output pin to acknowledge via the CUBIT-*Pro*'s CIF2 input pin that the flush was completed. The second exception condition accommodated is the flagging of a HEC error by the ALI-25C. If a HEC error is found, the ALI-25C asserts its EInt output pin, which drives the CIF4 input pin of the CUBIT-*Pro* and causes it to increment its HEC Error Counter.

The ABRENA pin must be held high or left floating (it has internal pull-up).

| PHYEN | TRAN | LMODE2 | LMODE1 | LMODE0 | Operating Mode: Inlet | Operating Mode: Outlet |

|-------|------|--------|--------|--------|-----------------------|------------------------|

| Х     | Low  | High   | Low    | High   | ALI-25: 53-byte cell  | ALI-25: 53-byte cell   |

Figure 8. ALI-25 Mode Signal Connections and Operating Mode Selection

#### **Back-to-Back Mode**

The Back-to-Back mode is used to support interconnection of two *CellBus* buses, as shown in Figure 9. If pin TRAN is low, each of the CUBIT-Pros has a translation memory connected, the cell address translation function is active, and the inlet cells are 53 bytes long. The cells from the outlet can either be 55 or 53 bytes long. If 55 bytes are selected, the cell will carry the Tandem Routing Header from the *CellBus* bus.

If TRAN is high, the translation function is not used. The transfers into the cell inlet will 55 bytes long. The two initial bytes are presented to the CUBIT-*Pro* as the *CellBus* Bus Routing Header. The cell outlet can present cells of either 55 or 53 bytes, whether or not internal translation is performed on the cell inlet side. If 55 bytes are selected, the cell will carry the Tandem Routing Header from the *CellBus* bus.

The cell outlet will carry two extra bytes which are the Tandem Routing Header from the *CellBus* bus. These two bytes are presented to the inlet port of the connected CUBIT-*Pro*, which uses them as a *CellBus* Bus Routing Header when it puts the cell on the bus.

In order to avoid re-transmission of multicast or broadcast cells from one *CellBus* bus to another, and back again, a CUBIT-*Pro* which is operating in the Back-to-Back mode will reject all incoming broadcast and multicast cells which originated from its own inlet side.

The timing of this mode is similar to that for UTOPIA ATM Layer emulation mode, except that the directionality of the COCLAV, COENB and COCLK signals is reversed, as shown in the connections diagrams of Figures 6 and 9.

The ABRENA pin must be held high or left floating (it has internal pull-up).

| PHYEN | TRAN | LMODE2 | LMODE1 | LMODE0 | Operating Mode: Inlet                                                            | Operating Mode: Outlet                                                     |

|-------|------|--------|--------|--------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Х     | High | High   | Low    | Low    | Back-to-Back: 55 bytes, cell plus two bytes of <i>CellBus</i> Bus Routing Header | Back-to-Back: 55 bytes, cell<br>plus two bytes of Tandem<br>Routing Header |

| Х     | Low  | High   | Low    | Low    | Back-to-Back: 53-byte cell                                                       | Back-to-Back: 53-byte cell                                                 |

| Х     | Low  | Low    | Low    | Low    | Back-to-Back: 53-byte cell                                                       | Back-to-Back: 55 bytes, cell<br>plus two bytes of Tandem<br>Routing Header |

| Х     | High | Low    | High   | Low    | Back-to-Back: 55 bytes, cell plus two bytes of <i>CellBus</i> Bus Routing Header | Back-to-Back: 53-byte cell                                                 |

Figure 9. Back-to-Back Mode Signal Connections and Operating Mode Selection

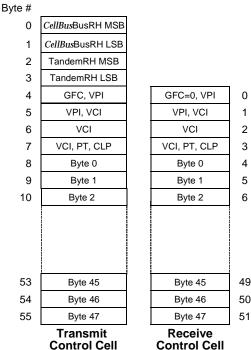

# Byte Ordering for UTOPIA, ALI-25 and Back-to-Back Modes

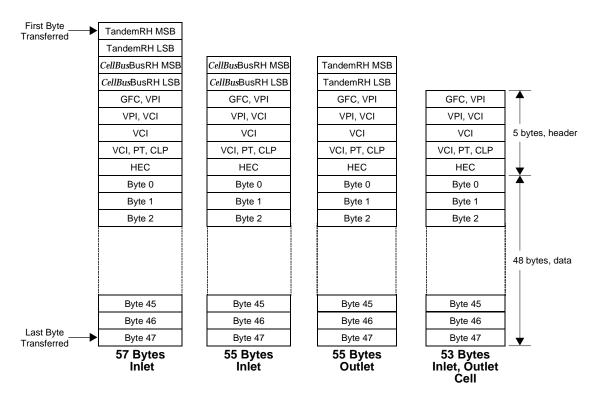

Byte ordering for the three cell inlet and outlet alternatives described above is illustrated in Figure 10.

Note: RH = Routing Header

Figure 10. Byte Ordering on Cell Inlet and Outlet in UTOPIA, ALI-25 and Back-to-Back Modes

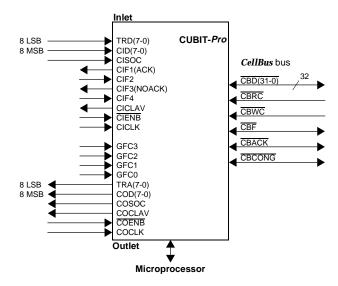

## 16-Bit Cell Interface Mode - ATM and PHY Layer Emulation

16-Bit cell interface mode can be selected to emulate an ATM Layer UTOPIA device, or alternatively to emulate a PHY Layer UTOPIA device, as shown in Figures 11 and 12, respectively.

16-Bit mode is enabled by setting device strap pin ABRENA low, with the settings of TRAN, LMODE2, LMODE1 and LMODE0 selected according to the table in Figure 11 for ATM Layer emulation, or according to the table in Figure 12 for PHY Layer emulation. The PHY Layer emulation is enabled with PHYEN.

The timing of the 16-Bit mode is identical to that of the UTOPIA mode, but the data width is expanded to a word of 16 bits in and out. The translation RAM is not used in this case. The extra 8 inlet bits are connected to the pins used for the data of the translation RAM, TRD (7-0), and the extra 8 outlet pins are the pins for the 8 LSB of the translation RAM address output, TRA (7-0).

| PHYEN | TRAN | LMODE2 | LMODE1 | LMODE0 | Operating Mode: Inlet                                                                                                         | Operating Mode: Outlet                                              |

|-------|------|--------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| High  | Х    | Low    | High   | Low    | 16-Bit: 29 words, cell plus<br>one word of Tandem<br>Routing Header, plus one<br>word of <i>CellBus</i> Bus<br>Routing Header | 16-Bit: 28 words, cell plus<br>one word of Tandem<br>Routing Header |

| High  | X    | Low    | High   | High   | 16-Bit: 29 words, cell plus<br>one word of Tandem<br>Routing Header, plus one<br>word of <i>CellBus</i> Bus<br>Routing Header | 16-Bit: 27-word cell                                                |

| High  | Х    | High   | Х      | Х      | 16-Bit: 28 words, cell, plus<br>one word of <i>CellBus</i> Bus<br>Routing Header                                              | 16-Bit: 28 words, cell plus<br>one word of Tandem<br>Routing Header |

| High  | Х    | Low    | Low    | High   | 16-Bit: 28 words, cell, plus one word of <i>CellBus</i> Bus Routing Header                                                    |                                                                     |

| High  | Х    | Low    | Low    | Low    | Reserved                                                                                                                      | Reserved                                                            |

Figure 11. ATM Layer Emulation 16-Bit Mode Signal Connections and Operating Mode Selection

Figure 12. PHY Layer Emulation 16-Bit Mode Signal Connections and Operating Mode Selection

| PHYEN | TRAN | LMODE2 | LMODE1 | LMODE0 | Operating Mode: Inlet                                                                                                         | Operating Mode: Outlet                                              |

|-------|------|--------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Low   | Х    | Low    | High   | Low    | 16-Bit: 29 words, cell plus<br>one word of Tandem<br>Routing Header, plus one<br>word of <i>CellBus</i> Bus<br>Routing Header | 16-Bit: 28 words, cell plus<br>one word of Tandem<br>Routing Header |

| Low   | х    | Low    | High   | High   | 16-Bit: 29 words, cell plus<br>one word of Tandem<br>Routing Header, plus one<br>word of <i>CellBus</i> Bus<br>Routing Header | 16-Bit: 27-word cell                                                |

| Low   | Х    | High   | Х      | Х      | 16-Bit: 28 words, cell, plus<br>one word of <i>CellBus</i> Bus<br>Routing Header                                              | 16-Bit: 28 words, cell plus<br>one word of Tandem<br>Routing Header |

| Low   | Х    | Low    | Low    | High   | 16-Bit: 28 words, cell, plus<br>one word of <i>CellBus</i> Bus<br>Routing Header                                              | 16-Bit: 27-word cell                                                |

| Low   | Х    | Low    | Low    | Low    | Reserved                                                                                                                      | Reserved                                                            |

# Word Ordering for 16-Bit Cell Interface Mode

The word ordering for 16-Bit mode is shown in Figure 13.

|                            | 29-Wo            | rd Inlet         |                  |                  |              |              |           |              |

|----------------------------|------------------|------------------|------------------|------------------|--------------|--------------|-----------|--------------|

| First Word_<br>Transferred | TandemRH MSB     | TandemRH LSB     | 28-Word          | l Inlet          | 28-Word      | d Outlet     |           |              |

| . rans.on oa               | CellBusBusRH MSB | CellBusBusRH LSB | CellBusBusRH MSB | CellBusBusRH LSB | TandemRH MSB | TandemRH LSB | 27-Wo     | ord Outlet   |

|                            | GFC, VPI         | VPI, VCI         | GFC, VPI         | VPI, VCI         | GFC, VPI     | VPI, VCI     | GFC, VPI  | VPI, VCI     |

|                            | VCI              | VCI, PT, CLP     | VCI              | VCI, PT, CLP     | VCI          | VCI, PT, CLP | VCI       | VCI, PT, CLP |

|                            | HEC              | Undefined        | HEC              | Undefined        | HEC          | Undefined    | HEC       | Undefined    |

|                            | Byte 0           | Byte 1           | Byte 0           | Byte 1           | Byte 0       | Byte 1       | Byte 0    | Byte 1       |

|                            | Byte 2           | Byte 3           | Byte 2           | Byte 3           | Byte 2       | Byte 3       | Byte 2    | Byte 3       |

|                            |                  |                  |                  |                  |              |              |           |              |

|                            |                  |                  |                  |                  |              |              |           |              |

|                            |                  |                  |                  |                  |              |              |           |              |

|                            | Byte 42          | Byte 43          | Byte 42          | Byte 43          | Byte 42      | Byte 43      | Byte 42   | Byte 43      |

|                            | Byte 44          | Byte 45          | Byte 44          | Byte 45          | Byte 44      | Byte 45      | Byte 44   | Byte 45      |

| Last Word                  | Byte 46          | Byte 47          | Byte 46          | Byte 47          | Byte 46      | Byte 47      | Byte 46   | Byte 47      |

|                            | High Byte        | Low Byte         | High Byte        | Low Byte         | High Byte    | Low Byte     | High Byte | Low Byte     |

Figure 13. Word Ordering on Cell Inlet and Outlet in 16-Bit Mode

#### TRAFFIC MANAGEMENT FUNCTIONS

# Dynamic Generic Flow Control (GFC) Field Insertion

The CUBIT-*Pro* can insert the value of the first nibble of the ATM cell header in real time. The value of the GFC nibble is supplied to the CUBIT-*Pro* via the input pins GFC(3-0). The insertion of the GFC value is enabled via the control bit GFCENA.

Figure 14. GFC Insertion on the Outlet Queue (GFCENA = 1)

If control bit GFCENA (Control Register Address 0CH, Bit 1) is set to one, then the state of the four Generic Flow Control input pins GFC(3-0) will be accepted during the leading rising edge of the clock for the first byte of the ATM cell header and inserted as an outgoing GFC on the following cell (see timing diagram in Figure 47 for details). Therefore the GFC value is inserted into the next outgoing cell.

# Forward Explicit Congestion Notification (FECN)

The CUBIT-*Pro* can notify an impending congested state by setting to one the middle bit of the Payload Type (PT) field in the ATM cell header. This Explicit Forward Congestion Indication bit (EFCI) will be asserted on a cell if both of two conditions occur at the same time:

- a) Bit 0 in register 0CH is set to one (IFECN = 1), and

- b) QM (bit 2 in register 0CH) = 0 and VBR Limit reached, or QM=1 and VBR Limit or CBR Limit reached.

The activation of the EFCI bit in the single-queue (QM = 0) and split-queue (QM = 1) modes is illustrated in Figures 15 and 16, respectively.

Note: The IFECN control bit is set to 1. The EFCI congestion indication is the middle bit of the PT sequence (X0X or X1X). Its value is determined when the cell leaves the queue.

Figure 15. Example of Congestion Indication in Single-Queue Mode (QM = 0)

Figure 15 shows a starting condition for the single-queue mode soon after the congestion conditions a) and b) have both become present, with three cells in the queue when VBRLIMIT is set to 2. Cells #1, #2 and #3 reached the Sync FIFO before the congestion occurred, so they are not marked with a congestion indication and have a PT value of X0X. The first cell in the queue (cell #4) is marked with a congestion indication (PT = X1X) and it moves into the Sync FIFO when the outlet link is free and Cell #1 is sent to the cell outlet port. Cells #5 and #6 then shift to the left, putting Cell #6 at the VBRLIMIT = 2 boundary, so congestion persists and Cell #5 is also marked with PT = X1X. When this cell moves into the Sync FIFO, Cell #6 shifts left and it is the only cell left in the queue, assuming no more cells have joined the queue. Since the queue length of 1 is now less than VBRLIMIT = 2, condition b) no longer exists and cell #6 carries no congestion marking (PT = X0X).

Figure 16 shows a starting condition for the split-queue mode some time after congestion conditions a) and b) have both become present, with three cells in the CBR cell queue when CBRLIMIT = 3 and two cells in the VBR cell queue when VBRLIMIT = 2 (i.e., both queues are at the congestion level).

Note: The IFECN control bit is set to 1. The EFCI congestion indication is the middle bit of the PT sequence (X0X or X1X). Its value is determined when the cell leaves the queue.

Figure 16. Example of Congestion Indication in Split-Queue Mode (QM=1)

As before, cells #1, #2 and #3 left the queues before the congestion occurred and are not marked for congestion indication (PT = X0X). When the outlet link becomes free and the cells in the Sync FIFO shift to the left, cells flow in to the Sync FIFO from the four data cell queues in priority order. Since the VBR queue contains two cells when VBRLIMIT = 2, congestion continues to exist while all cells in the CBR cell queue are moved into the Sync FIFO, so cells #4, #5 and #6 are marked with congestion indications (PT = X1X). Now, assuming no more cells are joining the queues, the CBR cell queue is empty but the VBR cell queue is still at the VBRLIMIT value with two cells, so cell #7 is also marked with a congestion indication. But when it moves to the Sync FIFO only one cell is left in the VBR cell queue, so conditions a) and b) no longer both exist, and this cell #8 is not marked with a congestion indication (PT = X0X).

# Congestion Indication from CellBus Bus to Cell Inlet

In the event of congestion being experienced at the output port of the receiving CUBIT-*Pro*, three bits are relayed back to the sending CUBIT-*Pro* to allow for congestion control. The output signals provided by the sending CUBIT-*Pro* are:

- CONGOUT: This output pin signal has a dual function which can be selected with bit EBP (bit 2 in register 0EH). If EBP=0 (default at power-up/reset) CONGOUT is a straight GTL-to-CMOS translation of the *CellBus* bus signal CBCONG. If EBP=1, then CONGOUT is an indication that the receiving CUBIT-*Pro* is experiencing congestion or impending congestion. These two situations correspond to the case where the outlet queue of the receiving CUBIT-*Pro* is full or the congestion limit (almost full) for that queue has been reached, respectively. In the case of almost full the cell will not be lost if CLP=0 in cycle 2, but a full queue will not accept any cells. In this case, a NACK will also be received. A pulse is available on the CONGOUT output (pin 155) of the CUBIT-*Pro* sending the cell after a receiving CUBIT-*Pro* experiences congestion (for UTOPIA, 16-Bit, and Back-to-Back modes).

- ACK: Positive acknowledge which indicates that the cell was accepted at the destination CUBIT-Pro. A pulse is provided on the CIF1 output (pin 118) of the CUBIT-Pro sending the cell if the cell is successfully accepted (for UTOPIA, 16-Bit, and Back-to-Back modes).

- NACK: Negative acknowledge which indicates the cell was not forwarded to the outlet queue of the receiving CUBIT-Pro. A pulse is provided on the CIF3 output (pin 115) of the CUBIT-Pro sending the cell if the cell is not forwarded, but dropped (for UTOPIA, 16-Bit, and Back-to-Back modes).

Note: The EBP bit (address 0EH, bit 2) must be set to enable the ACK and NACK functions of CIF1 and CIF3 in the UTOPIA and back-to-back modes. The ACK and NACK functions of CIF1 and CIF3 are always enabled in the 16-Bit mode.

## Paralleling Cell Inlet/Outlet Ports for Redundancy

If the control bit ONLINE (control register address 0CH, bit 7) is set to zero, then all of the CUBIT-*Pro* cell outlet interface output pins will be taken to the high impedance (Hi-Z) state and the cell inlet data input pins will be disabled. Thus two CUBIT-Pros may be paralleled for redundancy, each connected to a separate *CellBus* bus. Cells will only be accepted from, or sent to, the line by the CUBIT-*Pro* in which ONLINE = 1.

## **INLET-SIDE TRANSLATION**

## Introduction

The translation function on the inlet side operates using information stored in an external static RAM, and can provide the following functions:

Virtual Path Identifier (VPI) translation or VPI/VCI translation (where VCI is Virtual Circuit Identifier), and *CellBus* Bus Routing Header insertion, and Tandem Routing Header insertion, and F4 flow cell routing, and F5 flow cell routing.

All translation operations start by performing a translation table lookup based on the VPI number of the incoming cell. Within the routing table record for that VPI is control information for that VPI, indicating whether cells are to be routed based on VPI number alone or on VPI and VCI.

If VPI-only routing is selected, a translated VPI number, accompanied by *CellBus* Bus and Tandem Routing Headers, is retrieved from the translation record for that VPI. In this case, the VCI number of the incoming cell is not changed. If VPI translation is selected, separate routing for F4 OAM flow cells and RM-VPC cells on that VPI can be programmed, allowing selective handling of these OAM-cells and RM-cells by a *CellBus* bus system.

If the VPI is instead programmed for VCI translation, then a two-step procedure is used to accomplish the translation. The VPI record, accessed first, indicates the size and position in memory of the VCI translation table. Using this information, and the VCI address of the cell, a VCI translation record is accessed. This translation record contains the VPI and VCI numbers to be assigned to the cell, along with the *CellBus* Bus and Tandem Routing Headers. When VPI/VCI translation is selected, separate routing for F5 OAM flow cells and RM-VCC cells on that VCI can be programmed, allowing selective handling of these OAM-cells and RM-cells in a manner similar to that of F4 OAM flow cells and RM-VPC cells.

In both cases, the cells with the translated headers and *CellBus* Bus and Tandem Routing Headers are forwarded to the bus in sequential order. Translation does not add delay to cells passing through the inlet side to the *CellBus* bus.

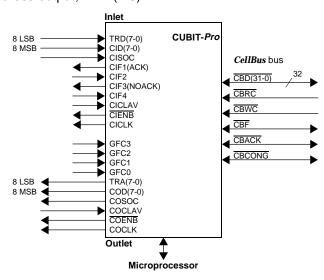

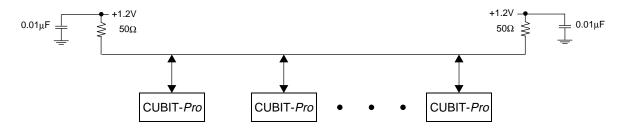

#### **Translation RAM Connections**

The CUBIT-*Pro* can address up to 256k bytes of translation SRAM (TRAM). The connections to the TRAM are shown in Figure 17. The TRAM access time requirement is dependent upon the cell inlet clock speed (i.e., in ATM Layer mode: *CellBus* bus clock, or PCLK, or LCLOCK; in PHY Layer mode: CICLK), see Figures 33 and 34. An access time of 35 nanoseconds or less will support the maximum *CellBus* bus speed.

Figure 17. Translation RAM Connections

The chip select should be implemented according to the number of SRAM devices used in the design. If a single 256k x 8 SRAM is used, the memory can be permanently selected, or if a low-power application is required then the memory can be selected only when the CUBIT-Pro needs to access the SRAM (use  $\overline{TROE}$  and  $\overline{TRWE}$ , as shown in Figure 17).

## **Translation RAM Control**

When the CUBIT-*Pro* device is configured to perform translation (input pin TRAN low), it replaces received values of VPI or VPI and VCI numbers with new values, and adds Routing Headers to the cells forwarded to the *CellBus* bus. The VPI/VCI number and Routing Header information that is inserted comes from translation record entries in the TRAM. The TRAM is organized into a block of VPI records and a block of VCI records, the contents of which are established by system control.

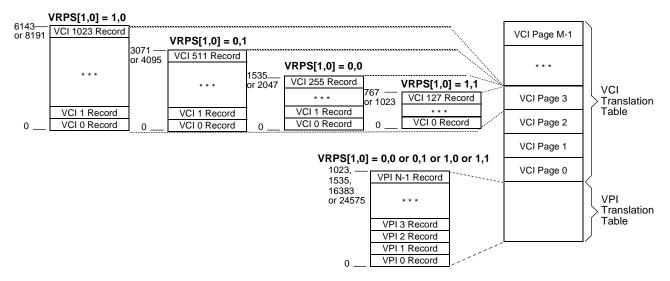

## **Translation RAM Organization**

The translation RAM partitioning is shown in Figure 18. The lower portion of the TRAM contains the translation records for VPIs. When the UNI mode is enabled (control bit UNI=1), the number of VPI entries is 256. When NNI mode is enabled (UNI=0), 4096 VPI entries are present.

Depending on whether the Tandem Routing Header is enabled the VP Record has: four bytes if the Tandem Routing Header (TRH) is not used (control bit TRHENA=0), and six bytes if the TRH is used (TRHENA=1). The size of the VPI memory space in this mode ranges from 1024 bytes (UNI mode, no TRH, 4 x 256) to 24576 bytes (NNI and TRH, 6 x 4096).

The memory space above the VPI section is the VCI translation record storage space, divided into a number of VCI pages. Each VCI page contains the translation records for 128, 256, 512, or 1024 VCIs.

Depending on whether Tandem Routing Header is enabled the VC Record has: six bytes if the Tandem Routing Header (TRH) is not used (control bit TRHENA=0), and eight bytes if the TRH is used (TRHENA=1).

The number of VCI records per page (VRP) depends on the settings of the VRPS[1,0] control bits in register 0EH as follows:

VRPS[1,0]=0,0: VRP is 256

VRPS[1,0]=0,1: VRP is 512

VRPS[1,0]=1,0: VRP is 1024

VRPS[1,0]=1,1: VRP is 128

The total size of the TRAM which the CUBIT-*Pro* can support is up to 262,144 bytes (256k). Hence, the number of VCI translation table pages which can be supported is a function of memory size, and the states of control bits UNI and TRHENA. For example, the maximum number (M) of VCI memory pages, for maximum memory size, is as follows:

VRPS[1,0]=0,0: VRP is 256

if UNI=1, TRHENA = 1; M = (262144-(256\*6))/(256\*8) = 127 VCI Pages,

if UNI=1, TRHENA = 0; M = (262144-(256\*4))/(256\*6) = 170 VCI Pages.

VRPS[1,0]=0,1: VRP is 512

if UNI=1, TRHENA = 1; M = (262144-(256\*6))/(512\*8) = 63 VCI Pages,

if UNI=1, TRHENA = 0; M = (262144-(256\*4))/(512\*6) = 85 VCI Pages.

VRPS[1,0]=1,0: VRP is 1024

if UNI=1, TRHENA = 1; M = (262144-(256\*6))/(1024\*8) = 31 VCI Pages,

if UNI=1, TRHENA = 0; M = (262144-(256\*4))/(1024\*6) = 42 VCI Pages.

VRPS[1,0]=1,1: VRP is 128

if UNI=1, TRHENA = 1; M = (262144-(256\*6))/(128\*8) = 254 VCI Pages,

if UNI=1, TRHENA = 0; M = Min[(262144-(256\*4))/(128\*6), 256] = Min [340,256] = 256 VCI Pages.

if VRPS[1,0]=1,1, VRP is 128. The maximum number of addressable pages is 256, even though, theoretically, 340 pages could fit in a SRAM of 256k bytes.

Figure 18. Translation RAM Organization

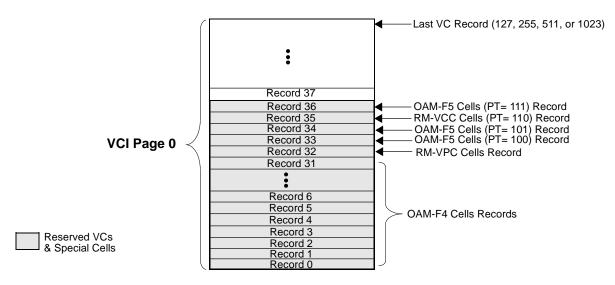

# VCI Page 0 Organization

This page may optionally be used for OAM-cells routing, RM-cells routing, or data cells routing. For OAM/RM and reserved VCs, bit OAMRMEN (bit 1 in register 0EH) must be set to 1. If OAM/RM routing is enabled (OAMRMEN=1) then the organization of VCI Page 0 is as shown in Figure 19.

Figure 19. VCI Page 0 Organization (Bit OAMRMEN=1)

If the device is required to operate in CUBIT TXC-05801 applications, then bit OAMRMEN must be set to 0, which is the power-up/reset default.

#### **Translation Procedure**

Translation is performed in a two-step procedure, starting with examining the incoming VPI number. A full 8-bit (UNI=1) or 12-bit (UNI=0) VPI number may be used. The incoming VPI number is used to address a VPI translation record. If the translation is to be done on VPI only, leaving the VCI number intact, then the VPI number and routing header are contained in the VPI translation record. If VPI and VCI translation is to be done, then the VPI record contains a pointer to the location of one or more "pages" of VCI translation records. Each "page" is a set of translation records for either 128, 256, 512, or 1024 consecutive VCI numbers (depending on the settings of bits VRPS[1,0] in register 0EH). Up to sixteen such VCI pages may be assigned to any VPI. The only restriction is that the VCI pages for each VPI must be assigned in consecutive VCI address space from zero upwards. Within this assigned space, the VCI number of the incoming cell is used to address a particular VCI translation record containing the new VPI and VCI numbers and the routing header.

OAM/RM cells are routed either from the VP record or VC record that is marked for this special cells routing, as detailed in the section below entitled "OAM-Cells and RM-Cells Record Format".

For the translation operation the CUBIT-*Pro* uses several data structures. These data structures can be of three different types:

VP Record VC Record

OAM/RM Record

Each of these records contains one or more control bits in the first byte of the record (byte 0), which determines whether the routing is per VP, per VC, or per OAM/RM cell. The control bits are described next.

#### Translation Records Control Bits

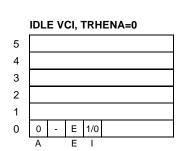

Four control bits, labelled as A, P, E and I, are used in byte 0 of translation records, as described below:

## Active (A) Bit:

If the A bit is set to one in a translation record, then that VPI or VCI is active. Cells received with this VPI or VCI will be translated and forwarded to the bus, unless bit I is set to one. If A=0, then cells received on this VPI or VCI will be considered misrouted, unless I=1.

## **VPI Translation Enable Bit (P):**

If this bit is one in a VPI translation record, then a VPI-only translation is made. If it is set to zero, a combined VPI and VCI translation is made.

# OAM/RM Cell Routing Enable Bit (E):

If bit E is set to one in a VPI record, then VCIs numbered 0 through 31 of that VPI will be routed according to OAM/RM records contained in record numbers 0 through 31 of VCI page zero. Additionally, if bit E is set to one in a VPI record, then cells of that VPI with VCI =6 and having the PT = 110 will be routed according to the OAM translation record contained in record number 32 of VCI page zero. Regular data cells (not conforming to the above rules) are routed according to the VP and/or VC record. If bit E is set to one in a VCI record, then cells of that VPI having the PT = 100, 101, 110, and 111(Payload Type Indicator, in ATM cell header) will be routed according to the OAM translation record contained in record numbers 33, 34, 35, and 36 of VCI page zero, respectively.

#### Ignore Bit (I):

If the ignore bit is one (I=1) in an active VP or VC (i.e., A=1 in the translation record) then incoming cells bearing this VP or VC number are discarded, but <u>not</u> counted as misrouted cells. If control bit NOTIGN (bit 5 in register 0EH) is set to 1, then connections with I=1 will be treated as if I=0.

## OAM/RM Routing Mode Bits (C1.C0):

These bits are used to determine on which VPI/VCI OAM/RM cells are routed. The possible combinations are:

- C1,C0 = 0,0: the cell header is translated according to the values in the OAM/RM record (this value and OAMRMEN=0 should be selected for applications supporting CUBIT TXC-05801 functionality)

- C1,C0 = 0,1: for F4 flow this virtual path connection (VPC) OAM cells/RM-VPC cells are not routed according to the OAM/RM record. Instead, these cells are routed according to the VP record corresponding to the incoming VP.

For F5 flow this virtual circuit connection (VCC) OAM cells/RM-VCC cells are not routed according to the OAM/RM record. Instead, these cells are routed according to the VC record corresponding to the incoming VP/VC combination.

- C1,C0 = 1,0: attach *CellBus* Bus Routing Header (CBRH) and Tandem Routing Header (TRH) only, and preserve the incoming VP/VC combination

- C1,C0 = 1,1: reserved

**Note:** In order to use Tandem Routing Header, TRHENA =1 must be selected regardless of the table values.

## CellBus Bus Routing Header

The *CellBus* Bus Routing Header is a 16-bit structure, which is formatted as described earlier in the *CellBus* Bus Cell Routing subsection. Additional detail is provided in Appendix A of "*CellBus* Bus Technical Manual and CUBIT-*Pro* Applications", TranSwitch document number TXC-05802-TM1.

## **Tandem Routing Header**

If the Tandem Routing Header is to be used as a *CellBus* Bus Routing Header, as when passed through a CUBIT-*Pro* in back-to-back mode, it must follow the same construction rules as a *CellBus* Bus Routing Header. If the Tandem Routing Header is used for some proprietary purposes, its format will follow a different specification.

## **Translation Record Formats**

# VPI Translation Record Formats

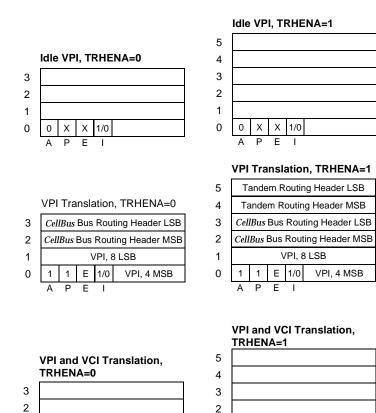

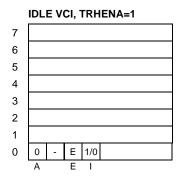

VPI translation records are four bytes long if TRHENA=0, or six bytes long if TRHENA=1, as shown in Figure 20. Each VPI may be either idle or busy. If it is busy, then each VPI may be set for VPI-only translation, or for combined VPI/VCI translation. The control bits (A, P, E and I) and Routing Headers are described in the preceding sections.

1

O

If the VPI is unused, then the MSB (Active bit, A) of relative address zero is set to zero, indicating idle. If a cell arrives with this VPI number, it is discarded and is counted as a misrouted cell.

If the VPI is busy and is to have VPI number translation only, then the A bit is set=1, and the P bit is set=1. In this case, the VPI to be inserted on the cell is contained in the 4 LSB of relative address zero (4 MSB of new VPI), and in relative address one (8 LSB of new VPI). *CellBus* Bus and Tandem Routing Headers are also contained in the next two or four bytes.

If the VPI is busy and is set for combined VPI/VCI number translation, a reference is generated to a VCI translation record. The VPI is set active (A=1), and is set for VCI translation (P=0). The 4 LSB of relative address zero contain the VCI Page Size, which is the number of assigned VCI pages, each of 128, 256, 512, or 1024 VCI records, allocated to this VPI (range from 1 to 16, where 0H=16). Relative address one contains the VCI Page Offset, which indicates where among the VCI pages the first utilized page starts.

Figure 20. VPI Translation Record Formats

VCI Page Size

VCI Page Offset

E 1/0

Е

The calculation of the start address for the VP record when there is no Tandem Routing Header (control bit TRHENA=0) is performed as follows:

$VP\_Start\_Addr = VP\# x 4$

If TRHENA=1 then:

1

VCI Page Offset

VCI Page Size

E 1/0

VP Start Addr = VP# x 6

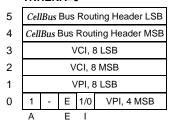

## VCI Translation Record Formats

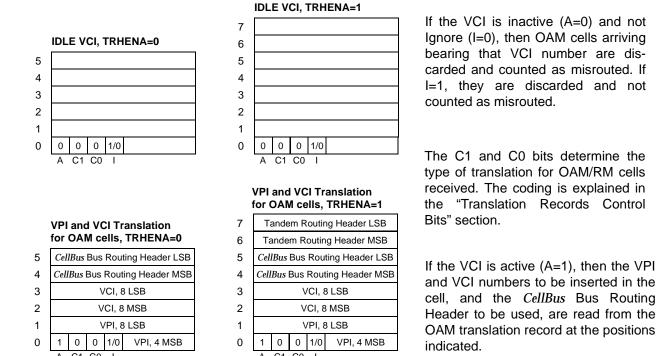

VCI translation records are six bytes long if TRHENA=0, and eight bytes long if TRHENA=1, as shown in Figure 21. Each VCI may be either idle or busy.

If the VCI is inactive (A=0) and not Ignore (I=0), then cells arriving bearing that VCI number are discarded and counted as misrouted. If I=1, they are discarded and not counted as misrouted.

# VPI and VCI Translation, TRHENA=0

VPI and VCI Translation,

If the VCI is active (A=1), then the VPI and VCI numbers to be inserted in the cell, and the *CellBus* Bus Routing Header to be used, are read from the VCI translation record at the positions indicated.

Figure 21. VCI Translation Record Formats

The calculation of the start address for the VC record uses information from the VP table addressed by the VP of the incoming cell, as well as information of the VCI of the incoming cell. The information required from the VP record is the VCI Page Offset (VPO). In the case with no Tandem Header Translation (control bit TRHENA=0 in register 0AH) and in UNI mode (control bit UNI=1 in register 0AH) the start address of the VC record corresponding to an incoming VP/VC, assuming a given number of VCI records per page (VRP, determined by the control bits VRPS1 and VRPS0 in register 0EH) is calculated (in decimal format) as follows:

$\label{eq:vc_start_Address} VC\_Start\_Address = 1024 + VPO \times VRP \times 6 + VCI \times 6$  or with TRHENA=1 and UNI=1:  $VC\_Start\_Address = 1536 + VPO \times VRP \times 8 + VCI \times 8$  or with TRHENA=0 and UNI=0:  $VC\_Start\_Address = 16384 + VPO \times VRP \times 6 + VCI \times 6$  or with TRHENA=1 and UNI=0:  $VC\_Start\_Address = 24576 + VPO \times VRP \times 8 + VCI \times 8.$

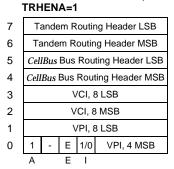

## OAM-Cells and RM-Cells Record Format

OAM/RM and reserved VC cells routing can be performed on any VP/VC combination with the appropriate programming of the E-bit in the VP or VC translation record, and setting OAMRMEN bit (bit 1 in register 0EH) to 1. For compatibility with CUBIT TXC-05801 applications, the bit OAMRMEN should be set to 0 (default).

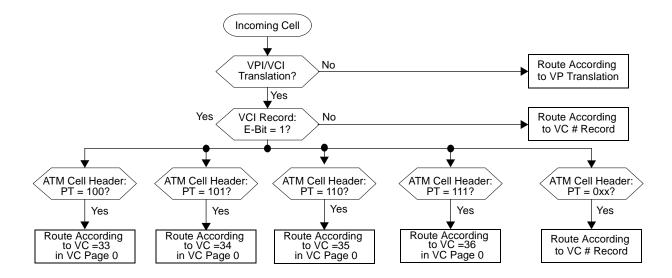

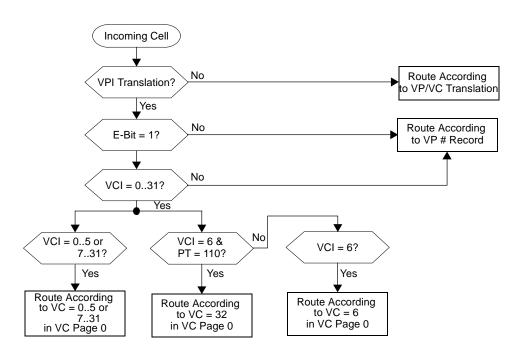

Both F4 and F5 flows are supported in the CUBIT-*Pro*. Depending on which flow is routed, two algorithms are used by the CUBIT-*Pro* (assuming OAMRMEN=1). The algorithm for F5-flow is depicted in Figure 22. The PT field of the ATM cell header coming in a VP/VC that is set for VP/VC translation (with E-bit set to 1 in the VC translation record) will be checked for all possible values and routed to VCI Page 0 according to the flow shown in Figure 22.

For F4 flow a cell coming in any VP will be sent to VCI Page 0 if the VCI is within numbers 0-31 (OAMRMEN=1) according to the algorithm shown in Figure 23.

Figure 22. OAM F5 and RM-VCC Cell Routing (Bit OAMRMEN=1)

Figure 23. OAM F4 and RM-VPC Cell Routing (Bit OAMRMEN=1)

The corresponding formats for OAM translation records are shown in Figure 24.

Note: OAM/RM Translation Records are optional. They are located in VCI page zero.

Figure 24. OAM/RM-Cells Translation Record Formats

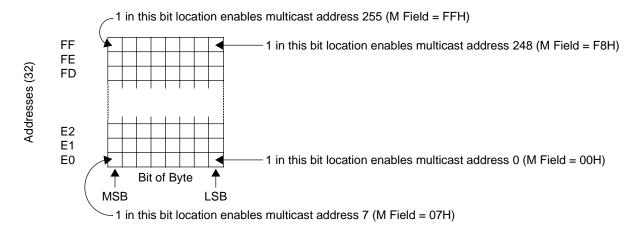

## **MULTICAST NUMBER MEMORY**

A multicast address control cell or multicast address data cell can be sent to a number of CUBIT-*Pro*s, and a single CUBIT-*Pro* can receive cells with a number of different addresses. This is controlled by the setup of the Multicast Number Memory (addresses E0H-FFH in the CUBIT-*Pro* memory map), which is a block of 32 bytes. Each of the 256 bits in the block maps to one multicast address, as shown in Figure 25. When a bit is set to 1, the CUBIT-*Pro* is enabled to receive the corresponding multicast address cell. Each CUBIT-*Pro* can be set to receive any or all of the 256 possible multicast addresses.