# **General Description**

GD16334 is a 32:4 multiplexer, intended for use with the GD16255, an STM-64 16:1 mutliplexer with PLL or in DSP applications with fast DAC's.

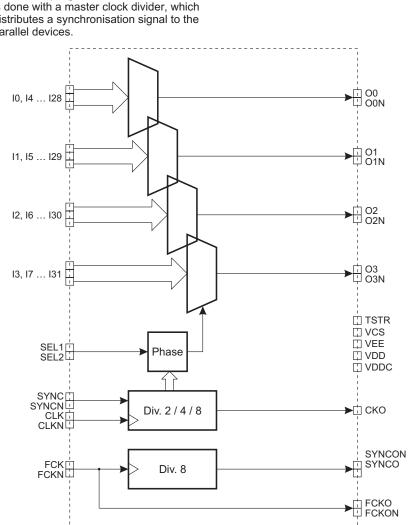

The GD16334 consists of:

- four 8:1 multiplexers

- ٠ a clock generator circuit

- ٠ a synchronisation circuit

The synchronisation circuit, enables a parallel coupling of several devices. This is done with a master clock divider, which distributes a synchronisation signal to the parallel devices.

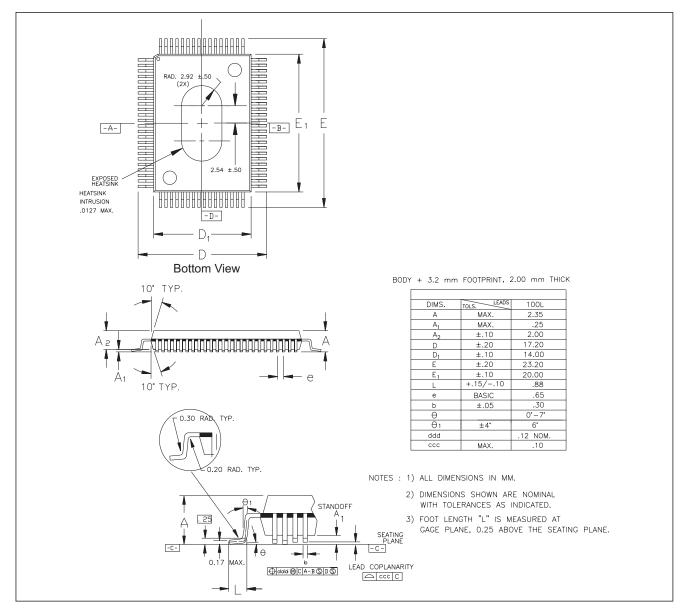

The GD16334 is provided in a 100 pin power enhanced plastic package.

The chip is designed for operation between -5 °C and +85 °C (case temperature).

# 622 MHz 32:4 Multiplexer GD16334

# Preliminary

#### Features

- Clock frequency to 622 MHz. •

- 32:4 MUX, obtained by four 8:1 synchronised MUX'es.

- High speed differential inputs, CML/PECL level.

- High speed differential CML outputs.

- Low speed inputs are CMOS level. .

- 100 pin QFP (14 x 20 mm) power en-. hanced plastic package.

- Power consumption: 2.0 W typical.

- Synchronisation of parallel devices, for wider bus widths.

- 5 V single supply operation.

# Applications

- **Tele Communication**

- STM-64

- **STM-16**

- OC-192 OC-48

- DSP

High speed DAC interface

Data Sheet Rev. 6

## **Functional Details**

#### Synchronisation

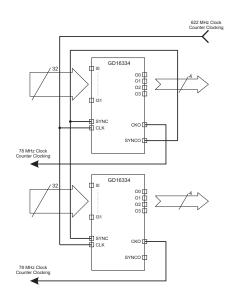

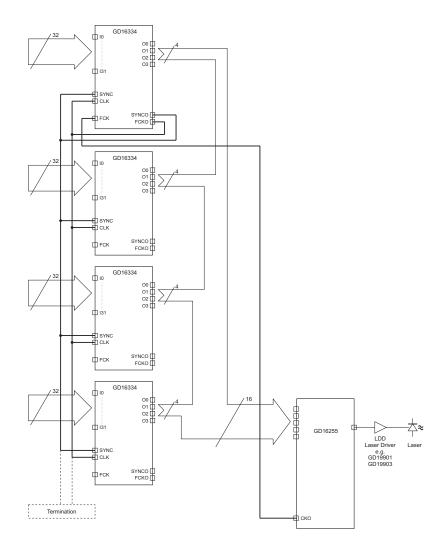

The GD16334 provides a synchronisation block that allows parallel operation of multiple devices for wider data width. When this is required only the synchronisation block in one GD16334 device is used as master controller, which drives the synchronisation input of all parallel connected (slave) MUX devices.

The synchronisation block provides a clock output (FCKO) and a SYNCO signal (which is a 1/8 clock signal) timed by the FCKO output. These signals are then daisy-chained to the CLK and SYNC inputs of all the MUX devices. This solution provides a fully synchronised parallel multiplexer structure, where all MUX data ports samples data in the same clock cycle.

The data inputs (FCK, CLK and SYNC) allow for either CML or PECL termination. Termination resistors must be provided externally (i.e.  $50 \Omega$  to V<sub>DD</sub> if CML or  $50 \Omega$  to V<sub>DD</sub> -2 V if PECL). The FCKO and SYNCO outputs are both open drain outputs accommodating the CLK and SYNC inputs in CML configuration.

There are two ways to connect the master clock, provided at the input to the GD16334's from the upstream device, with different timing constrains. Using the clock output (FCKO) from the synchronisation block, will give a good timing condition for the SYNC signal path, with respect to the clock. But it will put constrains on the timing at the data outputs, since the synchronisation block will add a delay to the master clock, with respect to the data coming from the upstream device (refer to Figure 1). Another approach is to feed the input clock directly to the CLK input of the MUX'es, maintaining the data/clock relations as given by the upstream device. This will however put constrains on the timing of the SYNC signal path. Depending on actual timing of the upstream device and actual board layout, both approaches may prove applicable.

In either case, to compensate for board delays use the far-end device as clock master such that the clock propagating the slave devices compensates delay on data propagating to the GD16255.

Figure 2. Maintaining fast clock < - > data relations

#### **Practical Considerations**

The SYNC and CLK control signals are differential high-speed control signals. Care should be taken to design the routing of these signals as transmission lines, i.e. as coplanar wave guides, or as strip lines. The signals should be routed without branches from the signal source with shortest possible distance to the first load, then onwards to the next load, and finally terminating in a resistor matching the transmission line impedance, normally 50  $\Omega$ . The transmission line should not have any branches in order to minimise stub effects (reflections).

Data Sheet Rev. 10

# Pin List

| Mnemonic:                                | Pin No.                                                                                                                  | Pin Type:   | Description:                                                                                                                                                               |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00, 00N<br>01, 01N<br>02, 02N<br>03, 03N | 9, 8<br>72, 73<br>58, 57<br>23, 24                                                                                       | CML OUT     | 622 Mbit/s differential data output.                                                                                                                                       |

| CLK, CLKN                                | 63, 64                                                                                                                   | CML/PECL IN | 622 MHz differential clock input.                                                                                                                                          |

| SYNC, SYNCN                              | 61, 62                                                                                                                   | CML/PECL IN | 78 MHz synchronisation input.                                                                                                                                              |

| 10, 14, 18, 112,<br>116, 120, 124, 128   | 7, 6, 5, 4,<br>99, 98, 97,96                                                                                             | CMOS IN     | 78 Mbit/s MUX input, for O0.                                                                                                                                               |

| 1,  5,  9,  13,<br> 17,  21,  25,  29    | 74, 75, 76, 77<br>82, 83, 84, 85                                                                                         | CMOS IN     | 78 Mbit/s MUX input, for O1.                                                                                                                                               |

| 12, 16, 110, 114,<br>118, 122, 126, 130  | 56, 55, 54, 53<br>49, 48, 47, 46                                                                                         | CMOS IN     | 78 Mbit/s MUX input, for O2.                                                                                                                                               |

| 13, 17, 111, 115,<br>119, 123, 127, 131  | 25, 26, 27, 28<br>32, 33, 34, 35                                                                                         | CMOS IN     | 78 Mbit/s MUX input, for O3.                                                                                                                                               |

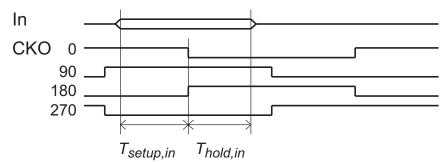

| ско                                      | 67                                                                                                                       | CMOS OUT    | 78 MHz clock output, used to sample I0I31, the sampling point can be adjusted in 4 phases defined by SEL1 and SEL2. 0° refers to sampling on clock going from high to low. |

| SEL1, SEL2                               | 69, 13                                                                                                                   | CMOS IN     | Select the sampling point of I0I31 rel. to CKO.   0° : SEL1=0, SEL2=1   90° : SEL1=0, SEL2=0   180° : SEL1=1, SEL2=1   270° : SEL1=1, SEL2=0                               |

| FCK, FCKN                                | 15, 16                                                                                                                   | PECL/CML IN | 622 MHz differential input to clock divider.                                                                                                                               |

| FCKO, FCKON                              | 17, 18                                                                                                                   | CML OUT     | 622 MHz differential clock output from clock divider.                                                                                                                      |

| SYNCO, SYNCON                            | 19, 20                                                                                                                   | CML OUT     | 78 MHz synchronisation output, timing identical to FCKO for synchronisation.                                                                                               |

| TSTR                                     | 14                                                                                                                       | CMOS IN     | Test reset. Only used in test, connect to $V_{\text{DD}}$ .                                                                                                                |

| VCS                                      | 68                                                                                                                       | Analog IN   | Internal control voltage, leave open.                                                                                                                                      |

| VEE                                      | 1, 2, 11, 21, 30, 31,<br>36, 39, 40, 41, 42,<br>45, 50, 51, 60, 66,<br>70, 79, 80, 81, 86,<br>89, 90, 91, 92, 95,<br>100 | GND         | 0 V                                                                                                                                                                        |

| VDDC                                     | 65                                                                                                                       | PWR         | 5 V, CMOS power                                                                                                                                                            |

| VDD                                      | 3, 10, 12, 22, 29,<br>37, 38, 43, 44, 52,<br>59, 71, 78, 87, 88,<br>93, 94                                               | PWR         | 5 V, CML power                                                                                                                                                             |

| Heat sink                                |                                                                                                                          |             | Connected to VEE                                                                                                                                                           |

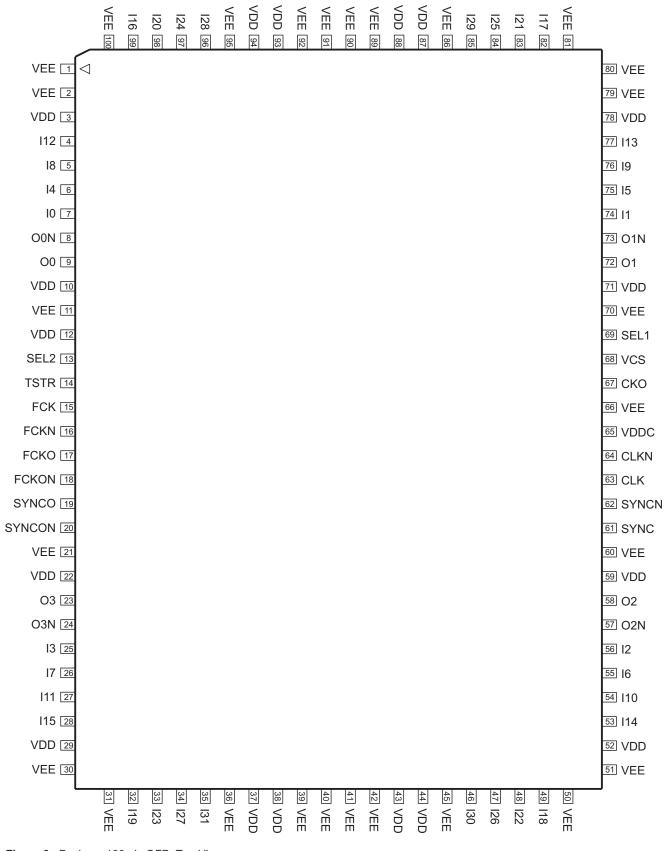

#### Package Pinout

Figure 3. Package 100 pin QFP, Top View

Data Sheet Rev. 10

GD16334

# Maximum Ratings

These are the limits beyond which the component may be damaged. All voltages in table are referred to VEE. All currents are defined positive in to the pin.

| Symbol:            | Characteristic:       | Conditions:      | MIN.: | TYP.: | MAX.:                | UNIT |

|--------------------|-----------------------|------------------|-------|-------|----------------------|------|

| V <sub>DDC</sub>   | Supply Voltage CMOS   | rel. to $V_{EE}$ | 0     |       | 6                    | V    |

| V <sub>DD</sub>    | Supply Voltage        | rel. to $V_{EE}$ | 0     |       | 6                    | V    |

| V <sub>o</sub> max | Output Voltage        |                  | -0.5  |       | V <sub>DD</sub> +0.5 | V    |

| I <sub>o</sub> max | Output Current        | CML              | -15   |       | 0                    | mA   |

| Io max-CMOS        | Output Current        | CMOS             | -30   |       | 30                   | mA   |

| V, max             | Input Voltage         |                  | -0.5  |       | V <sub>DD</sub> +0.5 | V    |

| l, max             | Input Current         |                  | -1.0  |       | 1.0                  | mA   |

| Tj                 | Operating Temperature | Junction         | -55   |       | 125                  | °C   |

| T <sub>s</sub>     | Storage Temperature   |                  | -65   |       | 150                  | °C   |

### **Thermal Characteristics**

| Symbol:          | Characteristic:                         | Conditions:                    | MIN.: | TYP.: | MAX.: | UNIT: |

|------------------|-----------------------------------------|--------------------------------|-------|-------|-------|-------|

| θ <sub>j-c</sub> | Thermal resistance, junction to case    |                                |       | 11.7  |       | °C/W  |

| $\theta_{j-a}$   | Thermal resistance, junction to ambient | Still air, Horizontal mounting |       | 42    |       | °C/W  |

| To               | Operating Temperature                   | Case                           | -5    |       | +85   | °C    |

# Thermal Considerations

A heat-conducting slug is placed at the bottom of the package allowing heat dissipation out of the bottom of the IC package to the PCB. The heat slug can be soldered to a conducting plane (VEE) on the PCB using solder paste, or a thermally conducting foil can be placed under the package. If the thermal foil method is preferred, a 0.25 mm thick foil may be used.

Via holes for heat transfer to the other side of the PCB should be made and a heat sink can be attached on the opposite side of the PCB if required.

# **DC Characteristics**

All voltages in table are referred to VEE. All currents are defined positive in to the pin.  $T_{\text{CASE}}$  = -5 °C to 85 °C.

| Symbol:                     | Characteristic:                     | Conditions:         | MIN.:                   | TYP.: | MAX.:                   | UNIT: |

|-----------------------------|-------------------------------------|---------------------|-------------------------|-------|-------------------------|-------|

| V <sub>DD</sub>             | Supply Voltage                      |                     | 4.75                    | 5.00  | 5.40                    | V     |

| I <sub>DD</sub>             | Supply Current                      | Note 1              |                         | 210   | 250                     | mA    |

| V <sub>CM</sub> CML/PECL    | CML/PECL Input Common Mode Voltage  | Note 2              | V <sub>DD</sub> -2.00   |       | V <sub>DD</sub> -0.2    | V     |

| V <sub>Idiff</sub> CML/PECL | CML/PECL Differential Input Voltage | Note 3              | 100                     | 500   | 1400                    | mV    |

| I <sub>IH,</sub> CML        | CML Input HI Current                | V⊮max               |                         |       | 0.4                     | mA    |

| I <sub>IL</sub> CML         | CML Input LO Current                | V <sub>IL</sub> min | -25                     |       |                         | μΑ    |

| I <sub>o,</sub> CML LOW     | CML Output Current                  | Logic "0"           | 6                       | 8     | 10                      | mA    |

| I <sub>o,</sub> CML HIGH    | CML Output Current                  | Logic "1"           | 0                       |       | 1.5                     | mA    |

| V <sub>IH</sub> смоs        | CMOS Input HI Voltage               |                     | $\frac{V_{DD}}{2}$ +0.5 |       | V <sub>DD</sub>         | V     |

| VILCMOS                     | CMOS Input LO Voltage               |                     | 0                       |       | $\frac{V_{DD}}{2}$ -0.5 | V     |

| I <sub>IH</sub> смоs        | CMOS Input HI Current               | V <sub>⊮</sub> max  |                         |       | 400                     | μΑ    |

| I <sub>IL</sub> CMOS        | CMOS Input LO Current               | V <sub>IL</sub> min | -300                    |       |                         | μΑ    |

| V <sub>оң</sub> смоs        | CMOS Output HI Voltage              |                     | 0.8 x V <sub>DD</sub>   |       | V <sub>DD</sub>         | V     |

| V <sub>oL</sub> CMOS        | CMOS Output LO Voltage              |                     | 0                       |       | 0.3 x V <sub>DD</sub>   | V     |

| I <sub>он,</sub> смоs       | CMOS Output HI Current              | СКО                 |                         |       | 16                      | mA    |

| I <sub>оц</sub> смоs        | CMOS Output LO Current              | СКО                 | -16                     |       |                         | mA    |

Note 1: Supply currents are estimates, based on post-layout simulations.

**Note 2:**  $V_{CM} = \frac{V_P + V_N}{2}$ Note 3:  $V_{Idiff} = |V_P - V_N|$

V<sub>N</sub> -

V<sub>P</sub> —

# **AC Characteristics**

| Symbol:     | Characteristic:             | Conditions: | MIN.: | TYP.: | MAX.: | UNIT: |

|-------------|-----------------------------|-------------|-------|-------|-------|-------|

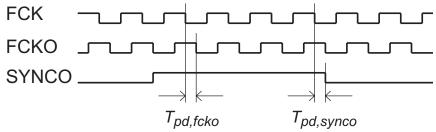

| Tpd,fcko    | Delay from FCK to FCKO      |             | 0.6   | 0.9   | 1.3   | ns    |

| Tpd,synco   | Delay from FCK to SYNCO     |             | 0.9   | 1.3   | 1.9   | ns    |

| Tsetup,in   | Ix set-up time before CKO   |             |       | 1.3   |       | ns    |

| Thold,in    | Ix hold time after CKO      |             |       | -0.3  |       | ns    |

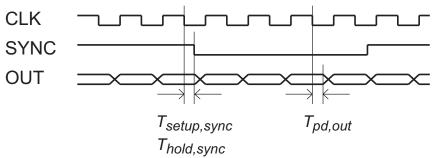

| Tsetup,sync | Sync set-up time before CLK |             |       | 0.1   |       | ns    |

| Thold,sync  | Sync hold time after CLK    |             |       | 0.3   |       | ns    |

| Tpd,cko     | Delay from CLK to CKO       |             | 0.9   | 1.3   | 1.9   | ns    |

| Tpd,out     | Delay from CLK to Ox        |             | 0.7   | 1.3   | 1.9   | ns    |

**Note:** All timing data are estimates, based on post-layout simulations.

Figure 4. Fast Clock Divider.

Figure 6. High Frequency.

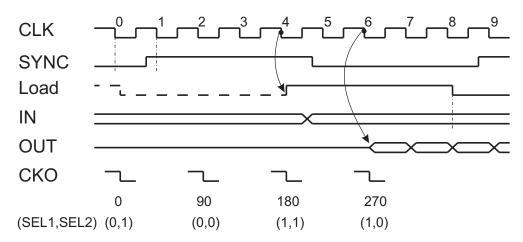

**Note:** When SYNC is sampled high, after a low sample, the internal clock divider is reset, giving a low CKO and data output two CLK samples after SYNC is sampled low.

Figure 7. Relation Between Data and Clock.

The internal load signal is generated relative to the rising edge of SYNC. The synchronisation sequence is initiated by the sampling of SYNC low followed by high. A rising edge on the internal load signal (load) is generated four CLK cycles after SYNC is sampled high.

The external load clock CKO can be adjusted in four phases relative to the internal load signal, selected by SEL1 and SEL2, as shown in the figure.

The figure also shows the number of bits stored in the device. The GD16334 starts transmitting data on the  $6^{th}$  CLK cycle after SYNC is sampled high. The low frequency input data is sampled on the  $8^{th}$  CLK cycle. This will give a total of 15 bits just before sampling data, and a total of 22 bits just after sampling – for each of the four MUX'es in the GD16334.

#### **Sequencing of Output Data**

The GD16334 MUX contains four identical 8:1 MUX'es. The data bits of the first MUX are shifted out with the data of input I0 (pin 7) coming out first, then I4, I8...I28. The second MUX shifts out I1 (pin 74) first, followed by I5, I9....I29. The last two MUX blocks work in the same manner.

### Package Outline

Figure 8. Package 100 pin QFP

#### **Device Marking**

Figure 9. Device Marking - Top View

### **Ordering Information**

To order, please specify as shown below:

| Product Name:   | Package Type: | Case Temperature Range: | Option: |

|-----------------|---------------|-------------------------|---------|

| GD16334 - 100BA | 100 pin QFP   | -5 °C +85 °C            |         |

Mileparken 22, DK-2740 Skovlunde Denmark Telephone : +45 4492 6100 Telefax : +45 4492 5900

| releiax  | 1 +45 4492 5900      |

|----------|----------------------|

| E-mail:  | : sales@giga.dk      |

| Web site | : http://www.giga.dk |

Please check our Internet web site for latest version of this data sheet.

The information herein is assumed to be reliable. GIGA assumes no responsibility for the use of this information, and all such information shall be at the users own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. GIGA does not authorise or warrant any GIGA Product for use in life support devices and/or systems. Distributor:

GD16334, Data Sheet Rev. 10 - Date: 8 February 1999

Copyright © 1999 GIGA A/S All rights reserved