## S19252 Data Sheet STS-192 SONET/SDH/FEC/GbE/FC 16-bit Transceiver with EDC

#### June 15, 2010

## **General Features**

micro

2011

- Operational from 9.9 Gbps to 11.32 Gbps

- Built-In Self Test (BIST) with Error Counter

- On-chip High-Frequency PLLs for Clock Recovery and Clock Generation

- 16-bit LVDS Parallel Data Path

- TX and RX Lock Detect Indicators

- Reference Loop Timing Modes

- Line and Diagnostic Loopback Mode for Faulty Node Identification

- -40°C to 85°C Industrial Temperature Range

- · Supports MDIO, I2C and SPI serial interface

- Complies with applicable OIF SFI-4 Phase 1, Telcordia/ ITU-T, 300-pin MSA, IEEE 802.3ae and XFP MSA Standards

- 2000 V ESD rating, 1500 V on high speed inputs

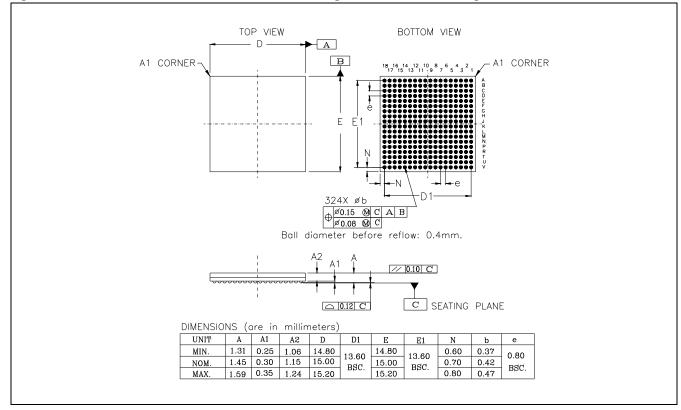

- 15 x 15 mm, 0.8 mm pitch package with RoHS compliant lead free option.

- 1.1 W typical

- JTAG support

## **Transmitter Features**

- Reference Clock Frequency Selection: Divide by 16, 64 or 66 of the TX rate; for example (644.53 MHz, 161.13 MHz or 156.25 MHz) for 10GE TX rate

- Internal, Self-Initializing FIFO to Decouple Transmit Clocks

- Programmable TSD Output Differential Swing

- 10 G Transmitter Serial Clock Output

- Duo Binary Encoding

- Transmitter De-Emphasis

## **Receiver Features**

- LOS/RSSI

- ISI compensation. Tolerates additional 350 ps/nm of chromatic dispersion with an OSNR penalty of 1.0dB over a traditional demux

- Tolerates up to 34" of Standard FR-4 Material

- Adaptive Post-Amplifier Offset Adjust

- Phase Adjust of -0.11 to +0.085 UI

- Reference Clock Frequency Selection: Divide by 16, 64 or 66 of the RX rate; for example (644.53 MHz, 161.13 MHz or 156.25 MHz) for 10GE RX rate

- Capability to Interface with Single-Ended or Differential TIAs (Center Tap Option)

- Input Sensitivity of 10 mV p-p (one wire or two wire) at 10<sup>-12</sup> BER

## Applications

- SONET/SDH and 10GbE-Based Transmission Systems & Modules

- Section Repeaters

- Add Drop Multiplexers (ADM)

- Broad-Band Cross-Connects

- Fiber Optic Test Equipment

## **General Description**

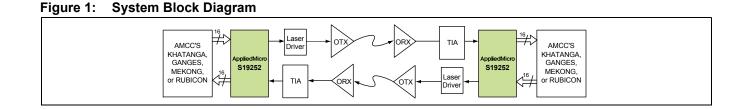

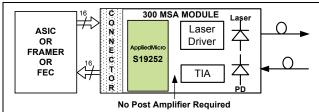

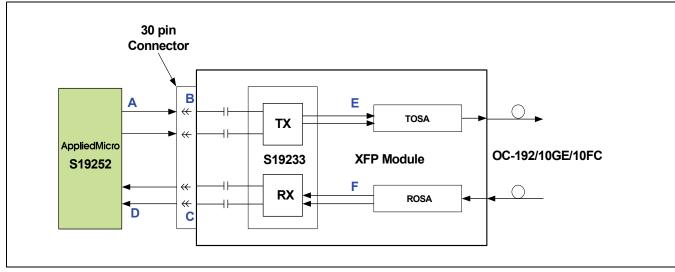

The S19252 MUX/DeMux chip is a fully integrated serialization/de-serialization SONET STS-192/ 10 GB Ethernet/Fiber Channel transceiver with Electronic Dispersion Compensation (EDC). This device can be used to compensate channel impairments caused by Single Mode Fiber (SMF) and copper medium. The chip performs all necessary parallel-to-serial and serial-to-parallel functions in conformance with SONET/SDH, 10 Gigabit Ethernet (10 GbE) and 10 Gigabit Fibre Channel (10 G FC) transmission standards. Figure 1, shows a typical network application. The other application block diagrams are shown in Figures 2, 3 and 4.

On-chip clock synthesis PLL components are contained in the S19252 chip, allowing the use of a slower external transmit clock reference. The chip can be used with 155.52 MHz or 622.08 MHz (or equivalent FEC/10 GbE/10 G FC rates) reference clocks, in support of existing system clocking schemes. The low-jitter LVDS interface guarantees compliance with the bit-error rate requirements of the Telcordia and ITU-T standards.

### NOTICE: THIS IS A "RELEASED" SPECIFICATION

This document is a **RELEASED** specification for a device under development by AppliedMicro:

- •

- Specifications in this document are not guaranteed to be the latest and are subject to change. This data sheet may be superseded by a future revision. Always confirm with AppliedMicro that you are using the latest version. •

- Please consult and register for documentation updates from AppliedMicro's external website via the AppliedMicro's MyProduct subscription updates page: https://www.AppliedMicro.com/MyAMCC/jsp/secure/alertSubscriptions/my\_product\_list.jsp.

| Data Sheet Type | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONCEPT         | Concept Specifications are made available for products ideas that are being marketed to obtain customer feedback.                                                                                                                                                                                                                                                                                                                                                                 |

| ADVANCE         | Advance Specifications are made available for products that are in the engineering development cycle. General samples are not yet available for these products and the specifications, including pin lists and functional descriptions, may change at any time WITHOUT NOTICE.                                                                                                                                                                                                    |

| PRELIMINARY     | Preliminary Specifications are made available for products that have been released for general sampling by AppliedMicro (known as Sample Release (SR)). The SR milestone indicates that device samples and evaluation kits may made available upon request. Preliminary device characterization and evaluation has also been completed by AppliedMicro. Known device errata's will be published and dispositioned upon SR. Device specifications may still change WITHOUT NOTICE. |

| RELEASED        | Released Specifications are made available for products that have passed AppliedMicro's Pro-<br>duction and Qualification Testing. Although Released Specifications are expected to never<br>change, occasional clean-up changes may be made throughout the remaining product life cycle.                                                                                                                                                                                         |

## **Table of Contents**

| GENERAL FEATURES                                                    | 1    |

|---------------------------------------------------------------------|------|

| Transmitter Features                                                | 1    |

| Receiver Features                                                   | 1    |

| APPLICATIONS                                                        | 1    |

| GENERAL DESCRIPTION                                                 | 1    |

| DATA SHEET TYPE                                                     | 2    |

| TABLE OF CONTENTS                                                   | 3    |

| LIST OF FIGURES                                                     | 6    |

| LIST OF TABLES                                                      | 7    |

| S19252 OVERVIEW                                                     | 8    |

| TRANSMIT INPUT PIN DESCRIPTION                                      |      |

| Parallel Input Data (PINP/N[15:0]) – External Pin                   |      |

| Parallel Input Clock (PICLKP/N) – External Pin                      |      |

| LVDS Input AC Enable (LVDS_INPUT_AC_EN) – Register                  |      |

| TX Ref. Select (TXREFA_NOTB) – Register                             |      |

| SONET Rate Select (SONET_RATESEL) – Register                        |      |

| GbE Rate Select (GBE_RATESEL) – Register                            |      |

| TX Ref. Rate Select (TXREFSEL) – Register                           | . 10 |

| CSU Ref. Clock (REFCLKAP/N) – External Pin                          | . 11 |

| External Voltage Controlled Oscillator (XVCO) – Register            | . 11 |

| Transmitter Reset (TX_RSTB) – Register                              | . 11 |

| External Voltage Controlled Oscillator 155 MHz (XVCO155) – Register |      |

| Kill Transmitter 155MCK Clock Output (KILLTXMCK) – Register         | . 11 |

| Kill Transmitter PCLK Output Clock (KILLPCLK) – Register            | . 11 |

| Kill Transmit Serial Data Output (KILLTXDATB) – Register            |      |

| Clock Synthesizer Input (CSU_INP/N) – External Pin                  |      |

| TX Loop Filter (TXCAP1, TXCAP2) – External Pin                      |      |

| Phase Initialization (PHINIT) – Register                            |      |

| Automatic FIFO Initialization (AUTO_FIFO_INIT) – Register           |      |

| Transmit Built-In Self Test Enable (TX_BIST_EN) – Register          |      |

| Transmit Built-In Self Test Clear (TX_BIST_CLR) – Register          |      |

| Parallel Input Data Bus Swap (TX_DATA_SWAP) – Register              |      |

| TRANSMIT OUTPUT PIN DESCRIPTION                                     |      |

| Transmit Serial Data (TSDP/N) – External Pin                        |      |

| Parallel Clock (PCLKP/N) – External Pin                             |      |

| 155.52 MHz Clock Output (TX_155MCKP/N) – External Pin               |      |

| Transmit Lock Detect (TX_LOCKDET) – Register and External Pin       |      |

| Phase Error (PHERR) – Register                                      |      |

| Phase Detector Output (PD_UP, PD_DWN) – External Pin                |      |

| Transmit Built-In Self Test Error (TX_BIST_ERR) – Register          |      |

| RECEIVE INPUT PIN DESCRIPTION                                       |      |

| Serial Data In (SERDATIP/N) – External Pin                          | . 15 |

| SERDATIP/N Internal Termination (CENTER_TAP) – External Pin                                                   |  |

|---------------------------------------------------------------------------------------------------------------|--|

| Receive Loop Filter (RXCAP1, RXCAP2) – External Pin                                                           |  |

| Receiver Reset (RX_RSTB) – Register                                                                           |  |

| Lock-to-Reference (LCKREFN) – Register                                                                        |  |

| LOS/Signal Detect (LOS_SD) – External Pin                                                                     |  |

| Signal Detect Polarity (SD_POL) – Register                                                                    |  |

| RX Ref. Select (RXREFA_NOTB) – Register                                                                       |  |

| Receive Reference Rate Select (RXREFSEL) – Register                                                           |  |

| CRU Reference Clock (REFCLKAP/N) – External Pin                                                               |  |

| Kill Parallel Output Clock (KILLPOCLK) – Register                                                             |  |

| Kill Parallel Output Data (KILLPOUTB) – Register                                                              |  |

| Kill Parallel Output MCK Clock (KILLRXMCK) – Register                                                         |  |

| Receive Built-In Self Test Enable (RX_BIST_EN) – Register                                                     |  |

| Receive Built-In Self Test Clear (RX_BIST_CLR) – Register                                                     |  |

| LOS Threshold Assert (LOS_VTH_AST [7:0]) – Register                                                           |  |

| LOS Threshold De-Assert (LOS_VTH_DST [7:0]) – Register                                                        |  |

| Phase Adjust (PHASE_ADJ[2:0]) – Register                                                                      |  |

| Post Amplifier Offset Adjust (PAOFFADJ[9:0]) and Adaptive Post Amplifier Offset Adjust En<br>ADJ) – Registers |  |

| Parallel Output Data Bus Swap (RX_DATA_SWAP) – Register                                                       |  |

| RECEIVE OUTPUT PIN DESCRIPTION                                                                                |  |

| Parallel Output Clock (POCLKP/N) – External Pin                                                               |  |

| Parallel Output Data (POUTP/N[15:0]) –<br>External Pin                                                        |  |

| Receive Lock Detect (RX_LOCKDET) – Register and External Pin                                                  |  |

| Recovered 622.08/155.52 MHz Clock (RX_MCKP/N) – External Pin                                                  |  |

| Receive Built-In Self Test Error (RX_BIST_ERR) – Register                                                     |  |

| COMMON INPUT PIN DESCRIPTION                                                                                  |  |

| Reset (RSTB) – External Pin                                                                                   |  |

| Diagnostic Loopback Enable (DLEB) – Register                                                                  |  |

| Line Loopback Enable (LLEB) – Register                                                                        |  |

| Reference Loop Timing (RLPTIME) – Register                                                                    |  |

| User Defined BIST Pattern (BIST_PTRN[15:0]) – Register                                                        |  |

| Pattern Select (PRBS_SELECT[1:0]) – Register                                                                  |  |

| Bit Error Rate Range Select (BER_SELECT[2:0]) – Register                                                      |  |

| Bit Error Rate Reset (BER_RSTB) – Register                                                                    |  |

| Clock Stop Value (CLKSTOP_VAL) – Register                                                                     |  |

| COMMON OUTPUT PIN DESCRIPTION                                                                                 |  |

| Transmit and Receive Alarm (TX_RX_ALARM) – Register and External Pin                                          |  |

| Built In Self Test Active (BIST_ACTIVE) – Register                                                            |  |

| Bit Error Rate Count (BER_COUNT[11:0]) – Register                                                             |  |

| Bit Error Rate Overflow (BER_OVERFLOW) – Register                                                             |  |

| Terminal Count Monitor (TERM_COUNT) – Register                                                                |  |

| TRANSMITTER FUNCTIONAL DESCRIPTION                                                                            |  |

| MUX Operation                                                                                                 |  |

| Clock Synthesizer                                                   | 25 |

|---------------------------------------------------------------------|----|

| Loop Timing                                                         | 25 |

| Line Loopback                                                       | 25 |

| Timing Generator                                                    | 25 |

| FIFO                                                                | 26 |

| FIFO Initialization                                                 | 26 |

| Parallel-to-Serial Converter                                        | 26 |

| Duo-Binary Encoding                                                 | 26 |

| Transmit Built-In Self Test Mode                                    | 26 |

| RECEIVER FUNCTIONAL DESCRIPTION                                     | 27 |

| Post-Amp                                                            | 27 |

| Clock Recovery                                                      | 27 |

| Receive Lock Detect                                                 | 28 |

| Serial-to-Parallel Converter                                        | 28 |

| Diagnostic Loopback                                                 | 28 |

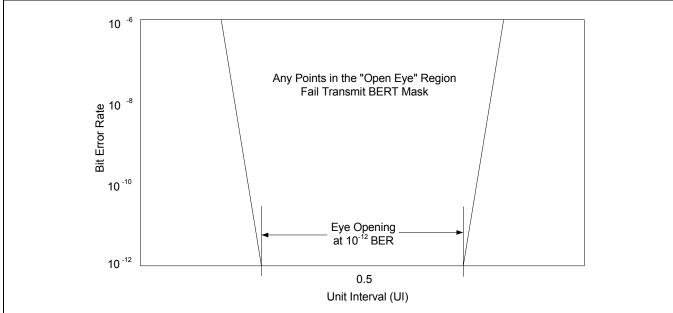

| Receive Built-In Self Test Mode                                     | 29 |

| INPUT/OUTPUT CONTROLS                                               | 30 |

| Mode Control                                                        | 30 |

| Serial Interface Mode                                               |    |

| MDIO Bus and Address Register                                       | 32 |

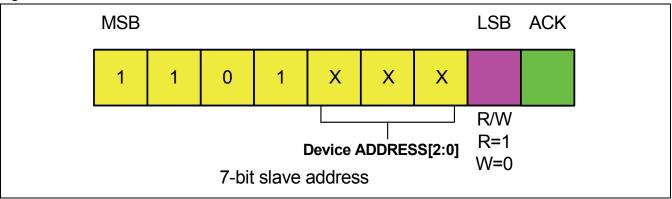

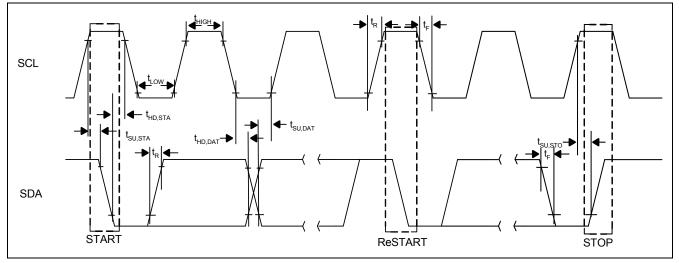

| I2C BUS® AND ADDRESS REGISTER                                       | 34 |

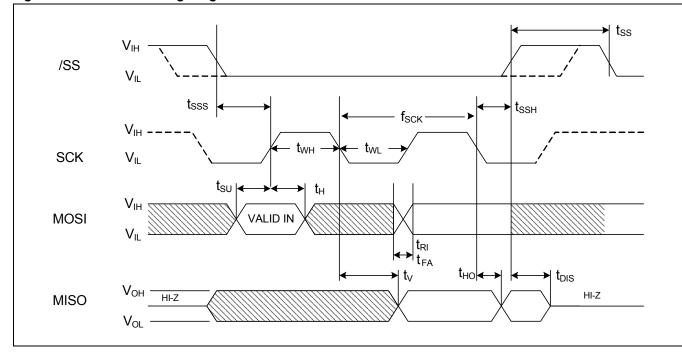

| Serial Peripheral Interface (SPI)                                   | 35 |

| SPI Pin Signals                                                     | 35 |

| SPI Protocol                                                        | 35 |

| JTAG Interface                                                      | 35 |

| SONET AND ETHERNET JITTER CRITERIA                                  |    |

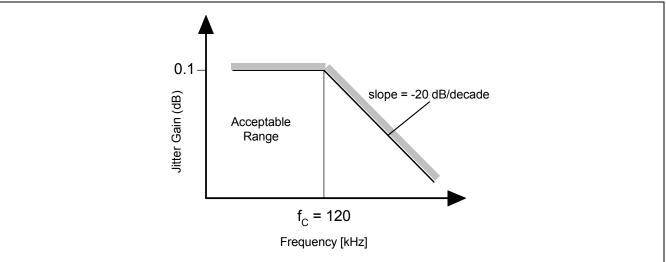

| SONET Jitter Transfer                                               | 36 |

| SONET Jitter Tolerance                                              | 36 |

| SONET Jitter Generation                                             | 37 |

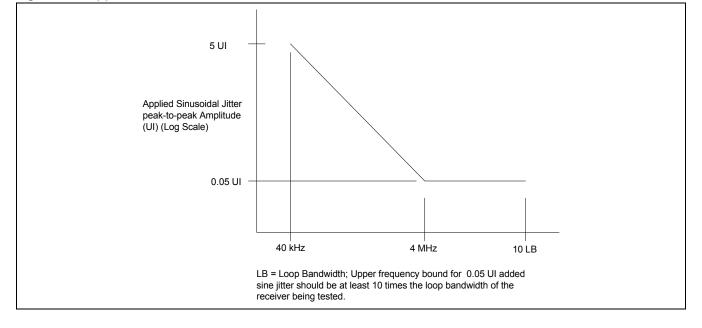

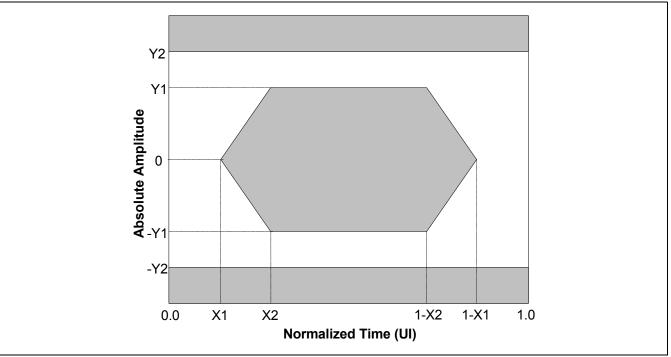

| 10 Gigabit Ethernet Jitter Tolerance                                | 37 |

| Sinusoidal Jitter                                                   | 38 |

| Test Pattern                                                        | 38 |

| REGISTER MAP                                                        | 41 |

| PIN ASSIGNMENTS AND DESCRIPTIONS                                    | 45 |

| S19252 – 324 PBGA PINOUT - 0.8 MM PITCH (BOTTOM VIEW) DATA_SWAP = 0 | 56 |

| S19252 – 324 PBGA 0.8 MM PITCH PACKAGE MECHANICAL DRAWING           | 57 |

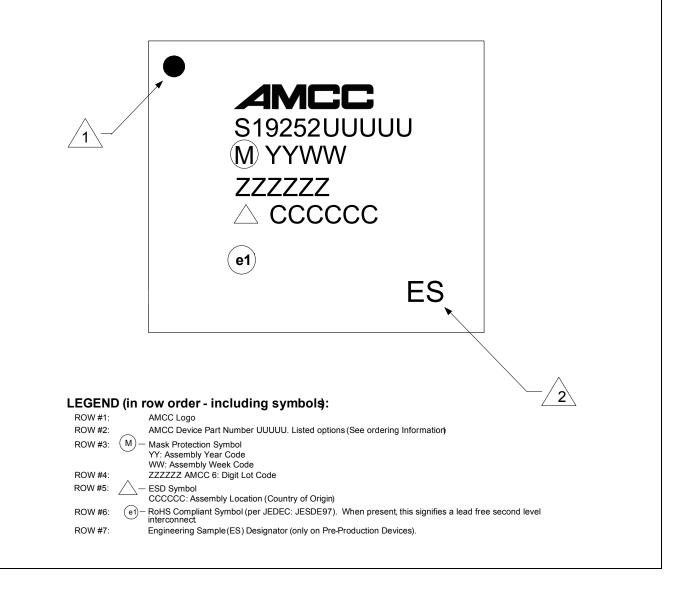

| S19252 – 324 PBGA PACKAGE MARKING DRAWING                           | 58 |

| PERFORMANCE SPECIFICATIONS                                          | 59 |

| ELECTRICAL SPECIFICATIONS                                           | 69 |

| EXTERNAL LOOP FILTER COMPONENTS                                     | 80 |

| RECOMMENDED TERMINATIONS                                            |    |

| DOCUMENT REVISION HISTORY                                           |    |

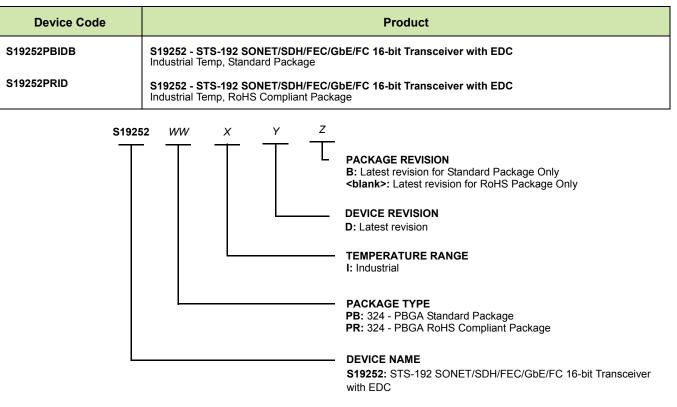

| ORDERING INFORMATION                                                |    |

|                                                                     |    |

Table of Contents

## List of Figures

| Figure 1: System Block Diagram                                                                   | . 1 |

|--------------------------------------------------------------------------------------------------|-----|

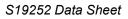

| Figure 2: Mid-Plane Application Block Diagram                                                    | . 8 |

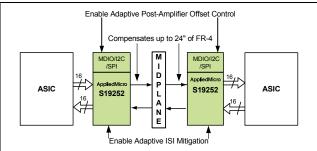

| Figure 3: XFP Application Block Diagram                                                          | . 8 |

| Figure 4: 300 MSA Application Block Diagram                                                      | . 8 |

| Figure 5: Transceiver Functional Block Diagram                                                   | . 9 |

| Figure 6: Two Wire Slave Address                                                                 | 34  |

| Figure 7: SONET STS-192 Jitter Transfer Characteristics                                          | 36  |

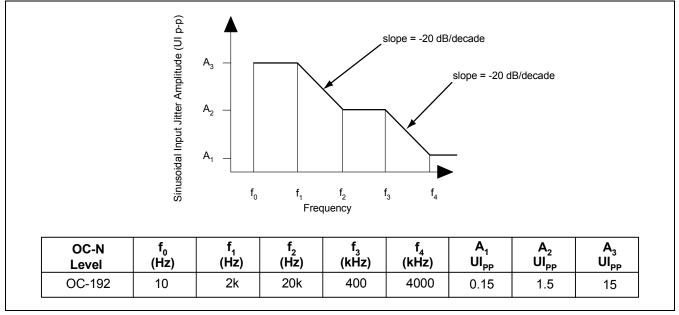

| Figure 8: SONET STS-192 Jitter Tolerance Mask                                                    | 36  |

| Figure 9: Input Jitter Mask for Receiver Test                                                    |     |

| Figure 10: Applied Sinusoidal Jitter - 10 GbE                                                    | 39  |

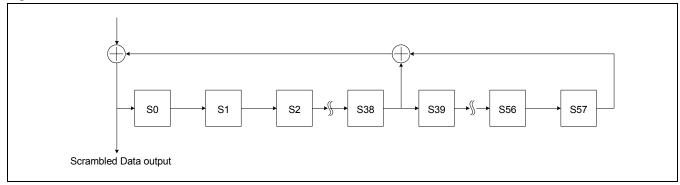

| Figure 11: Scrambler and Descrambler                                                             | 39  |

| Figure 12: S19252 – 324 PBGA Pinout - 0.8 mm Pitch (Bottom View) Data_swap = 0                   | 56  |

| Figure 13: S19252 – 324 PBGA 0.8 mm Pitch Package Mechanical Drawing                             | 57  |

| Figure 14: S19252 – 324 PBGA Package Marking Drawing (Top View)                                  |     |

| Figure 15: S19252 with XFP System Performance Points.                                            | 65  |

| Figure 16: XFI Transmitter Differential Output Compliance Mask                                   | 66  |

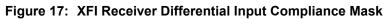

| Figure 17: XFI Receiver Differential Input Compliance Mask                                       |     |

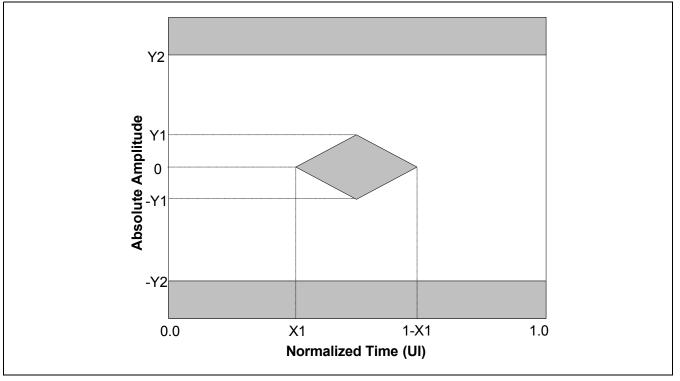

| Figure 18: XFI Receiver Input Telecom Sinusoidal Jitter Tolerance                                | 67  |

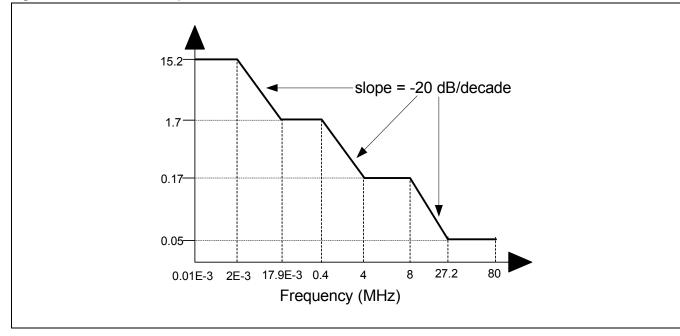

| Figure 19: XFI Receiver Input Datacom Sinusoidal Jitter Tolerance                                | 67  |

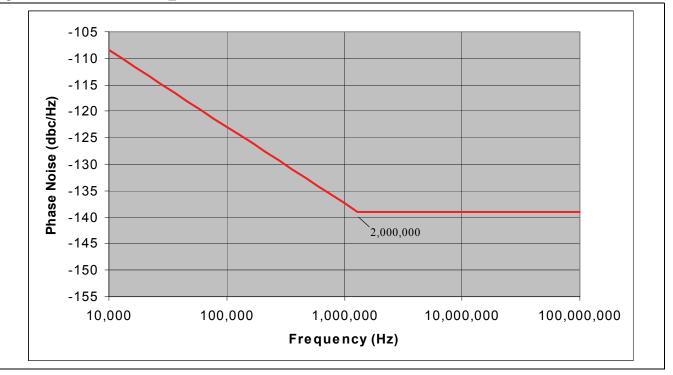

| Figure 20: 622.08 MHz CSU_REFCLK Phase Noise                                                     | 68  |

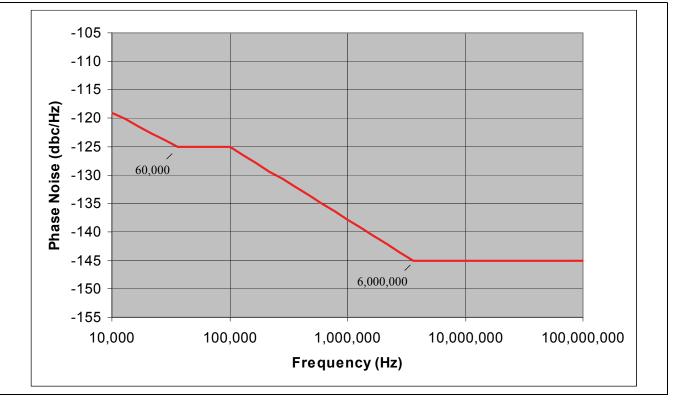

| Figure 21: 155.52 MHz CSU_REFCLK Phase Noise                                                     | 68  |

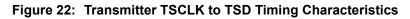

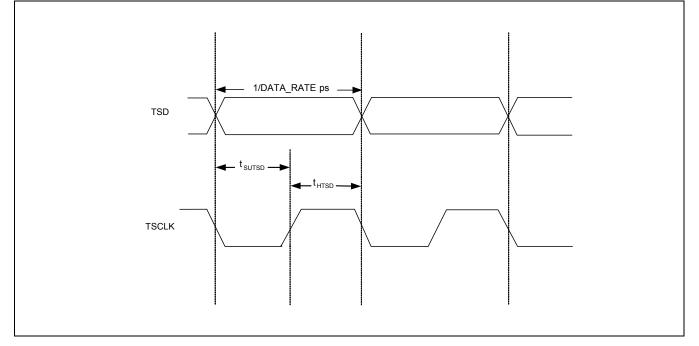

| Figure 22: Transmitter TSCLK to TSD Timing Characteristics.                                      | 75  |

| Figure 23: Transmitter Timing Characteristics                                                    | 75  |

| Figure 24: Receiver Timing Characteristics                                                       |     |

| Figure 25: I2C BUS <sup>®</sup> Timing Diagram                                                   | 78  |

| Figure 26: SPI BUS Timing Diagram                                                                |     |

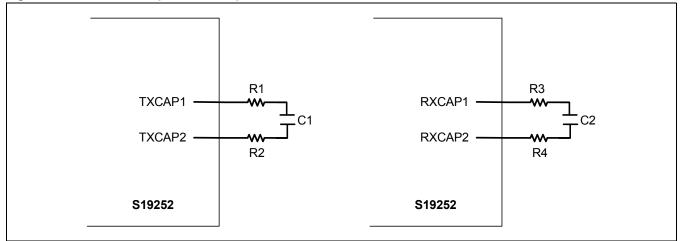

| Figure 27: External Loop Filter Components                                                       |     |

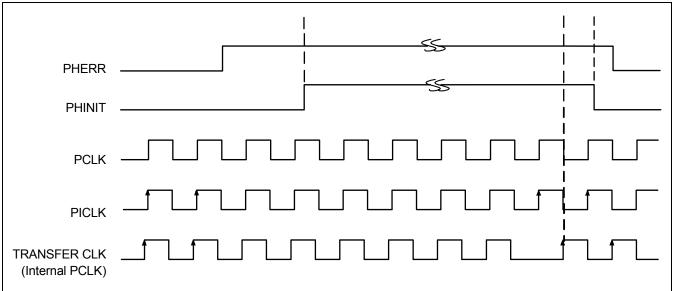

| Figure 28: FIFO Initialization                                                                   |     |

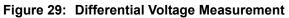

| Figure 29: Differential Voltage Measurement.                                                     |     |

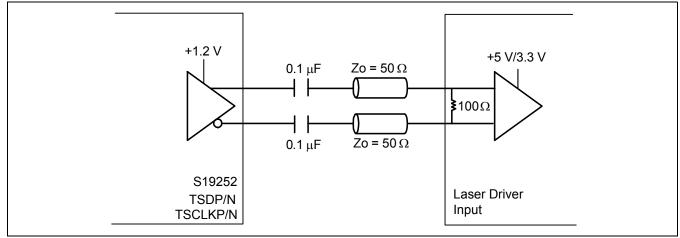

| Figure 30: S19252 Differential CML Output to +5 V/+3.3 V PECL Input AC Coupled Termination       |     |

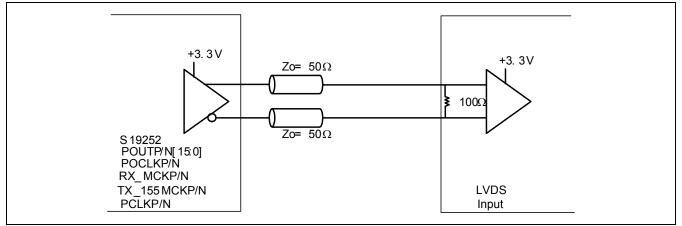

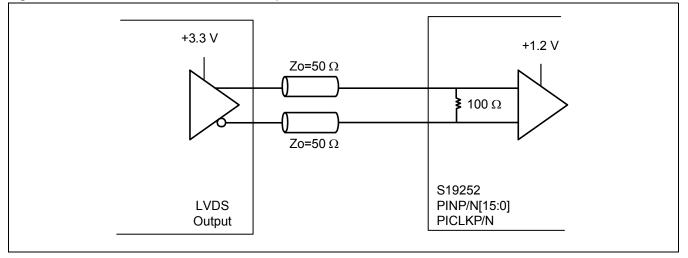

| Figure 31: S19252 LVDS Driver to LVDS Input Termination                                          |     |

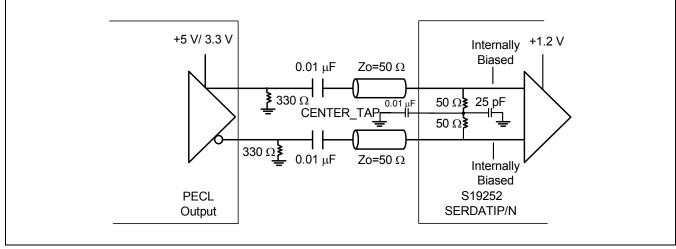

| Figure 32: +5 V Differential PECL Driver to S19252 Differential CML Input AC Coupled Termination | 84  |

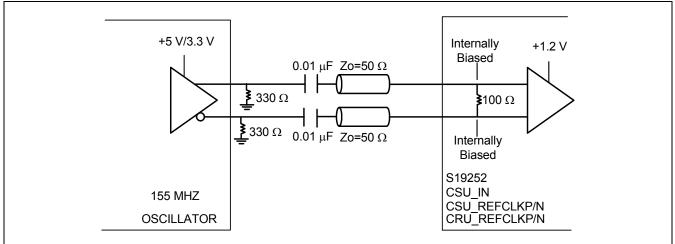

| Figure 33: +5 V/+3.3 V Differential PECL Driver to S19252 CML Reference Clock Input              |     |

| AC Coupled Termination                                                                           |     |

| Figure 34: LVDS Driver to S19252 LVDS Inputs                                                     | 85  |

## **List of Tables**

| Table 1: Transmit Reference Source Select.    10                                       |

|----------------------------------------------------------------------------------------|

| Table 2: Transmit Reference Rate Select    10                                          |

| Table 3: Reference Frequency (CSU REFCLK) for the Clock Synthesis Unit.       12       |

| Table 4: Reference Frequency with External VCO Selected    13                          |

| Table 5: Receive Reference Source Select    16                                         |

| Table 6: Receive Reference Rate Select    16                                           |

| Table 7: Reference Frequency (CRU REFCLK) for the Clock and Data Recovery Unit         |

| Table 9: Post-Amplifier Offset Adjust    19                                            |

| Table 8: Phase Adjust Control    19                                                    |

| Table 10: Adaptive Post-Amplifier Offset Adjust.    19                                 |

| Table 11: Line Loopback Enable Mode    21                                              |

| Table 12: Reference and Loopback Enable    22                                          |

| Table 13: PRBS Pattern Select    23                                                    |

| Table 14: Bit Error Rate Range Select    23                                            |

| Table 15: Mode Control         30                                                      |

| Table 16: Serial Interface Mode    31                                                  |

| Table 17: Serial Port Frame Format.    33                                              |

| Table 18: Applied Sinusoidal Jitter    39                                              |

| Table 19: Pattern Segments.    40                                                      |

| Table 20: Test Patterns    40                                                          |

| Table 21: Register Map Summary    41                                                   |

| Table 22: Input Pin Assignments and Descriptions    45                                 |

| Table 23: Output Pin Assignments and Descriptions    51                                |

| Table 24: S19252 JTAG Pin Assignments and Descriptions    53                           |

| Table 25: S19252 MPIO Pin Assignments and Descriptions    54                           |

| Table 26: Power and Ground Pin Assignments and Descriptions    55                      |

| Table 27: Thermal Management (0.8 mm Pitch Package).    57                             |

| Table 28: Performance Specifications    59                                             |

| Table 29: Absolute Maximum and Minimum Ratings    69                                   |

| Table 30: Recommended Operating Conditions    70                                       |

| Table 31: LVCMOS Input/Output Characteristics    71                                    |

| Table 32: High-Speed CML Input/Output Characteristics (TSD, TSCLK, SERDATI).       71  |

| Table 33: Phase Detector CML Output Characteristics (PD_UP/DWN).    72                 |

| Table 34: REFCLK CML Input Characteristics (REFCLKA, REFCLKB, CSU_IN)                  |

| Table 35: LVDS Input/Output Characteristics    73                                      |

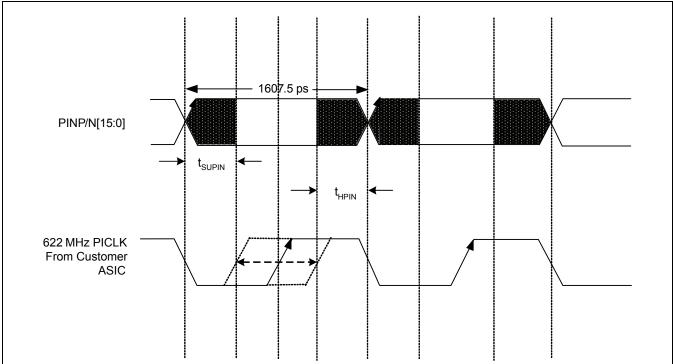

| Table 36: Transmitter Timing Characteristics    74                                     |

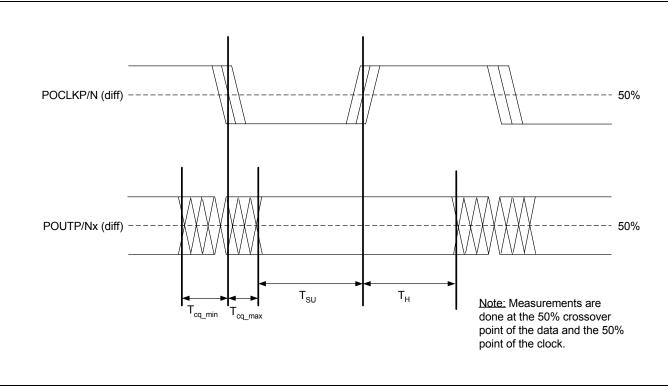

| Table 37: Receiver Timing Characteristics.    76                                       |

| Table 38: MDIO Timing Characteristics    77                                            |

| Table 39: I2C BUS <sup>®</sup> LVCMOS Input/Output & Timing Characteristics.       78  |

| Table 40: SPI BUS Timing Characteristics    79                                         |

| Table 41: Transmit and Receive External Loop Filter Components, See Figure 27       80 |

## S19252 Overview

The S19252 transceiver incorporates SONET/SDH/10 GbE/10 G Fibre Channel serialization and deserialization functions. This chip can be used to implement the front end of SONET/10 GbE/10 G Fibre Channel equipment, which consists primarily of the serial transmit interface and the serial receive interface. The chip includes parallel-to-serial, and serial-to-parallel conversion and system timing.

The sequence of operations is as follows:

#### Transmitter Operations:

- 1. 16-bit parallel input

- 2. Parallel-to-serial conversion

- 3. Serial data output

- 4. At rate transmitter clock output

#### **Receiver Operations:**

- 1. Serial input to limiting post-amp

- 2. Inter Symbol Interference (ISI) compensation

- 3. Threshold adjustment

- 4. Clock and Data recovery

- 5. Phase adjustment for improved BER

- 6. Serial-to-parallel conversion

- 7. 16-bit parallel data and clock output

#### Figure 2: Mid-Plane Application Block Diagram

#### Figure 3: XFP Application Block Diagram

#### Figure 4: 300 MSA Application Block Diagram

#### Suggested Interface Devices

| AppliedMicro | GANGES II<br>(S19202CBI20) | STS-192 POS/ATM SONET/SDH<br>Mapper                                    |

|--------------|----------------------------|------------------------------------------------------------------------|

| AppliedMicro | RUBICON (S19227)           | OC-192/48/12/3 DW/FEC/PM<br>and ASYNC Mapper Device with<br>Strong FEC |

| AppliedMicro | MEKONG (S19204)            | STS-192 Pointer Processor                                              |

| AppliedMicro | KHATANGA<br>(S19205)       | STS-192c SONET/SDH Framer/<br>Mapper with Integrated MAC               |

#### Standards Compliance List

| Standard                                            | Revision  | Date               |

|-----------------------------------------------------|-----------|--------------------|

| 300 Pin MSA for<br>10G Transponders                 | Edition 4 | August 14, 2002    |

| GR-253-CORE SONET Jitter<br>Specifications          | Issue 4.0 | December 2005      |

| IEEE Draft P802.3ae/                                | -         | August 30, 2002    |

| XFP MSA (XFI Electrical- High<br>Speed outputs)     | Rev 4.0   | April 13, 2004     |

| SFF-8431 <sup>1</sup> (SFP+ Host Serdes)            | Rev 1.3   | February 16, 2007  |

| Fibre Channel Physical Interfaces (FC-PI-2)         | Rev 4.1   | March 24, 2004     |

| OIF SFI4 Phase 1 <sup>2</sup><br>Parallel Interface | Rev 1.0   | September 26, 2000 |

1. See SFP+ Jitter Performance, Table 28 for transmitter

conditional compliance.

See LVDS Characteristics, Table 35 for Input Level conditional compliance.

Standard Compliance only relates to applicable sections pertaining to this product type.

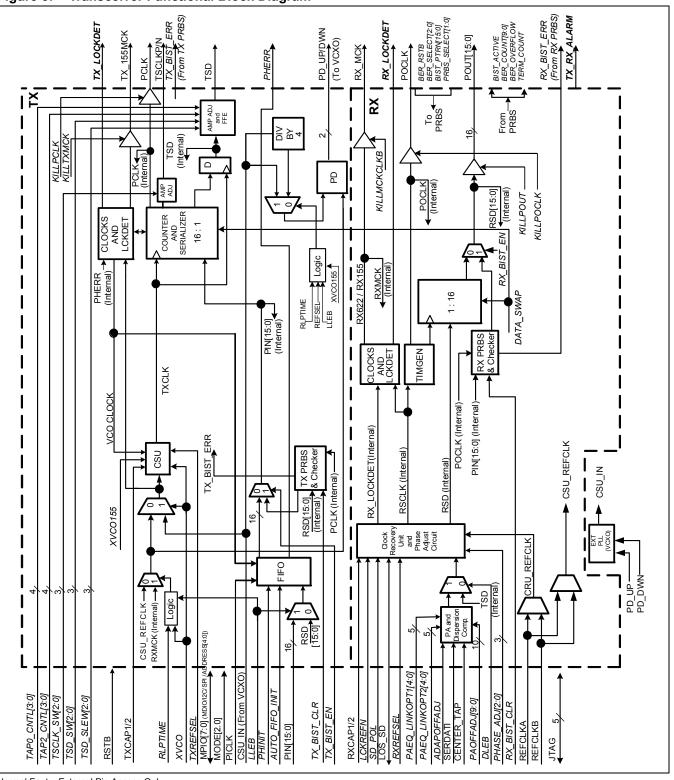

Figure 5: Transceiver Functional Block Diagram

Normal Font – External Pin Access Only

Italics Font – Serial Bus Register Access Only

Italics and Bold Font – External Pin And Serial Bus Register Access

Revision 5.03

#### AppliedMicro - Confidential and Proprietary

## **Transmit Input Pin Description**

## Parallel Input Data (PINP/N[15:0]) – External Pin

PINP/N[15:0] is the LVDS parallel data input bus which is multiplexed 16:1 and transmitted serially at STS-192/ 10 GbE/10G FC rates. This data is aligned with the Parallel Input Clock (PICLKP/N). Bit 15 is the Most Significant Bit (MSB). This bus is typically connected to a framer, mapper or digital wrapper (e.g. GANGES, or RUBICON). These inputs are internally terminated 100  $\Omega$  line-to-line and are either internally biased for AC coupling or DC level shifted for DC coupling. See LVDS\_INPUT\_AC\_EN control description.

## Parallel Input Clock (PICLKP/N) – External Pin

PICLKP/N is the LVDS 622.08 MHz (or equivalent FEC/10 GbE/10G FC Rate) input clock to which the Parallel Input Data (PINP/N[15:0]) is aligned. PICLKP/ N is a delayed version of the PCLK. This clock is used to clock the data into the S19252 FIFO. These inputs are internally terminated 100  $\Omega$  line-to-line and are either internally biased for AC coupling or DC level shifted for DC coupling. See LVDS\_INPUT\_AC\_EN control description.

#### LVDS Input AC Enable (LVDS\_INPUT\_AC\_EN) – Register

The LVDS\_INPUT\_AC\_EN is an active high input which selects between AC or DC coupling for the PINP/ N[15:0] and PICLKP/N (LVDS) inputs. When active (default), the LVDS inputs will provide bias for AC coupled inputs. When disabled the LVDS inputs will provide DC level shifting for DC coupled inputs.

## TX Ref. Select (TXREFA\_NOTB) – Register

The TXREFA\_NOTB is the active high input which selects between REFCLKAP/N or REFCLKBP/N reference clock input. When the TXREFA\_NOTB is active (default), the REFCLKAP/N is selected to be the input for the TX Reference Frequency for the Clock Synthesis Unit (CSU). If the TXREFA\_NOTB is inactive, the REFCLKBP/N is used as the reference clock source for the CSU. See Table 1. This input is only accessible through the serial bus registers.

#### Table 1: Transmit Reference Source Select

| TXREFA_N<br>OTB | Reference Clock Source |

|-----------------|------------------------|

| 1               | REFCLKAP/N             |

| 0               | REFCLKBP/N             |

## SONET Rate Select (SONET\_RATESEL) – Register

SONET Rate Select. When active, the device is operating at SONET rate. When inactive, it is operating at either 10 G FC or GbE rate.

## GbE Rate Select (GBE\_RATESEL) – Register

GbE Rate Select. When active, the device is operating at 10 GbE or FC rate. The signal is only functional when SONET\_RATESEL is inactive.

## TX Ref. Rate Select (TXREFSEL) – Register

The TX Reference Rate Select (TXREFSEL) input selects between a 155.52 MHz or 622.08 MHz (or equivalent FEC/10 GbE/10G FC rate) reference clock. When SONET RATESEL is inactive, and GBE RATESEL is active, 10 GE reference (156.25 MHz) or FC reference (159.375 MHz) is used. When the SONET RATESEL is active, and TXREFSEL is inactive, the common reference 155 MHz clock is used; if TXREFSEL is set active, then 622 MHz is used. See Table 2, Transmit Reference Rate Select for the CSU. These inputs are only accessible through the serial bus registers.

|  | Table 2: | Transmit Reference Rate Select |

|--|----------|--------------------------------|

|--|----------|--------------------------------|

| TX<br>REF<br>SEL | SONET_<br>RATE<br>SEL | GBE_<br>RATE<br>SEL | Reference Clock<br>(MHz)<br>and Rate Multiplier           |  |

|------------------|-----------------------|---------------------|-----------------------------------------------------------|--|

| х                | 0                     | 1                   | (10GE) 156.25 or (FC) 159.375 (or<br>equiv. FEC rate) x66 |  |

| 0                | 1                     | х                   | 155 (or equiv. FEC rate) x64                              |  |

| 1                | 1                     | Х                   | 622 (or equiv. FEC rate) x16                              |  |

Note that the source of TXREFCLK is either REFCLKA or REFCLKB. The default is REFCLKAP/N.

# CSU Ref. Clock (REFCLKAP/N) – External Pin

The differential CML Reference Clock (REFCLKAP/N by default) input is used to drive the clock synthesizer Phase Lock Loop (PLL). See Table 3, Reference Frequency (CSU REFCLK) for the Clock Synthesis Unit and for the recommended FEC rates. The REFCLKAP/N input may go into the Phase Detector (PD) block shown in Figure 5. The output of the PD block (PD\_UP/PD\_DOWN) can be fed into an External filter and Voltage Controlled Oscillator (VCO) to clean up the REFCLKAP/N for improved jitter generation. The output of the external VCO is fed into the CSU IN input. The CSU IN will act as the reference clock for the CSU block if XVCO select input is active. Table 3 summarizes the increased CSU\_REFCLK rates required for FEC/10GbE/10G FC operation. The S19252 incorporates the bandwidth expansion requirements needed for the FEC applications that provide up to eight bytes of correction for a 255 byte block. Increased CSU REFCLK frequency is required for bandwidth expansion due to code words and Frame Synchronization Byte (FSB). This input is internally biased and terminated and must be AC coupled.

# External Voltage Controlled Oscillator (XVCO) – Register

The XVCO is the active high control input that selects CSU\_IN as the reference clock for the CSU block. When active, the CSU\_IN (output of the external VCO) input is used as the reference clock for the CSU for improved jitter generation. When inactive and in the normal mode, the CSU\_REFCLK is directly used as the reference clock for the CSU block. This input is only accessible through the serial bus register.

# Transmitter Reset (TX\_RSTB) – Register

The active low Transmitter Reset (TX\_RSTB) signal, when asserted low, will reset the CSU and associated logic. Use this reset after all Transmitter CSU and REFCLK control changes. When this bit is high (default) the CSU will function normal. This input is only accessible through the serial bus register.

### External Voltage Controlled Oscillator 155 MHz (XVCO155) – Register

The XVCO155 is the active high control for selecting either a 622 MHz (or equiv. FEC/10 GbE/10 GFC) or 155 MHz (or equiv. FEC/10 GbE/10 GFC) external VCO Frequency. When this bit is low (default), the XVCO operates at 622 MHz. When this bit is high, the XVCO operates at 155 MHz. This input is only accessible through the serial bus register.

# Kill Transmitter 155MCK Clock Output (KILLTXMCK) – Register

The active high Kill Transmitter 155MCK clock output (KILLTXMCK) signal, when asserted high, will force the TX\_155MCK clock output to a logic state determined by the CLKSTOP\_VAL. When this bit is low (default) the TX\_155MCK will function normal. This input is only accessible through the serial bus register.

# Kill Transmitter PCLK Output Clock (KILLPCLK) – Register

The active high Kill Transmitter PCLK output clock (KILLPCLK) signal, when asserted high, will force the PCLK clock output to a logic state determined by the CLKSTOP\_VAL. When this bit is low (default) the PCLK will function normal. This input is only accessible through the serial bus register.

### Kill Transmit Serial Data Output (KILLTXDATB) – Register

The active low Kill Transmitter Serial Data output (KILLTXDATB) signal, when asserted low, will force the TSD data output pins to a logic state determined by the TSD\_SQ\_POL. When this bit is high (default) the TSD output will function normal. This input is only accessible through the serial bus register.

Revision 5.03

| TXREF<br>SEL | SONET_<br>RATE<br>SEL | GBE_<br>RATE<br>SEL | Mode<br>Description                             | REFCLK<br>Multiplier /<br>Rate<br>Expansion | Serial Data<br>Output<br>Frequency<br>(Gbps) <sup>1</sup> | Required<br>CSU REFCLK<br>Frequency<br>(MHz) <sup>2</sup> |

|--------------|-----------------------|---------------------|-------------------------------------------------|---------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|

| 0            | 1                     | Х                   | STS-192, 0 bytes                                | 64 / 0%                                     | 9.95328                                                   | 155.52                                                    |

| 0            | 1                     | х                   | STS-192, Reed Soloman -<br>255/238              | 64 / 7.14%                                  | 10.664                                                    | 166.63                                                    |

| 0            | 1                     | х                   | STS-192, Reed Soloman -<br>255/237              | 64 / 7.59%                                  | 10.709                                                    | 167.33                                                    |

| 0            | 1                     | Х                   | 10 Gigabit Ethernet                             | 64 / 0%                                     | 10.000                                                    | 156.25                                                    |

| 0            | 0                     | 1                   | 10 Gigabit Ethernet 64/66B<br>Encoded           | 66 / 3.125%                                 | 10.3125                                                   | 156.25                                                    |

| 0            | 1                     | х                   | 10 Gigabit Ethernet 64/66B<br>Encoded           | 64 / 3.125%                                 | 10.3125                                                   | 161.13                                                    |

| 0            | 1                     | х                   | 10 Gigabit Ethernet 64/66B<br>Encoded - 255/238 | 64 / 7.14%                                  | 11.0491                                                   | 172.642                                                   |

| 0            | 1                     | х                   | 10 Gigabit Ethernet 64/66B<br>Encoded - 255/237 | 64 / 7.59%                                  | 11.0957                                                   | 173.37                                                    |

| 0            | 0                     | 1                   | 10 G Fibre Channel                              | 66 / 0%                                     | 10.51875                                                  | 159.375                                                   |

| 0            | 1                     | х                   | 10 G Fibre Channel                              | 64 / 0%                                     | 10.51875                                                  | 164.355                                                   |

| 0            | 1                     | х                   | 10 G Fibre Channel,<br>Reed Soloman- 255/238    | 64 / 7.14%                                  | 11.27                                                     | 176.096                                                   |

| 0            | 1                     | х                   | 10 G Fibre Channel,<br>Reed Soloman- 255/237    | 64 / 7.59%                                  | 11.3176                                                   | 176.838                                                   |

| 1            | 1                     | Х                   | STS-192, 0 bytes                                | 16 / 0%                                     | 9.95328                                                   | 622.08                                                    |

| 1            | 1                     | Х                   | STS-192, Reed Soloman -<br>255/238              | 16 / 7.14%                                  | 10.664                                                    | 666.514                                                   |

| 1            | 1                     | х                   | STS-192, Reed Soloman -<br>255/237              | 16 / 7.59%                                  | 10.709                                                    | 669.327                                                   |

#### Table 3: Reference Frequency (CSU REFCLK) for the Clock Synthesis Unit

1. Refer to CSU and CRU VCO Specifications in Table 28 for CSU VCO frequency range selection.

2. All Serial Data Rates shown for divide by 64 REFCLKs could also use divide by 16 REFCLKS by setting TXREFSEL to 1.

The BOLD CELLS denote the default state

## Clock Synthesizer Input (CSU\_INP/N) – External Pin

The clock synthesizer input is the differential REFCLK CML input to the internal CSU. This input is typically driven from an external VCO, which is controlled by an external loop filter and the internal phase detector output (PD\_UP, PD\_DWN). CSU\_IN will be used as the reference clock for the CSU block when XVCO control input is active. The S19252 should have low jitter generation when CSU\_IN is used as the reference clock in conjunction with the internal phase detector output. The CSU\_IN jitter generation will be as good as one could expect from a clean external CSU\_REFCLK. See Figure 20 and 21 for details. This input is internally biased and terminated and must be AC coupled.

Case 1. XVCO Select Input is Inactive - In this mode, the external VCO is bypassed. The output of the internal phase detector (PD block shown in Figure 5) is not used. The TXREFSEL input selects either the 155.52 MHz or 622.08 MHz reference frequency (CSU REFCLK input) for SONET/SDH applications. Accordingly, the CSU operates in the 155.52 MHz or 622.08 MHz CSU REFCLK mode. Case 2. XVCO Select Input is Active - In this mode, the external VCO is used. The output of the phase detector block (PD UP/DWN) is fed into the external filter/VCO. The output of the external VCO is fed into the CSU IN input. Setting the XVCO155 control register to a logic high will select a 155.52 MHz external VCO otherwise the external VCO would be 622.08 MHz with XVCO155=0 (default).

TXREFSEL input should be programmed to logic low when CSU REFCLK = 155.52 MHz. This enables the CSU\_IN divide by four (622.08 MHz Divide by four =

155.52 MHz) to go into one of the Phase Detector (PD) inputs. The 155.52 MHz CSU\_REFCLK directly goes into the second PD input. TXREFSEL should be programmed to logic high when CSU REFCLK = 622.08 MHz. This would enable the CSU\_IN (622.08 MHz output of the external VCO) directly into one of the Phase Detector (PD) inputs. The 622.08 MHz CSU REFCLK goes directly into the second Phase Detector (PD) input. See Table 4, *Reference Frequency with External VCO Selected.* Note that XVCO mode is not supported when GBE\_RATSEL=1. This input is only accessible through the serial bus register.

### TX Loop Filter (TXCAP1, TXCAP2) – External Pin

The transmit clock synthesizer unit external loop filter capacitor and resistors are connected to these pins. These devices should be surrounded by a ground shield. The component values are as stated in Table 38, *Transmit and Receive External Loop Filter Components*.

### Phase Initialization (PHINIT) – Register

The active high Phase Initialization (PHINIT) input is an asynchronous input that initializes the internal phase adjust circuit for the transmitter FIFO. When active, this input will align the PICLK and the internally generated PCLK. When AUTO\_FIFO\_INIT is not enabled, PHINIT must be asserted if the PHERR signal is active which indicates potential internal setup/hold timing violations. See *Figure 28, FIFO Initialization*. This input is only accessible through the serial bus register.

| Table 4:         Reference Frequency with External VCO Selected |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

| хусо | XVCO155 | SONET_RATSEL | TXREFSEL | CSU REFCLK | CSU_IN Frequency | CSU Mode   |

|------|---------|--------------|----------|------------|------------------|------------|

| 1    | 0       | 1            | 1        | 622.08 MHz | 622.08 MHz       | 622.08 MHz |

| 1    | 0       | 1            | 0        | 155.52 MHz | 622.08 MHz       | 622.08 MHz |

| 1    | 1       | 1            | 0        | 155.52 MHz | 155.52 MHz       | 155.52 MHz |

| 1    | 1       | 1            | 1        | 622.08 MHz | 155.52 MHz       | 155.52 MHz |

The BOLD CELLS denote the default state

4, d. en le

# Automatic FIFO Initialization (AUTO\_FIFO\_INIT) – Register

This active high control input internally connects the transmit FIFO signals (PHERR output and PHINIT input) and automatically initializes the FIFO in case of a PCLK/PICLK set-up or hold time violation. This input is only accessible through the serial bus register.

#### Transmit Built-In Self Test Enable (TX\_BIST\_EN) – Register

This active high input enables the transmit built-in self test mode. For normal system operation, TX\_BIST\_EN should be programmed to logic low. The S19252 goes in the BIST mode when TX\_BIST\_EN is programmed to logic high. Once the TX\_BIST\_EN is programmed to logic high, the PRBS generator will start sending the PRBS/user defined pattern (see Table 13 for details). The checker will be activated but will not start checking for the valid data pattern until RX\_LOCKDET is active. This function is accessible through the serial bus register. Note - While TX BIST is enabled the parallel input bus will not provide a TX\_DATA\_SWAP even if TX\_DATA\_SWAP is enabled.

#### Transmit Built-In Self Test Clear (TX\_BIST\_CLR) – Register

This active high level sensitive input clears the transmit built-in self test error (TX\_BIST\_ERR). For normal system operation, TX\_BIST\_CLR should be programmed to logic low. The TX\_BIST\_ERR flag can be cleared by asserting the TX\_BIST\_CLR in the BIST mode or by resetting (RSTB) the S19252. TX\_BIST\_CLR is an active high level sensitive input. In order for the transmit checker to clear the TX\_BIST\_ERR flag, TX\_BIST\_CLR must be asserted high. This input is only accessible through the serial bus register.

### Parallel Input Data Bus Swap (TX\_DATA\_SWAP) – Register

This input reverses the order of the parallel input data bus (PINP/N[15:0]). This makes routing easier with configurations requiring Data Bus bit order reversal.

AppliedMicro recommends that DATA\_SWAP input be programmed to logic low (Default) when S19252 is used with the 300-pin MSA connector. The S19252 should be placed on the top side of the module when used with the 300-pin MSA connector. See Table 22 for details. This input is only accessible through the serial bus register. TX BIST results are invalid while TX\_DATA\_SWAP is enabled.

## **Transmit Output Pin Description**

#### Transmit Serial Data (TSDP/N) – External Pin

The differential High Speed CML Transmit Serial Data (TSDP/N) output is the serialized version of the incoming parallel data stream. This output is typically used to drive the laser driver.

### Parallel Clock (PCLKP/N) – External Pin

The LVDS Parallel Clock (PCLKP/N) output is a 622.08 MHz (or equivalent FEC/10 GbE/10 GFC rates) internally generated clock output used to coordinate parallel data transfers with upstream logic. The PCLKP/N is directly derived from the CSU REFCLKP/N in the normal operating mode. PCLK is the divided-down version of the internal TXCLK. PCLK is used to clock data out of the upstream devices (framer/mapper). PCLK is also used internally to clock data from the FIFO into the parallel-to-serial shift register. See Table 35 for LVDS termination.

#### 155.52 MHz Clock Output (TX\_155MCKP/N) – External Pin

The LVDS 155.52 MHz Clock Output (or equivalent FEC/10 Gigabit Ethernet rate) TX\_155MCKP/N pin is an internally generated clock output used to drive the reference clock input of the receive section of the S19252 in the normal mode of operation. The TX\_155MCKP/N cannot be used as the reference clock for the receive section of the S19252 in the RLPTIME. See Table 35 for LVDS termination.

# Transmit Lock Detect (TX\_LOCKDET) – Register and External Pin

The active high transmit Lock Detect is an LVCMOS output. This asynchronous output will be active high once the internal PLL has locked to the clock provided on the CSU REFCLK input. The TX\_LOCKDET output goes active (high) when the PCLK is within 500 ppm from the CSU REFCLK. This output can be accessed through the serial bus register and through an external LVCMOS pin.

## Phase Error (PHERR) – Register

Phase Error is an active high output. To prevent errors caused by short set-up or hold times between the PICLK and internally generated PCLK, the timing generator circuitry monitors the phase relationship between the two clock domains. The Phase Error (PHERR) signal will be asserted high at the start of the PCLK cycle for which there may be setup/hold timing violations between the PICLK and internal byte clock (PCLK) timing domains. Since PHINIT will initialize the FIFO if a high level is held for at least 50 ns, the FIFO will be initialized if PHERR is connected to PHINIT on the serial bus. This output is only accessible through the serial bus register.

## Phase Detector Output (PD\_UP, PD\_DWN) – External Pin

These Phase Detector CML signals are the output of an internal phase detector which may be used to reduce jitter from an incoming CSU REFCLK or from an internally recovered clock used in loopback modes. This output is typically used to drive an external loop filter, which in turn controls a VCO that has its output feeding the CSU\_IN input. The internal phase detector, with the loop filter and VCO, form a PLL which may be used to remove jitter from CSU\_REFCLK or internal POCLK.

#### Transmit Built-In Self Test Error (TX\_BIST\_ERR) – Register

Active high transmit built-in self test error (TX BIST ERR) signal indicates a bit error in the transmit built-in self test loop. After the transmit checker is initialized, it will compare the parallel data output with the calculated pattern. If the parallel data output does not match the calculated pattern, the TX BIST ERR flag will be set active. The TX\_BIST\_ERR flag can be cleared by asserting TX\_BIST\_CLR in the TX\_BIST\_EN mode or by resetting (RSTB) the S19252. The TX BIST ERR can also be cleared with a rising edge of TX BIST EN. This output is only accessible through the serial bus register.

## **Receive Input Pin Description**

# Serial Data In (SERDATIP/N) – External Pin

The Serial Data In (SERDATIP/N) pins are the differential high Speed CML inputs. They receive inputs from an optics module or other upstream logic device. The S19252 extracts the clock from the SERDATIP/N inputs and provides a recovered clock (internal RSCLK) with re-timed parallel data. See Figure 28 for the SERDATIP/N termination scheme. The SERDATIP/N is internally terminated 100  $\Omega$  line-to-line (50  $\Omega$  + 50  $\Omega$  with center tap capacitor). The two 50  $\Omega$  resistors are center-tapped with a 25 pF capacitor for use in single-ended applications. The SERDATIP/N inputs must be AC coupled. These pins are internally biased and terminated 100  $\Omega$  line-to-line.

### SERDATIP/N Internal Termination (CENTER\_TAP) – External Pin

The SERDATIP/N is internally terminated with two 50  $\Omega$  resistors in series. The two 50  $\Omega$  resistors are center-tapped with an internal 25 pF capacitor to Ground. The input to the capacitor can be directly accessed through the CENTER\_TAP pin. This input should be connected to an external broadband 0.01  $\mu$ F capacitor to ground if driven single-ended or differential. This termination scheme enables the S19252 to be driven in the single-ended mode and offers better common mode noise rejection. See Figure 32 for the SERDATIP/N termination scheme.

# Receive Loop Filter (RXCAP1, RXCAP2) – External Pin

The CRU external loop filter capacitor and resistors are connected to the RXCAP1 and RXCAP2 pins. These devices should be surrounded by a ground shield. Component values should be as stated in Table 41, *Transmit and Receive External Loop Filter Components*.

## Receiver Reset (RX\_RSTB) – Register

The active low Receiver Reset (RX\_RSTB) signal, when asserted low, will reset the PA/CRU and associated logic. Use this reset after all Receiver VCO and REFCLK control changes. When this bit is high (default) the PA and CRU will function normal. This input is only accessible through the serial bus register.

The active low Lock-to-Reference (LCKREFN) input register, when asserted low, will force the PLL to lock to the Reference Clock defined by the RXREFSEL and de-assert RX\_LOCKDET. The POCLKP/N will lock to the reference clock in this mode. When the LCKREFN is inactive (high), the POCLKP/N will lock to the valid incoming serial data (SERDATIP/N). This input should be programmed to logic high for normal operation. This input is only accessible through the serial bus register.

## LOS/Signal Detect (LOS\_SD) – External Pin

This is a dual-purpose pin that can be either an input or output pin, the I/O function is controlled by setting LOS\_SDC bit via serial bus. When the LOS\_SDC is set to '0', this pin will be a Signal Detect input pin. The default of this pin is a Signal-Detect input pin.

The Signal-Detect is an active high or active low LVCMOS single-ended input to be driven by the external optical receiver module to indicate the presence of received optical power. Signal Detect active level (high or low) is programmed by the SD\_POL.

As an output pin, by setting the LOS\_SDC to '1' and the RX\_LOS\_CNTL to '1', this pin will act as a Loss-of-Signal (LOS) output pin. When the SD\_POL is set to '1', the LOS\_SD will be active high.

When a loss-of-light condition occurs, a de-asserted Signal-Detect (LOS\_SD) input pin or an asserted Loss-of-Signal (LOS\_SD) output pin will cause the internal PLL to be locked to the CRU reference input signal and if, the squelch function is enabled (default), the SERDATIP/N (and POUT[15:0]) will be forced to a Logic '0' state.

### Signal Detect Polarity (SD\_POL) – Register

The signal detect polarity is an input signal that will set the LOS\_SD input as either active high or active low. Setting this pin low will set the LOS\_SD input as active low. Setting this pin high will set the LOS\_SD input as active high. This input is only accessible through the serial bus register.

# RX Ref. Select (RXREFA\_NOTB) – Register

The RX Reference Select (RXREFA\_NOTB) input selects between REFCLKAP/N or REFCLKBP/N reference clock input. When the RXREFA\_NOTB is set low (default), the REFCLKBP/N is selected to be the input for the Receiver Reference Frequency for the Clock Data Recover Unit (CRU). When this bit is set high, the REFCLKAP/N is used as the CRU reference frequency input. This input is only accessible through the serial bus registers.

| Table 5: | <b>Receive Reference</b> | Source Select |

|----------|--------------------------|---------------|

|----------|--------------------------|---------------|

| RXREFA_NOTB | Reference Clock Source |  |  |  |

|-------------|------------------------|--|--|--|

| 1           | REFCLKAP/N             |  |  |  |

| 0           | REFCLKBP/N (Default)   |  |  |  |

#### Receive Reference Rate Select (RXREFSEL) – Register

This is the receive reference rate select input. When SONET\_RATESEL is low, and GBE\_RATESEL is high denotes that the 10 GE reference (156.25 MHz) or FC reference (159.375 MHz) is used. When SONET\_RATESEL is high, the RXREFSEL low indicates that the 155 MHz clock is used; and while high 622 MHz clock is used. See Table 6. This input is only accessible through the serial bus register.

Table 6:

Receive Reference Rate Select

| RX<br>REF<br>SEL | SONET_<br>RATE<br>SEL | GBE_<br>RATE<br>SEL | Reference Clock<br>(MHz) and Rate<br>Multiplier              |

|------------------|-----------------------|---------------------|--------------------------------------------------------------|

| x                | 0                     | 1                   | (10GE) 156.25 or (FC)<br>159.375 (or equiv. FEC<br>rate) x66 |

| 0                | 1                     | х                   | 155 (or equiv. FEC rate)<br>x64                              |

| 1                | 1                     | Х                   | 622 (or equiv. FEC rate)<br>x16                              |

Note that the source of RXREFCLK is either REFCLKA or REFCLKB. The default is REFCLKBP/N.

## CRU Reference Clock (REFCLKAP/N) – External Pin

The differential REFCLK CML 155.52 MHz (or equivalent FEC/10 Gigabit Ethernet Rate) reference clock (CRU REFCLKP/N) input is used to establish the initial operating frequency of the Phase Lock Loop (PLL). This input can also be driven by the 155MCKP/ N output from the transmit section of S19252. Table 7 summarizes the settings and increased CRU REFCLK

rates required for the FEC operation. The S19252 incorporates the bandwidth expansion requirements needed for FEC/10 GB Ethernet applications that provide up to eight bytes of correction per 255 byte block. Increased CRU\_REFCLK frequency is required for bandwidth expansion due to code words and Frame Synchronization Byte (FSB). This input is internally biased and terminated 100  $\Omega$  line-to-line and must be AC coupled.

|              |                       |                     |                                                 | REFCLK                            | Serial Data                               | Required                                      |

|--------------|-----------------------|---------------------|-------------------------------------------------|-----------------------------------|-------------------------------------------|-----------------------------------------------|

| RXREF<br>SEL | SONET_<br>RATE<br>SEL | GBE_<br>RATE<br>SEL | Mode<br>Description                             | Multiplier /<br>Rate<br>Expansion | Input<br>Frequency<br>(Gbps) <sup>1</sup> | CRU REFCLK<br>Frequency<br>(MHz) <sup>2</sup> |

| 0            | 1                     | Х                   | STS-192, 0 bytes                                | 64 / 0%                           | 9.95328                                   | 155.52                                        |

| 0            | 1                     | х                   | STS-192, Reed Soloman -<br>255/238              | 64 / 7.14%                        | 10.664                                    | 166.63                                        |

| 0            | 1                     | х                   | STS-192, Reed Soloman -<br>255/237              | 64 / 7.59%                        | 10.709                                    | 167.33                                        |

| 0            | 1                     | Х                   | 10 Gigabit Ethernet                             | 64 / 0%                           | 10.000                                    | 156.25                                        |

| 0            | 0                     | 1                   | 10 Gigabit Ethernet 64/66B<br>Encoded           | 66 / 3.125%                       | 10.3125                                   | 156.25                                        |

| 0            | 1                     | х                   | 10 Gigabit Ethernet 64/66B<br>Encoded           | 64 / 3.125%                       | 10.3125                                   | 161.13                                        |

| 0            | 1                     | х                   | 10 Gigabit Ethernet 64/66B<br>Encoded - 255/238 | 64 / 7.14%                        | 11.0491                                   | 172.642                                       |

| 0            | 1                     | х                   | 10 Gigabit Ethernet 64/66B<br>Encoded - 255/237 | 64 / 7.59%                        | 11.0957                                   | 173.37                                        |

| 0            | 0                     | 1                   | 10 G Fibre Channel                              | 66 / 0%                           | 10.51875                                  | 159.375                                       |

| 0            | 1                     | х                   | 10 G Fibre Channel                              | 64 / 0%                           | 10.51875                                  | 164.355                                       |

| 0            | 1                     | х                   | 10 G Fibre Channel,<br>Reed Soloman- 255/238    | 64 / 7.14%                        | 11.27                                     | 176.096                                       |

| 0            | 1                     | х                   | 10 G Fibre Channel,<br>Reed Soloman- 255/237    | 64 / 7.59%                        | 11.3176                                   | 176.838                                       |

| 1            | 1                     | х                   | STS-192, 0 bytes                                | 16 / 0%                           | 9.95328                                   | 622.08                                        |

| 1            | 1                     | х                   | STS-192, Reed Soloman -<br>255/238              | 16 / 7.14%                        | 10.664                                    | 666.514                                       |

| 1            | 1                     | х                   | STS-192, Reed Soloman -<br>255/237              | 16 / 7.59%                        | 10.709                                    | 669.327                                       |

#### Table 7: Reference Frequency (CRU REFCLK) for the Clock and Data Recovery Unit

1. Refer to CSU and CRU VCO Specifications in Table 28 for CRU VCO frequency range selection.

2. All Serial Data Rates shown for divide by 64 REFCLKs could also use divide by 16 REFCLKS by setting RXREFSEL to 1.

Revision 5.03

AppliedMicro - Confidential and Proprietary

### Kill Parallel Output Clock (KILLPOCLK) – Register

The active high Kill Parallel Output Clock (KILLPOCLK) signal, when asserted high, will force the POCLK output to a state specified by the CLKSTOP\_VAL register bit. This input may be programmed to logic '0' for normal operation. This input is only accessible through the serial bus register.

### Kill Parallel Output Data (KILLPOUTB) – Register

The active low Kill Parallel Output Data (KILLPOUTB) signal, when asserted low, will force the POUT[15:0] output to a logic '0' state. This input may be programmed to logic '1' for normal operation. This input is only accessible through the serial bus register.

#### Kill Parallel Output MCK Clock (KILLRXMCK) – Register

The active high Kill Parallel Output 622MCK Clock (KILLRXMCK) signal, when asserted high, will force the 622MCK output to a state specified by the CLKSTOP\_VAL register bit. This input may be programmed to logic '0' for normal operation. This input is only accessible through the serial bus register.

### Receive Built-In Self Test Enable (RX\_BIST\_EN) – Register

This active high input enables the receive built-in self test mode. For normal system operation, RX\_BIST\_EN should be programmed to logic '0'. The S19252 goes in the BIST mode when RX\_BIST\_EN is programmed to logic high. Once the RX\_BIST\_EN is programmed to logic high, the PRBS generator will start sending the PRBS/user defined pattern (see Table 13 for details) through the parallel outputs, and the checker will be activated but will not start checking for the valid data pattern until TX\_LOCKDET is active. This input is only accessible through the serial bus register. *Note* - While RX BIST is enabled the parallel output bus will not provide a RX\_DATA\_SWAP even if RX\_DATA\_SWAP is enabled.

### Receive Built-In Self Test Clear (RX\_BIST\_CLR) – Register

This active high level sensitive input clears the receive Built-In Self Test Error (RX\_BIST\_ERR). For normal system operation, RX\_BIST\_CLR should be programmed to logic '0'. The RX\_BIST\_ERR flag can be cleared by asserting RX\_BIST\_CLR in the BIST mode or by resetting (RSTB) the S19252. RX\_BIST\_CLR is an active high level sensitive input. In order for the receive checker to clear the RX\_BIST\_ERR flag, the RX\_BIST\_CLR must be asserted high. This input is only accessible through the serial bus register.

### LOS Threshold Assert (LOS\_VTH\_AST [7:0]) – Register

The LOS Threshold Assert (LOS\_VTH\_AST[7:0]) inputs control the LOS assert threshold for the high speed serial input. The 8-bit control register set the LOS assert voltage where the Loss of signal condition is declared. These inputs are only accessible through the serial bus registers

### LOS Threshold De-Assert (LOS\_VTH\_DST [7:0]) – Register

The LOS Threshold De-Assert (LOS\_VTH\_DST[7:0]) inputs control the LOS de-assert threshold for the high speed serial input. The 8-bit control register set the LOS de-assert voltage where the Loss of signal condition is declared. These inputs are only accessible through the serial bus registers

### Phase Adjust (PHASE\_ADJ[2:0]) – Register

The Phase Adjust (PHASE\_ADJ[2:0]) inputs control the phase offset between the high speed recovered data and clock for improved bit error rate and link budgets. These registers are not adaptively controlled. See Table 8 for details of the phase adjust settings. These inputs are only accessible through the serial bus registers.

| Table 8: | Phase Ad | just Control |

|----------|----------|--------------|

|----------|----------|--------------|

| Phase Adjust Input (PHASE_ADJ) |                |             |                  |  |  |  |

|--------------------------------|----------------|-------------|------------------|--|--|--|

| 2                              | 1              | 0           | Phase Adjustment |  |  |  |

| 0                              | 0              | 0           | +8.5 ps          |  |  |  |

| 0                              | 0              | 1           | +5.5 ps          |  |  |  |

| 0                              | 1              | 1 0 +2.5 ps |                  |  |  |  |

| 0                              | 1              | 1 1 0 ps    |                  |  |  |  |

| 1                              | 0 0            |             | -2.5 ps          |  |  |  |

| 1                              | 1 0 1          |             | -5.2 ps          |  |  |  |

| 1                              | 1 0            |             | -8.0 ps          |  |  |  |

| 1                              | 1 1 1 -11.0 ps |             |                  |  |  |  |

The BOLD CELLS denote the device default state. The PHASE\_ADJ inputs is recommended to be set to "010" state for optimal performance.

#### Post Amplifier Offset Adjust (PAOFFADJ[9:0]) and Adaptive Post Amplifier Offset Adjust Enable (ADAPOFFADJ) – Registers

The Post-Amp Offset Adjust (PAOFFADJ[9:0]) inputs may be used to compensate for input data signal duty cycle distortion or asymmetrical noise (for example EDFA noise). The PAOFFADJ[9:8] control the step resolution ( $\Delta$ ) of the post-amp offset change. PAOFFADJ[7:0] control the post-amp offset adjustment settings (number of steps =  $2^8$  = 256). The positive portion of the differential data signal may be relatively offset from the negative by ±78 mV/±39 mV/±28 mV/ ±19 mV with a resolution ( $\Delta$ ) of 0.6 mV/0.3 mV/ 0.22 mV/0.15 mV respectively. See Table 9 for details of the post-amp offset adjust settings.

The ADAPOFFADJ is an active high input that enables the adaptive setting of the offset adjust to enhance the bit error rate. Upon start up with ADAPOFFADJ active, the default value gets loaded onto the PAOFFADJ[9:8] registers. The feedback control loop in the S19252 will find the setting for offset adjustment that yields the best possible bit error rate. When ADAPOFFADJ is disabled, PAOFFADJ[9:0] must be externally controlled to achieve the best possible bit error rate. See Table 10 for details of the adaptive post-amp offset adjust settings.These inputs are only accessible through the serial bus registers.

| t |

|---|

|   |

| PAOFFADJ[9:8] Settings for Resolution/Range |           |                          |  |  |  |  |  |

|---------------------------------------------|-----------|--------------------------|--|--|--|--|--|

| PAOFFADJ9                                   | PAOFFADJ8 | Resolution=<br>∆/± Range |  |  |  |  |  |

| 0                                           | 0         | 0.6mV/±78mV              |  |  |  |  |  |

| 0                                           | 1         | 0.3mV/±39mV              |  |  |  |  |  |

| 1                                           | 0         | 0.22mV/±28mV             |  |  |  |  |  |

| 1                                           | 1         | 0.15mV/±19mV             |  |  |  |  |  |

PAOFFADJ[7:0] Settings for Offset Adjustment

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | α   | SERDATIP-<br>SERDATIN =     |

|---|---|---|---|---|---|---|---|-----|-----------------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   | -128 * ∆ mV                 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1   | -127 * ∆ mV                 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 2   | -126 * ∆ mV                 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 3   | -125 * ∆ mV                 |

| Х | Х | Х | Х | Х | х | Х | Х | α   | $(-128+\alpha)^* \Delta mV$ |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 254 | 126 * ∆ mV                  |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 255 | 127 * ∆ mV                  |

The BOLD CELLS denote the default state. The default state settings for PAOFFADJ[7:0] may vary from one device to another.

| ADAPOFFADJ | Adaptive Offset Adjust Control                                                                                      |  |  |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0          | Inactive. (PAOFFADJ[9:0] must be exter-<br>nally controlled for offset adjustment)                                  |  |  |  |  |  |  |

| 1          | Active (Set the resolution through PAOF-<br>FADJ[9:8]. PAOFFADJ[7:0] are adap-<br>tively controlled to enhance BER) |  |  |  |  |  |  |

The BOLD CELLS denote the default state

#### Parallel Output Data Bus Swap (RX\_DATA\_SWAP) – Register

This input reverses the order of the parallel output data bus (POUTP/N[15:0]). This makes routing easier with configurations requiring Data Bus bit order reversal.

AppliedMicro recommends that DATA\_SWAP input be programmed to logic low (Default) when S19252 is used with the 300-pin MSA connector. The S19252 should be placed on the top side of the module when used with the 300-pin MSA connector. See Table 22 for details. This input is only accessible through the serial bus register. While RX BIST is enabled the parallel output bus will not provide a RX\_DATA\_SWAP even if RX DATA SWAP is enabled.

## **Receive Output Pin Description**

## Parallel Output Clock (POCLKP/N) – External Pin

The LVDS Parallel Output Clock (POCLKP/N) output is an internally regenerated clock which is used to transfer demultiplexed data from an internal holding register to the output register, which drives the parallel output data bus POUTP/N [15:0]. This clock is synchronized with the parallel output data. According to OIF99.102.5, section 9.0 for an SFI4 phase 1 I/O, the clock edges should align to the data edges in order to simplify the driver macro design for the SERDES and framers (to do this invert the POCLKP/N by swapping the P and N pins). As is the rising edge of the POCLKP/N is instead centered with the output data valid window (POUTP/N[15:0]). This simplifies the board design, as delaying the clock on the board is not required. See Table 35 for LVDS termination.

## Parallel Output Data (POUTP/N[15:0]) – External Pin

The Parallel Output Data (POUTP/N[15:0]) LVDS outputs are re-timed data that are output from the demultiplexer at a rate of 622.08 Mbps (or equivalent FEC/10 Gigabit Ethernet rate). Bit 15 is the most significant bit and is the first received bit. The data is re-timed and synchronized to the Parallel Output Clock (POCLKP/N). This bus is typically connected to a framer, mapper or digital wrapper (e.g. AppliedMicro's KHATANGA, GANGES or RUBICON). See Table 35 for LVDS termination.

# Receive Lock Detect (RX\_LOCKDET) – Register and External Pin

Active high LVCMOS Lock Detect (RX\_LOCKDET) signal indicates a valid incoming data stream. When inactive (low), it indicates that the incoming data stream has failed the frequency test as dictated by the PLL or that LCKREFN has been asserted low or LOS\_SD has been de-asserted for negated Signal-Detect input or asserted for Loss-of-Signal output. This test is used to determine if the serial input data is valid. When RX\_LOCKDET is active, the PLL is locked to the data stream. This output can be accessed through the serial bus register and external LVCMOS pin.

#### Recovered 622.08/155.52 MHz Clock (RX\_MCKP/N) – External Pin

The LVDS 622.08/155 MHz Clock (or equivalent FEC/ 10 Gigabit Ethernet rate) (RX\_MCKP/N) is the clock which is recovered from the input data stream. When RX622SEL is asserted, RXMCK is 622 MHz. When the RX622SEL is de-asserted, RXMCK is 155 MHz. This clock may be used to drive the reference clock input of the transmit side (CSU REFCLK) of the S19252. See Table 35 for LVDS termination.

#### Receive Built-In Self Test Error (RX\_BIST\_ERR) – Register

The active high receive Built-In Self Test Error (RX BIST ERR) signal indicates a bit error in the receive built-in self test loop. After the receive checker is initialized, it will compare the parallel data input with the calculated pattern. If the parallel data input does not match the calculated pattern, the RX BIST ERR flag will be set active. The RX BIST ERR flag can be asserting RX BIST CLR cleared by in the RX BIST EN mode or by resetting (RSTB) the S19252. The RX BIST ERR can also be cleared with a rising edge of RX BIST EN. This output is only accessible through the serial bus register.

## **Common Input Pin Description**

### Reset (RSTB) – External Pin

This active low LVCMOS Reset (RSTB) input asynchronously resets the device. All clocks, including PCLK, are disabled during reset. For normal system operation, VDD\_3.3V should be connected to RSTB input. This input should be active for 100 ns to accurately reset the device. This input can be accessed through the external LVCMOS input pin.

# Diagnostic Loopback Enable (DLEB) – Register

The DLEB is an active low input that selects the diagnostic loopback mode. In this mode, the Transmitter Data (TSD) is routed internally from the transmitter to the receiver. When DLEB mode is enabled, the received parallel data from the framer/ mapper transmit path is routed back to the receive parallel data path of the framer/mapper. This mode allows the digital side of the node to be isolated from the rest of the network. The received serial data, SERDATIP/N, will not be passed on to the framer/ mapper. The network, however, will receive the aligned high-speed data TSD, when DLEB mode is active. This input is accessible through the serial bus register.

### Line Loopback Enable (LLEB) – Register