## TP3054-X, TP3057-X

# Extended Temperature Serial Interface CODEC/Filter COMBO® Family

## **General Description**

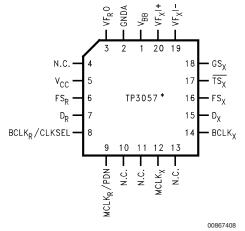

The TP3054, TP3057 family consists of  $\mu$ -law and A-law monolithic PCM CODEC/filters utilizing the A/D and D/A conversion architecture shown in *Figure 1*, and a serial PCM interface. The devices are fabricated using National's advanced double-poly CMOS process (microCMOS).

The encode portion of each device consists of an input gain adjust amplifier, an active RC pre-filter which eliminates very high frequency noise prior to entering a switched-capacitor band-pass filter that rejects signals below 200 Hz and above 3400 Hz. Also included are auto-zero circuitry and a companding coder which samples the filtered signal and encodes it in the companded µ-law or A-law PCM format. The decode portion of each device consists of an expanding decoder, which reconstructs the analog signal from the companded  $\mu$ -law or A-law code, a low-pass filter which corrects for the sin x/x response of the decoder output and rejects signals above 3400 Hz followed by a single-ended power amplifier capable of driving low impedance loads. The devices require two 1.536 MHz, 1.544 MHz or 2.048 MHz transmit and receive master clocks, which may be asynchronous; transmit and receive bit clocks, which may vary from 64 kHz to 2.048 MHz; and transmit and receive frame sync pulses. The timing of the frame sync pulses and PCM data is compatible with both industry standard formats.

#### **Features**

- -40°C to +85°C operation

- Complete CODEC and filtering system (COMBO) including:

- Transmit high-pass and low-pass filtering

- Receive low-pass filter with sin x/x correction

- Active RC noise filters

- μ-law or A-law compatible COder and DECoder

- Internal precision voltage reference

- Serial I/O interface

- Internal auto-zero circuitry

- µ-law, 16-pin—TP3054

- A-law, 16-pin—TP3057

- Designed for D3/D4 and CCITT applications

- ±5V operation

- Low operating power—typically 50 mW

- Power-down standby mode typically 3 mW

- Automatic power-down

- TTL or CMOS compatible digital interfaces

- Maximizes line interface card circuit density

- Dual-In-Line or PCC surface mount packages

- See also AN-370, "Techniques for Designing with CODEC/Filter COMBO Circuits"

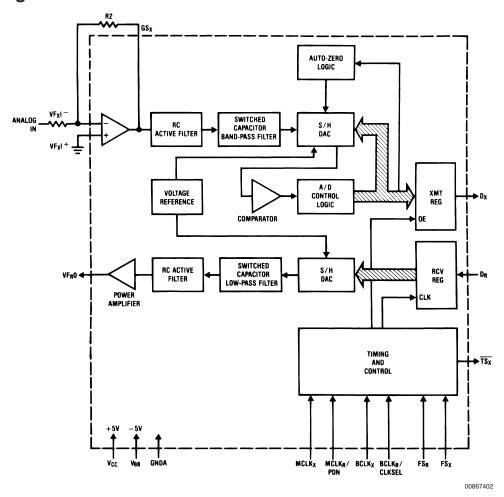

## **Connection Diagrams**

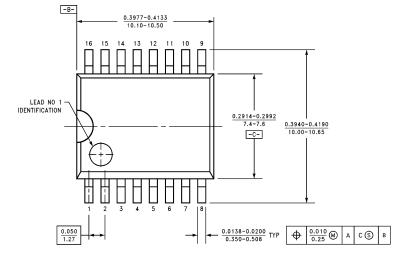

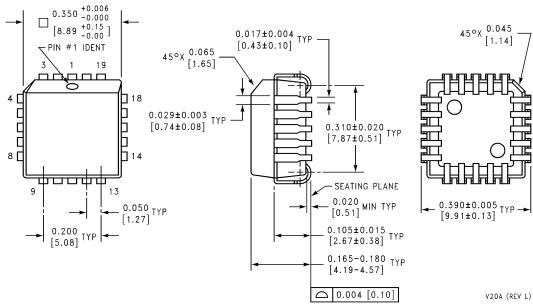

### Plastic Chip Carriers

Top View Order Number TP3057V-X NS Package Number V20A

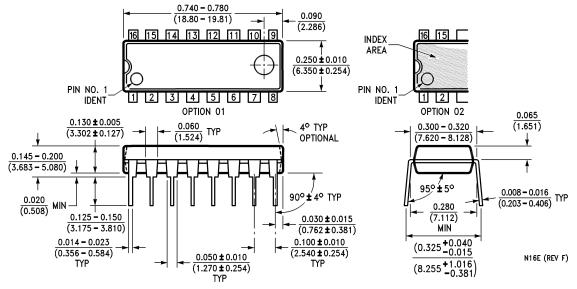

#### **Dual-In-Line Package**

Top View

Order Number TP3054N-X

NS Package Number N16E

Order Number TP3054WM-X

NS Package Number M16B

COMBO® and TRI-STATE® are registered trademarks of National Semiconductor Corporation.

# **Block Diagram**

FIGURE 1.

| Pin Descriptions | Symbol | Function |

|------------------|--------|----------|

|------------------|--------|----------|

| $\mathbf{Symbol} \\ \mathbf{V}_{\mathrm{BB}}$ | <b>Function</b> Negative power supply pin.                                                                                                                                                                                     | BCLK <sub>R</sub> /CLKSEL | The bit clock which shifts data into $D_R$ after the $FS_R$ leading edge. May vary from 64 kHz to 2.048 MHz.                                                                                                |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GNDA                                          | $V_{BB} = -5V \pm 5\%$ .<br>Analog ground. All signals are referenced to this pin.                                                                                                                                             |                           | Alternatively, may be a logic input which selects either 1.536 MHz/1.544 MHz or 2.048 MHz for master clock in                                                                                               |

| VF <sub>R</sub> O                             | Analog output of the receive power amplifier.                                                                                                                                                                                  |                           | synchronous mode and BCLK <sub>X</sub> is used for both transmit and receive directions                                                                                                                     |

| V <sub>CC</sub>                               | Positive power supply pin. $V_{CC} = +5V \pm 5\%$ .                                                                                                                                                                            | MCLK <sub>B</sub> /PDN    | (see <i>Table 1</i> ).  Receive master clock. Must be 1.536                                                                                                                                                 |

| FS <sub>R</sub>                               | Receive frame sync pulse which enables $\mathrm{BCLK}_{\mathrm{R}}$ to shift PCM data into $\mathrm{D}_{\mathrm{R}}$ . FS $_{\mathrm{R}}$ is an 8 kHz pulse train. See <i>Figure 2</i> and <i>Figure 3</i> for timing details. | ·                         | MHz, 1.544 MHz or 2.048 MHz. May be asynchronous with $\mathrm{MCLK}_{\mathrm{X}}$ , but should be synchronous with $\mathrm{MCLK}_{\mathrm{X}}$ for best performance. When $\mathrm{MCLK}_{\mathrm{R}}$ is |

| D <sub>R</sub>                                | Receive data input. PCM data is shifted into $D_R$ following the $FS_R$ leading edge.                                                                                                                                          |                           | connected continuously low, $\mathrm{MCLK}_{\mathrm{X}}$ is selected for all internal timing. When $\mathrm{MCLK}_{\mathrm{R}}$ is connected continuously high, the device is powered down.                 |

## Pin Descriptions (Continued)

| Symbol            | Function                                                                                                                                                                                |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLK <sub>X</sub> | Transmit master clock. Must be 1.536 MHz, 1.544 MHz or 2.048 MHz. May be asynchronous with MCLK $_{\rm R}$ . Best performance is realized from synchronous operation.                   |

| FS <sub>X</sub>   | Transmit frame sync pulse input which enables $BCLK_X$ to shift out the PCM data on $D_X$ . $FS_X$ is an 8 kHz pulse train, see <i>Figure 2</i> and <i>Figure 3</i> for timing details. |

| BCLK <sub>X</sub> | The bit clock which shifts out the PCM data on $D_x$ . May vary from 64 kHz to 2.048 MHz, but must be synchronous with MCLK <sub>x</sub> .                                              |

| $D_X$             | The TRI-STATE® PCM data output which is enabled by FS <sub>x</sub> .                                                                                                                    |

| $\overline{TS_X}$ | Open drain output which pulses low during the encoder time slot.                                                                                                                        |

| GS <sub>X</sub>   | Analog output of the transmit input amplifier. Used to externally set gain.                                                                                                             |

| $VF_XI^-$         | Inverting input of the transmit input amplifier.                                                                                                                                        |

| $VF_XI^+$         | Non-inverting input of the transmit input amplifier.                                                                                                                                    |

## **Functional Description**

#### **POWER-UP**

When power is first applied, power-on reset circuitry initializes the COMBO and places it into a power-down state. All non-essential circuits are deactivated and the  $D_{\rm X}$  and  $VF_{\rm R}O$  outputs are put in high impedance states. To power-up the device, a logical low level or clock must be applied to the MCLK<sub>R</sub>/PDN pin and FS\_X and/or FS\_R pulses must be present. Thus, 2 power-down control modes are available. The first is to pull the MCLK\_R/PDN pin high; the alternative is to hold both FS\_X and FS\_R inputs continuously low—the device will power-down approximately 1 ms after the last FS\_X or FS\_R pulse. Power-up will occur on the first FS\_X or FS\_R pulse. The TRI-STATE PCM data output, D\_X, will remain in the high impedance state until the second FS\_X pulse.

#### SYNCHRONOUS OPERATION

For synchronous operation, the same master clock and bit clock should be used for both the transmit and receive directions. In this mode, a clock must be applied to  $\mathsf{MCLK}_\mathsf{X}$  and the  $\mathsf{MCLK}_\mathsf{R}/\mathsf{PDN}$  pin can be used as a power-down control. A low level on  $\mathsf{MCLK}_\mathsf{R}/\mathsf{PDN}$  powers up the device and a high level powers down the device. In either case,  $\mathsf{MCLK}_\mathsf{X}$  will be selected as the master clock for both the transmit and receive circuits. A bit clock must also be applied to  $\mathsf{BCLK}_\mathsf{X}$  and the  $\mathsf{BCLK}_\mathsf{R}/\mathsf{CLKSEL}$  can be used to select the proper internal divider for a master clock of 1.536 MHz, 1.544 MHz or 2.048 MHz. For 1.544 MHz operation, the device automatically compensates for the 193rd clock pulse each frame.

With a fixed level on the BCLK $_{\rm R}$ /CLKSEL pin, BCLK $_{\rm X}$  will be selected as the bit clock for both the transmit and receive directions. *Table 1* indicates the frequencies of operation which can be selected, depending on the state of BCLK $_{\rm R}$ /CLKSEL. In this synchronous mode, the bit clock, BCLK $_{\rm X}$ , may be from 64 kHz to 2.048 MHz, but must be synchronous with MCLK $_{\rm X}$ .

Each FS $_{\rm X}$  pulse begins the encoding cycle and the PCM data from the previous encode cycle is shifted out of the enabled D $_{\rm X}$  output on the positive edge of BCLK $_{\rm X}$ . After 8 bit clock periods, the TRI-STATE D $_{\rm X}$  output is returned to a high impedance state. With an FS $_{\rm R}$  pulse, PCM data is latched via the D $_{\rm R}$  input on the negative edge of BCLK $_{\rm X}$  (or BCLK $_{\rm R}$  if running). FS $_{\rm X}$  and FS $_{\rm R}$  must be synchronous with MCLK $_{\rm X/R}$ .

**TABLE 1. Selection of Master Clock Frequencies**

|                           | Master Clock |              |  |  |  |  |  |  |

|---------------------------|--------------|--------------|--|--|--|--|--|--|

| BCLK <sub>R</sub> /CLKSEL | Frequenc     | y Selected   |  |  |  |  |  |  |

|                           | TP3057       | TP3054       |  |  |  |  |  |  |

| Clocked                   | 2.048 MHz    | 1.536 MHz or |  |  |  |  |  |  |

|                           |              | 1.544 MHz    |  |  |  |  |  |  |

| 0                         | 1.536 MHz or | 2.048 MHz    |  |  |  |  |  |  |

|                           | 1.544 MHz    |              |  |  |  |  |  |  |

| 1                         | 2.048 MHz    | 1.536 MHz or |  |  |  |  |  |  |

|                           |              | 1.544 MHz    |  |  |  |  |  |  |

#### **ASYNCHRONOUS OPERATION**

For asynchronous operation, separate transmit and receive clocks may be applied.  $MCLK_X$  and  $MCLK_R$  must be 2.048 MHz for the TP3057, or 1.536 MHz, 1.544 MHz for the TP3054, and need not be synchronous. For best transmission performance, however, MCLK<sub>B</sub> should be synchronous with MCLK<sub>x</sub>, which is easily achieved by applying only static logic levels to the MCLK<sub>R</sub>/PDN pin. This will automatically connect  $\mathsf{MCLK}_\mathsf{X}$  to all internal  $\mathsf{MCLK}_\mathsf{R}$  functions (see Pin Description). For 1.544 MHz operation, the device automatically compensates for the 193rd clock pulse each frame. FS<sub>x</sub> starts each encoding cycle and must be synchronous with MCLKx and BCLKx. FSB starts each decoding cycle and must be synchronous with BCLK<sub>R</sub>. BCLK<sub>R</sub> must be a clock, the logic levels shown in Table 1 are not valid in asynchronous mode.  $\operatorname{BCLK}_X$  and  $\operatorname{BCLK}_R$  may operate from 64 kHz to 2.048 MHz.

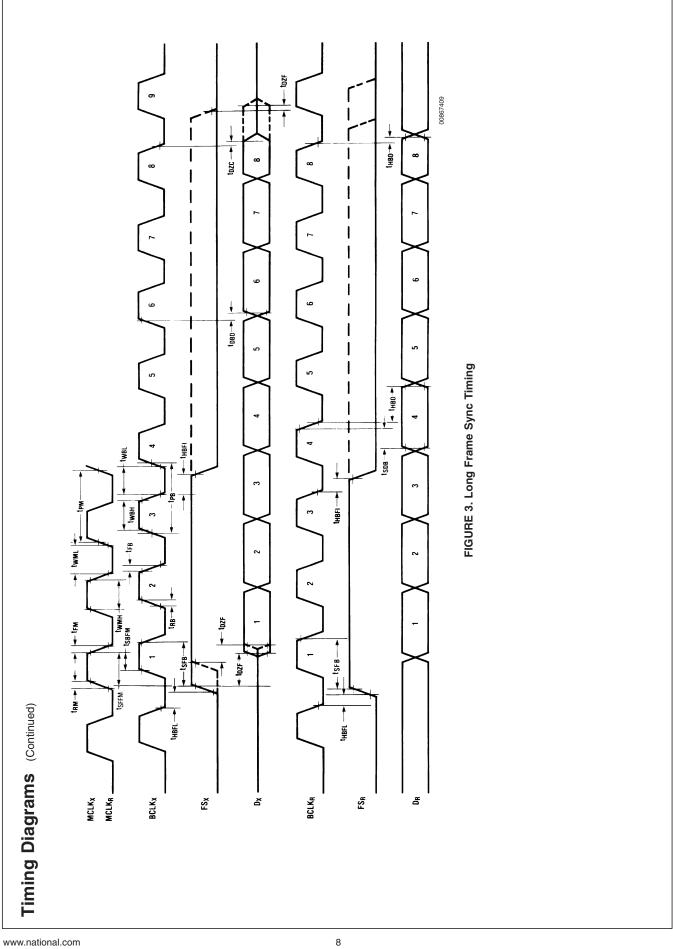

#### SHORT FRAME SYNC OPERATION

The COMBO can utilize either a short frame sync pulse or a long frame sync pulse. Upon power initialization, the device assumes a short frame mode. In this mode, both frame sync pulses,  $FS_{\rm X}$  and  $FS_{\rm R}$ , must be one bit clock period long, with timing relationships specified in Figure 2. With  $FS_{\rm X}$  high during a falling edge of BCLK\_X, the next rising edge of BCLK\_X enables the  $D_{\rm X}$  TRI-STATE output buffer, which will output the sign bit. The following seven rising edges clock out the remaining seven bits, and the next falling edge disables the  $D_{\rm X}$  output. With  $FS_{\rm R}$  high during a falling edge of BCLK\_R (BCLK\_X in synchronous mode), the next falling edge of BCLK\_R latches in the sign bit. The following seven falling edges latch in the seven remaining bits. All four devices may utilize the short frame sync pulse in synchronous or asynchronous operating mode.

#### Functional Description (Continued)

#### LONG FRAME SYNC OPERATION

To use the long frame mode, both the frame sync pulses, FS<sub>X</sub> and FS<sub>B</sub>, must be three or more bit clock periods long, with timing relationships specified in Figure 3. Based on the transmit frame sync, FSx, the COMBO will sense whether short or long frame sync pulses are being used. For 64 kHz operation, the frame sync pulse must be kept low for a minimum of 160 ns. The  $\mathrm{D}_{\mathrm{X}}$  TRI-STATE output buffer is enabled with the rising edge of FSX or the rising edge of BCLK<sub>x</sub>, whichever comes later, and the first bit clocked out is the sign bit. The following seven BCLK<sub>X</sub> rising edges clock out the remaining seven bits. The D<sub>X</sub> output is disabled by the falling  $\operatorname{BCLK}_X$  edge following the eighth rising edge, or by FS<sub>x</sub> going low, whichever comes later. A rising edge on the receive frame sync pulse, FS<sub>R</sub>, will cause the PCM data at D<sub>B</sub> to be latched in on the next eight falling edges of BCLK<sub>B</sub> (BCLK<sub>x</sub> in synchronous mode). All four devices may utilize the long frame sync pulse in synchronous or asynchronous

In applications where the LSB bit is used for signalling, with  $FS_R$  two bit clock periods long, the decoder will interpret the lost LSB as "1/2" to minimize noise and distortion.

#### TRANSMIT SECTION

The transmit section input is an operational amplifier with provision for gain adjustment using two external resistors, see *Figure 4*. The low noise and wide bandwidth allow gains in excess of 20 dB across the audio passband to be realized. The op amp drives a unity-gain filter consisting of RC active

pre-filter, followed by an eighth order switched-capacitor bandpass filter clocked at 256 kHz. The output of this filter directly drives the encoder sample-and-hold circuit. The A/D is of companding type according to  $\mu$ -law (TP3054) or A-law (TP3057) coding conventions. A precision voltage reference is trimmed in manufacturing to provide an input overload (t\_MAX) of nominally 2.5V peak (see table of Transmission Characteristics). The FS\_x frame sync pulse controls the sampling of the filter output, and then the successive-approximation encoding cycle begins. The 8-bit code is then loaded into a buffer and shifted out through  $D_X$  at the next FS\_x pulse. The total encoding delay will be approximately 165  $\mu$ s (due to the transmit filter) plus 125  $\mu$ s (due to encoding delay), which totals 290  $\mu$ s. Any offset voltage due to the filters or comparator is cancelled by sign bit integration.

#### **RECEIVE SECTION**

The receive section consists of an expanding DAC which drives a fifth order switched-capacitor low pass filter clocked at 256 kHz. The decoder is A-law (TP3057) or  $\mu$ -law (TP3054) and the 5th order low pass filter corrects for the sin x/x attenuation due to the 8 kHz sample/hold. The filter is then followed by a 2nd order RC active post-filter/power amplifier capable of driving a  $600\Omega$  load to a level of 7.2 dBm. The receive section is unity-gain. Upon the occurrence of FS $_{\rm R}$ , the data at the D $_{\rm R}$  input is clocked in on the falling edge of the next eight BCLK $_{\rm R}$  (BCLK $_{\rm X}$ ) periods. At the end of the decoder time slot, the decoding cycle begins, and 10  $\mu$ s later the decoder DAC output is updated. The total decoder delay is ~10  $\mu$ s (decoder update) plus 110  $\mu$ s (filter delay) plus 62.5  $\mu$ s (½ frame), which gives approximately 180  $\mu$ s.

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$V_{CC}$  to GNDA 7V  $V_{BB}$  to GNDA -7V

Voltage at any Analog Input

or Output  $V_{CC}$ +0.3V to  $V_{BB}$ -0.3V

Voltage at any Digital Input or

Output  $V_{CC}$ +0.3V to GNDA-0.3V Operating Temperature Range  $-55^{\circ}$ C to + 125 $^{\circ}$ C Storage Temperature Range  $-65^{\circ}$ C to +150 $^{\circ}$ C Lead Temperature

(Soldering, 10 sec.) 300°C

## **Electrical Characteristics**

Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{CC} = +5.0V \pm 5\%$ ,  $V_{BB} = -5.0V \pm 5\%$ ;  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  by correlation with 100% electrical testing at  $T_A = 25^{\circ}\text{C}$ . All other limits are assured by correlation with other production tests and/or product design and characterization. All signals referenced to GNDA. Typicals specified at  $V_{CC} = +5.0V$ ,  $V_{BB} = -5.0V$ ,  $T_A = 25^{\circ}\text{C}$ .

| Symbol             | Parameter                        | Conditions                                                                      | Min  | Тур  | Max  | Units |

|--------------------|----------------------------------|---------------------------------------------------------------------------------|------|------|------|-------|

| DIGITAL I          | NTERFACE                         |                                                                                 |      |      |      |       |

| $V_{IL}$           | Input Low Voltage                |                                                                                 |      |      | 0.6  | V     |

| $V_{IH}$           | Input High Voltage               |                                                                                 | 2.2  |      |      | V     |

| $V_{OL}$           | Output Low Voltage               | D <sub>X</sub> , I <sub>L</sub> =3.2 mA                                         |      |      | 0.4  | V     |

|                    |                                  | SIG <sub>R</sub> , I <sub>L</sub> =1.0 mA                                       |      |      | 0.4  | V     |

|                    |                                  | $\overline{TS_{X}}$ , I <sub>L</sub> =3.2 mA, Open Drain                        |      |      | 0.4  | V     |

| $V_{OH}$           | Output High Voltage              | $D_X$ , $I_H$ =-3.2 mA                                                          | 2.4  |      |      | V     |

|                    |                                  | SIG <sub>R</sub> , I <sub>H</sub> =-1.0 mA                                      | 2.4  |      |      | V     |

| $I_{IL}$           | Input Low Current                | GNDA≤V <sub>IN</sub> ≤V <sub>IL</sub> , All Digital Inputs                      | -10  |      | 10   | μΑ    |

| I <sub>IH</sub>    | Input High Current               | $V_{IH} \leq V_{IN} \leq V_{CC}$                                                | -10  |      | 10   | μΑ    |

| l <sub>oz</sub>    | Output Current in High Impedance | D <sub>X</sub> , GNDA≤V <sub>O</sub> ≤V <sub>CC</sub>                           | -10  |      | 10   | μΑ    |

|                    | State (TRI-STATE)                |                                                                                 |      |      |      |       |

| ANALOG             | INTERFACE WITH TRANSMIT INPUT    | AMPLIFIER (ALL DEVICES)                                                         |      | •    | •    |       |

| I <sub>I</sub> XA  | Input Leakage Current            | –2.5V≤V≤+2.5V, VF <sub>X</sub> I <sup>+</sup> or VF <sub>X</sub> I <sup>-</sup> | -200 |      | 200  | nA    |

| R <sub>I</sub> XA  | Input Resistance                 | –2.5V≤V≤+2.5V, VF <sub>X</sub> I <sup>+</sup> or VF <sub>X</sub> I <sup>-</sup> | 10   |      |      | MΩ    |

| R <sub>O</sub> XA  | Output Resistance                | Closed Loop, Unity Gain                                                         |      | 1    | 3    | Ω     |

| R <sub>L</sub> XA  | Load Resistance                  | GS <sub>X</sub>                                                                 | 10   |      |      | kΩ    |

| $C_LXA$            | Load Capacitance                 | GS <sub>X</sub>                                                                 |      |      | 50   | pF    |

| $V_OXA$            | Output Dynamic Range             | $GS_X$ , $R_L \ge 10 \text{ k}\Omega$                                           | -2.8 |      | 2.8  | V     |

| $A_VXA$            | Voltage Gain                     | VF <sub>X</sub> I <sup>+</sup> to GS <sub>X</sub>                               | 5000 |      |      | V/V   |

| $F_UXA$            | Unity Gain Bandwidth             |                                                                                 | 1    | 2    |      | MHz   |

| $V_{OS}XA$         | Offset Voltage                   |                                                                                 | -20  |      | 20   | mV    |

| $V_{CM}XA$         | Common-Mode Voltage              | CMRRXA > 60 dB                                                                  | -2.5 |      | 2.5  | V     |

| CMRRXA             | Common-Mode Rejection Ratio      | DC Test                                                                         | 60   |      |      | dB    |

| PSRRXA             | Power Supply Rejection Ratio     | DC Test                                                                         | 60   |      |      | dB    |

| ANALOG             | INTERFACE WITH RECEIVE FILTER    | (ALL DEVICES)                                                                   |      |      |      |       |

| RoRF               | Output Resistance                | Pin VF <sub>R</sub> O                                                           |      | 1    | 3    | Ω     |

| $R_LRF$            | Load Resistance                  | VF <sub>R</sub> O=±2.5V                                                         | 600  |      |      | Ω     |

| $C_LRF$            | Load Capacitance                 |                                                                                 |      |      | 500  | pF    |

| VOS <sub>R</sub> O | Output DC Offset Voltage         |                                                                                 | -200 |      | 200  | mV    |

| POWER D            | ISSIPATION (ALL DEVICES)         |                                                                                 |      |      |      |       |

| I <sub>CC</sub> 0  | Power-Down Current               | No Load (Note 2)                                                                |      | 0.65 | 2.0  | mA    |

| I <sub>BB</sub> 0  | Power-Down Current               | No Load (Note 2)                                                                |      | 0.01 | 0.33 | mA    |

| I <sub>CC</sub> 1  | Power-Up (Active) Current        | No Load( -40°C to 85°C)                                                         |      | 5.0  | 11.0 | mA    |

| I <sub>BB</sub> 1  | Power-Up (Active) Current        | No Load ( -40°C to 85°C)                                                        |      | 5.0  | 11.0 | mA    |

|                    | <del>-</del>                     |                                                                                 |      |      |      |       |

Note 1: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits.

Note 2:  $I_{CC0}$  and  $I_{BB0}$  are measured after first achieving a power-up state.

# **Timing Specifications**

Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{CC}$  = +5.0V ±5%,  $V_{BB}$  = -5.0V ±5%;  $T_A$  = -40°C to +85°C by correlation with 100% electrical testing at  $T_A$  = 25°C. All other limits are assured by correlation with other production tests and/or product design and characterization. All signals referenced to GNDA. Typicals specified at  $V_{CC}$  = +5.0V,  $V_{BB}$  = -5.0V,  $T_A$  = 25°C. All timing parameters are assured at  $V_{OH}$  = 2.0V and  $V_{OL}$  = 0.7V. See Definitions and Timing Conventions section for test methods information.

| Symbol            | Parameter                                                                                  | Conditions                                                 | Min | Тур   | Max   | Units |

|-------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------|-----|-------|-------|-------|

| 1/t <sub>PM</sub> | Frequency of Master Clocks                                                                 | Depends on the Device Used and the                         |     | 1.536 |       | MHz   |

|                   |                                                                                            | BCLK <sub>R</sub> /CLKSEL Pin.                             |     | 1.544 |       | MHz   |

|                   |                                                                                            | MCLK <sub>X</sub> and MCLK <sub>R</sub>                    |     | 2.048 |       | MHz   |

| t <sub>RM</sub>   | Rise Time of Master Clock                                                                  | MCLK <sub>X</sub> and MCLK <sub>R</sub>                    |     |       | 50    | ns    |

| $t_{\sf FM}$      | Fall Time of Master Clock                                                                  | MCLK <sub>X</sub> and MCLK <sub>R</sub>                    |     |       | 50    | ns    |

| t <sub>PB</sub>   | Period of Bit Clock                                                                        |                                                            | 485 | 488   | 15725 | ns    |

| t <sub>RB</sub>   | Rise Time of Bit Clock                                                                     | BCLK <sub>X</sub> and BCLK <sub>R</sub>                    |     |       | 50    | ns    |

| t <sub>FB</sub>   | Fall Time of Bit Clock                                                                     | BCLK <sub>X</sub> and BCLK <sub>R</sub>                    |     |       | 50    | ns    |

| t <sub>WMH</sub>  | Width of Master Clock High                                                                 | MCLK <sub>X</sub> and MCLK <sub>R</sub>                    | 160 |       |       | ns    |

| t <sub>WML</sub>  | Width of Master Clock Low                                                                  | MCLK <sub>X</sub> and MCLK <sub>R</sub>                    | 160 |       |       | ns    |

| t <sub>SBFM</sub> | Set-Up Time from BCLK <sub>X</sub> High                                                    | First Bit Clock after Short Frame                          | 100 |       |       | ns    |

|                   | to MCLK <sub>x</sub> Falling Edge                                                          | the Leading Edge                                           |     |       |       |       |

|                   |                                                                                            | of FS <sub>X</sub> Long Frame                              | 125 |       |       |       |

| t <sub>SFFM</sub> | Setup Time from FS <sub>X</sub> High to MCLK <sub>X</sub> Falling Edge                     | Long Frame Only                                            | 100 |       |       | ns    |

| t <sub>WBH</sub>  | Width of Bit Clock High                                                                    | V <sub>IH</sub> =2.2V                                      | 160 |       |       | ns    |

| t <sub>WBL</sub>  | Width of Bit Clock Low                                                                     | V <sub>IL</sub> =0.6V                                      | 160 |       |       | ns    |

| t <sub>HBFL</sub> | Holding Time from Bit Clock Low to Frame Sync                                              | Long Frame Only                                            | 0   |       |       | ns    |

| t <sub>HBFS</sub> | Holding Time from Bit Clock                                                                | Short Frame Only                                           | 0   |       |       | ns    |

|                   | High to Frame Sync                                                                         |                                                            |     |       |       |       |

| t <sub>SFB</sub>  | Set-Up Time from Frame Sync to Bit Clock Low                                               | Long Frame Only                                            | 115 |       |       | ns    |

| t <sub>DBD</sub>  | Delay Time from BCLK <sub>X</sub> High                                                     | Load=150 pF plus 2 LSTTL Loads                             | 0   |       | 140   | ns    |

|                   | to Data Valid                                                                              | Lood 150 pF phio 0 LCTTL Loods                             | -   |       | 140   |       |

| t <sub>DBTS</sub> | Delay Time to $\overline{TS_X}$ Low                                                        | Load=150 pF plus 2 LSTTL Loads                             |     |       | 140   | ns    |

| t <sub>DZC</sub>  | Delay Time from BCLK <sub>X</sub> Low to Data Output Disabled                              | C <sub>L</sub> =0 pF to 150 pF                             | 50  |       | 165   | ns    |

| t <sub>DZF</sub>  | Delay Time to Valid Data from FS <sub>X</sub> or BCLK <sub>X</sub> , Whichever Comes Later | C <sub>L</sub> =0 pF to 150 pF                             | 20  |       | 165   | ns    |

| t <sub>SDB</sub>  | Set-Up Time from D <sub>R</sub> Valid to BCLK <sub>R/X</sub> Low                           |                                                            | 50  |       |       | ns    |

| t <sub>HBD</sub>  | Hold Time from BCLK <sub>R/X</sub> Low to                                                  |                                                            | 50  |       |       | ns    |

| t <sub>SF</sub>   | D <sub>R</sub> Invalid  Set-Up Time from FS <sub>x/R</sub> to                              | Short Frame Sync Pulse (1 Bit Clock                        | 50  |       |       | ns    |

| 51                | BCLK <sub>X/R</sub> Low                                                                    | Period Long)                                               |     |       |       |       |

| t <sub>HF</sub>   | Hold Time from BCLK <sub>X/R</sub> Low                                                     | Short Frame Sync Pulse (1 Bit Clock                        | 100 |       |       | ns    |

|                   | to FS <sub>X/R</sub> Low                                                                   | Period Long)                                               |     |       |       |       |

| t <sub>HBFI</sub> | Hold Time from 3rd Period of Bit Clock Low to Frame Sync                                   | Long Frame Sync Pulse (from 3 to 8 Bit Clock Periods Long) | 100 |       |       | ns    |

|                   | (FS <sub>X</sub> or FS <sub>R</sub> )                                                      | 5,                                                         |     |       |       |       |

| t <sub>WFL</sub>  | Minimum Width of the Frame                                                                 | 64k Bit/s Operating Mode                                   | 160 |       |       | ns    |

|                   | Sync Pulse (Low Level)                                                                     |                                                            |     |       |       |       |

## **Transmission Characteristics**

Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{CC}$  = +5.0V ±5%,  $V_{BB}$  = -5.0V ±5%;  $T_A$  = -40°C to +85°C by correlation with 100% electrical testing at  $T_A$  = 25°C. All other limits are assured by correlation with other production tests and/or product design and characterization. GNDA = 0V, f = 1.02 kHz,  $V_{IN}$  = 0 dBm0, transmit input amplifier connected for unity gain non inverting. Typicals are specified at  $V_{CC}$  = +5.0V,  $V_{BB}$  = -5.0V,  $V_{AB}$  = 25°C.

| Symbol           | Parameter                                        | Conditions                                                      | Min   | Тур    | Max  | Units           |

|------------------|--------------------------------------------------|-----------------------------------------------------------------|-------|--------|------|-----------------|

| AMPLITU          | IDE RESPONSE                                     |                                                                 |       |        |      |                 |

|                  | Absolute Levels                                  | Nominal 0 dBm0 Level is 4 dBm                                   |       |        |      |                 |

|                  | (Definition of nominal gain)                     | (600Ω)                                                          |       |        |      |                 |

|                  |                                                  | 0 dBm0                                                          |       | 1.2276 |      | Vrms            |

| t <sub>MAX</sub> |                                                  | Max Overload Level                                              |       |        |      |                 |

|                  |                                                  | TP3054 (3.17 dBm0)                                              |       | 2.501  |      | V <sub>PK</sub> |

|                  |                                                  | TP3057 (3.14 dBm0)                                              |       | 2.492  |      | V <sub>PK</sub> |

| G <sub>XA</sub>  | Transmit Gain, Absolute                          | T <sub>A</sub> =25°C, V <sub>CC</sub> =5V, V <sub>BB</sub> =-5V |       |        |      |                 |

|                  |                                                  | Input at GS <sub>x</sub> =0 dBm0 at 1020 Hz                     | -0.15 |        | 0.15 | dB              |

| G <sub>XR</sub>  | Transmit Gain, Relative to G <sub>XA</sub>       | f=16 Hz                                                         |       |        | -40  | dB              |

|                  |                                                  | f=50 Hz                                                         |       |        | -30  | dB              |

|                  |                                                  | f=60 Hz                                                         |       |        | -26  | dB              |

|                  |                                                  | f=200 Hz                                                        | -1.8  |        | -0.1 | dB              |

|                  |                                                  | f=300 Hz-3000 Hz                                                | -0.15 |        | 0.15 | dB              |

|                  |                                                  | f=3152 Hz                                                       | -0.15 |        | 0.20 | dB              |

|                  |                                                  | f=3300 Hz                                                       | -0.35 |        | 0.1  | dB              |

|                  |                                                  | f=3400 Hz                                                       | -0.7  |        | 0    | dB              |

|                  |                                                  | f=4000 Hz                                                       |       |        | -14  | dB              |

|                  |                                                  | f=4600 Hz and Up, Measure                                       |       |        | -32  | dB              |

|                  |                                                  | Response from 0 Hz to 4000 Hz                                   |       |        |      |                 |

| G <sub>XAT</sub> | Absolute Transmit Gain Variation                 | Relative to G <sub>XA</sub>                                     | -0.15 |        | 0.15 | dB              |

|                  | with Temperature                                 |                                                                 |       |        |      |                 |

| G <sub>XAV</sub> | Absolute Transmit Gain Variation                 | Relative to G <sub>XA</sub>                                     | -0.05 |        | 0.05 | dB              |

|                  | with Supply Voltage                              |                                                                 |       |        |      |                 |

| G <sub>XRL</sub> | Transmit Gain Variations with                    | Sinusoidal Test Method                                          |       |        |      |                 |

|                  | Level                                            | Reference Level=-10 dBm0                                        |       |        |      |                 |

|                  |                                                  | $VF_XI^+=-40$ dBm0 to +3 dBm0                                   | -0.2  |        | 0.2  | dB              |

|                  |                                                  | $VF_XI^+=-50$ dBm0 to $-40$ dBm0                                | -0.4  |        | 0.4  | dB              |

|                  |                                                  | $VF_XI^+=-55$ dBm0 to $-50$ dBm0                                | -1.2  |        | 1.2  | dB              |

| G <sub>RA</sub>  | Receive Gain, Absolute                           | $T_A = 25$ °C, $V_{CC} = 5V$ , $V_{BB} = -5V$                   |       |        |      |                 |

|                  |                                                  | Input=Digital Code Sequence                                     |       |        |      |                 |

|                  |                                                  | for 0 dBm0 Signal at 1020 Hz                                    | -0.20 |        | 0.20 | dB              |

| $G_{RR}$         | Receive Gain, Relative to G <sub>RA</sub>        | f=0 Hz to 3000 Hz                                               | -0.15 |        | 0.15 | dB              |

|                  |                                                  | f=3300 Hz                                                       | -0.35 |        | 0.1  | dB              |

|                  |                                                  | f=3400 Hz                                                       | -0.7  |        | 0    | dB              |

|                  |                                                  | f=4000 Hz                                                       |       |        | -14  | dB              |

| G <sub>RAT</sub> | Absolute Receive Gain Variation with Temperature | Relative to G <sub>RA</sub>                                     | -0.15 |        | 0.15 | dB              |

| G <sub>RAV</sub> | Absolute Receive Gain Variation                  | Relative to G <sub>BA</sub>                                     | -0.05 |        | 0.05 | dB              |

| FIAV             | with Supply Voltage                              | · · · · · · · · · · · · · · · · · · ·                           |       |        |      |                 |

| G <sub>RRL</sub> | Receive Gain Variations with                     | Sinusoidal Test Method; Reference                               |       |        |      |                 |

|                  | Level                                            | Input PCM Code Corresponds to an                                |       |        |      |                 |

|                  |                                                  | Ideally Encoded                                                 |       |        |      |                 |

|                  |                                                  | PCM Level =–40 dBm0 to +3 dBm0                                  | -0.2  |        | 0.2  | dB              |

|                  |                                                  | PCM Level =-50 dBm0 to -40 dBm0                                 | -0.4  |        | 0.4  | dB              |

|                  |                                                  | PCM Level = -55 dBm0 to -50 dBm0                                | -1.2  |        | 1.2  | dB              |

|                  | I                                                | , , , , , , , , , , , , , , , , , , ,                           |       | I      |      |                 |

## **Transmission Characteristics** (Continued)

Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{CC}$  = +5.0V ±5%,  $V_{BB}$  = -5.0V ±5%;  $T_A$  = -40°C to +85°C by correlation with 100% electrical testing at  $T_A$  = 25°C. All other limits are assured by correlation with other production tests and/or product design and characterization. GNDA = 0V, f = 1.02 kHz,  $V_{IN}$  = 0 dBm0, transmit input amplifier connected for unity gain non inverting. Typicals are specified at  $V_{CC}$  = +5.0V,  $V_{BB}$  = -5.0V,  $V_{AB}$  = 25°C.

| Symbol            | Parameter                                   | Conditions                                          | Min  | Тур      | Max | Units  |

|-------------------|---------------------------------------------|-----------------------------------------------------|------|----------|-----|--------|

| AMPLITU           | JDE RESPONSE                                |                                                     |      |          |     |        |

| V <sub>RO</sub>   | Receive Output Drive Level                  | $R_L$ =600 $\Omega$                                 | -2.5 |          | 2.5 | V      |

| ENVELO            | PE DELAY DISTORTION WITH FREC               | QUENCY                                              |      |          |     |        |

| $D_XA$            | Transmit Delay, Absolute                    | f=1600 Hz                                           |      | 290      | 315 | μs     |

| $D_XR$            | Transmit Delay, Relative to D <sub>XA</sub> | f=500 Hz-600 Hz                                     |      | 195      | 220 | μs     |

|                   |                                             | f=600 Hz-800 Hz                                     |      | 120      | 145 | μs     |

|                   |                                             | f=800 Hz-1000 Hz                                    |      | 50       | 75  | μs     |

|                   |                                             | f=1000 Hz-1600 Hz                                   |      | 20       | 40  | μs     |

|                   |                                             | f=1600 Hz-2600 Hz                                   |      | 55       | 75  | μs     |

|                   |                                             | f=2600 Hz-2800 Hz                                   |      | 80       | 105 | μs     |

|                   |                                             | f=2800 Hz-3000 Hz                                   |      | 130      | 155 | μs     |

| D <sub>RA</sub>   | Receive Delay, Absolute                     | f=1600 Hz                                           |      | 180      | 200 | μs     |

| D <sub>RR</sub>   | Receive Delay, Relative to D <sub>RA</sub>  | f=500 Hz-1000 Hz                                    | -40  | -25      |     | μs     |

|                   |                                             | f=1000 Hz-1600 Hz                                   | -30  | -20      |     | μs     |

|                   |                                             | f=1600 Hz-2600 Hz                                   |      | 70       | 90  | μs     |

|                   |                                             | f=2600 Hz-2800 Hz                                   |      | 100      | 125 | μs     |

|                   |                                             | f=2800 Hz-3000 Hz                                   |      | 145      | 175 | μs     |

| NOISE             |                                             |                                                     |      | 1        | 1   | 1      |

| N <sub>XC</sub>   | Transmit Noise, C Message                   | TP3054                                              |      | 12       | 16  | dBrnC0 |

|                   | Weighted                                    | (Note 3)                                            |      |          |     |        |

| N <sub>XP</sub>   | Transmit Noise, P Message                   | TP3057                                              |      | -74      | -67 | dBm0p  |

|                   | Weighted                                    | (Note 3)                                            |      |          |     |        |

| N <sub>RC</sub>   | Receive Noise, C Message                    | PCM Code is Alternating                             |      |          |     |        |

|                   | Weighted                                    | Positive and Negative Zero — TP3054                 |      | 8        | 11  | dBrnC0 |

| N <sub>RP</sub>   | Receive Noise, P Message                    | TP3057 PCM Code Equals Positive                     |      |          |     |        |

|                   | Weighted                                    | Zero —                                              |      | -82      | -79 | dBm0p  |

| N <sub>RS</sub>   | Noise, Single Frequency                     | f=0 kHz to 100 kHz, Loop Around                     |      |          | -53 | dBm0   |

|                   |                                             | Measurement, VF <sub>X</sub> I <sup>+</sup> =0 Vrms |      |          |     |        |

| PPSR <sub>X</sub> | Positive Power Supply Rejection,            | V <sub>CC</sub> =5.0 V <sub>DC</sub> +100 mVrms     |      |          |     |        |

|                   | Transmit                                    | f=0 kHz-50 kHz (Note 4)                             | 40   |          |     | dBC    |

| NPSR <sub>X</sub> | Negative Power Supply Rejection,            | V <sub>BB</sub> =-5.0 V <sub>DC</sub> + 100 mVrms   |      |          |     |        |

|                   | Transmit                                    | f=0 kHz-50 kHz (Note 4)                             | 40   |          |     | dBC    |

| PPSR <sub>R</sub> | Positive Power Supply Rejection,            | PCM Code Equals Positive Zero                       |      |          |     |        |

|                   | Receive                                     | $V_{CC}$ =5.0 $V_{DC}$ +100 mVrms                   |      |          |     |        |

|                   |                                             | Measure VF <sub>B</sub> 0                           |      |          |     |        |

|                   |                                             | f=0 Hz-4000 Hz                                      | 38   |          |     | dBC    |

|                   |                                             | f=4 kHz-25 kHz                                      | 38   |          |     | dB     |

|                   |                                             | f=25 kHz-50 kHz                                     | 35   |          |     | dB     |

| NPSR <sub>B</sub> | Negative Power Supply Rejection,            | PCM Code Equals Positive Zero                       |      |          |     |        |

|                   | Receive                                     | $V_{BB}$ =-5.0 $V_{DC}$ +100 mVrms                  |      |          |     |        |

|                   |                                             | Measure VF <sub>B</sub> 0                           |      |          |     |        |

|                   |                                             | f=0 Hz-4000 Hz                                      | 38   |          |     | dBC    |

|                   |                                             | f=4 kHz-25 kHz                                      | 38   |          |     | dB     |

|                   |                                             | f=25 kHz-50 kHz                                     | 35   |          |     | dB     |

|                   |                                             | . 10 10 12 00 10 12                                 |      | <u> </u> |     | 45     |

## **Transmission Characteristics** (Continued)

Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{CC}$  = +5.0V ±5%,  $V_{BB}$  = -5.0V ±5%;  $T_A$  = -40°C to +85°C by correlation with 100% electrical testing at  $T_A$  = 25°C. All other limits are assured by correlation with other production tests and/or product design and characterization. GNDA = 0V, f = 1.02 kHz,  $V_{IN}$  = 0 dBm0, transmit input amplifier connected for unity gain non inverting. Typicals are specified at  $V_{CC}$  = +5.0V,  $V_{BB}$  = -5.0V,  $T_A$  = 25°C.

| Symbol            | Parameter                      | Conditions                               |       | Min | Тур | Max | Units |

|-------------------|--------------------------------|------------------------------------------|-------|-----|-----|-----|-------|

| NOISE             |                                |                                          |       |     | •   | •   | •     |

| SOS               | Spurious Out-of-Band Signals   | Loop Around Measurement, 0               | dBm0, |     |     | -30 | dB    |

|                   | at the Channel Output          | 300 Hz to 3400 Hz Input PCM              | Code  |     |     |     |       |

|                   |                                | Applied at D <sub>R</sub> .              |       |     |     |     |       |

|                   |                                | 4600 Hz-7600 Hz                          |       |     |     | -30 | dB    |

|                   |                                | 7600 Hz-8400 Hz                          |       |     |     | -40 | dB    |

|                   |                                | 8400 Hz-100,000 Hz                       |       |     |     | -30 | dB    |

| DISTORT           | TON                            |                                          |       |     |     | •   |       |

| STD <sub>X,</sub> | Signal to Total Distortion     | Sinusoidal Test Method (Note             | 6)    |     |     |     |       |

| $STD_R$           | Transmit or Receive            | Level=3.0 dBm0                           |       | 33  |     |     | dBC   |

|                   | Half-Channel                   | =0 dBm0 to -30 dBm0                      |       | 36  |     |     | dBC   |

|                   |                                | =-40 dBm0                                | XMT   | 28  |     |     | dBC   |

|                   |                                |                                          | RCV   | 29  |     |     | dBC   |

|                   |                                | =-55 dBm0                                | XMT   | 13  |     |     | dBC   |

|                   |                                |                                          | RCV   | 14  |     |     | dBC   |

| $SFD_X$           | Single Frequency Distortion,   |                                          |       |     |     | -43 | dB    |

|                   | Transmit                       |                                          |       |     |     |     |       |

| $SFD_R$           | Single Frequency Distortion,   |                                          |       |     |     | -43 | dB    |

|                   | Receive                        |                                          |       |     |     |     |       |

| IMD               | Intermodulation Distortion     | Loop Around Measurement,                 |       |     |     | -41 | dB    |

|                   |                                | $VF_XI^+=-4$ dBm0 to -21 dBm0,           | Two   |     |     |     |       |

|                   |                                | Frequencies in the Range                 |       |     |     |     |       |

|                   |                                | 300 Hz-3400 Hz                           |       |     |     |     |       |

| CROSST            | ALK                            |                                          |       |     |     |     |       |

| CT <sub>X-R</sub> | Transmit to Receive Crosstalk, | f=300 Hz-3400 Hz                         |       |     | -90 | -70 | dB    |

|                   | 0 dBm0 Transmit Level          | D <sub>R</sub> =Quiet PCM Code (Note 6)  |       |     |     |     |       |

| CT <sub>R-X</sub> | Receive to Transmit Crosstalk, | f=300 Hz-3400 Hz, VF <sub>X</sub> I=Mult | itone |     | -90 | -70 | dB    |

|                   | 0 dBm0 Receive Level           | (Note 4)                                 |       |     |     |     |       |

## **ENCODING FORMAT AT D<sub>x</sub> OUTPUT**

|                                                   | TP3054 |   |   |   |   |      |       |      |         | TP3   | 057  |   |   |   |   |   |

|---------------------------------------------------|--------|---|---|---|---|------|-------|------|---------|-------|------|---|---|---|---|---|

|                                                   | μ-Law  |   |   |   |   |      |       |      |         | A-l   | _aw  |   |   |   |   |   |

|                                                   |        |   |   |   |   | (Inc | ludes | Ever | n Bit I | nvers | ion) |   |   |   |   |   |

| V <sub>IN</sub> (at GS <sub>x</sub> )=+Full-Scale | 1      | 0 | 0 | 0 | 0 | 0    | 0     | 0    | 1       | 0     | 1    | 0 | 1 | 0 | 1 | 0 |

| V <sub>IN</sub> (at GS <sub>x</sub> )=0V          | 1      | 1 | 1 | 1 | 1 | 1    | 1     | 1    | 1       | 1     | 0    | 1 | 0 | 1 | 0 | 1 |

|                                                   | 0      | 1 | 1 | 1 | 1 | 1    | 1     | 1    | 0       | 1     | 0    | 1 | 0 | 1 | 0 | 1 |

| V <sub>IN</sub> (at GS <sub>X</sub> )=-Full-Scale | 0      | 0 | 0 | 0 | 0 | 0    | 0     | 0    | 0       | 0     | 1    | 0 | 1 | 0 | 1 | 0 |

Note 3: Measured by extrapolation from the distortion test result at -50 dBm0.

Note 4:  $PPSR_X$ ,  $NPSR_X$ , and  $CT_{R-X}$  are measured with a -50 dBm0 activation signal applied to  $VF_XI^+$ .

Note 5: TP3054/57 are measured using C message weighted filter for μ-law and psophometric weighted filter for A-law.

Note 6: CT<sub>X-R</sub> @ 1.544 MHz MCLK<sub>X</sub> freq. is -70 dB max. 50%  $\pm 5\%$  BCLK<sub>X</sub> duty cycle.

## **Applications Information**

#### **POWER SUPPLIES**

While the pins of the TP3050 family are well protected against electrical misuse, it is recommended that the standard CMOS practice be followed, ensuring that ground is connected to the device before any other connections are made. In applications where the printed circuit board may be plugged into a "hot" socket with power and clocks already present, an extra long ground pin in the connector should be used.

All ground connections to each device should meet at a common point as close as possible to the GNDA pin. This minimizes the interaction of ground return currents flowing through a common bus impedance. 0.1  $\mu\text{F}$  supply decoupling capacitors should be connected from this common ground point to  $V_{\text{CC}}$  and  $V_{\text{BB}},$  as close to device pins as possible.

For best performance, the ground point of each CODEC/FILTER on a card should be connected to a common card ground in star formation, rather than via a ground bus.

This common ground point should be decoupled to  $V_{\rm CC}$  and  $V_{\rm BB}$  with 10  $\mu F$  capacitors.

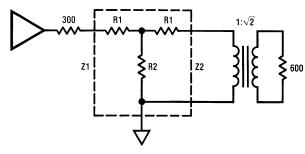

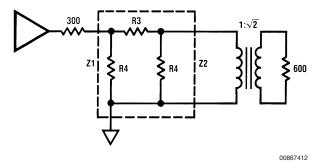

#### **RECEIVE GAIN ADJUSTMENT**

For applications where a TP3050 family CODEC/filter receive output must drive a  $600\Omega$  load, but a peak swing lower than  $\pm 2.5V$  is required, the receive gain can be easily adjusted by inserting a matched T-pad or  $\pi$ -pad at the output. Table 2 lists the required resistor values for  $600\Omega$  terminations. As these are generally non-standard values, the equations can be used to compute the attenuation of the closest practical set of resistors. It may be necessary to use unequal values for the R1 or R4 arms of the attenuators to achieve a precise attenuation. Generally it is tolerable to allow a small deviation of the input impedance from nominal while still maintaining a good return loss. For example a 30 dB return loss against  $600\Omega$  is obtained if the output impedance of the attenuator is in the range  $282\Omega$  to  $319\Omega$  (assuming a perfect transformer).

#### **T-Pad Attenuator**

00867411

$$\begin{split} \text{R1} &= \text{Z1}\bigg(\frac{N^2+1}{N^2-1}\bigg) - 2\sqrt{\text{Z1}.\text{Z2}}\,\bigg(\frac{N}{N^2-1}\bigg) \\ \text{R2} &= 2\sqrt{\text{Z1}.\text{Z2}}\,\bigg(\frac{N}{N^2-1}\bigg) \\ \text{Where: N} &= \sqrt{\frac{\text{POWER IN}}{\text{POWER OUT}}} \\ \text{and} \\ \text{S} &= \sqrt{\frac{\text{Z1}}{\text{Z2}}} \end{split}$$

Also:  $Z = \sqrt{Z_{SC} \cdot Z_{OC}}$

Where  $Z_{SC}$  = impedance with short circuit termination and  $Z_{OC}$  = impedance with open circuit termination

# Applications Information (Continued)

$\pi$ -Pad Attenuator

Note: See Application Note 370 for further details.

$$R3 = \sqrt{\frac{Z1.Z2}{2}} \left( \frac{N^2 - 1}{N} \right)$$

$$R3 = Z1 \left( \frac{N^2 - 1}{N^2 - 2NS + 1} \right)$$

TABLE 2. Attentuator Tables for Z1=Z2=300 $\Omega$  (All Values in  $\Omega$ )

| dB  | R1   | R2   | R3    | R4    |

|-----|------|------|-------|-------|

| 0.1 | 1.7  | 26k  | 3.5   | 52k   |

| 0.2 | 3.5  | 13k  | 6.9   | 26k   |

| 0.3 | 5.2  | 8.7k | 10.4  | 17.4k |

| 0.4 | 6.9  | 6.5k | 13.8  | 13k   |

| 0.5 | 8.5  | 5.2k | 17.3  | 10.5k |

| 0.6 | 10.4 | 4.4k | 21.3  | 8.7k  |

| 0.7 | 12.1 | 3.7k | 24.2  | 7.5k  |

| 0.8 | 13.8 | 3.3k | 27.7  | 6.5k  |

| 0.9 | 15.5 | 2.9k | 31.1  | 5.8k  |

| 1.0 | 17.3 | 2.61 | 34.6  | 5.2k  |

| 2   | 34.4 | 1.3k | 70    | 2.6k  |

| 3   | 51.3 | 850  | 107   | 1.8k  |

| 4   | 68   | 650  | 144   | 1.3k  |

| 5   | 84   | 494  | 183   | 1.1k  |

| 6   | 100  | 402  | 224   | 900   |

| 7   | 115  | 380  | 269   | 785   |

| 8   | 379  | 284  | 317   | 698   |

| 9   | 143  | 244  | 370   | 630   |

| 10  | 156  | 211  | 427   | 527   |

| 11  | 168  | 184  | 490   | 535   |

| 12  | 180  | 161  | 550   | 500   |

| 13  | 190  | 142  | 635   | 473   |

| 14  | 200  | 125  | 720   | 450   |

| 15  | 210  | 110  | 816   | 430   |

| 16  | 218  | 98   | 924   | 413   |

| 18  | 233  | 77   | 1.17k | 386   |

| 20  | 246  | 61   | 1.5k  | 366   |

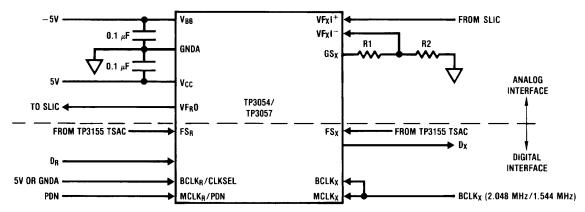

# **Typical Synchronous Application**

0086740

Note 1: XMIT gain = 20

$$\times$$

log  $\left(\frac{R1+R2}{R2}\right)$  ,(R1+R2)  $>$  10 K $\Omega$ .

FIGURE 4.

## Physical Dimensions inches (millimeters)

unless otherwise noted

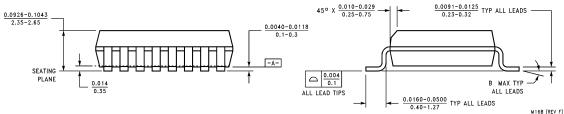

Dual-In-Line Package (M) Order Number TP3054WM-X NS Package Number M16B

Molded Dual-In-Line Package (N) Order Number TP3054N-X NS Package Number N16E

## Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

Cavity Dual-In-Line Package (V) Order Number TP3057V-X NS Package Number V20A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560