Document Number: 71110

S-00025-Rev. A, 24-Jan-00

**APPLICATIONS**

# **Power Selector Switch**

## **FEATURES**

- MOSFETs Configured To Give Spdt Switch With One Control Input

- 2.5- to 8-V Ground Referenced Control Input

- 30-mΩ Main Switch On-Resistance

- 70-mΩ Alternate Switch On-Resistance •

- SOIC-8 Package

DESCRIPTION

- 3000-V ESD Protection On Control Input

- Zero Power Consumption In Alternate Power Mode

- ACPI Power Switching In Desktop Computers

The Si4700DY consists of two MOSFETs configured for use as a single-pole, double-throw (SPDT) switch. A single ground referenced input, controls which switch is on. The Si4700DY is intended for use in applications where two power sources are available and the circuit must select one of the two depending on the conditions. An example of such a circuit is ACPI implementation in computers where part of a circuit must switch to an "always-on" power supply when the computer is in suspend mode, but runs off the main power supply for normal operation.

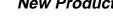

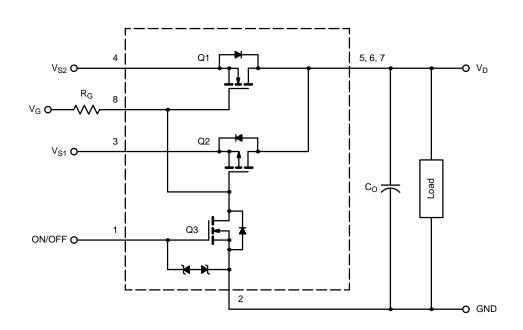

## FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION

# Si4700DY

# Vishay Siliconix

## **New Product**

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> = 25°C UNLESS OTHERWISE NOTED) |    |                                   |            |              |           |

|-------------------------------------------------------------------------|----|-----------------------------------|------------|--------------|-----------|

| Parameter                                                               |    | Symbol                            | 10 sec     | Steady State | Unit<br>v |

| Drain-Source Voltage                                                    | Q1 | V <sub>DS</sub>                   | 12         |              |           |

|                                                                         | Q2 | VDS                               | -12        |              |           |

| Logic Control Input                                                     |    | V <sub>IN</sub>                   | 8          |              |           |

| Continuous Drain Current <sup>a</sup>                                   | Q1 | 1-                                | 7.6        | 5.3          |           |

|                                                                         | Q2 |                                   | 5.0        | 3.5          |           |

| Pulsed Drain Current <sup>b</sup>                                       | Q1 |                                   | 20         |              | А         |

|                                                                         | Q2 | I <sub>DM</sub>                   | 20         |              |           |

| Continuous Intrinsic Diode Conduction <sup>a</sup>                      | Q1 |                                   | 2.1        | 1.15         |           |

|                                                                         | Q2 | - <sup>I</sup> s -                | 2.1        | 1.15         |           |

| Maximum Power Dissipation <sup>a</sup>                                  |    | PD                                | 2.35       | 1.25         | W         |

| Operating Junction and Storage Temperature Range                        |    | T <sub>j</sub> , T <sub>stg</sub> | –55 to 150 |              | °C        |

| ESD Voltage <sup>c</sup>                                                |    | ESD                               | 3          |              | KV        |

Notes

a.

b.

Surface mounted on 1" x1" FR4 board. Pulse test: pulse width  $\leq$  300 μS, duty cycle  $\leq$  2%. Equivalent to MIL-STD-883D Human Body Model (100 pF, 1500 Ω) c.

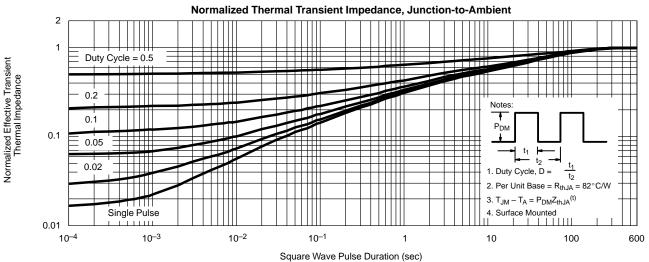

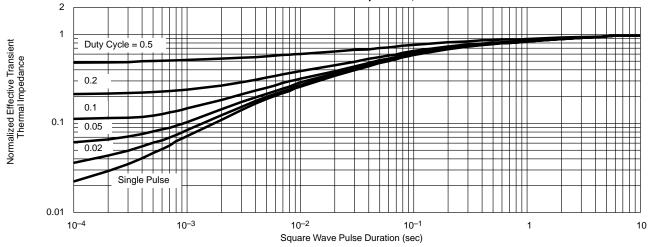

| THERMAL RESISTANCE RATINGS                    |                        |                   |         |         |      |

|-----------------------------------------------|------------------------|-------------------|---------|---------|------|

| Parameter                                     |                        | Symbol            | Typical | Maximum | Unit |

| Maximum Junction-to-Ambient <sup>a</sup>      | $t \le 10 \text{ sec}$ | R <sub>thJA</sub> | 43      | 53      |      |

| Maximum Junction-to-Ambiente                  | Steady State           |                   | 82      | 100     | °C/W |

| Maximum Junction-to-Foot (Drain) <sup>b</sup> | Steady State           | R <sub>thJF</sub> | 25      | 30      |      |

Notes

Surface Mounted on 1" x 1" FR4 Board. a.

Sunction-to-foot thermal impedance represents the effective thermal impedance of all heat carrying leads in parallel and is intended for use in conjunction with the thermal impedance of the PC board pads to ambient ( $R_{thJA} = R_{thJF} + R_{thPCB-A}$ ). It can also be used to estimate chip temperature if power dissipation and the lead temperature of a heat carrying (drain) lead is known. b.

| SPECIFICATIONS            |                     |                                                                      |        |     |                  |     |      |  |

|---------------------------|---------------------|----------------------------------------------------------------------|--------|-----|------------------|-----|------|--|

|                           |                     |                                                                      | Limits |     |                  |     |      |  |

| Parameter                 | Symbol              | Specific Test Conditions                                             |        | Min | Typ <sup>a</sup> | Max | Unit |  |

|                           |                     |                                                                      |        |     |                  |     |      |  |

| Off State Leakage Current |                     | $V_{\text{DS}} = -12 \text{ V},  \text{V}_{\text{GS}} = 0 \text{ V}$ | Q1     |     |                  | 1   |      |  |

|                           |                     |                                                                      | Q2     |     |                  | -1  |      |  |

|                           | DSS                 | $V_{DS} = -8 V$ , $V_{GS} = 0 V$                                     | Q3     |     |                  | 1   | μA   |  |

|                           |                     | $V_{DS}$ = -12 V, $V_{GS}$ = 0 V, $T_{J}$ = 55 $^{\circ}$ C          | Q2     |     |                  | -5  | 1    |  |

| Gate-Body Leakage         | I <sub>GSS</sub>    | $V_{DS}$ = 0 V, $V_{GS}$ = ±4.5 V                                    | Q3     |     |                  | ±1  | 1    |  |

| Gate-Threshold Voltage    | V <sub>GS(th)</sub> | $V_{DS} = V_{GS}$ , $I_D = 250 \ \mu A$                              | Q3     | 0.6 |                  |     | V    |  |

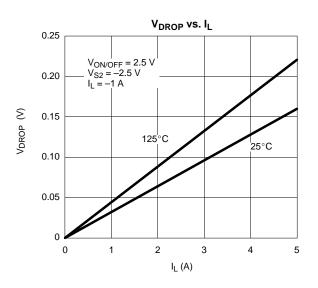

| On-Resistance             | r <sub>DS(on)</sub> | $V_{S}$ = 4.5 V, $I_{D}$ = 1 A, $V_{ON/OFF}$ = 2.5 V                 | Q1     |     | 25               | 30  | mΩ   |  |

|                           |                     | $V_{S}$ = 2.5 V, $I_{D}$ = 1 A, $V_{ON/OFF}$ = 2.5 V                 | Q1     |     | 32               | 40  |      |  |

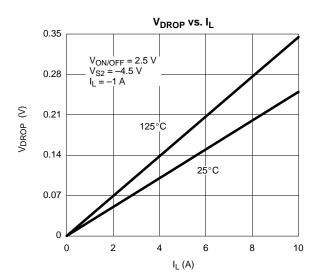

|                           |                     | $V_{S}$ = 4.5 V, $I_{D}$ = 1 A, $V_{ON/OFF}$ = 2.5 V                 | Q2     |     | 58               | 70  |      |  |

|                           |                     | $V_{S}$ = 2.5 V, $I_{D}$ = 1 A, $V_{ON/OFF}$ = 2.5 V                 | Q2     |     | 90               | 110 | 1    |  |

Notes a. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

PIN CONFIGURATION

Order Number: Si4700DY

| TRUTH TABLE     |     |     |  |  |

|-----------------|-----|-----|--|--|

| V <sub>IN</sub> | Q1  | Q2  |  |  |

| L               | ON  | OFF |  |  |

| Н               | OFF | ON  |  |  |

| PIN DESCRIPTION |                     |                                                     |  |  |  |

|-----------------|---------------------|-----------------------------------------------------|--|--|--|

| Pin Number      | Symbol              | Description                                         |  |  |  |

| 1               | V <sub>ON/OFF</sub> | Logic Input Signal                                  |  |  |  |

| 2               | GND                 | Ground (reference for logic input and power ground) |  |  |  |

| 3               | Q2 SOURCE           | Input for alternate power                           |  |  |  |

| 4               | Q1 SOURCE           | Input for main power                                |  |  |  |

| 5, 6, 7         | DRAIN               | Output                                              |  |  |  |

| 8               | V <sub>GATE</sub>   | Gate drive voltage via pull-up resistor             |  |  |  |

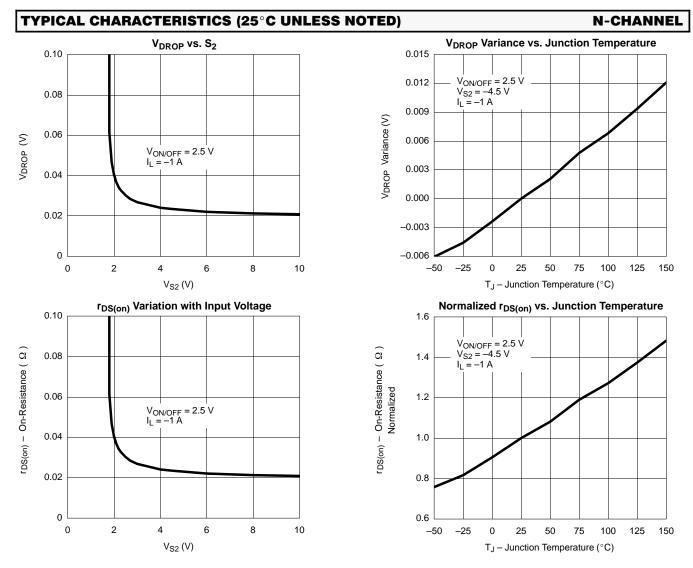

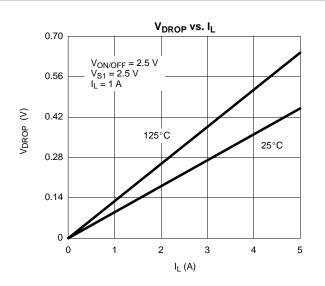

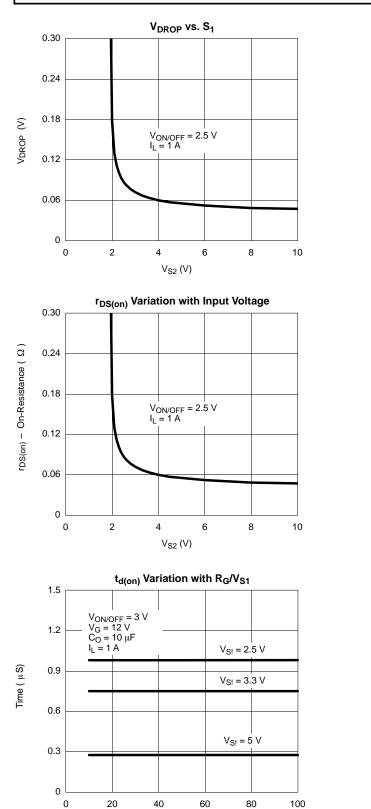

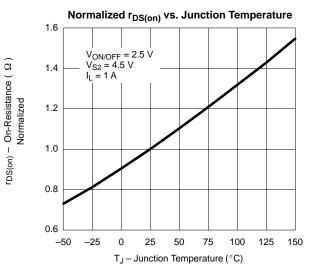

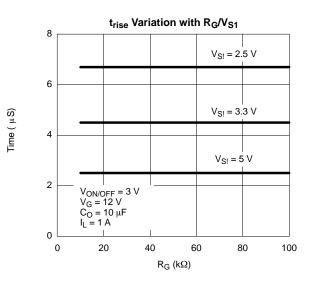

## TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

### **N-CHANNEL**

# Si4700DY

## **Vishay Siliconix**

**New Product**

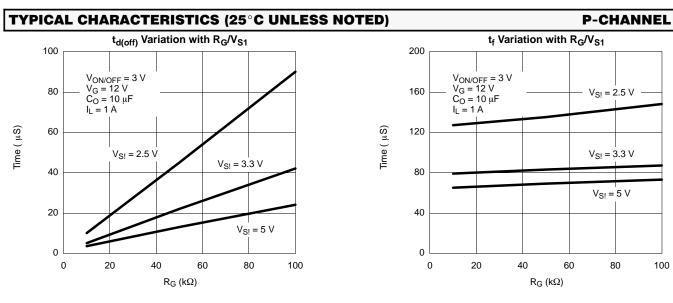

## TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

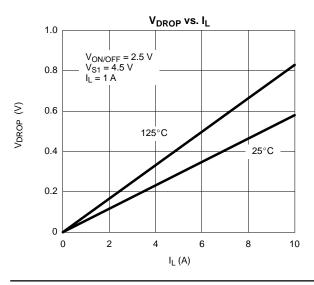

### **P-CHANNEL**

www.vishay.com • FaxBack 408-970-5600 2-4

Document Number: 71110 S-00025—Rev. A, 24-Jan-00

# Si4700DY Vishay Siliconix

## **TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)**

#### **P-CHANNEL**

$\mathsf{R}_{\mathsf{G}}(\mathsf{k}\Omega)$

V<sub>DROP</sub> Variance vs. Junction Temperature 0.04  $\begin{array}{l} V_{ON/OFF} = 2.5 \ V \\ V_{S1} = 4.5 \ V \\ I_L = 1 \ A \end{array}$ 0.03 VDROP Variance (V) 0.02 0.01 0.00 -0.01 -0.02 -50 -25 0 25 50 75 100 125 150 T<sub>J</sub> – Junction Temperature (°C)

Document Number: 71110 S-00025—Rev. A, 24-Jan-00

## **Vishay Siliconix**

**New Product**

TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

# **ALL CHANNELS**

Normalized Thermal Transient Impedance, Junction-to-Foot

www.vishay.com • FaxBack 408-970-5600 2-6

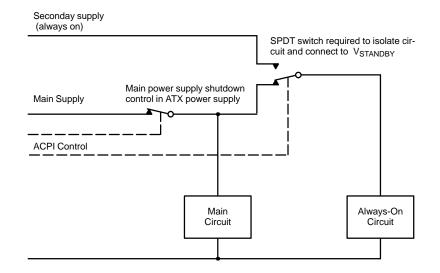

## **TYPICAL APPLICATIONS**

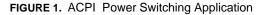

The Si4700 is designed to be used to select one of two power sources for a circuit, such as needed to implement ACPI in desktop computers. In this application, parts of the circuit must run off an always-on power supply when the computer is in suspend mode. When in normal mode, these circuits run off the main power supply.

The Si4700DY contains an n-channel MOSFET and a p-channel MOSFET switch connected together to make a single-pole, double-throw switch. An additional on-board small signal MOSFET provides a ground referenced logic input. When the control input is high, the power MOSFET gates are pulled to ground, and the p-channel MOSFET is on. When the input is low, the gates are pulled above the supply rail, and the n-channel MOSFET is on (pulling the gate of the p-channel above the source potential has no effect).

The gate drive for the n-channel device, Q1, uses an external 12-V supply via an external resistor. A typical value for this resistor is around 20 k $\Omega$ , but the value is not critical as long as the current in Q3 is kept below 0.05 A. A higher value of resistance reduces the current while in suspend mode, but also introduces a longer delay when turning on Q1.

The Si4700DY switch is a break-before-make configuration, therefore sufficient capacitance must be present on the isolated load to ensure hold up during switching. Due to fast switching times this should not be significant and is preferred over a make-before-break that would connect the two power supplies directly for a short period.

Note that the n-channel MOSFET is oriented to ensure that the internal diode does not conduct while the sub-circuit is isolated. In this direction it also provides a fail-safe path for the circuit's power through the diode. The forward drop of the p-channel MOSFET's diode will block any current back-feeding the secondary supply, assuming the two supplies are very close in voltage.

The Si4700DY has a maximum  $r_{DS(on)}$  of 30 m $\Omega$  for the n-channel MOSFET used during normal operation and 70 m $\Omega$  for the p-channel used when the computer is in suspend, making it ideal for loads up to 3 A or higher depending on voltage drop requirements. It can be used on any rail voltage between 2.5 V and 8 V (based on an absolute max of 12 V), with a logic input between 2.5-V and 5-V nominal.

Document Number: 71110 S-00025—Rev. A, 24-Jan-00

FIGURE 2. Si4700DY used for ACPI Power Switching

Vishay

# Disclaimer

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.