128MB to 16GB CompactFlash Card

Solid-State Memory Card (No Moving Parts)

Capacity: 128MB - 16GB

CFA 3.0 and ATA-5 Compatible

ATA Transfer modes:

- PIO 0-6, MWDMA 0-4

- PIO 0-6 only (for applications that require MWDMA access to be disabled)

Supports TrueIDE and PC Card Memory and I/O Modes

Form Factors:

- CompactFlash Type I

- CompactFlash Type II

- CompactFlash Adapter

Endurance Guarantee of 2,000,000 Write/Erase Cycles

Card Information Structure (CIS) Programmed into 256 Bytes of Internal Memory

PC Card and Socket Services Release 2.1 or later compatible

5V or 3.3V Power Supply

Commercial and Industrial Operating Temperature Range

5-Byte Detection, 4-Byte Correction ECC Engine

10 Year Data Retention

**RoHS-6** Compliant

# SLCFxxx(M/G)M1(T2)U(I)

# **General Description and Key Features**

STEC's flash storage adheres to the latest industry compliance and regulatory standards including UL, FCC, RoHS, and various compliance associations. Each device incorporates a proprietary state-of-the-art flash memory controller that provides the greatest flexibility to customer-specific applications while supporting key flash management features resulting in the industry's highest reliability and endurance. Key features include:

- Built-in ECC engine detects up to 5-byte and corrects up to 4-byte errors

- Sophisticated block management and wear leveling algorithms guarantees 2,000,000 write/erase cycles

- Power-down data protection ensures data integrity and errors in case of power loss

- Lifecycle management feature allows users to monitor the device's block management

STEC's CF Card is the product of choice in applications requiring high reliability and high tolerance to shock, vibration, humidity, altitude, ESD, and temperature. The rugged industrial design combined with industrial temperature (-40°C to 85°C) testing and adherence to rigid JEDEC JESD22 standards ensures flawless execution in the harshest environments.

In addition to custom hardware and firmware designs, STEC also offers value-added services including:

- Custom labeling and packaging

- Custom software imaging and ID strings

- Full BOM control and product change notification

- Total supply-chain management to ensure continuity of supply

- In-field application engineering to help customers through product design-ins

#### **Ordering Information: CompactFlash Card**

| Part Number     | CF Form Factor | Capacity   |

|-----------------|----------------|------------|

| SLCF128MM1U(I)  | Туре І         | 128 Mbytes |

| SLCF256MM1U(I)  | Туре І         | 256 Mbytes |

| SLCF512MM1U(I)  | Туре І         | 512 Mbytes |

| SLCF1GM1U(I)    | Туре І         | 1 GByte    |

| SLCF2GM1U(I)    | Туре І         | 2 GBytes   |

| SLCF4GM1U(I)    | Туре І         | 4 GBytes   |

| SLCF8GM1U(I)    | Туре І         | 8 GBytes   |

| SLCF16GM1T2U(I) | Туре II        | 16 GBytes  |

|                 |                |            |

#### Legend:

- SLCF = STEC standard CF Card part number prefix.

- (M/G) = proceeding capacity (xxx) is in Megabytes (M) or Gigabytes (G).

- M1 = STEC Mach 1 controller.

- **U** = RoHS-6 compliant lead-free.

- **Part numbers without (I) =** Commercial temperature range (0°C to 70°C).

- (I) = Industrial temperature range (-40°C to +85 °C).

- F = media set to fixed storage for non-removable IDE applications. Use with operating systems, such as Windows XP, that require storage media to be identified as a fixed drive before it can be used as a bootable drive. Example: SLCFxxx(M/G)M1(T2)U(I)-F.

- P = firmware programmed for PIO Modes 0-6 only for applications requiring MWDMA access to be disabled. Example: SLCFxxx(M/G)M1(T2)U(I)-P.

- S = optimized for applications that store small (1-4 sector) data packets, e.g. transactional data acquisition. Example: SLCFxxx(M/G)M1(T2)U(I)-S.

# **Table of Contents**

|     | eral Description and Key Features                                                                                                                                                                                                                                                                                                                                        |                                              |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Ord | ering Information: CompactFlash Card                                                                                                                                                                                                                                                                                                                                     | . 1                                          |

|     | Product Specifications         1.1 Labeling         1.2 Package Dimensions and Pin Locations         1.2.1 CompactFlash Type I         1.2.2 CompactFlash Type II         1.3 Pin Assignment         1.4 Signal Descriptions         1.5 Performance         1.6 CHS Parameters         1.7 Standards Compliance         1.7.1 CE and FCC Class B & D         1.7.2 RoHS | 3<br>4<br>4<br>5<br>6<br>7<br>10<br>10<br>11 |

| 2.0 | Environmental Specifications                                                                                                                                                                                                                                                                                                                                             |                                              |

|     | <ul> <li>2.1 Recommended Operating Conditions</li></ul>                                                                                                                                                                                                                                                                                                                  | 12<br>12                                     |

| 3.0 | Electrical Specifications                                                                                                                                                                                                                                                                                                                                                | .13                                          |

|     | <ul> <li>3.1 Absolute Maximum Ratings</li></ul>                                                                                                                                                                                                                                                                                                                          | 13<br>14<br>14                               |

|     | 3.3.3 PC Card Memory Mode Common Memory Read                                                                                                                                                                                                                                                                                                                             | 16                                           |

|     | <ul> <li>3.3.4 PC Card Memory Mode Common Memory Write</li> <li>3.3.5 PC Card I/O Mode Read AC Characteristics</li></ul>                                                                                                                                                                                                                                                 | 18<br>19                                     |

|     | <ul> <li>3.3.7 True IDE Mode Register Access</li></ul>                                                                                                                                                                                                                                                                                                                   | 21<br>23                                     |

| 4.0 | Host Access Specification                                                                                                                                                                                                                                                                                                                                                |                                              |

|     | <ul> <li>4.1 Task File Register and Byte/Word/Odd-Byte Mode Mappings</li></ul>                                                                                                                                                                                                                                                                                           | 25<br>26                                     |

| 5.0 | Registers                                                                                                                                                                                                                                                                                                                                                                |                                              |

|     | <ul><li>5.1 Configuration Registers</li><li>5.2 Task File Registers</li></ul>                                                                                                                                                                                                                                                                                            |                                              |

| 6.0 |                                                                                                                                                                                                                                                                                                                                                                          |                                              |

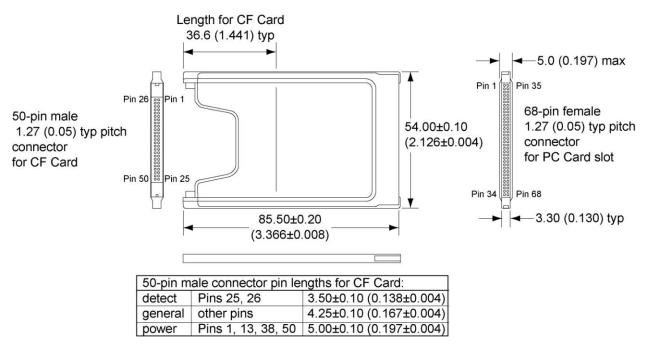

| 7.0 | Appendix: CompactFlash Adapter                                                                                                                                                                                                                                                                                                                                           | 35                                           |

|     | <ul> <li>7.1 CF Adapter Ordering Information</li> <li>7.2 CF Adapter Specifications</li> <li>7.3 CF Adapter Package Dimensions and Pin Locations</li> </ul>                                                                                                                                                                                                              | 35<br>36                                     |

| 8.0 | 7.4 CF Adapter Pin Assignment<br>Revision History                                                                                                                                                                                                                                                                                                                        |                                              |

# **1.0 Product Specifications**

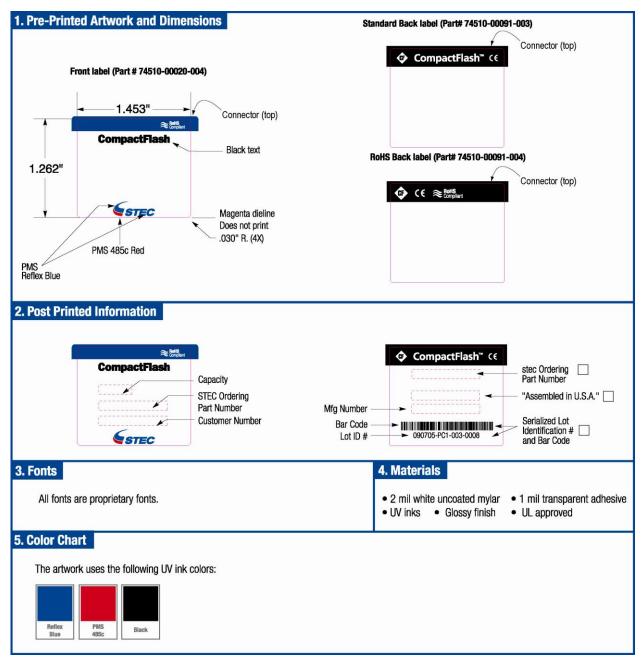

#### 1.1 Labeling

STEC CF Cards can be manufactured with standard labeling, or customer-specific, custom labeling. Standard labeling is shown in Figure 1.

Figure 1: Standard Labeling

## 1.2 Package Dimensions and Pin Locations

#### 1.2.1 CompactFlash Type I

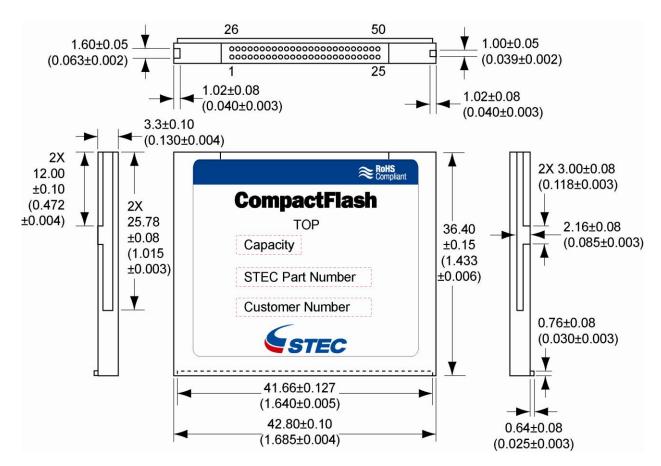

Table 1 and Figure 2 show the mechanical dimensions of the CompactFlash Type I.

#### Table 1: Mechanical dimensions CompactFlash Type I

| Parameter                     | Value                                |  |  |

|-------------------------------|--------------------------------------|--|--|

| Length                        | 36.40 ± 0.15 mm (1.433 ±. 0.006 in)  |  |  |

| Width                         | 42.80 ± 0.10 mm (1.685 ± 0.004 in)   |  |  |

| Height (including label area) | 3.30 mm ± 0.10 mm (0.130 ± 0.004 in) |  |  |

Figure 2: Mechanical dimensions CompactFlash Type I

# 1.2.2 CompactFlash Type II

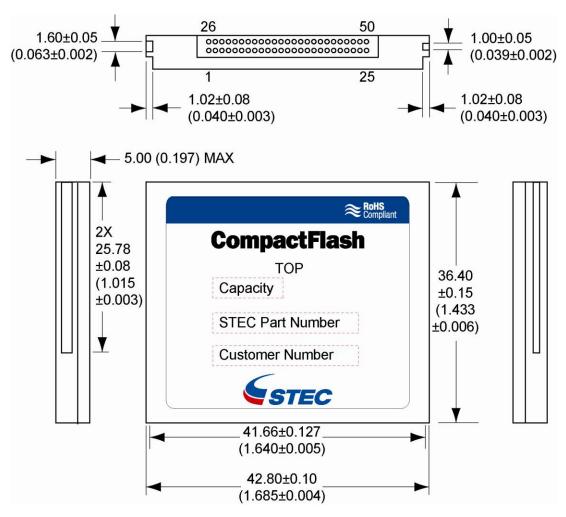

Table 2 and Figure 3 show the mechanical dimensions of the CompactFlash Type II.

Table 2: Mechanical dimensions CompactFlash Type II

| Parameter                     | Value                               |  |  |

|-------------------------------|-------------------------------------|--|--|

| Length                        | 36.40 ± 0.15 mm (1.433 ±. 0.006 in) |  |  |

| Width                         | 42.80 ± 0.10 mm (1.685 ± 0.004 in)  |  |  |

| Height (including label area) | 5.00 mm (0.197 in) max              |  |  |

Figure 3: Mechanical dimensions CompactFlash Type II

# 1.3 Pin Assignment

| rable 5. Or Gala Fill Assignment |                |          |               |                                                        |          |  |  |  |

|----------------------------------|----------------|----------|---------------|--------------------------------------------------------|----------|--|--|--|

| Pin<br>Number                    | Signal Name    | Pin Type | Pin<br>Number | Signal Name                                            | Pin Type |  |  |  |

| 1                                | GND            | Ground   | 26            | -CD1                                                   | 0        |  |  |  |

| 2                                | D03            | I/O      | 27            | D11                                                    | I/O      |  |  |  |

| 3                                | D04            | I/O      | 28            | D12                                                    | I/O      |  |  |  |

| 4                                | D05            | I/O      | 29            | D13                                                    | I/O      |  |  |  |

| 5                                | D06            | I/O      | 30            | D14                                                    | I/O      |  |  |  |

| 6                                | D07            | I/O      | 31            | D15                                                    | I/O      |  |  |  |

| 7                                | -CE1<br>-CS0   | I        | 32            | -CE2<br>-CS1                                           | I        |  |  |  |

| 8                                | A10            | I        | 33            | -VS1                                                   | 0        |  |  |  |

| 9                                | -OE<br>-ATASEL | I        | 34            | -IORD                                                  | I        |  |  |  |

| 10                               | A09            | I        | 35            | -IOWR                                                  | l        |  |  |  |

| 11                               | A08            | I        | 36            | -WE                                                    | I        |  |  |  |

| 12                               | A07            | I        | 37            | RDY/-BSY<br>-IREQ<br>INTRQ                             | 0        |  |  |  |

| 13                               | VCC            | Power    | 38            | VCC                                                    | Power    |  |  |  |

| 14                               | A06            | I        | 39            | -CSEL                                                  | l        |  |  |  |

| 15                               | A05            | I        | 40            | -VS2                                                   | 0        |  |  |  |

| 16                               | A04            | I        | 41            | RESET<br>-RESET                                        | I        |  |  |  |

| 17                               | A03            | I        | 42            | -WAIT<br>IORDY                                         | 0        |  |  |  |

| 18                               | A02            | I        | 43            | -INPACK<br>DMARQ (not used for part<br>numbers with P) | 0        |  |  |  |

| 19                               | A01            | I        | 44            | -REG<br>-DMACK (not used for part<br>numbers with P)   | Ι        |  |  |  |

| 20                               | A00            | I        | 45            | BVD2<br>-SPKR<br>-DASP                                 | I/O      |  |  |  |

| 21                               | D00            | I/O      | 46            | BVD1<br>-STSCHG<br>-PDIAG                              | I/O      |  |  |  |

| 22                               | D01            | I/O      | 47            | D08                                                    | I/O      |  |  |  |

| 23                               | D02            | I/O      | 48            | D09                                                    | I/O      |  |  |  |

|                                  |                |          |               |                                                        |          |  |  |  |

#### Table 3: CF Card Pin Assignment

Legend: "-" = Low active

24

25

WP

-IOIS16 -CD2

49

50

0

0

D10

GND

I/O

Ground

# 1.4 Signal Descriptions

| Table 4: CF Card Signal Descriptions |

|--------------------------------------|

|--------------------------------------|

| Signal Name                         | Туре | Pin<br>Number                                                            | Description                                                                                                                                                                                   |

|-------------------------------------|------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BVD2<br>(PC Card Memory Mode)       | I/O  | 45                                                                       | This output line is always driven to a high state in Memory<br>Mode since a battery is not required for this product.                                                                         |

| -SPKR<br>(PC Card I/O Mode)         |      |                                                                          | This output line is always driven to a high state in I/O Mode since this product produces no audio.                                                                                           |

| -DASP<br>(True IDE Mode)            |      |                                                                          | In the True IDE Mode, this input/output is the Disk<br>Active/Slave Present signal in the Master/Slave handshake<br>protocol.                                                                 |

| -CD1, -CD2<br>(PC Card Memory Mode) | I/O  | 26, 25                                                                   | These Card Detect pins are connected to ground on the card.<br>They are used by the host to determine that the card is fully<br>inserted into the socket.                                     |

| -CD1, -CD2<br>(PC Card I/O Mode)    |      |                                                                          | This signal is the same as Memory Mode.                                                                                                                                                       |

| -CD1, -CD2<br>(True IDE Mode)       |      |                                                                          | These signals are not used in IDE Mode.                                                                                                                                                       |

| D15-D00<br>(PC Card Memory Mode)    | I/O  | 31, 30,<br>29, 28,<br>27, 49,<br>48, 47, 6,<br>5, 4, 3, 2,<br>23, 22, 21 | These lines carry the data, commands, and host and the controller. D00 is the LSB of the LSB of the Odd Byte of the Word.                                                                     |

| D15-D00<br>PC Card I/O Mode         |      |                                                                          | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                    |

| D15-D00<br>(True IDE Mode)          |      |                                                                          | In True IDE Mode, all Task File operations occur in byte mode on the low order bus D00-D07 while all data transfers are 16 bit using D00-D15.                                                 |

| -IOWR<br>(PC Card Memory Mode)      | Ι    | 35                                                                       | This signal is not used in this mode.                                                                                                                                                         |

| -IOWR<br>(PC Card I/O Mode)         |      |                                                                          | The I/O Write strobe pulse is used to clock I/O data onto the data bus and into the controller registers. The clocking occurs on the negative to positive edge of the signal (trailing edge). |

| -IOWR<br>(True IDE Mode)            |      |                                                                          | In True IDE Mode, this signal has the same function as in PC Card I/O Mode.                                                                                                                   |

| -IORD<br>(PC Card Memory Mode)      | Ι    | 34                                                                       | This signal is not used in this mode.                                                                                                                                                         |

| -IORD<br>(PC Card I/O Mode)         |      |                                                                          | This is an I/O Read strobe generated by the host. This signal gates I/O data onto the bus from the CF Card.                                                                                   |

| -IORD<br>(True IDE Mode)            |      |                                                                          | In True IDE Mode, this signal has the same function as in PC Card I/O Mode.                                                                                                                   |

| -WE<br>(PC Card Memory Mode)        | I    | 36                                                                       | This is a signal driven by the host and used for strobing<br>memory write data into the registers. It is also used for writing<br>the configuration registers.                                |

| -WE<br>(PC Card I/O Mode)           |      |                                                                          | In PC Card I/O Mode, this signal is used for writing the configuration registers.                                                                                                             |

| -WE<br>(True IDE Mode)              |      |                                                                          | In True IDE Mode, this input signal is not used and should be connected to VCC.                                                                                                               |

| -OE<br>(PC Card Memory Mode)        | I    | 9                                                                        | This is an Output Enable strobe generated by the host interface.<br>It is used to read data from the CF Card in PC Card Memory<br>Mode and to read the CIS and configuration registers.       |

# SLCFxxx(M/G)M1(T2)U(I) Datasheet\_\_\_\_

| Signal Name                                              | Туре | Pin<br>Number                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------|------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -OE<br>(PC Card I/O Mode)                                |      |                                                       | In PC Card I/O Mode, this signal is used to read the CIS and configuration registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -ATASEL<br>(True IDE Mode)                               |      |                                                       | To enable True IDE Mode, this input should be grounded by the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RDY/-BSY<br>(PC Card Memory Mode)                        | 0    | 37                                                    | In Memory Mode, this signal is set high when the CF Card is<br>ready to accept a new data transfer operation and held low<br>when the CF Card is busy. The host must provide a pull-up<br>resistor. At power up and at reset, the RDY/-BSY signal is<br>held low (busy) until the CF Card completes its power up or<br>reset function. No access of any type should be made to the<br>CF Card during this time. The<br>RDY/-BSY signal is held high (disabled from being busy)<br>when the CF Card is powered up with RESET continuously<br>disconnected or asserted high. |

| -IREQ<br>(PC Card I/O Mode)                              |      |                                                       | After the CF Card has been configured for I/O operation, this signal is used as the active low interrupt request. This line is strobed low to generate a pulse mode interrupt or held low for a level mode interrupt.                                                                                                                                                                                                                                                                                                                                                      |

| INTRQ<br>(True IDE Mode)                                 |      |                                                       | In True IDE Mode, this signal is the active high interrupt request to the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A10-A0<br>(PC Card Memory Mode)                          | I    | 8, 10, 11,<br>12, 14,<br>15, 16,<br>17, 18,<br>19, 20 | These address lines along with the -REG signal are used to select the following: the I/O port address registers within the CF Card, the memory mapped port address registers within the CF Card, a byte in the CIS and the Configuration Control and Status Registers.                                                                                                                                                                                                                                                                                                     |

| A10-A0<br>(PC Card I/O Mode)                             |      |                                                       | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A2-A0<br>(True IDE Mode)                                 |      | 18, 19, 20                                            | In True IDE Mode only, A2:A0 are used to select the one of eight registers in the Task File. The remaining address lines should be grounded.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| -CE1, -CE2<br>(PC Card Memory Mode<br>Card Enable        | I    | 7, 32                                                 | These input signals are used both to select the CF Card and to indicate to the CF Card whether a byte or a word operation is being performedCE2 always accesses the odd byte of the wordCE1 accesses the even byte or the odd byte of the word depending on A0 and -CE2. A multiplexing scheme based on A0, -CE1, -CE2 allows 8-bit hosts to access all data on D0-D7.                                                                                                                                                                                                     |

| -CE1, -CE2<br>(PC Card I/O Mode)<br>Card Enable          |      |                                                       | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| -CS0, -CS1<br>(True IDE Mode)                            |      |                                                       | In the True IDE Mode, -CS0 is the chip select for the task file registers while -CS1 is used to select the Alternate Status Register and the CF Card Control Register.                                                                                                                                                                                                                                                                                                                                                                                                     |

| -CSEL<br>(PC Card Memory Mode)                           | I    | 39                                                    | This signal is not used for this mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -CSEL<br>(PC Card I/O Mode)                              |      |                                                       | This signal is not used for this mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -CSEL<br>(True IDE Mode)                                 |      |                                                       | This internally pulled up signal is used to configure the card<br>as a Master or Slave. When the pin is grounded, the card is<br>configured as a Master. When the pin is open, the card is<br>configured as a Slave.                                                                                                                                                                                                                                                                                                                                                       |

| -REG<br>(PC Card Memory Mode)<br>Attribute Memory Select | Ι    | 44                                                    | This signal distinguishes between accesses to Common Memory (high) and Register Attribute Memory (low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# SLCFxxx(M/G)M1(T2)U(I) Datasheet

| Signal Name                                                     | Туре | Pin<br>Number | Description                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -REG<br>(PC Card I/O Mode)                                      |      |               | The signal must also be active (low) during I/O Cycles when the I/O address is on the bus.                                                                                                                                                                                       |

| -DMACK (not used for part<br>numbers with P)<br>(True IDE Mode) |      |               | In True IDE Mode this input signal is used by host in response to DMARQ to initiate DMA transfers.                                                                                                                                                                               |

| WP<br>(PC Card Memory Mode)<br>Write Protect                    | 0    | 24            | The CF Card does not have a write protect switch; therefore,<br>this signal is held low after the completion of the reset<br>initialization sequence.                                                                                                                            |

| -IOIS16<br>(PC Card I/O Mode)                                   |      |               | A low signal indicates that a 16 bit or odd byte only operation can be performed at the addressed port.                                                                                                                                                                          |

| -IOCS16<br>(True IDE Mode)                                      |      |               | Not defined in IDE Mode.                                                                                                                                                                                                                                                         |

| -INPACK<br>(PC Card Memory Mode)                                | 0    | 43            | This signal is not used in this mode.                                                                                                                                                                                                                                            |

| -INPACK<br>(PC Card I/O Mode)<br>Input Acknowledge              |      |               | The Input Acknowledge signal is asserted by the CF Card<br>when it is selected and responding to an I/O read cycle at the<br>address that is on the bus. The host uses this signal to<br>control the enable of any input data buffers between the CF<br>Card and the host's CPU. |

| DMARQ (Not used for part<br>numbers with P)<br>(True IDE Mode)  |      |               | In True IDE Mode this signal is asserted by the CF Card<br>when it is ready to transfer data to/from the host. Data<br>direction is controlled by -IORD and -IOWR. This signal is<br>used in a handshake manner with -DMACK.                                                     |

| BVD1<br>(PC Card Memory Mode)                                   | I/O  | 46            | This signal is asserted high as since a battery is not used with this product.                                                                                                                                                                                                   |

| -STSCHG<br>(PC Card I/O Mode)<br>Status Changed                 |      |               | This signal is asserted low to alert the host to changes in the RDY/-BSY and Write Protect states. Its use is controlled by the Configuration and Status Register.                                                                                                               |

| -PDIAG<br>(True IDE Mode)                                       |      |               | In True IDE Mode, this input/output signal is the Pass Diagnostic signal in the Master/Slave handshake protocol.                                                                                                                                                                 |

| -WAIT<br>(PC Card Memory Mode)                                  | 0    | 42            | This signal is not used by the CF Card, and is pulled up to VCC through a 4.7K ohm resistor.                                                                                                                                                                                     |

| -WAIT<br>(PC Card I/O Mode)                                     |      |               | This signal is not used by the CF Card, and is pulled up to VCC through a 4.7K ohm resistor.                                                                                                                                                                                     |

| IORDY<br>(True IDE Mode)                                        |      |               | This signal is not used by the CF Card, and is pulled up to VCC through a 4.7K ohm resistor.                                                                                                                                                                                     |

| GND<br>(PC Card Memory Mode)                                    | GND  | 1, 50         | Ground                                                                                                                                                                                                                                                                           |

| GND<br>(PC Card I/O Mode)                                       |      |               | Ground                                                                                                                                                                                                                                                                           |

| GND<br>(True IDE Mode)                                          |      |               | Ground                                                                                                                                                                                                                                                                           |

| VCC<br>(PC Card Memory Mode)                                    | VCC  | 13, 38        | +5 V or 3.3V power                                                                                                                                                                                                                                                               |

| VCC<br>(PC Card I/O Mode)                                       |      |               | +5 V or 3.3V power                                                                                                                                                                                                                                                               |

| VCC<br>(True IDE Mode)                                          |      |               | +5 V or 3.3V power                                                                                                                                                                                                                                                               |

| RESET<br>(PC Card Memory Mode)                                  | I    | 41            | When RESET is high, this signal resets the CF Card. The CF Card is reset only at power up if this signal is left high or open from power-up. The CF Card can also be reset when the soft reset bit in the Configuration Option Register is set.                                  |

# SLCFxxx(M/G)M1(T2)U(I) Datasheet

| Signal Name                           | Туре | Pin<br>Number | Description                                                                                                                |

|---------------------------------------|------|---------------|----------------------------------------------------------------------------------------------------------------------------|

| RESET<br>(PC Card I/O Mode)           |      |               | This signal is the same as the PC Card Memory Mode signal.                                                                 |

| -RESET<br>(True IDE Mode)             |      |               | In the True IDE Mode this input pin is the active low hardware reset from the host.                                        |

| -VS1<br>-VS2<br>(PC Card Memory Mode) | 0    | 33, 40        | -VS1 is grounded so that the card CIS can be read at 3.3 voltsVS2 is reserved for a secondary voltage and is not connected |

| -VS1<br>-VS2<br>(PC Card I/O Mode)    |      |               | This signal is the same for all models.                                                                                    |

| -VS1<br>-VS2<br>(True IDE Mode)       |      |               | This signal is not used in IDE Mode.                                                                                       |

#### 1.5 Performance

#### Table 5: CF Card Read/Write Performance

| Parameter                       | Value                 |  |

|---------------------------------|-----------------------|--|

| Data transfer rate to/from host | 16.7 MBytes/s (burst) |  |

| Sustained read                  | up to 10 MBytes/s     |  |

| Sustained write                 | up to 7 MBytes/s      |  |

#### 1.6 CHS Parameters

#### Table 6: CHS Parameters per capacity

| Capacity | Cylinder (C)<br>(standard) | Cylinder (C)<br>(for part number with S suffix) | Head (H) | Sectors/Track (S) |

|----------|----------------------------|-------------------------------------------------|----------|-------------------|

| 128MB    | 980                        | 924                                             | 8        | 32                |

| 256MB    | 980                        | 924                                             | 16       | 32                |

| 512MB    | 993                        | 939                                             | 16       | 63                |

| 1GB      | 1,986                      | 1,878                                           | 16       | 63                |

| 2GB      | 3,970                      | 3,756                                           | 16       | 63                |

| 4GB      | 7,964                      | 7,535                                           | 16       | 63                |

| 8GB      | 16,062                     | 15,093                                          | 16       | 63                |

| 16GB     | 31,760                     | -                                               | 16       | 63                |

#### **1.7 Standards Compliance**

STEC products specified in this document are certified for compliance with the following industry standards:

- CFA v4.0, PCMCIA v7.0

- UL 950

- CE, and FCC Class B & D

- RoHS

#### 1.7.1 CE and FCC Class B & D

The STEC products specified in this document meet the following requirements and limits of the European Standards:

Class B requirements of the following European Standard:

EN 55022: 1998 – "Information technology equipment – Radio disturbance characteristics – Limits and methods of measurement"

Class D limits of the following European Standards:

EN 61000-3-2 "Electromagnetic compatibility (EMC) Part 3-2: Limits – Limits for harmonic current emissions (equipment input current up to and including 16 A per phase)"

EN 61000-3-3: 1995 – "Part 3: Limits – Section 3: Limitation of voltage fluctuations and flicker in low-voltage supply systems for equipment with rated current <= 16A"

EN 55024 – "Information technology equipment – Immunity characteristics – Limits and methods of measurement"

#### 1.7.2 RoHS

STEC certifies that its products do not contain any of the restricted substances as stated below and are in compliance with RoHS EU directive 2002/95/EC, specifically:

- Mercury (Hg)

- Cadmium Cd)

- Chromium VI (Cr +6)

- Polybrominated biphenyl (PBB)

- Polybrominated biphenyl ether (PBDE)

- Lead (Pb)

Materials used in the STEC's products are limited to the following:

- Steel, Nylon 6/6, PCB laminate

- Copper, Gold, Nickel

- Silicon on ICs and Components

- Polyester on Labels

# 2.0 Environmental Specifications

## 2.1 Recommended Operating Conditions

#### Table 7: CF Card Recommended Operating Conditions

| Parameter                        | Symbol | Min  | Тур | Max   | Unit |

|----------------------------------|--------|------|-----|-------|------|

| Commercial Operating Temperature | Та     | 0    | 25  | 70    | °C   |

| Industrial Operating Temperature | Та     | -40  | -   | 85    | °C   |

| VCC voltage 5.0                  | VCC5   | 4.75 | 5.0 | 5.25  | V    |

| VCC voltage 3.3                  | VCC3.3 | 3.18 | 3.3 | 3.465 | V    |

#### 2.2 Reliability

#### Table 8: CF Card Endurance & Data Reliability

| Parameter        | Value                            |

|------------------|----------------------------------|

| Endurance        | 2,000,000 Write/Erase Cycles     |

| Data reliability | 1 in 10 <sup>14</sup> bits, read |

| Data retention   | 10 years                         |

# 2.3 Shock, Vibration, and Humidity

#### Table 9: CF Card Shock, Vibration & Humidity

| Parameter | Value                                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|

| Shock     | 1.5K G peak, 0.5ms pulse duration, five (5) pulses per each of six (6) directions<br>(per JEDEC JESD22 standard, method B110) |

| Vibration | 20 G peak, 20Hz-2000Hz, 4 cycles per direction<br>(per JEDEC JESD22 standard, method B103)                                    |

| Humidity  | 85°C 85% RH, 500 hrs                                                                                                          |

# 3.0 Electrical Specifications

## 3.1 Absolute Maximum Ratings

| Parameter                 | Symbol    | Value            | Unit |

|---------------------------|-----------|------------------|------|

| Voltage                   | Vin, Vout | -0.5 to VCC +0.5 | V    |

| Storage temperature range | Tstg      | -65 to +150      | °C   |

#### 3.2 DC Characteristics

Measurements at Recommended Operating Conditions unless otherwise specified.

Table 11: CF Card DC Characteristics

| Symbol | Parameter                  | Min  | Max      | Unit | Notes                                                                              |

|--------|----------------------------|------|----------|------|------------------------------------------------------------------------------------|

| VIL    | Input LOW Voltage          | -0.3 | +0.8     | V    | VCC=3.3V or 5.0V                                                                   |

| VIH    | Input HIGH Voltage         | 2.0  | VCC +0.3 | V    | VCC=3.3V or 5.0V                                                                   |

| VOL3.3 | Output LOW Voltage 3.3     |      | 0.45     | V    | VCC=3.3V                                                                           |

| VOL5   | Output LOW Voltage 5       |      | 0.8      |      | VCC=5.0V                                                                           |

| VOH    | Output HIGH Voltage        | 2.4  |          | V    | VCC=3.3V or 5.0V                                                                   |

| ICCSB  | Standby Mode               |      | 2        | mA   | ICC at VCC=3.3V or 5.0V                                                            |

| ICC    | Operating Current          |      | 75       | mA   | ICC at VCC=3.3V or 5.0V;<br>Operating current measured with<br>2-way interleaving. |

| ILI    | Input Leakage Current      |      | 10       | μΑ   | VCC=3.3V or 5.0V                                                                   |

| ILO3.3 | Output Leakage Current 3.3 |      | 1        | μΑ   | VCC=3.3V                                                                           |

| ILO5   | Output Leakage Current 5   |      | 2        | μΑ   | VCC= 5.0V                                                                          |

| CI/O   | Input/output Capacitance   |      | 25       | pF   | VCC=3.3V or 5.0V                                                                   |

# 3.3 AC Characteristics

Measurements at Recommended Operating Conditions, unless otherwise specified.

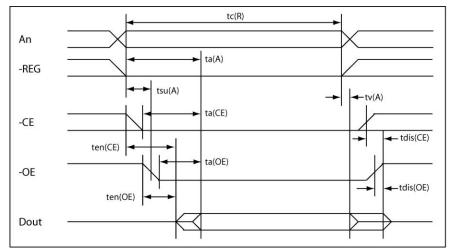

#### 3.3.1 PC Card Memory Mode Attribute Memory Read

Table 12: PC Card Memory Mode Attribute Memory Read AC Characteristics

| Parameter                      | Symbol   | IEEE Symbol | Min (ns) | Max (ns) |

|--------------------------------|----------|-------------|----------|----------|

| Read Cycle Time                | tc(R)    | tAVAV       | 250      |          |

| Address Access Time            | ta(A)    | tAVQV       |          | 250      |

| Card Enable Access Time        | ta(CE)   | tELQV       |          | 250      |

| Output Enable Access Time      | ta(OE)   | tGLQV       |          | 125      |

| Output Disable Time from -CE   | tdis(CE) | tEHQZ       |          | 100      |

| Output Disable Time from -OE   | tdis(OE) | tGHQZ       |          | 100      |

| Address Setup Time             | tsu(A)   | tAVGL       | 30       |          |

| Output Enable Time from -CE    | ten(CE)  | tELQNZ      | 5        |          |

| Output Enable Time from -OE    | ten(OE)  | tGLQNZ      | 5        |          |

| Data Valid from Address Change | tv(A)    | tAXQX       | 0        |          |

| Address Hold Time              | th(A)    | —           | 20       |          |

| -CE Setup Time                 | tsu(CE)  | _           | 0        |          |

| -CE Hold Time                  | th(CE)   |             | 20       |          |

Figure 4: PC Card Memory Mode Attribute Memory Read Timing Diagram

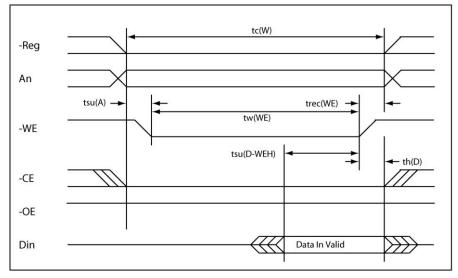

# 3.3.2 PC Card Memory Mode Attribute Memory Write

| Parameter                      | Symbol      | IEEE Symbol | Min (ns) | Max (ns) |

|--------------------------------|-------------|-------------|----------|----------|

| Write Cycle Time               | tc(W)       | tAVAV       | 250      |          |

| Write Pulse Width              | tw(WE)      | tWLWH       | 150      |          |

| Address Setup Time             | tsu(A)      | tAVWL       | 30       |          |

| Address Setup Time (-WE)       | tsu(A-WEH)  | —           | 180      |          |

| -CE Setup Time (-WE)           | tsu(CE-WEH) | —           | 180      |          |

| Data Setup Time (-WE)          | tsu(D-WEH)  | tDVWH       | 80       |          |

| Data Hold Time                 | th(D)       | tWMDX       | 30       |          |

| Write Recovery Time            | trec(WE)    | tWMAX       | 30       |          |

| Output Disable Time (-WE)      | tdis(WE)    | —           |          | 100      |

| Output Disable Time (-OE)      | tdis(OE)    | —           |          | 100      |

| Output Enable Time (-WE)       | ten(WE)     | _           | 5        |          |

| Output Enable Time (-OE)       | ten(OE)     | —           | 5        |          |

| Output Enable Setup Time (-WE) | tsu(OE-WE)  | —           | 10       |          |

| Output Enable Hold Time (-WE)  | th(OE-WE)   | _           | 10       |          |

| -CE Setup Time                 | tsu(CE)     |             | 0        |          |

| -CE Hold Time                  | th(CE)      | —           | 20       |          |

Table 13: PC Card Memory Mode Attribute Memory Write AC Characteristics

Figure 5: PC Card Memory Mode Attribute Memory Write Timing Diagram

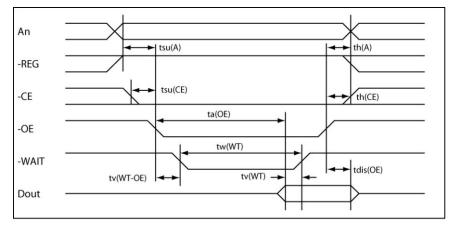

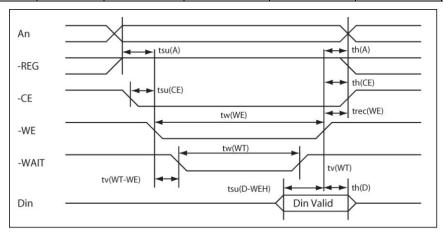

# 3.3.3 PC Card Memory Mode Common Memory Read

| Parameter                               | Symbol    | IEEE<br>Symbol | 250 ns Cycle<br>Time Mode | 120 ns Cycle<br>Time Mode | 100 ns Cycle<br>Time Mode | 80 ns Cycle<br>Time Mode |

|-----------------------------------------|-----------|----------------|---------------------------|---------------------------|---------------------------|--------------------------|

| Output Enable<br>Access Time<br>(max)   | ta(OE)    | tGLQV          | 125                       | 60                        | 50                        | 45                       |

| Output Disable<br>Time from OE<br>(max) | tdis(OE)  | tGHQZ          | 100                       | 60                        | 50                        | 45                       |

| Address Setup<br>Time (min)             | tsu(A)    | tAVGL          | 30                        | 15                        | 10                        | 10                       |

| Address Hold<br>Time (min)              | th(A)     | tGHAX          | 20                        | 15                        | 15                        | 10                       |

| CE Setup<br>before OE (min)             | tsu(CE)   | tELGL          | 0                         | 0                         | 0                         | 0                        |

| CE Hold<br>following OE<br>(min)        | th(CE)    | tGHEH          | 20                        | 15                        | 15                        | 10                       |

| Wait Delay<br>Falling from OE<br>(max)  | tv(WT-OE) | tGLWTV         | 35                        | 35                        | 35                        | N/A                      |

| Data Setup for<br>Wait Release<br>(max) | tv(WT)    | tQVWTH         | 0                         | 0                         | 0                         | N/A                      |

| Wait Width<br>Time (max)                | tw(WT)    | tWTLWTH        | 350                       | 350                       | 350                       | N/A                      |

Table 14: PC Card Memory Mode Common Memory Read AC Characteristics

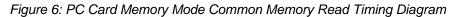

# 3.3.4 PC Card Memory Mode Common Memory Write

| Parameter                           | Symbol         | IEEE<br>Symbol | 250 ns<br>Cycle Time<br>Mode | 120 ns<br>Cycle Time<br>Mode | 100 ns<br>Cycle Time<br>Mode | 80ns Cycle<br>Time Mode |

|-------------------------------------|----------------|----------------|------------------------------|------------------------------|------------------------------|-------------------------|

| Data Setup before<br>WE (min)       | tsu<br>(D-WEH) | tDVWH          | 80                           | 50                           | 40                           | 30                      |

| Data Hold following<br>WE (min)     | th(D)          | tWMDX          | 30                           | 15                           | 10                           | 10                      |

| WE Pulse Width (min)                | tw(WE)         | tWLWH          | 150                          | 70                           | 60                           | 55                      |

| Address Setup Time<br>(min)         | tsu(A)         | tAVWL          | 30                           | 15                           | 10                           | 10                      |

| CE Setup before WE<br>(min)         | tsu(CE)        | tELWL          | 0                            | 0                            | 0                            | 0                       |

| Write Recovery Time<br>(min)        | trec(WE)       | tWMAX          | 30                           | 15                           | 15                           | 15                      |

| Address Hold Time<br>(min)          | th(A)          | tGHAX          | 20                           | 15                           | 15                           | 15                      |

| CE Hold following WE<br>(min)       | th(CE)         | tGHEH          | 20                           | 15                           | 15                           | 10                      |

| Wait Delay Falling<br>from WE (max) | t∨(WT-<br>WE)  | tWLWTV         | 35                           | 35                           | 35                           | N/A                     |

| WE High from Wait<br>Release (min)  | tv(WT)         | tWTHWH         | 0                            | 0                            | 0                            | N/A                     |

| Wait Width Time<br>(max)            | tw(WT)         | wWTLWTH        | 350                          | 350                          | 350                          | N/A                     |

Table 15: PC Card Memory Mode Common Memory Write AC Characteristics

Figure 7: PC Card Memory Mode Common Memory Write Timing Diagram

# 3.3.5 PC Card I/O Mode Read AC Characteristics

| Parameter                                | Symbol       | IEEE<br>Symbol | 250 ns Cycle<br>Time Mode | 120 ns Cycle<br>Time Mode | 100 ns Cycle<br>Time Mode | 80 ns Cycle<br>Time Mode |

|------------------------------------------|--------------|----------------|---------------------------|---------------------------|---------------------------|--------------------------|

| Data Delay<br>after<br>-IORD (max)       | td(IORD)     | tIGLQV         | 100                       | 50                        | 50                        | 45                       |

| Data Hold<br>following -IORD<br>(min)    | th(IORD)     | tIGHQX         | 0                         | 5                         | 5                         | 5                        |

| -IORD Width<br>Time (min)                | tw(IORD)     | tIGLIGH        | 165                       | 70                        | 65                        | 55                       |

| Address Setup<br>before -IORD<br>(min)   | tsuA(IORD)   | tAVIGL         | 70                        | 25                        | 25                        | 15                       |

| Address Hold<br>following -IORD<br>(min) | thA(IORD)    | tIGHAX         | 20                        | 10                        | 10                        | 10                       |

| -CE Setup<br>before -IORD<br>(min)       | tsuCE(IORD)  | tELIGL         | 5                         | 5                         | 5                         | 5                        |

| -CE Hold<br>following -IORD              | thCE(IORD)   | tIGHEH         | 20                        | 10                        | 10                        | 10                       |

| -REG Setup<br>before -IORD<br>(min)      | tsuREG(IORD) | tRGLIGL        | 5                         | 5                         | 5                         | 5                        |

| -REG Hold<br>following –<br>IORD (min)   | thREG(IORD)  | tIGHRGH        | 0                         | 0                         | 0                         | 0                        |

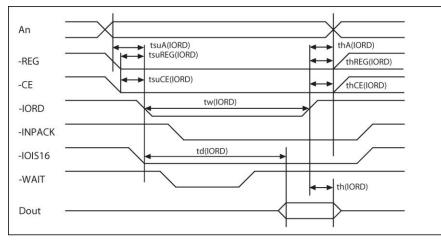

Table 16: PC Card I/O Mode Read AC Characteristics

Figure 8: PC Card I/O Mode Read Timing Diagram

# 3.3.6 PC Card I/O Mode Write AC Characteristics

| Parameter                                | Symbol       | IEEE<br>Symbol | 250 ns<br>Cycle Time<br>Mode | 120 ns<br>Cycle Time<br>Mode | 100 ns<br>Cycle Time<br>Mode | 80 ns Cycle<br>Time Mode |

|------------------------------------------|--------------|----------------|------------------------------|------------------------------|------------------------------|--------------------------|

| Data Setup<br>before -IOWR<br>(min)      | tsu(IOWR)    | tDVIWH         | 60                           | 20                           | 20                           | 15                       |

| Data Hold<br>following -IOWR<br>(min)    | th(IOWR)     | tIWHDX         | 30                           | 10                           | 5                            | 5                        |

| -IOWR Width<br>Time (min)                | tw(IOWR)     | tIWLIWH        | 165                          | 70                           | 65                           | 55                       |

| Address Setup<br>before -IOWR<br>(min)   | tsuA(IOWR)   | tAVIWL         | 70                           | 25                           | 25                           | 15                       |

| Address Hold<br>following –IOWR<br>(min) | thA(IOWR)    | tIWHAX         | 20                           | 20                           | 10                           | 10                       |

| -CE Setup before<br>-IOWR (min)          | tsuCE(IOWR)  | tELIWL         | 5                            | 5                            | 5                            | 5                        |

| -CE Hold<br>following -IOWR<br>(min)     | thCE(IOWR)   | tIWHEH         | 20                           | 20                           | 10                           | 10                       |

| -REG Setup<br>before -IOWR<br>(min)      | tsuREG(IOWR) | tRGLIWL        | 5                            | 5                            | 5                            | 5                        |

| -REG Hold<br>following -IOWR<br>(min)    | thREG(IOWR)  | tIWHRGH        | 0                            | 0                            | 0                            | 0                        |

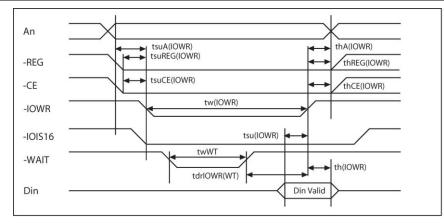

Table 17: PC Card I/O Mode Write AC Characteristics

Figure 9: PC Card I/O Mode Read Timing Diagram

# 3.3.7 True IDE Mode Register Access

| Parameter                                      | Symbol | Mode0 | Mode1 | Mode2 | Mode3 | Mode4 | Mode5 | Mode6 | Unit |

|------------------------------------------------|--------|-------|-------|-------|-------|-------|-------|-------|------|

| Cycle time (min)                               | tO     | 600   | 383   | 330   | 180   | 120   | 100   | 80    | ns   |

| Address valid to<br>-IORD/-IOWR<br>(min) setup | t1     | 70    | 50    | 30    | 30    | 25    | 15    | 10    | ns   |

| -IORD/-IOWR<br>pulse width 8bit<br>(min)       | t2     | 290   | 290   | 290   | 80    | 70    | 65    | 55    | ns   |

| -IORD/-IOWR<br>recovery time<br>(min)          | t2i    | _     | _     | _     | 70    | 25    | 25    | 20    | ns   |

| -IOWR data<br>setup (min)                      | t3     | 60    | 45    | 30    | 30    | 20    | 20    | 15    | ns   |

| -IOWR data<br>hold (min)                       | t4     | 30    | 20    | 15    | 10    | 10    | 5     | 5     | ns   |

| -IORD data<br>setup (min)                      | t5     | 50    | 35    | 20    | 20    | 20    | 15    | 10    | ns   |

| -IORD data hold<br>(min)                       | t6     | 5     | 5     | 5     | 5     | 5     | 5     | 5     | ns   |

| -IORD data<br>tristate (max)                   | t6z    | 30    | 30    | 30    | 30    | 30    | 20    | 20    | ns   |

| Addresses valid<br>to -IOCS16<br>assert. (max) | t7     | 90    | 50    | 40    | N/A   | N/A   | N/A   | N/A   | ns   |

| Address valid to<br>-IOCS16<br>release (max)   | t8     | 60    | 45    | 30    | N/A   | N/A   | N/A   | N/A   | ns   |

| -IORD/-IOWR to<br>address valid<br>hold        | t9     | 20    | 15    | 10    | 10    | 10    | 10    | 10    | ns   |

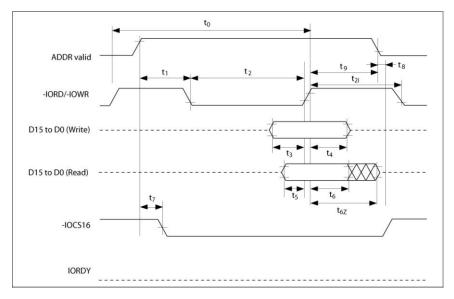

Table 18: True IDE Mode Register Access AC Characteristics

# 3.3.8 True IDE Mode PIO Access

| Parameter                                      | Symbol | Mode0 | Mode1 | Mode2 | Mode3 | Mode4 | Mode5 | Mode6 | Unit |

|------------------------------------------------|--------|-------|-------|-------|-------|-------|-------|-------|------|

| Cycle time (min)                               | tO     | 600   | 383   | 330   | 180   | 120   | 100   | 80    | ns   |

| Address valid to<br>-IORD/-IOWR<br>(min) setup | t1     | 70    | 50    | 30    | 30    | 25    | 15    | 10    | ns   |

| -IORD/-IOWR<br>pulse width 8bit<br>(min)       | t2     | 290   | 290   | 290   | 80    | 70    | 65    | 55    | ns   |

| -IORD/-IOWR<br>recovery time<br>(min)          | t2i    | _     | _     | _     | 70    | 25    | 25    | 20    | ns   |

| -IOWR data<br>setup (min)                      | t3     | 60    | 45    | 30    | 30    | 20    | 20    | 15    | ns   |

| -IOWR data<br>hold (min)                       | t4     | 30    | 20    | 15    | 10    | 10    | 5     | 5     | ns   |

| -IORD data<br>setup (min)                      | t5     | 50    | 35    | 20    | 20    | 20    | 15    | 10    | ns   |

| -IORD data hold<br>(min)                       | t6     | 5     | 5     | 5     | 5     | 5     | 5     | 5     | ns   |

| -IORD data<br>tristate (max)                   | t6z    | 30    | 30    | 30    | 30    | 30    | 20    | 20    | ns   |

| Addresses valid<br>to -IOCS16<br>assert. (max) | t7     | 90    | 50    | 40    | N/A   | N/A   | N/A   | N/A   | ns   |

| Address valid to -IOCS16 release               | t8     | 60    | 45    | 30    | N/A   | N/A   | N/A   | N/A   | ns   |

| -IORD/-IOWR to<br>address valid<br>hold        | t9     | 20    | 15    | 10    | 10    | 10    | 10    | 10    | ns   |

Table 19: True IDE Mode PIO Access AC Characteristics

Figure 10: True IDE Mode PIO Access Timing Diagram

# 3.3.9 True IDE Mode Multiword DMA (not used for part numbers with P)

| Parameter                           | Symbol          | Mode 0 | Mode 1 | Mode 2 | Mode 3 | Mode 4 | Unit |

|-------------------------------------|-----------------|--------|--------|--------|--------|--------|------|

| Cycle time (min)                    | to              | 480    | 150    | 120    | 100    | 80     | ns   |

| -IORD/-IOWR Asserted Pulse<br>(min) | t <sub>D</sub>  | 215    | 80     | 70     | 65     | 55     | ns   |

| -IORD data access (max)             | t <sub>E</sub>  | 150    | 60     | 50     | 50     | 45     | ns   |

| -IORD data hold (min)               | t <sub>F</sub>  | 5      | 5      | 5      | 5      | 5      | ns   |

| -IORD/-IOWR data setup<br>(min)     | t <sub>G</sub>  | 100    | 30     | 20     | 15     | 10     | ns   |

| -IOWR data hold (min)               | tн              | 20     | 15     | 10     | 5      | 5      | ns   |

| DMACK to<br>-IORD/-IOWR setup (min) | tı              | 0      | 0      | 0      | 0      | 0      | ns   |

| -IORD/-IOWR to DMACK hold (min)     | tj              | 20     | 5      | 5      | 5      | 5      | ns   |

| -IORD negated pulse width (max)     | t <sub>KR</sub> | 50     | 50     | 25     | 25     | 20     | ns   |

| -IOWR negated pulse width<br>(min)  | t <sub>KW</sub> | 215    | 50     | 25     | 25     | 20     | ns   |

| -IORD to DMARQ delay (max)          | t <sub>LR</sub> | 120    | 40     | 35     | 35     | 35     | ns   |

| -IOWR to DMARQ delay<br>(max)       | t <sub>LW</sub> | 40     | 40     | 35     | 35     | 35     | ns   |

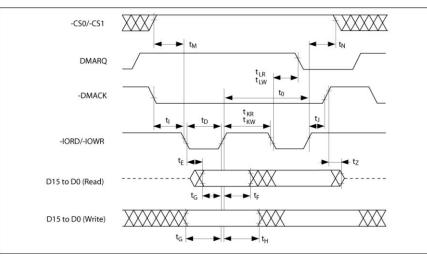

Table 20: True IDE Mode Multiword DMA AC Characteristics

Figure 11: True IDE Mode Multiword DMA Timing Diagram

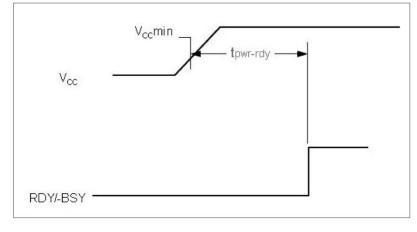

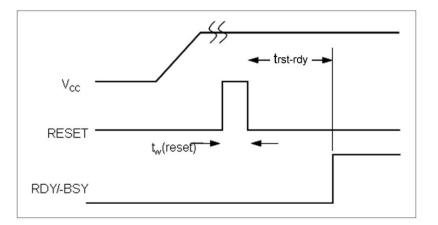

# 3.4 PC Card Memory and I/O Modes Power Up to READY and RESET to READY

| Parameter                | Symbol                 | Capacity | Min    | Тур  | Мах  | Unit |

|--------------------------|------------------------|----------|--------|------|------|------|

|                          |                        | 128MB    | 0.069  | 70   | 71   | ms   |

|                          | +                      | 256MB    | 0.073  | 73.8 | 74.1 | ms   |

| Power up to READY        | t <sub>rdy</sub>       | 512MB    | 0.0702 | 70.3 | 70.3 | ms   |

|                          |                        | 1GB      | 0.069  | 69.2 | 69.5 | ms   |

| RESET to READY           |                        | 128MB    | 0.048  | 48   | 48   | ms   |

|                          | +                      | 256MB    | 0.0521 | 52.1 | 52.2 | ms   |

|                          | t <sub>rdy</sub>       | 512MB    | 0.0483 | 48.3 | 48.5 | ms   |

|                          |                        | 1GB      | 0.0469 | 47.1 | 47.3 | ms   |

| Minimum Rec. Reset Width | T <sub>w</sub> (reset) | -        | 0.200  | -    | -    | ms   |

Table 21: Power Up to READY and RESET to READY AC Characteristics

Figure 12: Power Up to RDY Timing

Figure 13: RESET to RDY Timing

# 4.0 Host Access Specification

#### 4.1 Task File Register and Byte/Word/Odd-Byte Mode Mappings

Please refer to the CF Card standards for complete details on:

- Task File Register mapping for the interface modes

- Byte/Word/Odd-byte mode mapping within each of the interface modes

#### 4.2 Host Access Interface Modes

The host can access the CF Card by using the following interface modes with the Task Registers:

- PC Card Memory Mode, Attribute Memory

The Card Information Structure (CIS) in Attribute Memory can be accessed by Byte/Word/Odd-byte

modes in PC Card Memory Mode. The -REG signal must be asserted when accessing Attribute

Memory. The CF Card is mapped to PC Card Memory Mode by the Index bits in the Configuration

Option Register. An example of a CIS is listed in 4.3, Card Information Structure (CIS).

- PC Card Memory Mode, Common Memory Common Memory can be accessed in the Byte/Word/Odd Byte modes in PC Card Memory Mode. The -REG signal must be de-asserted when accessing the Common Memory. The CF Card is mapped to PC Card Memory Mode by the Index bits in the Configuration Option Register

- 3. PC Card I/O Mode

The CF Card can be accessed by Byte/Word/Odd Byte modes in PC Card I/O Mode. The CF Card is mapped to PC Card I/O Mode by the Index bits in the Configuration Option Register. The Index bits also select Contiguous I/O, Primary I/O, or Secondary I/O mapping when using the PC Card I/O Mode.

4. True-IDE mode

The CF Card is configured in a True IDE Mode of operation when the -ATASEL input signal is asserted GND by the host at power up. In the True IDE Mode, Attribute Registers are not accessible from the host. The Data Register is accessed in word (16-bit) mode at power up. The CF Card permits 8-bit accesses if the host issues a Set Feature Command to put the CF Card in 8-bit mode. Parameter information that the CF Card uses in True IDE mode is returned when the Identify Drive command (ECh) is invoked. Refer to 4.4 Identify Drive Parameter Information for an example.

# 4.3 Card Information Structure (CIS)

The CF Card uses a Card Information Structure (CIS) as summarized below:

- 0000: Code 01, link 03 D9 01 FF Tuple CISTPL\_DEVICE (01), length 3 (03) at offset 0

- Device type is FUNCSPEC

- Device speed is 250ns

- Write protect switch is not in control

- Device size is 2K bytes

- 0005: Code 1C, link 04

03 D9 01 FF

Tuple CISTPL\_DEVICE\_OC (1C), length 4 (04) at offset 5

- Device conditions: minimum cycle with WAIT at Vcc = 3.3V

- Device type is FUNCSPEC

- Device speed is 250ns

- Write protect switch is not in control

- Device size is 2K bytes

- 000B: Code 18, link 02 DF 01 Tuple CISTPL\_JEDEC\_C (18), length 2 (02) at offset B

- Device 0 JEDEC id: Manufacturer DF, ID 01

- 000F: Code 20, link 04 4D 01 00 01 Tuple CISTPL\_MANFID (20), length 4 (04) at offset F

- Manufacturer # 0x014D hardware rev 1.00

- 0015: Code 15, link 13 04 01 53 54 49 00 46 6C 61 73 68 20 37 2E 30 2E 30 00 FF Tuple CISTPL\_VERS\_1 (15), length 19 (13) at offset 15

- Major version 4, minor version 1

- Product Information: "STI" (Manufacuturer) "Flash X.Y.Z" (Product Name)

- 002A: Code 21, link 02 04 /xx 01 Tuple CISTPL\_FUNCID (21), length 2 (02) at offset 2A

- Function code 04 (Fixed), or xx (Removable), system init 01

- 002E: Code 22, link 02 01 01 Tuple CISTPL\_FUNCE (22), length 2 (02) at offset 2E

- This is an PC Card ATA Disk

- 0032: Code 22, link 03 02 0C 0F Tuple CISTPL\_FUNCE (22), length 3 (03) at offset 32

- Vpp is not required

- This is a silicon device

- Identify Drive Model/Serial Number is guaranteed unique

- Low-Power Modes supported: Sleep Standby Idle

- Drive automatically minimizes power

- All modes include 3F7 or 377

- Index bit is not supported

- -IOIS16 is unspecified in Twin configurations

- 0037: Code 1A, link 05

01 03 00 02 0F

Tuple CISTPL\_CONFIG (1A), length 5 (05) at offset 37

- Last valid configuration index is 3

- Configuration Register Base Address is 200

- Configuration Registers Present:

- Configuration Option Register at 200

- Card Configuration and Status Register at 202

- Pin Replacement Register at 204

- Socket and Copy Register at 206

- 003E: Code 1B, link 08

C0 C0 A1 01 55 08 00 20

Tuple CISTPL\_CFTABLE\_ENTRY (1B), length 8 (08) at offset 3E

- Configuration Table Index is 00 (default)

- Interface type is Memory

- BVDs not active, WP not active, RdyBsy active

- Wait signal support required

- Vcc Power Description: Nom V = 5.0 V