# HIGH SPEED 32K x 8 CMOS EPROM

## **KEY FEATURES**

- Fast Access Time

- $t_{ACC} = 35 \text{ ns}$

- $t_{CE} = 35 \text{ ns}$

- Low Power Consumption

- 200  $\mu$ A Standby I $_{CC}$

- Immune to Latch-UP

- Up to 200 mA

- ESD Protection Exceeds 2000 Volts

- Available in 300 Mil DIP and PLDCC

- DESC SMD No. 5962-86063

#### GENERAL DESCRIPTION

The WS57C256F is a High Performance 32K x 8 UV Erasable EPROM. It is manufactured using an advanced CMOS process technology enabling it to operate at speeds as fast as 35 ns Address Access Time ( $t_{ACC}$ ) and 35 ns Chip Enable Time ( $t_{CE}$ ). It was designed utilizing WSI's patented self-aligned split gate EPROM cell, resulting in a low power device with a very cost effective die size. The low standby power capability of this 256 K product (200  $\mu$ A in a CMOS interface environment) is especially attractive.

This product, with its high speed capability, is particularly appropriate for use with today's fast DSP processors and high-clock-rate Microprocessors. The WS57C256F's 35 ns speed enables these advanced processors to operate without introducing any undesirable wait states. The WS57C256F is also ideal for use in modem applications, and is recommended for use in these applications by the leading modem chip set manufacturer.

The WS57C256F is available in a variety of package types including the space saving 300 Mil DIP, the surface mount PLDCC, and other windowed and non-windowed options. And its standard JEDEC EPROM pinouts provide for automatic upgrade density paths for current 64K and 128K EPROM users.

## **MODE SELECTION**

| PINS<br>MODE           | CE/<br>PGM      | ŌĒ              | A <sub>9</sub>  | A <sub>0</sub> | V <sub>PP</sub>              | v <sub>CC</sub> | OUTPUTS           |

|------------------------|-----------------|-----------------|-----------------|----------------|------------------------------|-----------------|-------------------|

| Read                   | VIL             | VIL             | Х               | Х              | Vсс                          | Vсс             | D <sub>OUT</sub>  |

| Output<br>Disable      | Х               | V <sub>IH</sub> | Х               | Х              | Vсс                          | Vcc             | High Z            |

| Standby                | VIH             | Х               | Х               | Х              | Vcc                          | Vcc             | High Z            |

| Program                | $V_{IL}$        | ٧ <sub>IH</sub> | Х               | Х              | $V_{PP}^2$                   | Vcc             | D <sub>IN</sub>   |

| Program<br>Verify      | Х               | V <sub>IL</sub> | Х               | Х              | V <sub>PP</sub> <sup>2</sup> | Vcc             | DOUT              |

| Program<br>Inhibit     | V <sub>IH</sub> | VIH             | Х               | Х              | V <sub>PP</sub> <sup>2</sup> | Vсс             | High Z            |

| Signature <sup>3</sup> | $V_{IL}$        | VIL             | $V_H^2$         | $V_{IL}$       | Vcc                          | Vcc             | 23 H <sup>4</sup> |

| Signature              | VIL             | VIL             | VH <sup>2</sup> | VIH            | Vcc                          | Vсс             | EO H <sup>5</sup> |

#### NOTES:

- 1. X can be  $V_{IL}$  or  $V_{IH}$ .

- 2.  $V_{IH} = V_{PP} = 12.75 \pm 0.25 \text{ V}.$

- Device Signature.

4. Manufacturer Signature.

3. A1 - A8,  $A10 - A14 = V_{II}$ .

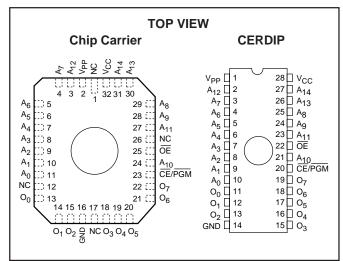

## PIN CONFIGURATION

## **PRODUCT SELECTION GUIDE**

| PARAMETER                 | WS57C256F-35 | WS57C256F-45 | WS57C256F-55 | WS57C256F-70 |

|---------------------------|--------------|--------------|--------------|--------------|

| Address Access Time (Max) | 35 ns        | 45 ns        | 55 ns        | 70 ns        |

| Output Enable Time (Max)  | 15 ns        | 20 ns        | 25 ns        | 30 ns        |

## **ABSOLUTE MAXIMUM RATINGS\***

| Storage Temperature65° to + 150°C                         |

|-----------------------------------------------------------|

| Voltage on any Pin with                                   |

| Respect to Ground0.6V to +7V                              |

| $V_{PP}$ and $A_{9}$ with Respect to Ground–0.6V to + 14V |

| ESD Protection>2000\                                      |

## \*NOTICE:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

## **OPERATING RANGE**

| RANGE      | TEMPERATURE     | V <sub>CC</sub> |  |  |

|------------|-----------------|-----------------|--|--|

| Commercial | 0°C to +70°C    | +5V ± 10%       |  |  |

| Industrial | -40°C to +85°C  | +5V ± 10%       |  |  |

| Military   | −55°C to +125°C | +5V ± 10%       |  |  |

# **DC READ CHARACTERISTICS** Over Operating Range with $V_{PP} = V_{CC}$

| SYMBOL           | PARAMETER                                | TEST CONDIT                                                     | MIN     | MAX                  | UNITS                 |    |

|------------------|------------------------------------------|-----------------------------------------------------------------|---------|----------------------|-----------------------|----|

| $V_{IL}$         | Input Low Voltage                        | (Note 4)                                                        | -0.1    | 0.8                  | V                     |    |

| $V_{IH}$         | Input High Voltage                       | (Note 4)                                                        |         | 2.0                  | V <sub>CC</sub> + 0.3 | V  |

| V <sub>OL</sub>  | Output Low Voltage                       | I <sub>OL</sub> = 16 mA                                         |         |                      | 0.4                   | V  |

| V <sub>OH</sub>  | Output High Voltage                      | $I_{OH} = -4 \text{ mA}$                                        |         | 2.4                  |                       | V  |

|                  | V <sub>CC</sub> Standby Current (CMOS)   | $\overline{\text{CE}} = \text{V}_{\text{CC}} \pm 0.3 \text{ V}$ | Comm'l  |                      | 200                   | μΑ |

| I <sub>SB1</sub> | V <sub>CC</sub> Standby Current (CiviOS) | (Note 1)                                                        | Ind/Mil |                      | 500                   | μΑ |

| I <sub>SB2</sub> | V <sub>CC</sub> Standby Current (TTL)    | $\overline{CE} = V_{IH} $ (Note 2)                              | Comm'l  |                      | 3                     | mA |

| 'SB2             | V <sub>CC</sub> Standby Suitent (112)    | OL = V <sub>III</sub> (Note 2)                                  | Ind/Mil |                      | 5                     | mA |

| I <sub>CC1</sub> | V <sub>CC</sub> Active Current (CMOS)    | (Notes 1 and 3)                                                 | Comm'l  |                      | 25                    | mA |

| 'CC1             | vee nouve ourient (owled)                | Outputs Not Loaded                                              | Ind/Mil |                      | 30                    | mA |

|                  | V <sub>CC</sub> Active Current (TTL)     | (Notes 2 and 3)                                                 | Comm'l  |                      | 50                    | mA |

| I <sub>CC2</sub> | V <sub>CC</sub> Active Current (11L)     | Outputs Not Loaded                                              | Ind/Mil |                      | 60                    | mA |

| I <sub>PP</sub>  | V <sub>PP</sub> Supply Current           | $V_{PP} = V_{CC}$                                               |         |                      | 100                   | μΑ |

| V <sub>PP</sub>  | V <sub>PP</sub> Read Voltage             |                                                                 |         | V <sub>CC</sub> −0.4 | V <sub>cc</sub>       | V  |

| I <sub>LI</sub>  | Input Leakage Current                    | $V_{IN} = 5.5V$ or Gnd                                          |         | -10                  | 10                    | μΑ |

| I <sub>LO</sub>  | Output Leakage Current                   | $V_{OUT} = 5.5 \text{ V or Gnd}$                                |         | -10                  | 10                    | μA |

NOTES:

- 1. CMOS inputs: GND  $\pm$  0.3V or  $V_{CC}$   $\pm$  0.3V.

- 2. TTL inputs:  $V_{IL} \le 0.8V$ ,  $V_{IH} \ge 2.0V$ .

- 3. Add 3 mA/MHz for A.C. power component.

- These are absolute voltages with respect to device ground pin and include all overshoots due to system and/or tester noise.

Do not attempt to test these values without suitable equipment.

## **AC READ CHARACTERISTICS** Over Operating Range. with $V_{PP} = V_{CC}$

| PARAMETER                      | SYMBOL           | 57C256F-35 |     | 57C256F-45 |     | 57C256F-55 |     | 57C256F-70 |     | UNITS |

|--------------------------------|------------------|------------|-----|------------|-----|------------|-----|------------|-----|-------|

| I ANAMETER                     | O'IMBOL          | MIN        | MAX | MIN        | MAX | MIN        | MAX | MIN        | MAX | OMITO |

| Address to Output Delay        | t <sub>ACC</sub> |            | 35  |            | 45  |            | 55  |            | 70  |       |

| CE to Output Delay             | t <sub>CE</sub>  |            | 35  |            | 45  |            | 55  |            | 70  |       |

| OE to Output Delay             | t <sub>OE</sub>  |            | 15  |            | 20  |            | 25  |            | 30  | ns    |

| Output Disable to Output Float | t <sub>DF</sub>  |            | 20  |            | 20  |            | 25  |            | 30  |       |

| Address to Output Hold         | t <sub>ОН</sub>  | 0          |     | 0          |     | 0          |     | 0          |     |       |

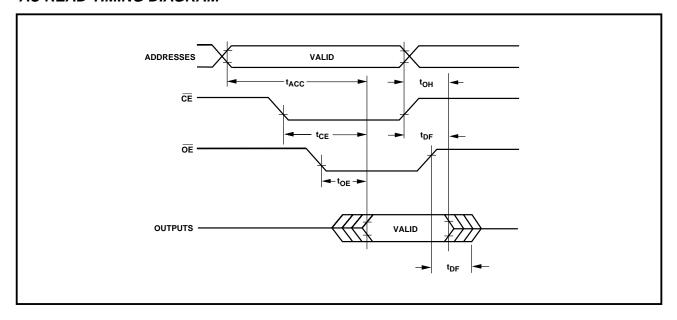

## AC READ TIMING DIAGRAM

## **CAPACITANCE**(5) $T_A = 25$ °C, f = 1 MHz

| SYMBOL           | PARAMETER                   | CONDITIONS            | TYP <sup>(6)</sup> | MAX | UNITS |

|------------------|-----------------------------|-----------------------|--------------------|-----|-------|

| C <sub>IN</sub>  | Input Capacitance           | $V_{IN} = 0V$         | 4                  | 6   | pF    |

| C <sub>OUT</sub> | Output Capacitance          | V <sub>OUT</sub> = 0V | 8                  | 12  | pF    |

| C <sub>VPP</sub> | V <sub>PP</sub> Capacitance | V <sub>PP</sub> = 0 V | 18                 | 25  | pF    |

NOTES: 5. This parameter is only sampled and is not 100% tested.

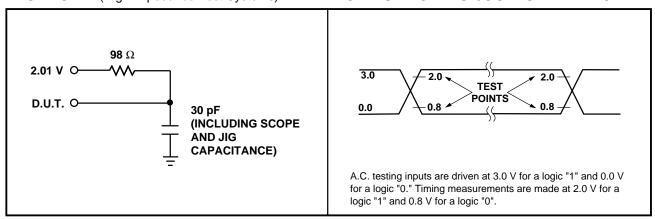

## TEST LOAD (High Impedance Test Systems)

## A.C. TESTING INPUT/OUTPUT WAVEFORM

NOTE: 7. Provide adequate decoupling capacitance as close as possible to this device to achieve the published A.C. and D.C. parameters.

A 0.1 microfarad capacitor in parallel with a 0.01 microfarad capacitor connected between V<sub>CC</sub> and ground is recommended.

Inadequate decoupling may result in access time degradation or other transient performance failures.

<sup>6.</sup> Typical values are for  $T_A = 25$ °C and nominal supply voltages.

## PROGRAMMING INFORMATION

**DC CHARACTERISTICS** ( $T_A = 25 \pm 5^{\circ}C$ ,  $V_{CC} = 6.25 \text{ V} \pm 0.25 \text{ V}$ ,  $V_{PP} = 12.75 \pm 0.25 \text{ V}$ )

| SYMBOLS         | PARAMETER                                                                              | MIN | MAX | UNITS |

|-----------------|----------------------------------------------------------------------------------------|-----|-----|-------|

| lu              | Input Leakage Current $(V_{IN} = V_{CC} \text{ or Gnd})$                               | -10 | 10  | μA    |

| Ірр             | V <sub>PP</sub> Supply Current During<br>Programming Pulse (CE/PGM = V <sub>IL</sub> ) |     | 60  | mA    |

| I <sub>cc</sub> | V <sub>CC</sub> Supply Current (Note 8)                                                |     | 35  | mA    |

| V <sub>OL</sub> | Output Low Voltage During Verify (I <sub>OL</sub> = 16 mA)                             |     | 0.4 | V     |

| Vон             | Output High Voltage During Verify $(I_{OH} = -4 \text{ mA})$                           | 2.4 |     | V     |

NOTE: 8. V<sub>CC</sub> must be applied either coincidentally or before V<sub>PP</sub> and removed either coincidentally or after V<sub>PP</sub>.

- 9. V<sub>PP</sub> must not be greater than 13 volts including overshoot. During  $\overline{CE} = \overline{PGM} = V_{IL}$ ,  $V_{PP}$  must not be switched from 5 volts to 12.5 volts or vice-versa.

- 10. During power up the  $\overline{PGM}$  pin must be brought high ( $\geq V_{IH}$ ) either coincident with or before power is applied to  $V_{PP}$ .

## **AC CHARACTERISTICS** $(T_A = 25 \pm 5^{\circ}C, V_{CC} = 6.25 \text{ V} \pm 0.25 \text{ V}, V_{PP} = 12.75 \pm 0.25 \text{ V})$

| SYMBOLS                           | PARAMETER                                | MIN | TYP | MAX | UNITS |

|-----------------------------------|------------------------------------------|-----|-----|-----|-------|

| t <sub>AS</sub>                   | Address Setup Time                       | 2   |     |     | μs    |

| t <sub>сон</sub>                  | CE High to OE High                       | 2   |     |     | μs    |

| t <sub>OES</sub>                  | Output Enable Setup Time                 | 2   |     |     | μs    |

| t <sub>OS</sub>                   | Data Setup Time                          | 2   |     |     | μs    |

| t <sub>AH</sub>                   | Address Hold Time                        | 0   |     |     | μs    |

| t <sub>OH</sub>                   | Data Hold Time                           | 2   |     |     | μs    |

| t <sub>DF</sub>                   | Chip Disable to Output Float Delay       | 0   |     | 130 | ns    |

| t <sub>OE</sub>                   | Data Valid From Output Enable            |     |     | 130 | ns    |

| t <sub>VS</sub> /t <sub>CES</sub> | V <sub>PP</sub> Setup Time/CE Setup Time | 2   |     |     | μs    |

| t <sub>PW</sub>                   | PGM Pulse Width                          | 100 |     | 200 | μs    |

| tocx                              | OE Low to CE "Don't Care"                | 2   |     |     | μs    |

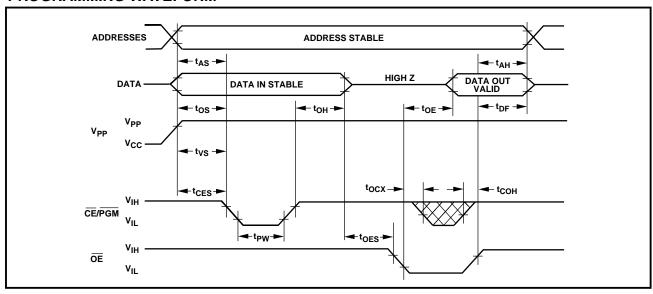

## PROGRAMMING WAVEFORM

## ORDERING INFORMATION

| PART NUMBER      | SPEED<br>(ns) | PACKAGE<br>TYPE          | PACKAGE<br>DRAWING | OPERATING<br>TEMPERATURE<br>RANGE | WSI<br>MANUFACTURING<br>PROCEDURE |

|------------------|---------------|--------------------------|--------------------|-----------------------------------|-----------------------------------|

| WS57C256F-35C    | 35            | 32 Pad CLLCC             | C2                 | Comm'l                            | Standard                          |

| WS57C256F-35D    | 35            | 28 Pin CERDIP, 0.6"      | D2                 | Comm'l                            | Standard                          |

| WS57C256F-35J    | 35            | 32 Pin PLDCC             | J4                 | Comm'l                            | Standard                          |

| WS57C256F-35L    | 35            | 32 Pin CLDCC             | L3                 | Comm'l                            | Standard                          |

| WS57C256F-35P    | 35            | 28 Pin Plastic DIP, 0.6" | P3                 | Comm'l                            | Standard                          |

| WS57C256F-35T    | 35            | 28 Pin CERDIP, 0.3"      | T2                 | Comm'l                            | Standard                          |

| WS57C256F-45C    | 45            | 32 Pad CLLCC             | C2                 | Comm'l                            | Standard                          |

| WS57C256F-45D    | 45            | 28 Pin CERDIP, 0.6"      | D2                 | Comm'l                            | Standard                          |

| WS57C256F-45P    | 45            | 28 Pin Plastic DIP, 0.6" | P3                 | Comm'l                            | Standard                          |

| WS57C256F-45T    | 45            | 28 Pin CERDIP, 0.3"      | T2                 | Comm'l                            | Standard                          |

| WS57C256F-55C    | 55            | 32 Pad CLLCC             | C2                 | Comm'l                            | Standard                          |

| WS57C256F-55CMB  | 55            | 32 Pad CLLCC             | C2                 | Military                          | MIL-STD-883C                      |

| WS57C256F-55D    | 55            | 28 Pin CERDIP, 0.6"      | D2                 | Comm'l                            | Standard                          |

| WS57C256F-55DM   | 55            | 28 Pin CERDIP, 0.6"      | D2                 | Military                          | Standard                          |

| WS57C256F-55DMB  | 55            | 28 Pin CERDIP, 0.6"      | D2                 | Military                          | MIL-STD-883C                      |

| WS57C256F-55J    | 55            | 32 Pin PLDCC             | J4                 | Comm'l                            | Standard                          |

| WS57C256F-55L    | 55            | 32 Pin CLDCC             | L3                 | Comm'l                            | Standard                          |

| WS57C256F-55P    | 55            | 28 Pin Plastic DIP, 0.6" | P3                 | Comm'l                            | Standard                          |

| WS57C256F-55T    | 55            | 28 Pin CERDIP, 0.3"      | T2                 | Comm'l                            | Standard                          |

| WS57C256F-55TMB  | 55            | 28 Pin CERDIP, 0.3"      | T2                 | Military                          | MIL-STD-883C                      |

| WS57C256F-70CMB* | 70            | 32 Pad CLLCC             | C2                 | Military                          | MIL-STD-883C                      |

| WS57C256F-70D    | 70            | 28 Pin CERDIP, 0.6"      | D2                 | Comm'l                            | Standard                          |

| WS57C256F-70DMB* | 70            | 28 Pin CERDIP, 0.6"      | D2                 | Military                          | MIL-STD-883C                      |

| WS57C256F-70J    | 70            | 32 Pin PLDCC             | J4                 | Comm'l                            | Standard                          |

| WS57C256F-70JI   | 70            | 32 Pin PLDCC             | J4                 | Industrial                        | Standard                          |

| WS57C256F-70T    | 70            | 28 Pin CERDIP, 0.3"      | T2                 | Comm'l                            | Standard                          |

NOTE: 11. The actual part marking will not include the initials "WS."

Return to Main Menu

# PROGRAMMING/ALGORITHMS/ERASURE/PROGRAMMERS

REFER TO PAGE 5-1

3-17

The WS57C256F is programmed using Algorithm D shown on page 5-9. When using Data I/O programmers, algorithm 57C256FB is recommended for use with the WS57C256F for best programming results.

<sup>\*</sup>SMD product. See section 4 for DESC SMD number.