# **HMMC-1002**

# DC-50 GHz Variable Attenuator

# **Data Sheet**

## **Description**

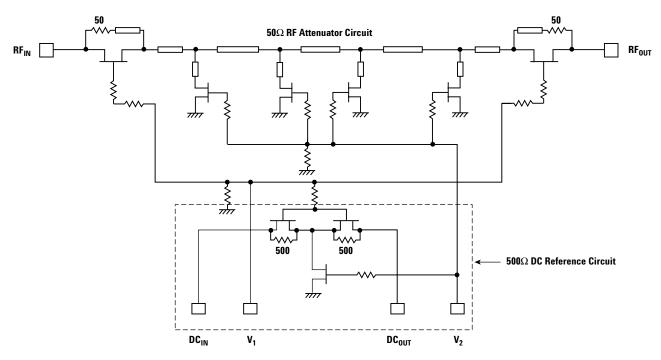

The HMMC-1002 is a monolithic, voltage variable, GaAs IC attenuator that operates from DC to 50 GHz. It is fabricated using MWTC's MMICB process which features an MBE epitaxial layer, backside ground vias, and FET gate lengths of approximately 0.4 mm. The variable resistive elements of the HMMC-1002 are two 750 mm wide series FETs and four 200 mm wide shunt FETs. The distributed topology of the HMMC-1002 minimizes the parasitic effects of its series and shunt FETs, allowing the HMMC-1002 to exhibit a wide dynamic range across its full bandwidth. An onchip DC reference circuit may be used to maintain optimum VSWR for any attenuation setting or to improve the attenuation versus voltage linearity of the attenuator circuit.

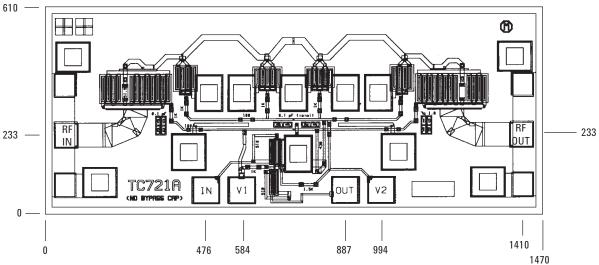

# TC721A N V1 COUT V2

Chip Size:  $1470 \times 610 \ \mu m \ (57.9 \times 24.0 \ mils)$

$\begin{array}{ll} \text{Chip Size Tolerance:} & \pm 10 \ \mu\text{m} \ (\pm 0.4 \ \text{mils}) \\ \text{Chip Thickness:} & 127 \pm 15 \ \mu\text{m} \ (5.0 \pm 0.6 \ \text{mils}) \\ \text{RF Pad Dimensions:} & 60 \times 70 \ \mu\text{m} \ (2.4 \times 2.8 \ \text{mils}), \ \text{or larger} \\ \text{DC Pad Dimensions:} & 75 \times 75 \ \mu\text{m} \ (3.0 \times 3.0 \ \text{mils}), \ \text{or larger} \\ \end{array}$

#### **Features**

• Specified Frequency Range:

DC-26.5 GHz

• Return Loss: 10 dB

• Minimum Attenuation: 2.0 dB

• Maximum Attenuation: 30.0 dB

# Absolute Maximum Ratings<sup>[1]</sup>

| Symbol             | Parameters/Conditions                  | Units | Min. | Max. |

|--------------------|----------------------------------------|-------|------|------|

| V <sub>DC-RF</sub> | DC Voltage to RF Ports                 | V     | -0.6 | +1.6 |

| V <sub>1</sub>     | V <sub>1</sub> Control Voltage         | V     | -5.0 | +0.5 |

| $\overline{V_2}$   | V <sub>2</sub> Control Voltage         | V     | -5.0 | +0.5 |

| V <sub>DC</sub>    | DC In/DC Out                           | V     | -0.6 | +1.0 |

| P <sub>IN</sub>    | RF Input Power                         | dBm   |      | 17   |

| T <sub>mina</sub>  | Min. Ambient Operating Temp.           | °C    | -55  |      |

| T <sub>maxa</sub>  | Max. Ambient Operating Temp.           | °C    |      | +125 |

| T <sub>stg</sub>   | Storage Temperature                    | °C    | -65  | +165 |

| T <sub>max</sub>   | Max. Assembly Temp. (for 60 sec. max.) | °C    |      | +300 |

### Notes:

# HMMC-1002 DC Specifications/Physical Properties, $T_{A}=25^{\circ}C$

| Symbol          | Parameters and Test Conditions                                                                                                        | Units | Min. | Тур. | Max. |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------|

| I <sub>V1</sub> | V <sub>1</sub> Control Current, (V <sub>1</sub> = -4V)                                                                                | mA    | 5.3  | 9.3  | 12   |

| I <sub>V2</sub> | V <sub>2</sub> Control Current, (V <sub>2</sub> = -4V)                                                                                | mA    | 5.3  | 9.3  | 12   |

| V <sub>P</sub>  | Pinch-Off Voltage, ( $V_2$ , $W/V_1 = 0V$ )<br>(Four 200 $\mu$ m wide shunt FETs, $V_{DD} = 1V$ @ RF <sub>in</sub> , $I_{DD} = 5$ mA) | V     | -0.6 | -1.3 | -2.5 |

# Electrical Specifications $^{[1]}$ , ${\rm T_A}={\rm 25^{\circ}C}$ , ${\rm Z_0}={\rm 50~\Omega}$

| Parameters and Test Conditions                                                                      | Units | Freq.<br>(GHz) | Min. | Тур. | Max. |

|-----------------------------------------------------------------------------------------------------|-------|----------------|------|------|------|

|                                                                                                     |       | 1.5            |      | 1.0  | 2.4  |

|                                                                                                     |       | 8.0            |      | 1.4  | 2.4  |

| Minimum Attenuation, $ S_{21}  V_1 = 0 V$ , $V_2 = -4 V$                                            | dB    | 20.00          |      | 1.7  | 2.4  |

|                                                                                                     |       | 26.5           |      | 2.0  | 2.4  |

|                                                                                                     |       | 50.0           |      | 3.9  |      |

| Input/Output Return Loss @ Min. Attenuation Setting,                                                | dB    | <26.5          | 10   | 16   |      |

| $(V_1 = 0 \text{ V}, V_2 = -4 \text{ V})$                                                           |       | <50.0          |      | 8    |      |

|                                                                                                     |       | 1.5            | 27   | 30   |      |

|                                                                                                     |       | 8.0            | 27   | 38   |      |

| Maximum Attenuation, $ S_{21} $ ( $V_1 = -4 V$ , $V_2 = 0 V$ )                                      | dB    | 20.0           | 27   | 38   |      |

|                                                                                                     |       | 26.5           | 27   | 40   |      |

|                                                                                                     |       | 50.0           |      | 35   |      |

| Input/Output Return Loss @ Max. Attenuation Setting,                                                | dB    | <26.5          | 8    | 10   |      |

| $V_1 = -4 \text{ V}, V_2 = 0 \text{ V}$                                                             |       | <50.0          |      | 10   |      |

| DC Power Dissipation, V <sub>1</sub> = -5 V, V <sub>2</sub> = -5 V (does not include input signals) | mW    |                |      |      | 152  |

#### Note

<sup>1.</sup> Operation in excess of any one of these conditions may result in damage to this device.

$<sup>1. \ \</sup> Attenuation \ is \ a \ positive \ number; \ whereas, \ S_{21} \ as \ measured \ on \ a \ Network \ Analyzer \ would \ be \ a \ negative \ number.$

#### **Application**

The HMMC-1002 is designed to be used as a gain control block in an ALC assembly. Because of its wide dynamic range and return loss performance, the HMMC-1002 may also be used as a broadband pulse modulator or single-pole single-throw, non-reflective switch.

## **Operation**

The attenuation value of the HMMC-1002 is adjusted by apply-ing negative voltage to  $V_2.$  At any attenuation setting, optimum VSWR is obtained by applying negative voltage to  $V_1.$  Applying negative voltage  $(V_2)$  to the gates of the shunt FETs sets the source-to-drain resistance and establishes the attenuation level. Applying negative voltage  $(V_1)$  to the gates of the series FETs optimizes the input and output match for different attenuation settings. In some applications, a single setting of  $V_1$  may provide sufficient input and output match over the desired attenuation range  $(V_1).$  For any HMMC-1002 the values of  $V_1$  may be adjusted so that the device attenuation versus voltage is monotonic for both  $V_1$  and  $V_2;$  however, this will slightly degrade the input and output return loss.

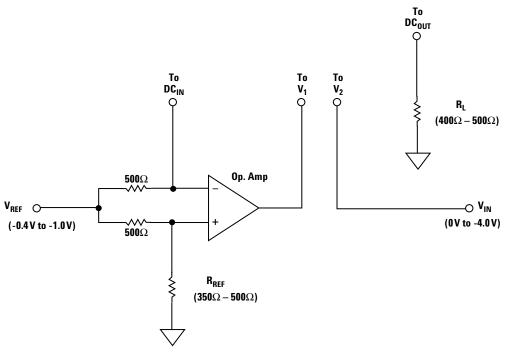

The attenuation and input/output match of the HMMC-1002 may also be controlled using only a single input voltage by utilizing the on-chip DC reference circuit and the driver circuit shown in Figure 4. This circuit optimizes VSWR for any attenuation setting.

Because of process variations, the values of  $V_{REF}$ ,  $R_{REF}$ , and  $R_L$  are different for each wafer if optimum performance is required. Typical values for these elements are given. The ratio of the resistors  $R_1$  and  $R_2$  determines the sensitivity of the attenuation versus voltage performance of the attenuator.

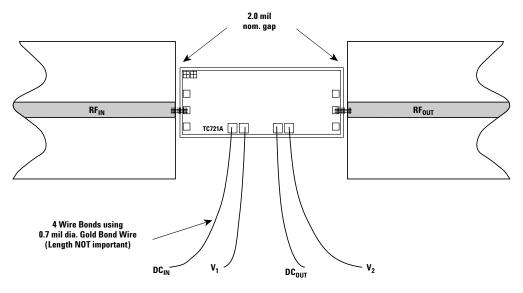

### **Assembly Techniques**

GaAs MMICs are ESD sensitive. ESD preventive measures must be employed in all aspects of storage, handling, and assembly. MMIC ESD precautions, handling considerations, die attach and bonding methods are critical fac-Figure tors in successful GaAs MMIC performance and reliability. Agilent application note #54, "GaAs MMIC ESD, Die Attach and Bonding Guidelines" provides basic information on these subjects.

## **Additional References:**

AN#31, "2–26.5 Variable Gain Amplifier Using HMMC-5021/22/26 and HMMC-1002 GaAs MMIC Components," AN#37, "HMMC-1002 Attenuator: Attenuation Control, "AN#44, "DC–50 GHz Variable Attenuator: S-Parameters," AN#45, "HMMC-1002 DC–50 GHz Variable Attenuator: Switching Speed Limitations, and PN#10, "HMMC-1002 50 GHz Attenuator 0–50 GHz Performance."

Figure 1. HMMC-1002 Schematic.

#### Notes:

- 1. All dimensions in microns and shown to center of bond pad.

- 2.  $DC_{in}$ , V1,  $DC_{out}$ , and  $V_2$  bonding pads are 75 x 75 microns.

- 3. RF input and output bonding pads are  $60 \times 70$  microns.

- 4. Chip thickness: 127  $\pm$  15  $\mu m$

Figure 2. HMMC-1002 Bonding Pad Locations.

Figure 3. HMMC-1002 Assembly Diagram.

Figure 4. Attenuator Driver.

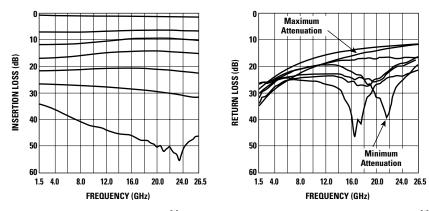

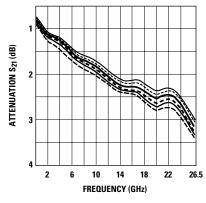

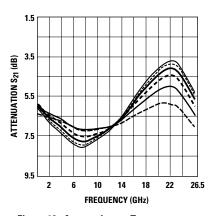

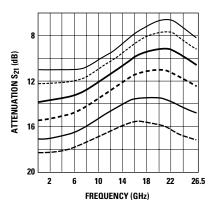

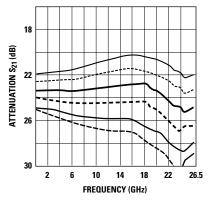

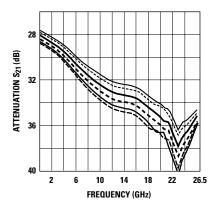

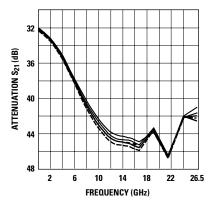

# **HMMC-1002 Typical Performance**

Figure 5. Attenuation vs. Frequency<sup>[1]</sup>.

Figure 6. Output Return Loss vs. Frequency<sup>[1]</sup>.

#### Note

1. Data obtained from on-wafer measurements.  $T_{chuck} = 25^{\circ}C$ .

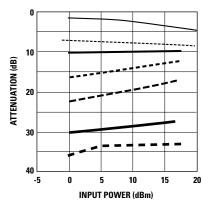

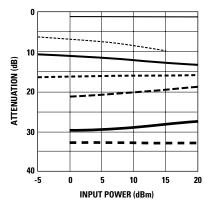

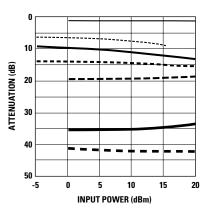

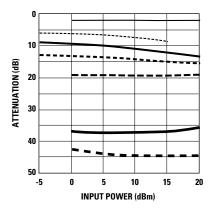

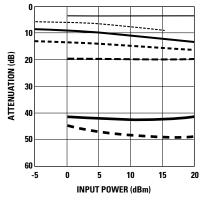

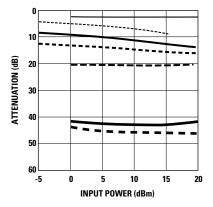

## **HMMC-1002 Typical Power Performance**

All Attenuation Settings were done at 1 GHz.

Figure 7. Attenuation vs. Input Power @ 50.0 MHz.<sup>[1]</sup>.

Figure 8. Attenuation vs. Input Power @ 2.0 GHz.<sup>[1]</sup>.

Figure 9. Attenuation vs. Input Power @ 10.0 GHz.<sup>[1]</sup>.

Figure 10. Attenuation vs. Input Power @ 14.0  $\rm GHz.^{[1]}$ .

Figure 11. Attenuation vs. Input Power @ 18.0 GHz.<sup>[1]</sup>.

Figure 12. Attenuation vs. Input Power @ 22.0 GHz.<sup>[1]</sup>.

## Note:

1. Data taken with the device mounted in connectorized package.

### **Key for Attenuation Settings:**

Min.

----- Min. + 5 dB ---- Min. + 10 dB

--- Min. + 15 dB

——— Min. + 20 dB

Min. + 30 dB

**– –** Max.

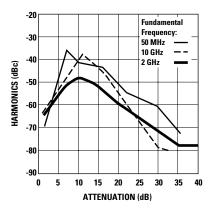

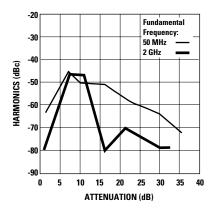

## **HMMC-1002 Typical Harmonic Performance**

Figure 13. Second Harmonic Suppression vs. Attenuation. Input Power = 0 dBm  $^{[1]}$ .

Figure 14. Third Harmonic Suppression vs. Attenuation. Input Power = 0 dBm $^{[1]}$ .

#### Note:

1. Data taken with the device mounted in connectorized package.

### **HMMC-1002 Typical Temperature Performance**

Figure 15. Attenuation vs. Temperature @ Minimum Attenuation.<sup>[1]</sup>.

Figure 16. Attenuation vs. Temperature @ 5 dB Attenuation.<sup>[1]</sup>.

Figure 17. Attenuation vs. Temperature @ 10 dB Attenuation.<sup>[1]</sup>.

Figure 18. Attenuation vs. Temperature @ 20 dB Attenuation.<sup>[1]</sup>.

Figure 19. Attenuation vs. Temperature @ 30 dB Attenuation.<sup>[1]</sup>.

Figure 20. Attenuation vs. Temperature @ Max. Attenuation.<sup>[1]</sup>.

#### Note:

1. Data taken with the device mounted in connectorized package.

#### **Key for Temperature Settings:**

This data sheet contains a variety of typical and guaranteed performance data. The information supplied should not be interpreted as a complete list of circuit specifications. In this data sheet the term *typical* refers to the 50th percentile performance. For additional information contact your local Avago Technologies' sales representative.

For product information and a complete list of distributors, please go to our web site: **www.avagotech.com**

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies, Pte. in the United States and other countries.

Data subject to change. Copyright © 2006 Avago Technologies Pte. All rights reserved. Obsoletes 5965-5452E

5988-1892EN April 3, 2006