## 5-A Controlled Slew Rate Load Switch with Level Shift

#### **FEATURES**

- 5-A Maximum Load

- Switches Voltages 1.8- to 5.5-V

- Ground Referenced Logic Inputs

- 1.8- to 5-V Logic Voltage Compatible

- 25-mΩ Maximum On-Resistance

- Level-Shifted Gate Drive Means The Control (Logic)

Voltage Is Independent Of Power Voltage

- Slow Turn-On (Controlled Slew Rate)

Eliminates High Inrush Currents

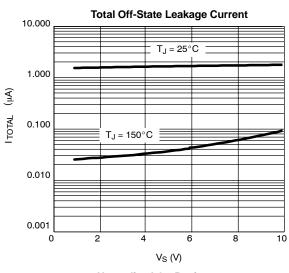

- Low Power Consumption In Off State

- Active Pull-Down On Output When In Off State

- RoHS Compliant

Pb-free Available

#### **DESCRIPTION**

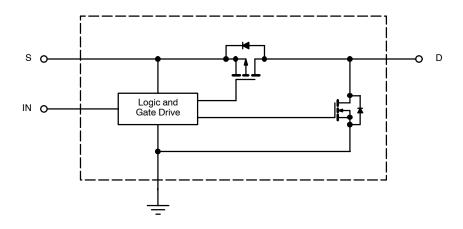

The Si4788CY is a p-channel MOSFET with a logic interface. The control input is compatible with all types of logic down to 1.8 V. The switch can be used to control voltages from 1.8 V to 5.5 V, and the logic input can be a lower voltage than the power. The switch also incorporates reduced switching speed

to reduce inrush when switching loads with a high value of capacitance. The Si4788CY is packaged in an 8-pin SOIC package and rated for the commercial temperature range of 0 to  $85^{\circ}$ C.

### **FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION**

## **Si4788CY**

## **Vishay Siliconix**

#### **ABSOLUTE MAXIMUM RATINGS**

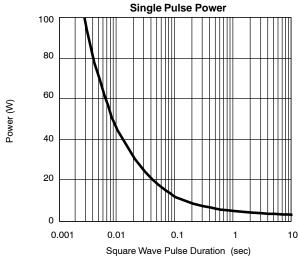

| Voltage Referenced to GND V <sub>S</sub> , V <sub>D</sub> <sup>a</sup>                                                                                                                                                           | Continuous P-Switch Current         5 A           Storage Temperature         -55 to 150°C                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{lll} V_{\text{IN}} & & -0.3 \text{ V to 7.0 V} \\ & \text{Power Dissipation (Continuous)}^{\text{a}} & & 1.5 \text{ W} \\ & \text{Pulsed Drain Current } (I_{\text{DM}})^{\text{b}} & & 40 \text{ A} \end{array}$ | <ul> <li>Notes</li> <li>a. Device mounted with all leads soldered to 1" x 1" FR4 with laminated copper PC board.</li> <li>b. Pulse width ≤300 μs, dc ≤2%.</li> </ul> |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING RANGE**

| V <sub>S</sub> , V <sub>D</sub> | Operating Temperature Range –25 to 85°C |

|---------------------------------|-----------------------------------------|

| V <sub>IN</sub>                 | Junction Temperature                    |

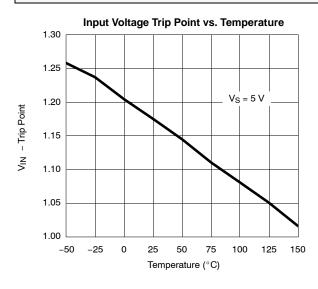

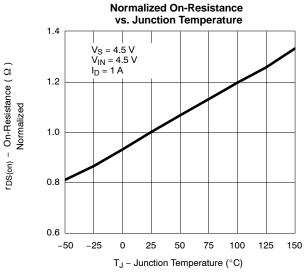

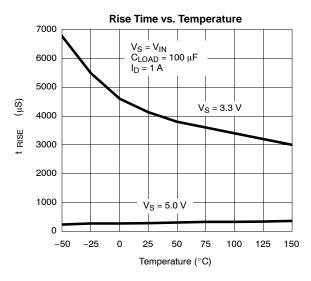

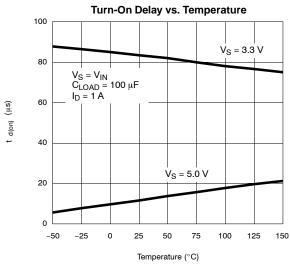

This device has a maximum recommended operating junction temperature of 85°C. This temperature limit is used for electrical specifications such as logic transition voltages only and is not a reliability limit. The device can be used with junction temperatures up to 150°C if relaxed specifications can be tolerated, although limits for these specifications may not be given. Performance curves can be used to give an indication of specifications at higher temperatures, but are not guaranteed.

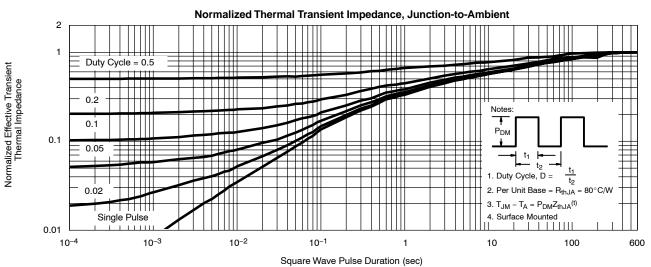

| THERMAL RESISTANCE RATINGS             |              |                   |         |         |      |  |

|----------------------------------------|--------------|-------------------|---------|---------|------|--|

| Parameter                              |              | Symbol            | Typical | Maximum | Unit |  |

| Maximum Junction-to-AmbientNO TAG      | Steady State | R <sub>thJA</sub> | 80      | 95      |      |  |

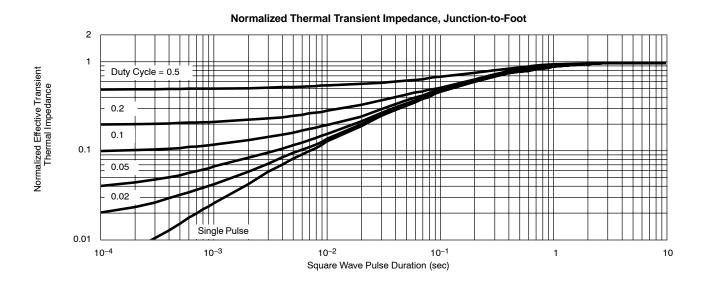

| Maximum Junction-to-Foot (Drain)NO TAG | Steady State | R <sub>thJF</sub> | 15      | 20      | °C/W |  |

#### Notes

- Surface Mounted on 1" x 1" FR4 Board.

- Junction-to-foot thermal impedance represents the effective thermal impedance of all heat carrying leads in parallel and is intended for use in conjunction with the thermal impedance of the PC board pads to ambient (RthJA = RthJF + RthPCB-A). It can also be used to estimate chip temperature if power dissipation and the lead temperature of a heat carrying (drain) lead is known.

| SPECIFICATIONS                             |                                                                   |                                                                                              |       |                  |      |                  |      |

|--------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------|------------------|------|------------------|------|

|                                            |                                                                   |                                                                                              |       | Limits           |      |                  |      |

| Parameter                                  | Symbol                                                            | Specific Test Conditions                                                                     | Tempa | Min <sup>b</sup> | Турс | Max <sup>b</sup> | Unit |

|                                            |                                                                   |                                                                                              |       |                  |      |                  |      |

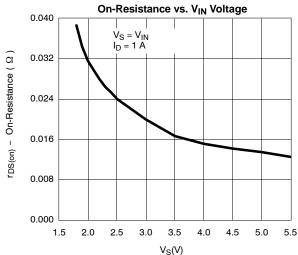

| On-Resistance r <sub>DS(on)</sub>          | V <sub>S</sub> = 2.5 V, I <sub>D</sub> = 1 A, V <sub>IN</sub> = H | Room                                                                                         |       | 23               | 29   | mΩ               |      |

|                                            | V <sub>S</sub> = 3.3 V, I <sub>D</sub> = 1 A, V <sub>IN</sub> = H | Room                                                                                         |       | 20               | 25   |                  |      |

|                                            |                                                                   | $V_S = 4.5 \text{ V}, I_D = 1 \text{ A}, V_{IN} = H$                                         | Room  |                  | 16   | 20               |      |

| Pull-Down Resistance                       | r <sub>PULL-DOWN</sub>                                            | $V_S = 3.3 \text{ V to 5 V, } V_{IN} = L$                                                    | Room  | 8                | 12   | 20               | Ω    |

| Leakage Current                            | I <sub>S(off)</sub>                                               | $V_S = 1.8 \text{ V to 5 V, } V_{IN} = L$                                                    | Room  |                  |      | 1.2              | μΑ   |

| Logic Input Voltage Low V <sub>INL</sub> — | .,                                                                | V <sub>S</sub> = 3.3 V to 5 V                                                                | Full  |                  |      | 0.6              |      |

|                                            | V <sub>S</sub> = 1.8 V to 3.3 V                                   | Full                                                                                         |       |                  | 0.3  |                  |      |

| Input Voltage High V <sub>INH</sub>        | V <sub>S</sub> = 3.3 V to 5 V                                     | Full                                                                                         | 2.2   |                  |      | V                |      |

|                                            | V <sub>S</sub> = 1.8 V to 3.3 V                                   | Full                                                                                         | 1.5   |                  |      |                  |      |

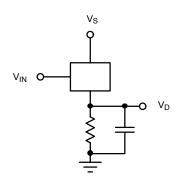

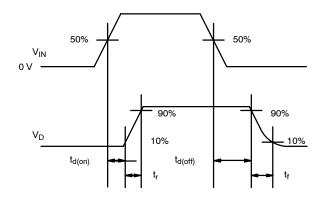

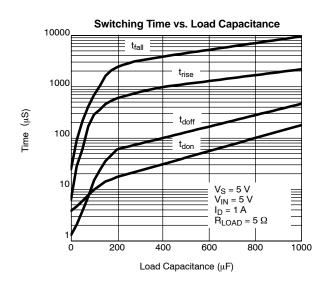

| Turn-On Delay                              | t <sub>d(on)</sub>                                                | V <sub>IN</sub> = 5 V, I <sub>LOAD</sub> = 1 A, C <sub>LOAD</sub> = 100 μF<br>Test Circuit 1 | Room  |                  | 16   | 35               |      |

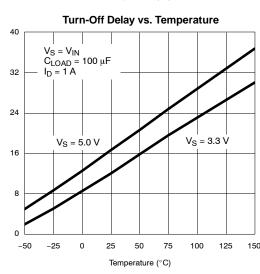

| Turn-Off Delay                             | t <sub>d(off)</sub>                                               |                                                                                              | Room  |                  | 20   | 40               |      |

| Rise Time                                  | t <sub>RISE</sub>                                                 |                                                                                              | Room  |                  | 280  | 550              | μs   |

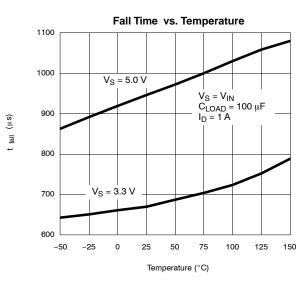

| Fall Time                                  | t <sub>FALL</sub>                                                 | ion Shoult 1                                                                                 | Room  |                  | 920  | 1800             |      |

| Maximum Turn-On Slew Rate                  | dv/dt                                                             |                                                                                              | Room  |                  | 20   |                  | V/ms |

#### Notes

- Room =  $25^{\circ}$ C, Full = as determined by the operating temperature suffix.

- The algebraic convention whereby the most negative value is a minimum and the most positive a maximum. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing. b.

## **TIMING DIAGRAMS**

**TEST CIRCUIT 1**

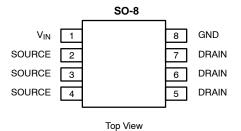

### **PIN CONFIGURATION**

| TRUTH TABLE |        |  |  |  |

|-------------|--------|--|--|--|

| $V_{IN}$    | Switch |  |  |  |

| 0           | Off    |  |  |  |

| 1           | On     |  |  |  |

Ordering Information: Si4788CY

Si4788CY-T1 (with Tape and Reel)

Si4788CY—E3 (Lead (Pb)-Free) Si4788CY-T1—E3 (Lead (Pb)-Free with Tape

and Reel)

| PIN DESCRIPTION |                 |             |  |  |

|-----------------|-----------------|-------------|--|--|

| Pin Number      | Symbol          | Description |  |  |

| 1               | V <sub>IN</sub> | Input pin   |  |  |

| 2, 3, 4         | SOURCE          |             |  |  |

| 5, 6, 7         | DRAIN           |             |  |  |

| 8               | GND             | Ground      |  |  |

## TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

(sn)

t d(off)

## TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

### TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

#### **TYPICAL APPLICATIONS**

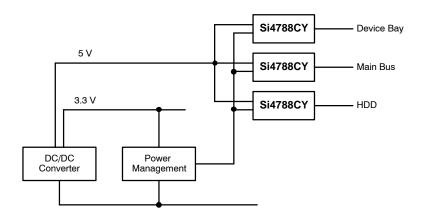

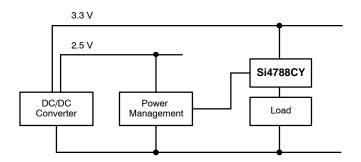

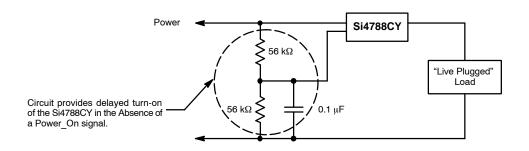

The Si4788CY can be used to control a load up to 5-Amp where the control logic voltage is different from the voltage of the load being controlled, and/or the load has a large capacitive component and inrush currents must be minimized during switching.

The low  $R_{DS(on)}$  of  $20\text{-}m\Omega$  typical makes the switch ideal for applications such as power bus switching in notebook computers and central office telecom equipment. For a load of 5 A, the voltage drop is only approximately 100 mV.

The control input is a CMOS compatible input with a minimum high input voltage of 2.2 V with a power rail voltage of 5 V. It is

therefore compatible with any CMOS logic voltage between 2.2 V and 5 V under these conditions with no extra configuration required. With a 3.3-V power rail voltage the minimum high input voltage is 1.5 V, making it compatible with 1.8-V logic.

The Si4788CY is designed to give a steady dv/dt on the output during turn-on even with capacitive loads. The output rise time is 280- $\mu s$  typical with a 100- $\mu F$  load, which corresponds to a dv/dt of about 20 V/ms, or a capacitive inrush current of around 2-A max with a 100- $\mu F$  load. Higher values of capacitance result in a slower switching speed, therefore even with very high values of capacitance, inrush should not be a problem.

FIGURE 1. Si4788CY Used To Control 5-V Bus With 3.3-V Logic Control

FIGURE 2. Si4788CY Used To Control 3.3-V Bus With 2.5-V or 3.3-V Logic

FIGURE 3. Si4788CY Used As Inrush Limiter On Removable Card

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="http://www.vishay.com/ppg?71100">http://www.vishay.com/ppg?71100</a>.

Document Number: 71100 S-50246—Rev. D, 21-Feb-05

Vishay

## **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Revision: 18-Jul-08

Document Number: 91000 www.vishay.com