# Intel NetStructure<sup>®</sup> MPCBL0050 Single Board Computer

**Technical Product Specification**

September 2007

Order Number: 318146-001

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

The Intel NetStructure<sup>®</sup> MPCBL0050 Single Board Computer may contain design defects or errors known as errata which may cause the product to deviate from published specifications.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel, Intel logo, Intel NetStructure, Intel SpeedStep, EM64T, and Xeon are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2007, Intel Corporation. All Rights Reserved.

Intel NetStructure<sup>®</sup> MPCBL0050 Single Board Computer Technical Product Specification 2

# Contents

| 1.0 | Intro      | duction                    |                    |                                                                                   | 13       |

|-----|------------|----------------------------|--------------------|-----------------------------------------------------------------------------------|----------|

|     | 1.1        | Docum                      | ent Organ          | ization                                                                           | 13       |

|     | 1.2        | -                          |                    | erms                                                                              | 14       |

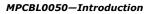

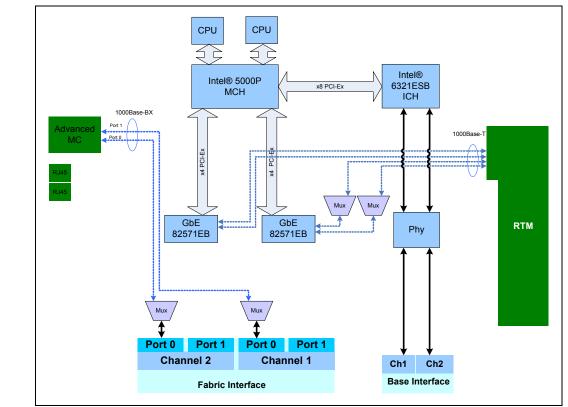

| 2.0 |            | re Ove                     | -                  |                                                                                   | 17       |

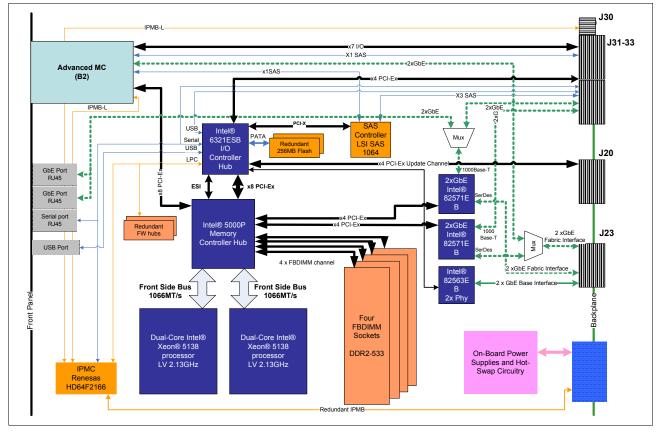

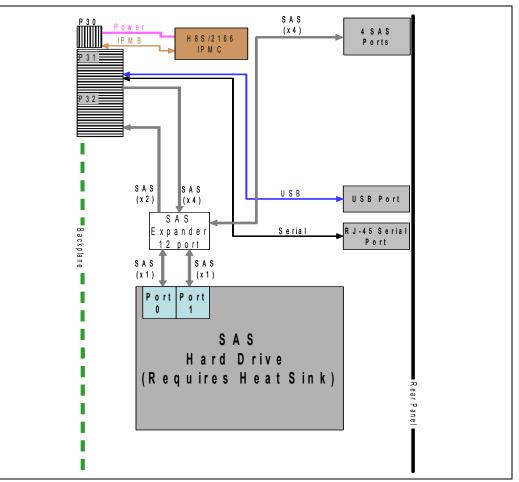

|     | 2.1<br>2.2 | Applica<br>MPCBL(<br>2.2.1 | 0050 Func          | tional Description<br>nsition Module                                              | 17       |

|     |            |                            | 2.2.1.1<br>2.2.1.2 | Intel NetStructure® MPRTM0040<br>Intel NetStructure® MPRTM0050                    | 19       |

|     |            | 2.2.2                      |                    | e Intel® Xeon® 5138 LV 2.13GHz Processor                                          |          |

|     |            | 2.2.3                      |                    |                                                                                   | 21       |

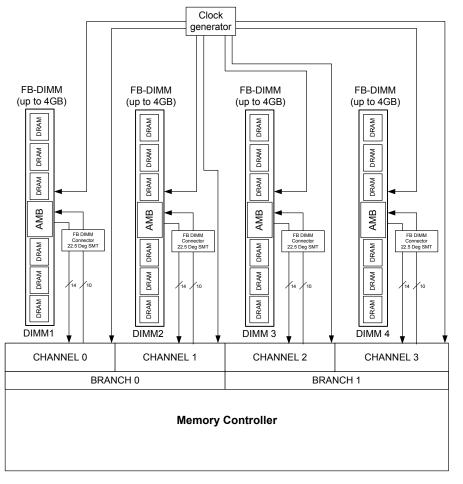

|     |            |                            | 2.2.3.1            | Intel <sup>®</sup> 5000 Memory Controller Hub                                     | 21       |

|     |            |                            | 2.2.3.2            | Intel <sup>®</sup> 6321ESB I/O Controller Hub                                     | 22       |

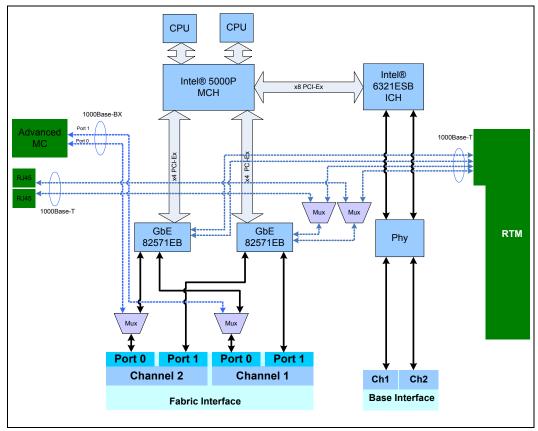

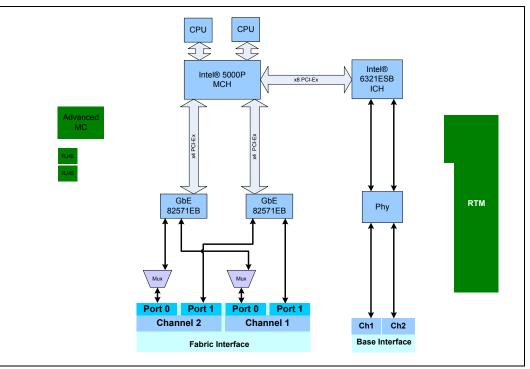

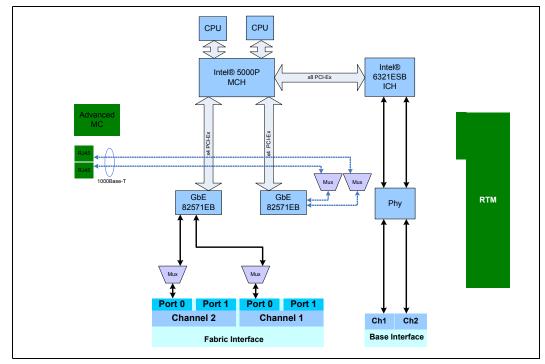

|     |            | 224                        | 2.2.3.3            | Intel <sup>®</sup> 82571EB Gigabit Ethernet Controller                            |          |

|     |            | 2.2.4<br>2.2.5             |                    |                                                                                   |          |

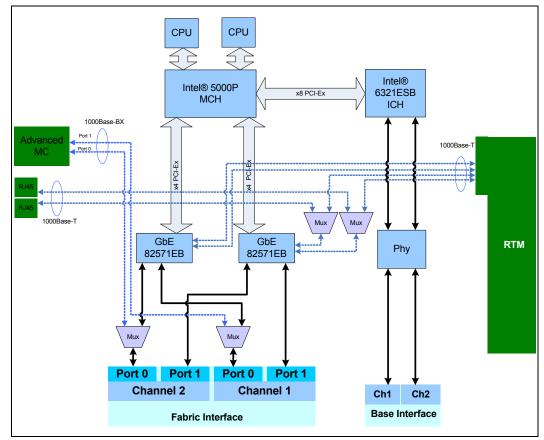

|     |            | 2.2.5                      | 2.2.5.1            | Gigabit Ethernet                                                                  |          |

|     |            |                            | 2.2.5.1            | Serial Attached SCSI (SAS) Controller                                             | 27       |

|     |            |                            | 2.2.5.3            | USB 2.0                                                                           | 27       |

|     |            |                            | 2.2.5.4            | Serial Ports                                                                      |          |

|     |            | 2.2.6                      |                    | IMC Slot                                                                          |          |

|     |            | 2.2.7                      |                    | Hub for EFI BIOS                                                                  |          |

|     |            |                            | 2.2.7.1<br>2.2.7.2 | FWH 0 (Main EFI)<br>FWH 1 (Backup/Recovery EFI)                                   | 29       |

|     |            |                            | 2.2.7.3            | EFI Backup Mechanism                                                              |          |

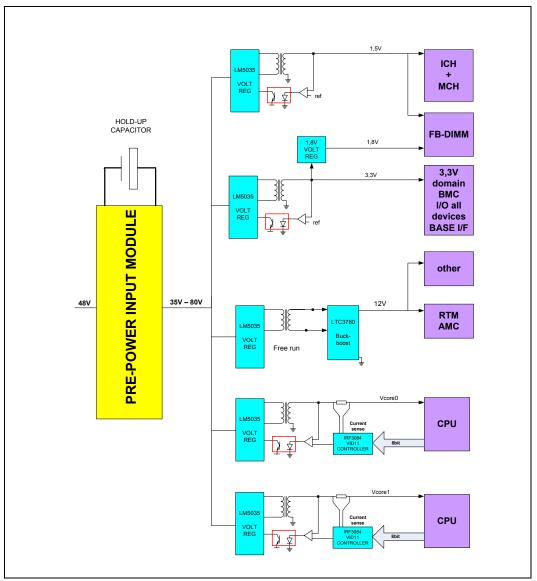

|     |            | 2.2.8                      | On-board           | I DC/DC converters                                                                | 30       |

|     |            |                            | 2.2.8.1            | AdvancedTCA -48V Power Feed                                                       | 31       |

|     |            |                            | 2.2.8.2            | 3.3V                                                                              | -        |

|     |            |                            | 2.2.8.3<br>2.2.8.4 | 1.5V<br>1.8V                                                                      |          |

|     |            |                            | 2.2.8.5            | 12V                                                                               |          |

|     |            |                            | 2.2.8.6            | CPU VRD                                                                           | -        |

|     |            | 2.2.9                      |                    | ous Emergency Power-down Circuitry                                                |          |

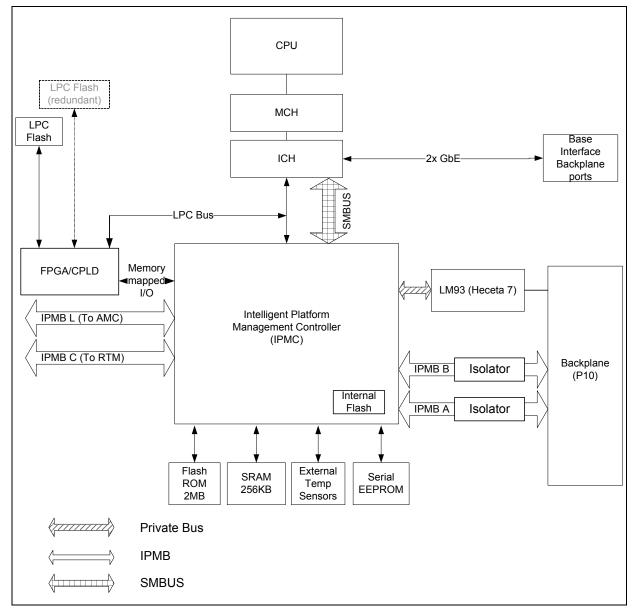

|     |            | 2.2.10                     | Intelliger         | t Platform Management Controller                                                  | 33       |

|     |            |                            |                    | te Flash Drives                                                                   |          |

|     |            | 2.2.12                     | Real-Tim           | e Clock                                                                           | 33       |

| 3.0 | Conne      |                            | and LEDs           |                                                                                   | 35       |

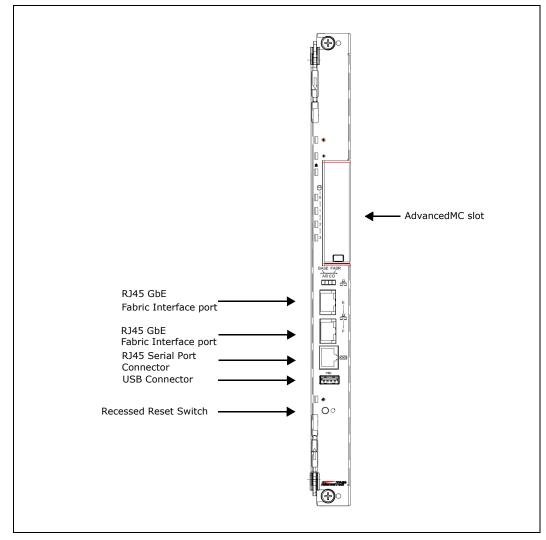

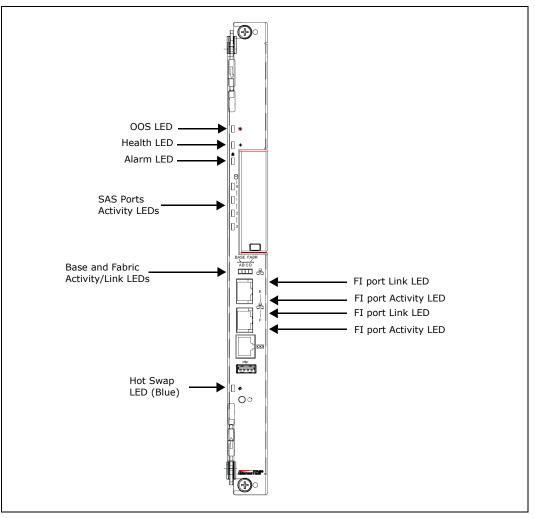

|     | 3.1        | Front P                    |                    | ectors                                                                            |          |

|     |            | 3.1.1                      |                    | nector                                                                            |          |

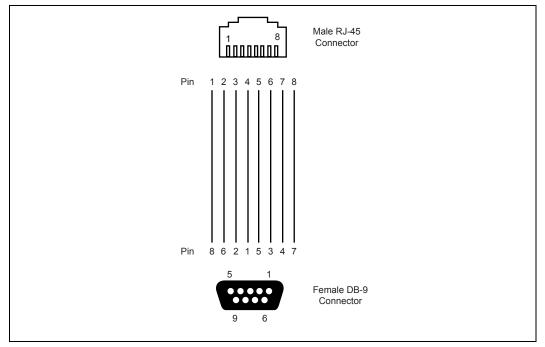

|     |            | 3.1.2                      |                    | rt Connector                                                                      |          |

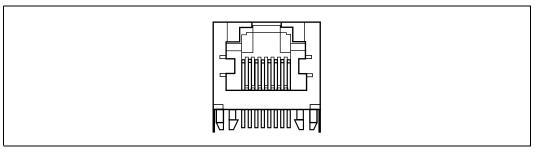

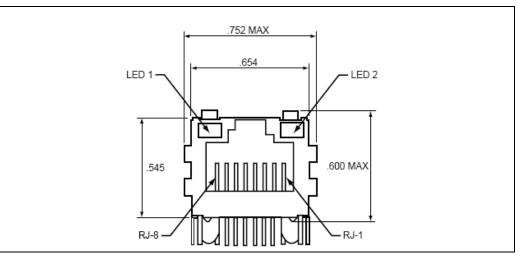

|     |            | 3.1.3<br>3.1.4             |                    | 10/100/1000 Connectors                                                            |          |

|     | 3.2        |                            |                    |                                                                                   |          |

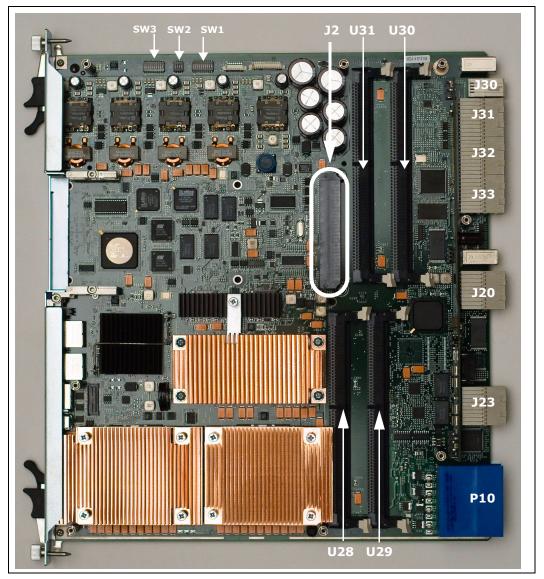

|     | 3.3        |                            |                    | n-Board Connectors, DIP Switch Location                                           |          |

|     | 3.4        |                            |                    |                                                                                   |          |

|     | 3.5        |                            |                    | ctors                                                                             |          |

|     |            | 3.5.1                      | Advanced           | JMC Connector (J2)                                                                | 44       |

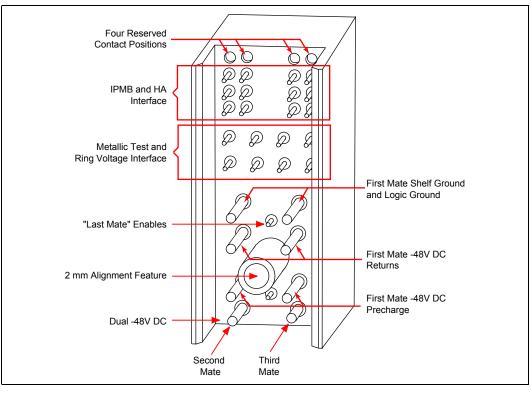

|     | 3.6        | Backpla                    |                    | ectors                                                                            |          |

|     |            | 3.6.1                      |                    | stribution Connector (P10)                                                        |          |

|     |            | 3.6.2                      |                    | JTCA Data Transport Connectors (J20, J23)                                         |          |

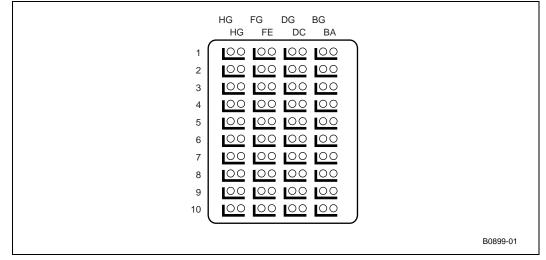

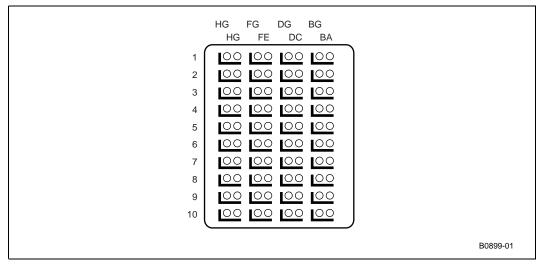

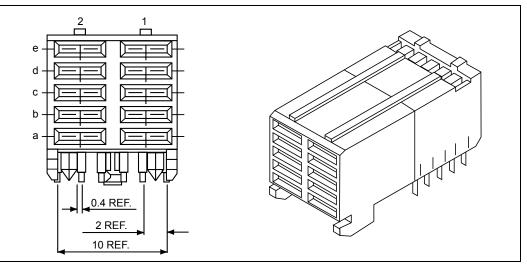

|     |            |                            | 3.6.2.1<br>3.6.2.2 | Update Channel connector (J20)<br>Base and Fabric Interface ports connector (J23) | 51<br>52 |

|     |            |                            |                    |                                                                                   |          |

|     |            | 3.6.3 Zone 3 Rear Transition Module Power Connector (J30)54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     |            | 3.6.4 Zone 3 Rear Transition Module Data/Control Connector (J31)55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|     |            | 3.6.5 Zone 3 Rear Transition Module Data Connector (J32)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|     |            | 3.6.6 Zone 3 Rear Transition Module Data/Control Connector (J33)57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

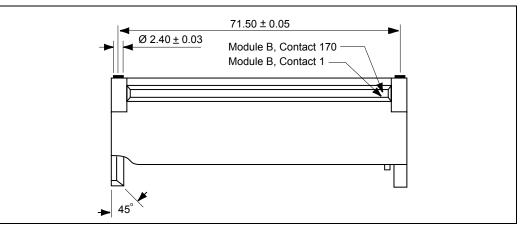

|     |            | 3.6.7 Alignment Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 4.0 | -          | ting the Unit 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|     | 4.1        | Board Configuration DIP Switches59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

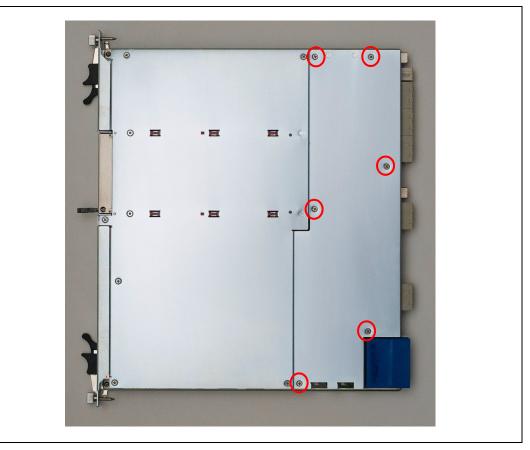

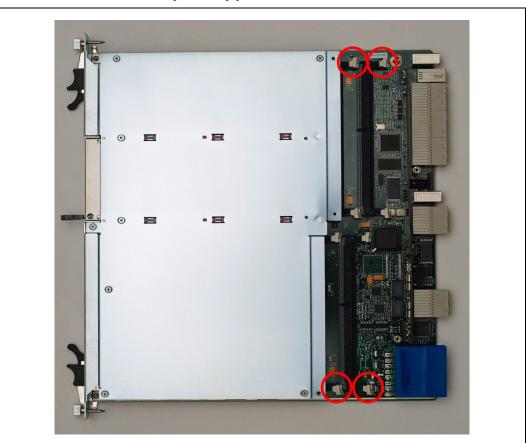

|     | 4.2        | Installing and Extracting the SBC59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|     |            | 4.2.1 Insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|     |            | 4.2.2 Ejection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|     | 4.3        | AdvancedMC Module Installation60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|     | 4.4        | AdvancedMC Filler Panels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|     | 4.5        | Memory (FBDIMM) Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

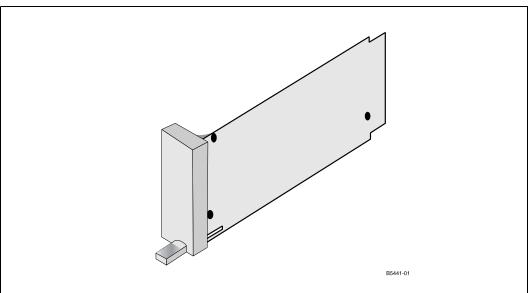

|     | 4.6<br>4.7 | Rear Transition Module (RTM) Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

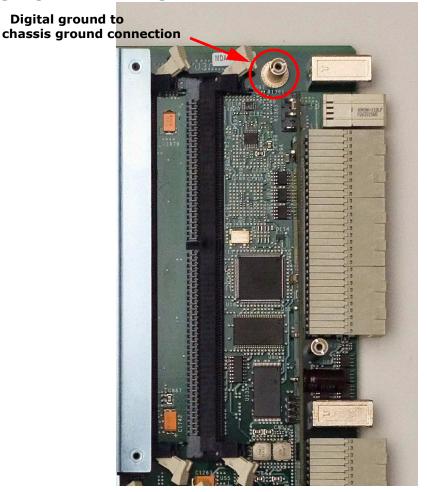

|     | 4.7<br>4.8 | Digital Ground to Chassis Ground Connectivity62<br>EFI BIOS Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|     | 4.9        | Remote Access Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|     | 4.10       | Boot Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|     | 4.10       | 4.10.1 Booting from a SAS Hard Disk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|     |            | 4.10.2 Booting from a PATA Flash (On-board)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|     |            | 4.10.3 Booting from a USB Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|     |            | 4.10.4 Booting from a LAN (PXE Boot)65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

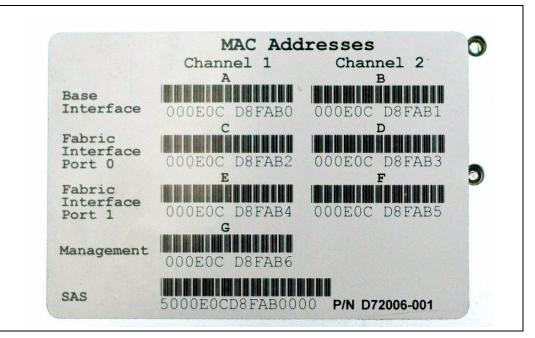

|     | 4.11       | Identifying MPCBL0050 Ethernet MAC Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|     | 4.12       | Cable Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|     | 4.13       | Firmware Updates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 5.0 | Hard       | vare Management 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|     | 5.1        | Supervision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|     | 5.1<br>5.2 | Supervision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|     |            | Sensor Data Record (SDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|     |            | Sensor Data Record (SDR).715.2.1 Power Unit Sensor.925.2.2 BIOS FWH State Change Sensors.93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

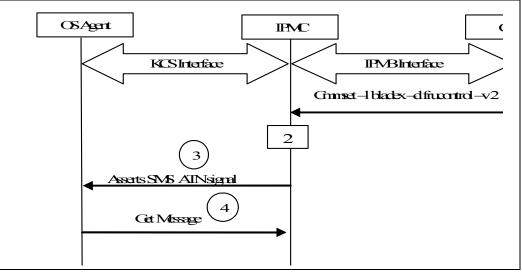

|     |            | Sensor Data Record (SDR).715.2.1 Power Unit Sensor.925.2.2 BIOS FWH State Change Sensors.935.2.3 Reset Sensor.93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

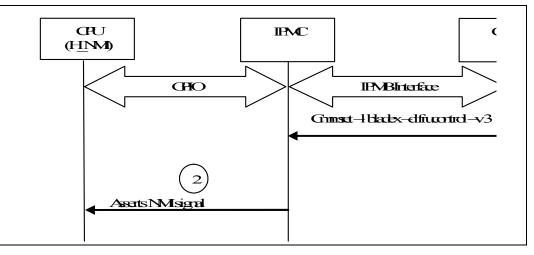

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     |            | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1 Analog Sensors97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

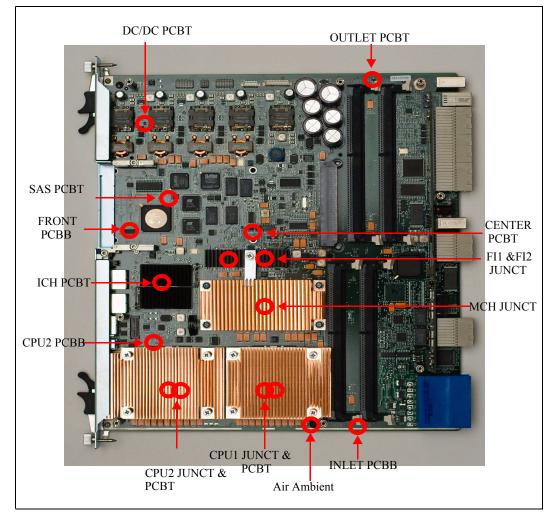

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1 Analog Sensors975.3.2 Temperature Sensor Locations100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1 Analog Sensors975.3.2 Temperature Sensor Locations1005.3.3 Processor Events100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1 Analog Sensors975.3.2 Temperature Sensor Locations1005.3.3 Processor Events1005.3.4 FB-DIMM Memory Events101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1 Analog Sensors975.3.2 Temperature Sensor Locations1005.3.3 Processor Events1005.3.4 FB-DIMM Memory Events1015.3.4.1 Correctable Errors101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1 Analog Sensors975.3.2 Temperature Sensor Locations1005.3.3 Processor Events1005.3.4 FB-DIMM Memory Events1015.3.4.1 Correctable Errors1015.3.4.3 Other Memory Events102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1 Analog Sensors975.3.2 Temperature Sensor Locations1005.3.3 Processor Events1005.3.4 FB-DIMM Memory Events1015.3.4.1 Correctable Errors1015.3.4.3 Other Memory Events102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1 Analog Sensors975.3.2 Temperature Sensor Locations1005.3.3 Processor Events1005.3.4 FB-DIMM Memory Events1015.3.4.1 Correctable Errors1015.3.4.2 Logging Threshold1015.3.4.3 Other Memory Events1025.3.5 System Firmware Progress (POST Error)1025.3.6 Port 80h POST Codes102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1 Analog Sensors975.3.2 Temperature Sensor Locations1005.3.4 FB-DIMM Memory Events1015.3.4.1 Correctable Errors1015.3.4.2 Logging Threshold1015.3.4.3 Other Memory Events1025.3.5 System Firmware Progress (POST Error)1025.3.7 Critical Interrupt103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1 Analog Sensors975.3.2 Temperature Sensor Locations1005.3.3 Processor Events1005.3.4 FB-DIMM Memory Events1015.3.4.1 Correctable Errors1015.3.4.2 Logging Threshold1015.3.5 System Firmware Progress (POST Error)1025.3.6 Port 80h POST Codes1025.3.8 IPMB Link Sensor103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|     | 5.2        | Sensor Data Record (SDR)       71         5.2.1 Power Unit Sensor       92         5.2.2 BIOS FWH State Change Sensors       93         5.2.3 Reset Sensor       93         5.2.4 NMI Sensor/NMI Assertion from IPMC       94         System Event Log (SEL)       96         5.3.1 Analog Sensors       97         5.3.2 Temperature Sensor Locations       100         5.3.3 Processor Events       100         5.3.4 FB-DIMM Memory Events       101         5.3.4.1 Correctable Errors       101         5.3.4.2 Logging Threshold       101         5.3.4.3 Other Memory Events       102         5.3.5 System Firmware Progress (POST Error)       102         5.3.6 Port 80h POST Codes       102         5.3.7 Critical Interrupt       103         5.3.8 IPMB Link Sensor       103         5.3.9 FRU Hot Swap       103                                                                                                                                                                                                                                                                                                            |  |

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1 Analog Sensors975.3.2 Temperature Sensor Locations1005.3.4 FB-DIMM Memory Events1015.3.4.1 Correctable Errors1015.3.4.2 Logging Threshold1015.3.5 System Firmware Progress (POST Error)1025.3.6 Port 80h POST Codes1025.3.7 Critical Interrupt1035.3.9 FRU Hot Swap1035.3.10 Ethernet Link Status103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|     | 5.2        | Sensor Data Record (SDR)715.2.1 Power Unit Sensor925.2.2 BIOS FWH State Change Sensors935.2.3 Reset Sensor935.2.4 NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1 Analog Sensors975.3.2 Temperature Sensor Locations1005.3.3 Processor Events1005.3.4 FB-DIMM Memory Events1015.3.4.1 Correctable Errors1015.3.4.2 Logging Threshold1015.3.5 System Firmware Progress (POST Error)1025.3.6 Port 80h POST Codes1025.3.7 Critical Interrupt1035.3.8 IPMB Link Sensor1035.3.10 Ethernet Link Status1035.3.11 Power Feeds, Power Supply, and Fuses103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|     | 5.3        | Sensor Data Record (SDR)       71         5.2.1 Power Unit Sensor       92         5.2.2 BIOS FWH State Change Sensors       93         5.2.3 Reset Sensor       93         5.2.4 NMI Sensor/NMI Assertion from IPMC       94         System Event Log (SEL)       96         5.3.1 Analog Sensors       97         5.3.2 Temperature Sensor Locations       100         5.3.3 Processor Events       100         5.3.4 FB-DIMM Memory Events       101         5.3.4.1 Correctable Errors       101         5.3.4.2 Logging Threshold       101         5.3.4.3 Other Memory Events       102         5.3.5 System Firmware Progress (POST Error)       102         5.3.6 Port 80h POST Codes       102         5.3.7 Critical Interrupt       103         5.3.8 IPMB Link Sensor       103         5.3.9 FRU Hot Swap       103         5.3.10 Ethernet Link Status       103         5.3.11 Power Feeds, Power Supply, and Fuses       103         5.3.12 IPMC Watchdog Timer Reset       103                                                                                                                                             |  |

|     | 5.2        | Sensor Data Record (SDR)715.2.1Power Unit Sensor925.2.2BIOS FWH State Change Sensors935.2.3Reset Sensor935.2.4NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1Analog Sensors975.3.2Temperature Sensor Locations1005.3.3Processor Events1005.3.4FB-DIMM Memory Events1015.3.4.1Correctable Errors1015.3.4.2Logging Threshold1015.3.4.3Other Memory Events1025.3.5System Firmware Progress (POST Error)1025.3.6Port 80h POST Codes1025.3.7Critical Interrupt1035.3.9FRU Hot Swap1035.3.10Ethernet Link Status1035.3.11Power Feeds, Power Supply, and Fuses1035.3.12IPMC Watchdog Timer Reset103Field Replaceable Unit (FRU) Information103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|     | 5.3        | Sensor Data Record (SDR)715.2.1Power Unit Sensor925.2.2BIOS FWH State Change Sensors935.2.3Reset Sensor935.2.4NMI Sensor/NMI Assertion from IPMC94System Event Log (SEL)965.3.1Analog Sensors975.3.2Temperature Sensor Locations1005.3.3Processor Events1005.3.4FB-DIMM Memory Events1015.3.4.1Correctable Errors1015.3.4.2Logging Threshold1015.3.4.3Other Memory Events1025.3.5System Firmware Progress (POST Error)1025.3.6Port 80h POST Codes1025.3.7Critical Interrupt1035.3.8IPMB Link Sensor1035.3.9FRU Hot Swap1035.3.10Ethernet Link Status1035.3.11Power Feeds, Power Supply, and Fuses1035.3.12IPMC Watchdog Timer Reset103Field Replaceable Unit (FRU) Information1035.4.1Common Header104                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     | 5.3        | Sensor Data Record (SDR)       71         5.2.1       Power Unit Sensor       92         5.2.2       BIOS FWH State Change Sensors       93         5.2.3       Reset Sensor       93         5.2.4       NMI Sensor/NMI Assertion from IPMC       94         System Event Log (SEL)       96         5.3.1       Analog Sensors       97         5.3.2       Temperature Sensor Locations       100         5.3.3       Processor Events       100         5.3.4       FB-DIMM Memory Events       101         5.3.4.1       Correctable Errors       101         5.3.4.2       Logging Threshold       101         5.3.4.3       Other Memory Events       102         5.3.4       Other Memory Events       102         5.3.5       System Firmware Progress (POST Error)       102         5.3.6       Port 80h POST Codes       102         5.3.7       Critical Interrupt       103         5.3.8       IPMB Link Sensor       103         5.3.9       FRU Hot Swap       103         5.3.10       Ethernet Link Status       103         5.3.11       Power Feeds, Power Supply, and Fuses       103         5.3.12       IPMC Watchd |  |

|     | 5.3        | Sensor Data Record (SDR)       71         5.2.1       Power Unit Sensor       92         5.2.2       BIOS FWH State Change Sensors       93         5.2.3       Reset Sensor       93         5.2.4       NMI Sensor/NMI Assertion from IPMC       94         System Event Log (SEL)       96         5.3.1       Analog Sensors       97         5.3.2       Temperature Sensor Locations       100         5.3.3       Processor Events       100         5.3.4       FB-DIMM Memory Events       101         5.3.4.1       Correctable Errors       101         5.3.4.2       Logging Threshold       101         5.3.4.3       Other Memory Events       102         5.3.5       System Firmware Progress (POST Error)       102         5.3.6       Port 80h POST Codes       102         5.3.7       Critical Interrupt       103         5.3.8       IPMB Link Sensor       103         5.3.10       Ethernet Link St |  |

|     | 5.3        | Sensor Data Record (SDR)       71         5.2.1       Power Unit Sensor       92         5.2.2       BIOS FWH State Change Sensors       93         5.2.3       Reset Sensor       93         5.2.4       NMI Sensor/NMI Assertion from IPMC       94         System Event Log (SEL)       96         5.3.1       Analog Sensors       97         5.3.2       Temperature Sensor Locations       100         5.3.3       Processor Events       100         5.3.4       FB-DIMM Memory Events       101         5.3.4.1       Correctable Errors       101         5.3.4.2       Logging Threshold       101         5.3.4.3       Other Memory Events       102         5.3.4       Other Memory Events       102         5.3.5       System Firmware Progress (POST Error)       102         5.3.6       Port 80h POST Codes       102         5.3.7       Critical Interrupt       103         5.3.8       IPMB Link Sensor       103         5.3.9       FRU Hot Swap       103         5.3.10       Ethernet Link Status       103         5.3.11       Power Feeds, Power Supply, and Fuses       103         5.3.12       IPMC Watchd |  |

|     |       | 5.4.5 MPCBL0050 FRU Record 10                          | )6 |

|-----|-------|--------------------------------------------------------|----|

|     |       | 5.4.6 FRU Area for Customer-Specific Information       | 16 |

|     |       | 5.4.7 Writing to the Customer FRU MRA 11               |    |

|     | 5.5   | E-Keying 11                                            |    |

|     | 5.6   | IPMC Platform Event Filtering (PEF) 11                 | 18 |

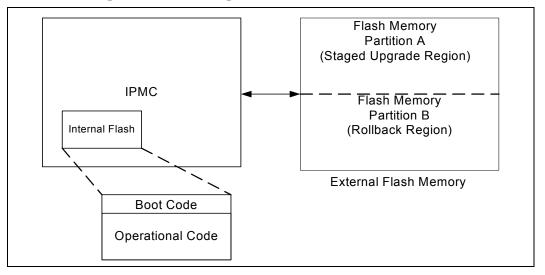

|     | 5.7   | IPMC Firmware Code Organization                        |    |

|     | 517   | 5.7.1 Functional Description                           |    |

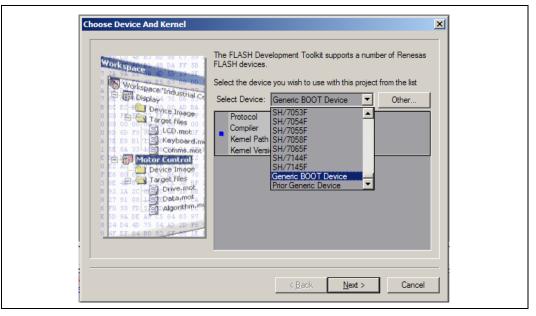

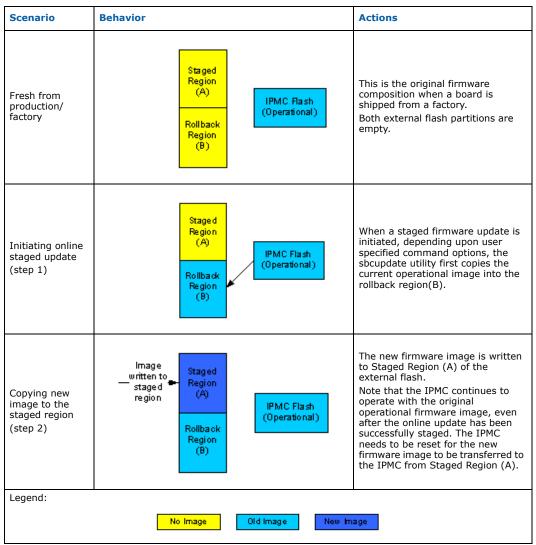

|     | 5.8   | IPMC Firmware Updates                                  |    |

|     | 5.0   | 5.8.1 Update Modes                                     |    |

|     | 5.9   | Ejector Mechanism                                      |    |

|     | 5.10  | Hot Swap LED                                           |    |

|     | 5.11  | ACPI                                                   |    |

|     | •·    | Reset Types                                            |    |

|     | J.12  | 5.12.1 Reset Control Sources                           |    |

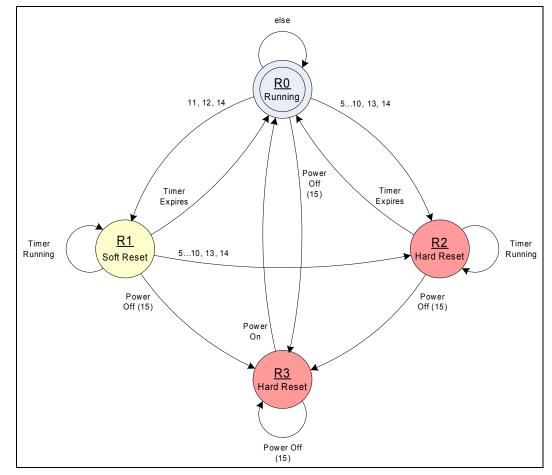

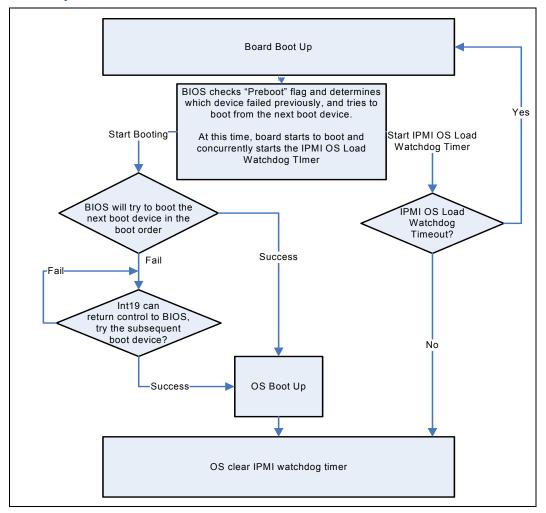

|     |       | 5.12.2 Payload Reset Diagram                           |    |

|     |       | 5.12.2 Fayload Reset Diagram                           |    |

|     |       | 5.12.4 IPMI Commanded Reset                            |    |

|     |       | 5.12.5 Watchdog Timer Expiration                       |    |

|     |       | 5.12.6 FRB3 Failure                                    |    |

|     | 5.13  | IPMC Reset Control                                     |    |

|     | 5.15  | 5.13.1 Standby Power On Reset                          |    |

|     |       | 5.13.2 IPMC Hardware Watch Dog Timer Expiration        |    |

|     |       | 5.13.3 IPMC Exit Firmware Update Mode                  |    |

|     |       | 5.13.4 IPMI BMC Cold Reset Command                     |    |

|     |       |                                                        |    |

|     | E 14  | 5.13.5 IPMC Operational Code Update with New FPGA Load |    |

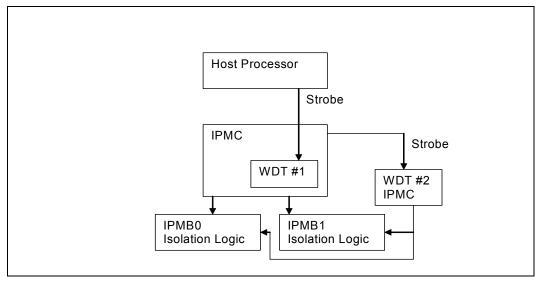

|     | 5.14  |                                                        |    |

|     |       | 5.14.1 WDT #1 (IPMI Watchdog Timer)                    | 20 |

|     | E 1 E | FRU Payload Control                                    |    |

|     | 5.15  | 5.15.1 Cold Reset                                      |    |

|     |       | 5.15.1 Cold Reset                                      |    |

|     |       | 5.15.2 Walth Reset                                     |    |

|     |       | 5.15.4 Diagnostic Interrupt                            |    |

|     | 5.16  | OEM IPMI Commands                                      |    |

|     | 5.10  |                                                        | 20 |

| 6.0 | EFI B | IOS Features 14                                        | 41 |

|     | 6.1   | Introduction 14                                        | 41 |

|     | 6.2   | EFI BIOS Flash Memory Organization 14                  |    |

|     | 6.3   | Redundant EFI BIOS Functionality 14                    |    |

|     | 6.4   | Language Support                                       |    |

|     | 6.5   | Recovering EFI BIOS Data 14                            | 12 |

|     | 6.6   | Complementary Metal-Oxide Semiconductor (CMOS) RAM 14  | 12 |

|     | 6.7   | Improving Booting Time 14                              |    |

|     | 6.8   | EFI BIOS Security Features                             |    |

|     |       | 6.8.1 Password Clear DIP Switch                        |    |

|     | 6.9   | Remote Access Configuration 14                         |    |

|     | 6.10  | Boot Device Priority                                   |    |

|     | 6.11  | Progressive Boot Support                               |    |

|     |       | 6.11.1 Progressive Boot Mechanism                      |    |

|     | 6.12  | Pre-Defined Resources for AdvancedMC Modules           |    |

|     |       | USB Support                                            |    |

|     |       | 6.13.1 Native USB Support                              |    |

|     |       | 6.13.2 Legacy USB Support                              |    |

| 70  |       |                                                        |    |

| 7.0 |       |                                                        | 47 |

|     | 7.1   | Introduction14                                         | +/ |

|     | 7.2   | Main Me  | enu                |                                               |

|-----|-------|----------|--------------------|-----------------------------------------------|

|     | 7.3   | Advance  | ed Menu.           |                                               |

|     |       | 7.3.1    | Processor          | r Submenu                                     |

|     |       | 7.3.2    | Memory S           | Submenu                                       |

|     |       | 7.3.3    |                    | roller Submenu150                             |

|     |       | 7.3.4    |                    | rage Submenu150                               |

|     |       | 7.3.5    |                    | rt Šubmenu                                    |

|     |       | 7.3.6    |                    | figuration Submenu151                         |

|     |       | 7.3.7    |                    | guration Submenu151                           |

|     | 7.4   | Security |                    |                                               |

|     | 7.5   |          |                    | ent Menu                                      |

|     |       | 7.5.1    |                    | terface Ports Options Submenu                 |

|     |       |          |                    | Redirection Submenu                           |

|     | 7.6   | -        |                    | nu                                            |

|     | /.0   |          |                    | <ul> <li>Order Submenu</li></ul>              |

|     |       | 7.6.2    |                    | Device Order Submenu                          |

|     | 7.7   |          |                    | enu                                           |

|     | 7.8   |          |                    |                                               |

|     | 7.9   |          | -                  |                                               |

|     |       |          |                    |                                               |

| 8.0 |       |          |                    | iges and Checkpoints 157                      |

|     | 8.1   |          |                    | rror Messages157                              |

|     | 8.2   | Port 80  | h POST Co          | odes160                                       |

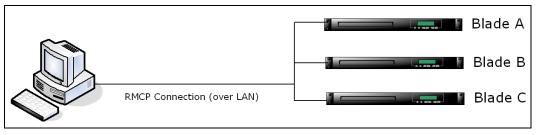

| 9.0 | Seria | l Over L | AN.                | 163                                           |

|     | 9.1   | Referen  | ices               |                                               |

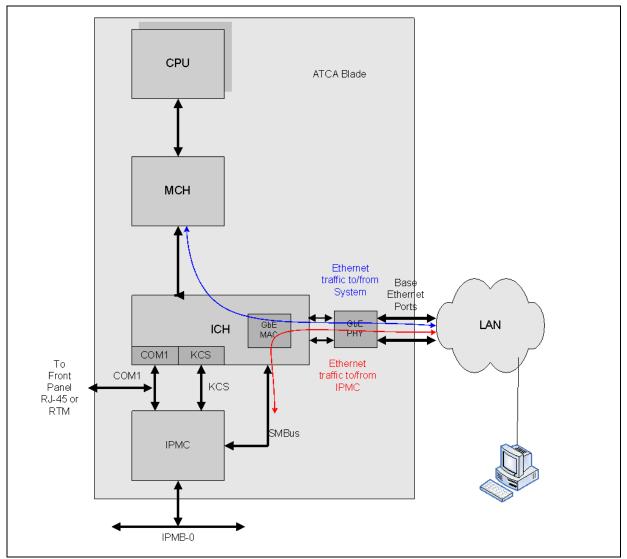

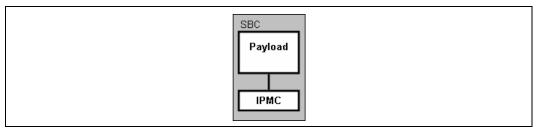

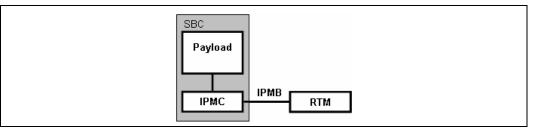

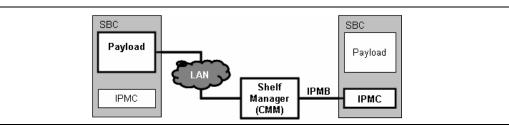

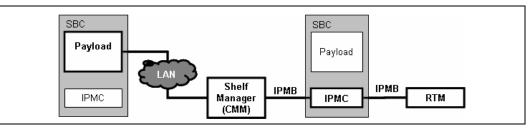

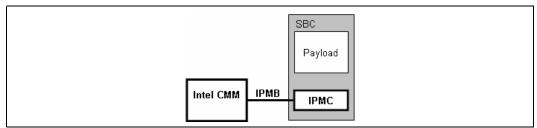

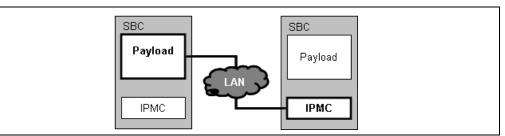

|     | 9.2   | SOL Arc  | chitecture         |                                               |

|     |       | 9.2.1    | Architect          | ural Components                               |

|     |       |          | 9.2.1.1            | IPMC                                          |

|     |       |          | 9.2.1.2            | Ethernet Controller                           |

|     | 9.3   | Theory   | of Operat          | ion165                                        |

|     |       |          |                    | nel Serial Port or RTM165                     |

|     |       | 9.3.2    | Serial Ov          | er LAN                                        |

|     | 9.4   |          |                    | Client                                        |

|     | 9.5   |          |                    | uration Script166                             |

|     | 9.6   |          |                    | Model                                         |

|     |       |          |                    | ng the Blade for SOL167                       |

|     | 9.7   |          |                    | (reference_cfg)168                            |

|     |       | 9.7.1    |                    | iguration Reference Script (reference_cfg)168 |

|     |       | 9.7.2    |                    | ehavior168                                    |

|     |       | 9.7.3    |                    | Information168                                |

|     |       | 9.7.4    |                    | meters                                        |

|     |       | 9.7.5    |                    | meters                                        |

|     |       | 9.7.6    |                    | Parameters                                    |

|     |       | 9.7.7    |                    | d Line Options169                             |

|     | 9.8   | Setting  |                    | al Over LAN Session170                        |

|     |       | 9.8.1    | Target Bl          | ade Setup170                                  |

|     |       |          | 9.8.1.1            | EFI BIOS Configuration170                     |

|     |       |          | 9.8.1.2            | Operating System Configuration                |

|     |       |          | 9.8.1.3            | sbcutils RPM Installation                     |