#### **CARDINAL COMPONENTS**

# **Re-Configurable 6 Output CMOS TCXO**

• Fixed & Re-Configurable Multi-Frequency Oscillator

• Intuitive software and FC interface

· Easily update system

· Software flexible, quick upgrades and changes

- Industry-standard packaging saves on board space

- Mult. outputs 1 pkg vs. mult. osc & assoc. comp.

Performs well under all conditions

**Specifications:**

**Applications**

High-end multimedia

Communications

• Industrial

Typ

A/D converters

Consumer Applications

New and innovative products

• Temperature-sensitive applications

Max

CCT6RC

Series

Unit

Part Numbering Example: CCT6RC 1A 200.0 / 150.0 / 125.0 / 100.0 / 75.0 / 12.0

Min

CCT\_6RC 1A 200 150 125 100 75 12

SERIES PACKAGE STYLE FREQUENCY A FREQUENCY B FREQUENCY C FREQUENCY D FREQUENCY E FREQUENCY R

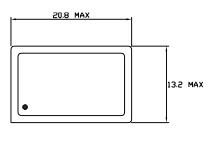

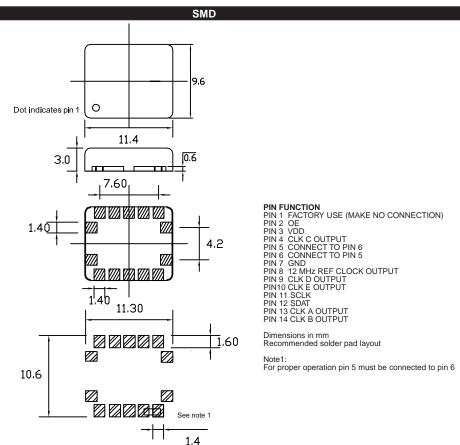

1A=14 pin dip 0.2 - 200 MHz 0.2 - 200 MHz 0.2 - 200 MHz 0.2 - 200 MHz 25 - 200 MHz 9=9.6x11.4 SMD

Frequency Range: 200 Output A CMOS 0.2 MHz Output B CMOS 0.2 200 MHz Output C CMOS 0.2 200 MHz 0.2 Output D CMOS 200 MHz Output E CMOS 25 200 MHz Output R Fixed 12 MHz **Available Stability Options:** -2.52.5 ppm Supply Voltage: 3.135 3.3 3.465 V **Operating Temperature** -40 85 °C Range Options: **Storage Temperature:** -55 125 °C **Duty Cycle:** 40 % 60 45 % 55 Start-Up Time: 3 10 mS Aging (PPM/1st Year): ±1 ppm Ta=25C, Vdd=3.3V Static Discharge Voltage 2000 V Mil-Std 883, method 3015 **Output Load:** pF CMOS, < 40 MHz 30 CMOS, ≥ 40 MHz 15 pF **Output Level: CMOS** Packaging: 25 / Tube 14 pin SMD Tape & Reel

Notes: Recommended .01 μF bypass capacitor from Vcc to GND. Capacitor should be as close to oscillator as possible.

### CARDINAL COMPONENTS

# **Re-Configurable 6 Output CMOS TCXO**

**Series**

**CCT6RC**

### **Electrical Characteristics**

|      | Description                | Conditions                                                                                                                                                                                                                                   | Min | Түр | Max | Unit     |

|------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----------|

| loh  | Output High Current        | Voh = (L)Vdd - 0.5, (L)Vdd = 3.3 V                                                                                                                                                                                                           | 12  | 24  |     | mA       |

| lol  | Output Low Current         | Vol = .5, (L)Vdd = 3.3 V                                                                                                                                                                                                                     | 12  | 24  |     | mA       |

| Vih  | High Level Input Voltage   | CMOS levels, % of Vdd                                                                                                                                                                                                                        | 0.7 |     |     | V        |

| Vil  | Low-Level Input Voltage    | CMOS levels, % of Vdd                                                                                                                                                                                                                        |     |     | 0.3 | V        |

| lih  | Input High Current         | Vin = AVdd - 0.3 V                                                                                                                                                                                                                           |     | <1  | 10  | μА       |

| lil  | Input Low Current          | Vin = + 0.3 V                                                                                                                                                                                                                                |     | <1  | 10  | μА       |

| loz  | Output Leakage Current     | tri-state outputs                                                                                                                                                                                                                            |     |     | 10  | μА       |

| Idd  | Total Power Supply Current | Example 1: 1 output@200 MHz; 1 output@66.666 MHz 1 output@100 MHz; 1 output@50 MHz 1 output@25 MHz; 1 output@12 MHz; Example 2: 1 output@200 Mhz; 1 output@155.52 MHz 1 output@100 Mhz; 1 output@77.76 MHz 1 output@50 Mhz; 1 output@12 MHz; |     | 35  |     | mA<br>mA |

| Idds | Shutdown Power Supply Curr | Shutdown active                                                                                                                                                                                                                              |     | 5   | 20  | μА       |

## **Output Clock Switching Characteristics**

|      | DESCRIPTION                                  | Conditions                                    | MIN  | Түр | Max | Unit |

|------|----------------------------------------------|-----------------------------------------------|------|-----|-----|------|

| 1/t1 | Output Frequency                             | Clock output limit, CMOS, Commercial          |      |     | 200 | MHz  |

| t3   | Rising Edge Slew Rate                        | Output clock rise time, 20% – 80% Vdd         | 0.75 | 1.4 |     | nS   |

| t4   | Falling Edge Slew Rate                       | Output clock fall time, 20% – 80% Vdd         | 0.75 | 1.4 |     | nS   |

| t5   | Output tri-state timing after SD/OE switches | Time for output to enter/leave tri-state mode |      | 150 | 300 | nS   |

| t6   | Clock Jitter<br>measured at Vdd/2            | Peak-to-Peak period jitter, CLK outputs       |      | 200 |     | pS   |

|      | Frequency Switch Time                        | Change time                                   |      | 2   | 4   | ms   |

### CARDINAL COMPONENTS

OUTPUT

OUTPUT

OUTPUT

ALL

THREE-STATE

OUTPUTS

CLK OUTPUT

CLK OUTPUT

CLK OUTPUT

CLK OUTPUT

OUTPUT

OUTPUT

CLK OUTPUT

CLK OUTPUT

OUTPUT

OUTPUT

CLK OUTPUT

OUTPUT

OUTPUT

OUTPUT

CLK OUTPUT

OUTP

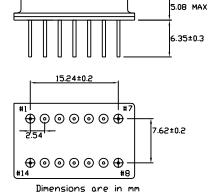

DIP

PIN FUNCTION

PIN 1 OE (CONNECT TO VDD)

PIN 2 SUSPEND (CONNECT TO GND)

PIN 3 VDD

PIN 3 VDD

PIN 4 CLK C OUTPUT

PIN 5 CONNECT TO PIN 6

PIN 6 CONNECT TO PIN 5

PIN 7 GND

PIN 8 12 MHz REF CLOCK OUTPUT

PIN 9 CLK D OUTPUT

PIN 10 CLK E OUTPUT

PIN 11 SDAT

PIN 12 SCLK

PIN 13 CLK A OUTPUT

PIN 13 CLK B OUTPUT

PIN 14 CLK B OUTPUT

Cardinal Components, Inc., 155 Rt. 46 W, Wayne, NJ. 07470 TEL: (973)785-1333 FAX: (973)785-0053 http://www.cardinalxtal.com E-Mail: cardinal@cardinalxtal.com

Specifications subject to change without notice. Check website for latest updates

**Series**

CCT6RC

### Flash Programmability:

Non-Volatile programming enables easy customization, ultrafast turnaround, performance tweaking, design timing margin testing, inventory control, lower part count, and more secure product supply. In addition, any part in the family can also be programmed multiple times, which reduces programming errors and provides an easy upgrade path for existing designs.

#### Feature of the I<sup>2</sup>C-bus:

- Only two bus lines are required; a serial data line (SDA) and a serial clock line (SCL)

- Each device connected to the bus is software addressable by a unique address and simple master/slave relationship exist at all times; master can operate as a master-transmitter or as master-receivers

- It's a true multi-master bus including collision detection and arbitration to prevent data corruption if two or more master simultaneously initiate data transfer

- Serial 8-bit oriented, bidirectional data transfers can be made at up to 100 Kbit/s in the standard mode, up to 400 kbit/s in the fast-mode, or up to 3.4 Mbit/s in the High-speed mode

### **Designer Benefits:**

I<sup>2</sup>C bus compatible In Circuit Reconfigurable Oscillator "ICRO" allow a system design to rapidly progress directly from a functional block diagram to a prototype. Moreover, since they 'clip' directly onto the I<sup>2</sup>C bus without any additional external interfacing, they allow a prototype system to be modified or upgraded simply by 'clipping' or 'unclipping' ICRO to or from the bus.

Here are some of the feature of I<sup>2</sup>C- bus compatible ICRO which are particularly attractive to designer

- Functional blocks on the block diagram correspond with the actual ICRO designs proceed rapidly from block diagram

to final schematic

- No need to design bus interfaces because the I<sup>2</sup>C-bus interface is already integrated on the ICRO

- Integrated addressing and data-transfer protocol allow systems to be completely software-defined

- The same ICRO types can often be used in many different applications

- Design-time reduces as designers quickly become familiar with the frequently used functional book represented by I<sup>2</sup>C-bus compatible and ICRO

- ICRO can be added to or remove from system without affecting any other circuits on the bus

In addition to these advantages, the CMOS ICRO in the I<sup>2</sup>C-bus compatible range offer designers special feature which are particularly attractive for portable equipment and battery-backed systems.

#### They All Have:

- Extremely low current consumption

- High Noise immunity

- Wide operating temperature range

#### **Manufacturer Benefits**

I<sup>2</sup>C-bus compatible ICRO don't only assist designer, they also give a wider range of benefits to the equipment manufacturer because:

- The simple 2-wire serial I<sup>2</sup>C bus minimizes interconnections so ICRO have fewer pins and there are not so many PCB tracks; result- smaller and less expensive PCBs

- The completely integrated I<sup>2</sup>C-bus protocol eliminates the need for address decoders and other 'glue logic'

- The multi-master capability of the I<sup>2</sup>C-bus allows rapid testing and alignment of end-user equipment via external connections to an assembly line

- I<sup>2</sup>C-bus handbook, I<sup>2</sup>C Website: www.semiconductors.philips.com/I2C