# **Freescale Semiconductor**

MPXV7002 Rev 2, 1/2009

# Integrated Silicon Pressure Sensor On-Chip Signal Conditioned, Temperature Compensated and Calibrated

The MPXV7002 series piezoresistive transducers are state-of-the-art monolithic silicon pressure sensors designed for a wide range of applications, but particularly those employing a microcontroller or microprocessor with A/D inputs. This transducer combines advanced micromachining techniques, thin-film metallization, and bipolar processing to provide an accurate, high level analog output signal that is proportional to the applied pressure.

### **Features**

- 2.5% Typical Error over +10°C to +60°C with Auto Zero

- 6.25% Maximum Error over +10°C to +60°C without Auto Zero

- Ideally Suited for Microprocessor or Microcontroller-Based Systems

- Thermoplastic (PPS) Surface Mount Package

- Temperature Compensated over +10° to +60°C

- Patented Silicon Shear Stress Strain Gauge

- · Available in Differential and Gauge Configurations

# MPXV7002 Series

-2 to 2 kPa (-0.3 to 0.3 psi) 0.5 to 4.5 V Output

# **Application Examples**

- Hospital Beds

- HVAC

- · Respiratory Systems

- Process Control

| ORDERING INFORMATION |                                         |      |            |        |               |       |              |          |            |

|----------------------|-----------------------------------------|------|------------|--------|---------------|-------|--------------|----------|------------|

| Device Name          | Package                                 | Case | # of Ports |        | Pressure Type |       |              | Device   |            |

| Device Name          | Options                                 | No.  | None       | Single | Dual          | Gauge | Differential | Absolute | Marking    |

| Small Outline Packag | Small Outline Package (MPXV7002 Series) |      |            |        |               |       |              |          |            |

| MPXV7002GC6U         | Rails                                   | 482A |            | •      |               | •     |              |          | MPXV7002G  |

| MPXV7002GC6T1        | Tape & Reel                             | 482A |            | •      |               | •     |              |          | MPXV7002G  |

| MPXV7002GP           | Trays                                   | 1369 |            | •      |               | •     |              |          | MPXV7002G  |

| MPXV7002DP           | Trays                                   | 1351 |            |        | •             |       | •            |          | MPXV7002DP |

### **SMALL OUTLINE PACKAGE**

MPXV7002GC6U/C6T1 CASE 482A-01

MPXV7002GP CASE 1369-01

MPXV7002DP CASE 1351-01

# **Operating Characteristics**

**Table 1. Operating Characteristics** ( $V_S = 5.0 \text{ Vdc}$ ,  $T_A = 25^{\circ}\text{C}$  unless otherwise noted. Decoupling circuit shown in Figure 3 required to meet specification.)

| Characteristic                                                |              | Symbol           | Min  | Тур                 | Max   | Unit              |

|---------------------------------------------------------------|--------------|------------------|------|---------------------|-------|-------------------|

| Pressure Range <sup>(1)</sup>                                 |              | P <sub>OP</sub>  | -2.0 | _                   | 2.0   | kPa               |

| Supply Voltage <sup>(2)</sup>                                 |              | V <sub>S</sub>   | 4.75 | 5.0                 | 5.25  | Vdc               |

| Supply Current                                                |              | Io               | _    | _                   | 10    | mAdc              |

| Pressure Offset <sup>(3)</sup> @ V <sub>S</sub> = 5.0 Volts   | (10 to 60°C) | V <sub>off</sub> | 2.25 | 2.5                 | 2.75  | Vdc               |

| Full Scale Output <sup>(4)</sup> @ V <sub>S</sub> = 5.0 Volts | (10 to 60°C) | V <sub>FSO</sub> | 4.25 | 4.5                 | 4.75  | Vdc               |

| Full Scale Span <sup>(5)</sup> @ V <sub>S</sub> = 5.0 Volts   | (10 to 60°C) | V <sub>FSS</sub> | 3.5  | 4.0                 | 4.5 V | Vdc               |

| Accuracy <sup>(6)</sup>                                       | (10 to 60°C) | _                | _    | ±2.5 <sup>(7)</sup> | ±6.25 | %V <sub>FSS</sub> |

| Sensitivity                                                   |              | V/P              | _    | 1.0                 |       | V/kPa             |

| Response Time <sup>(8)</sup>                                  |              | t <sub>R</sub>   | _    | 1.0                 |       | ms                |

| Output Source Current at Full Scale Output                    |              | I <sub>O+</sub>  | _    | 0.1                 |       | mAdc              |

| Warm-Up Time <sup>(9)</sup>                                   |              | _                | _    | 20                  |       | ms                |

- 1. 1.0 kPa (kiloPascal) equals 0.145 psi.

- 2. Device is ratiometric within this specified excitation range.

- 3. Offset (Voff) is defined as the output voltage at the minimum rated pressure.

- 4. Full Scale Output (V<sub>FSO</sub>) is defined as the output voltage at the maximum or full rated pressure.

- Full Scale Span (V<sub>FSS</sub>) is defined as the algebraic difference between the output voltage at full rated pressure and the output voltage at the minimum rated pressure.

- 6. Accuracy (error budget) consists of the following:

Linearity: Output deviation from a straight line relationship with pressure over the specified pressure range.

Temperature Hysteresis: Output deviation at any temperature within the operating temperature range, after the temperature is cycled to

and from the minimum or maximum operating temperature points, with zero differential pressure applied.

Pressure Hysteresis: Output deviation at any pressure within the specified range, when this pressure is cycled to and from the

minimum or maximum rated pressure, at 25°C.

TcSpan: Output deviation over the temperature range of 10° to 60°C, relative to 25°C.

TcOffset: Output deviation with minimum rated pressure applied, over the temperature range of 10° to 60°C, relative to

25°C.

Variation from Nominal: The variation from nominal values, for Offset or Full Scale Span, as a percent of V<sub>FSS</sub>, at 25°C.

- 7. Auto Zero at Factory Installation: Due to the sensitivity of the MPXV7002 Series, external mechanical stresses and mounting position can affect the zero pressure output reading. Auto zero is defined as storing the zero pressure output reading and subtracting this from the device's output during normal operations. Reference AN1636 for specific information. The specified accuracy assumes a maximum temperature change of ± 5°C between auto zero and measurement.

- 8. Response Time is defined as the time for the incremental change in the output to go from 10% to 90% of its final value when subjected to a specified step change in pressure.

- 9. Warm-up Time is defined as the time required for the product to meet the specified output voltage after the Pressure has been stabilized.

# **Maximum Ratings**

Table 2. Maximum Ratings<sup>(1)</sup>

| Rating                     | Symbol           | Value       | Unit |

|----------------------------|------------------|-------------|------|

| Maximum Pressure (P1 > P2) | P <sub>max</sub> | 75          | kPa  |

| Storage Temperature        | T <sub>stg</sub> | -30 to +100 | °C   |

| Operating Temperature      | T <sub>A</sub>   | 10 to 60    | °C   |

<sup>1.</sup> Exposure beyond the specified limits may cause permanent damage or degradation to the device.

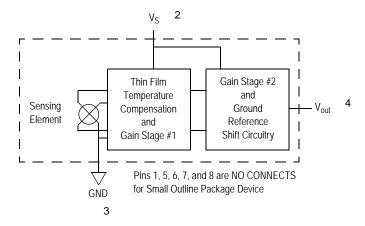

Figure 1 shows a block diagram of the internal circuitry integrated on a pressure sensor chip.

Figure 1. Integrated Pressure Sensor Schematic

# ON-CHIP TEMPERATURE COMPENSATION, CALIBRATION AND SIGNAL CONDITIONING

The performance over temperature is achieved by integrating the shear-stress strain gauge, temperature compensation, calibration and signal conditioning circuitry onto a single monolithic chip.

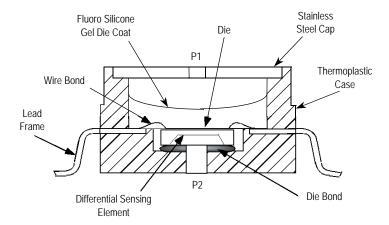

Figure 2 illustrates the Differential or Gauge configuration in the basic chip carrier (Case 482). A gel die coat isolates the die surface and wire bonds from the environment, while allowing the pressure signal to be transmitted to the sensor diaphragm.

The MPXV7002 series pressure sensor operating characteristics, and internal reliability and qualification tests are based on use of dry air as the pressure media. Media, other than dry air, may have adverse effects on sensor

performance and long-term reliability. Contact the factory for information regarding media compatibility in your application.

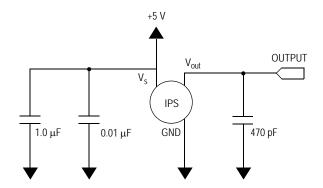

Figure 3 shows the recommended decoupling circuit for interfacing the integrated sensor to the A/D input of a microprocessor or microcontroller. Proper decoupling of the power supply is recommended.

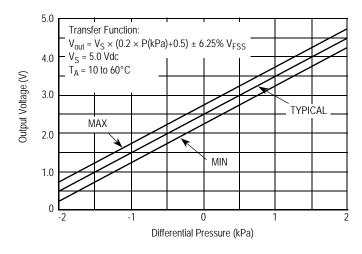

Figure 4 shows the sensor output signal relative to pressure input. Typical, minimum, and maximum output curves are shown for operation over a temperature range of 10° to 60°C using the decoupling circuit shown in Figure 3. The output will saturate outside of the specified pressure range.

Figure 2. Cross-Sectional Diagram SOP (not to scale)

Figure 3. Recommended Power Supply Decoupling and Output Filtering (For additional output filtering, please refer to Application Note AN1646.)

Figure 4. Output versus Pressure Differential

# PRESSURE (P1)/VACUUM (P2) SIDE IDENTIFICATION TABLE

Freescale designates the two sides of the pressure sensor as the Pressure (P1) side and the Vacuum (P2) side. The Pressure (P1) side is the side containing a gel die coat which protects the die from harsh media.

The Pressure (P1) side may be identified by using the following table:

| Part Number        | Case Type | Pressure (P1)<br>Side Identifier |  |  |

|--------------------|-----------|----------------------------------|--|--|

| MPXV7002GC6U/GC6T1 | 482A-01   | Side with Port Attached          |  |  |

| MPXV7002GP         | 1369-01   | Side with Port Attached          |  |  |

| MPXV7002DP         | 1351-01   | Side with Part Marking           |  |  |

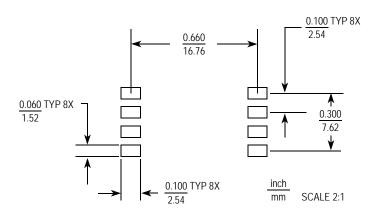

## MINIMUM RECOMMENDED FOOTPRINT FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the total design. The footprint for the surface mount packages must be the correct size to ensure proper solder connection interface between the board and the package. With the correct

footprint, the packages will self align when subjected to a solder reflow process. It is always recommended to design boards with a solder mask layer to avoid bridging and shorting between solder pads.

Figure 5. Small Outline Package Footprint

- NOTES:

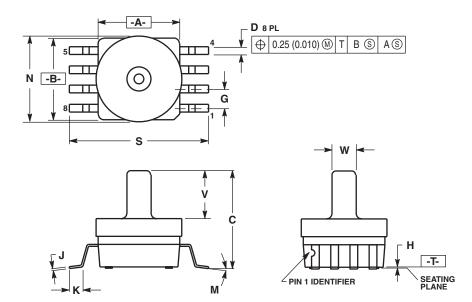

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006).

5. ALL VERTICAL SURFACES 5" TYPICAL DRAFT.

|     | INC       | HES   | MILLIM   | IETERS |  |  |

|-----|-----------|-------|----------|--------|--|--|

| DIM | MIN       | MAX   | MIN      | MAX    |  |  |

| Α   | 0.415     | 0.425 | 10.54    | 10.79  |  |  |

| В   | 0.415     | 0.425 | 10.54    | 10.79  |  |  |

| C   | 0.500     | 0.520 | 12.70    | 13.21  |  |  |

| D   | 0.038     | 0.042 | 0.96     | 1.07   |  |  |

| G   | 0.100 BSC |       | 2.54 BSC |        |  |  |

| Н   | 0.002     | 0.010 | 0.05     | 0.25   |  |  |

| J   | 0.009     | 0.011 | 0.23     | 0.28   |  |  |

| K   | 0.061     | 0.071 | 1.55     | 1.80   |  |  |

| M   | 0°        | 7°    | 0°       | 7°     |  |  |

| N   | 0.444     | 0.448 | 11.28    | 11.38  |  |  |

| S   | 0.709     | 0.725 | 18.01    | 18.41  |  |  |

| ٧   | 0.245     | 0.255 | 6.22     | 6.48   |  |  |

| W   | 0.115     | 0.125 | 2.92     | 3.17   |  |  |

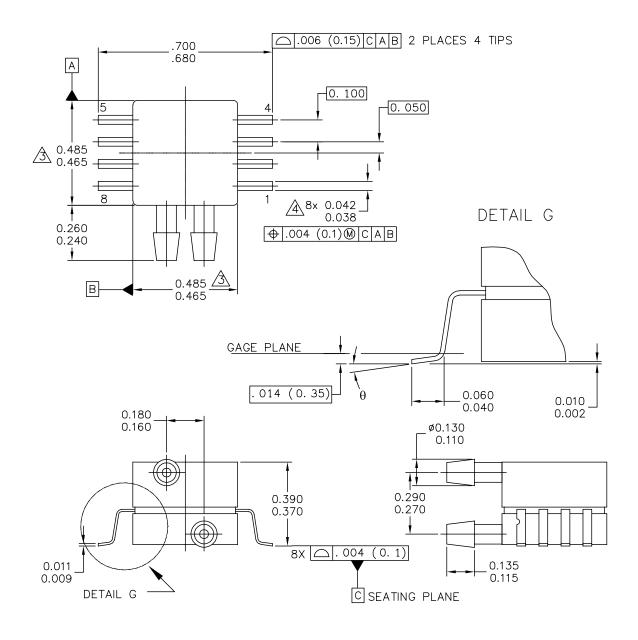

**CASE 482A-01 ISSUE A SMALL OUTLINE PACKAGE**

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                               |           | DOCUMENT NO  | ): 98ASA99255D   | REV: A      |

| 8 LD SNSR. DUAL                                      | PORT      | CASE NUMBER  | R: 1351–01       | 27 JUL 2005 |

|                                                      |           | STANDARD: NO | N-JEDEC          |             |

# CASE 1351-01 ISSUE A SMALL OUTLINE PACKAGE

### NOTES:

- 1. CONTROLLING DIMENSION: INCH

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PPROTRUSIONS. MOLD FLASH AND PROTRUSIONS SHALL NOT EXCEED .006 PER SIDE.

DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE .008 MAXIMUM.

|       | STYLE 2:                                  |                                                            |                                                                                 |

|-------|-------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------|

| GND   | PIN                                       | 1:                                                         | N/C                                                                             |

| +Vout | PIN                                       | 2:                                                         | ٧s                                                                              |

| Vs    | PIN                                       | 3:                                                         | GND                                                                             |

| −Vout | PIN                                       | 4:                                                         | Vout                                                                            |

| N/C   | PIN                                       | 5:                                                         | N/C                                                                             |

| N/C   | PIN                                       | 6:                                                         | N/C                                                                             |

| N/C   | PIN                                       | 7:                                                         | N/C                                                                             |

| N/C   | PIN                                       | 8:                                                         | N/C                                                                             |

|       | +Vout<br>Vs<br>-Vout<br>N/C<br>N/C<br>N/C | GND PIN +Vout PIN Vs PIN -Vout PIN N/C PIN N/C PIN N/C PIN | GND PIN 1: +Vout PIN 2: Vs PIN 3: -Vout PIN 4: N/C PIN 5: N/C PIN 6: N/C PIN 7: |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | L OUTLINE | PRINT VERSION NO | OT TO SCALE   |             |

|------------------------------------------------------|-----------|------------------|---------------|-------------|

| TITLE:                                               |           | DOCUMENT NO      | : 98ASA99255D | REV: A      |

| 8 LD SNSR, DUAL                                      | PORT      | CASE NUMBER      | 2: 1351–01    | 27 JUL 2005 |

|                                                      |           | STANDARD: NO     | N-JEDEC       |             |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE | PRINT VERSION NO                | OT TO SCALE |  |

|------------------------------------------------------|--------------------|---------------------------------|-------------|--|

| TITLE:                                               | DOCUMENT N         | 0: 98ASA99303D                  | REV: B      |  |

| 8 LD SOP, SIDE PO                                    | ORT CASE NUMBE     | CASE NUMBER: 1369-01 24 MAY 200 |             |  |

| · ·                                                  | STANDARD: N        | ON-JEDEC                        |             |  |

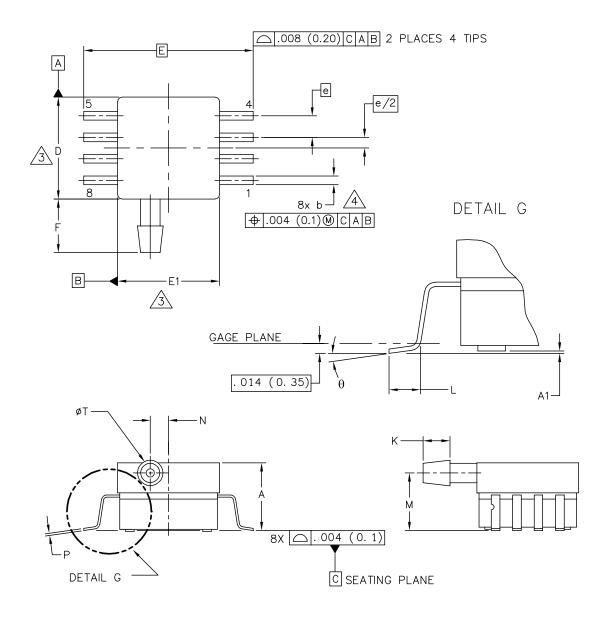

# CASE 1369-01 ISSUE B SMALL OUTLINE PACKAGE

## NOTES:

- 1. CONTROLLING DIMENSION: INCH

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- △ DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PPROTRUSIONS.

MOLD FLASH AND PROTRUSIONS SHALL NOT EXCEED .006 (0.152) PER SIDE.

- DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE .008 (0.203) MAXIMUM.

|                     | INC                                                             | HES         | MIL    | LIMETERS                         |      | I         | NCHES         | ΜI      | LLIMETERS   |

|---------------------|-----------------------------------------------------------------|-------------|--------|----------------------------------|------|-----------|---------------|---------|-------------|

| DIM                 | MIN                                                             | MAX         | MIN    | MAX                              | DIM  | MIN       | MAX           | MIN     | MAX         |

| Α                   | . 300                                                           | . 330       | 7. 11  | 7. 62                            | θ    | 0°        | 7 <b>°</b>    | 0,      | 7°          |

| A1                  | . 002                                                           | . 010       | 0. 05  | 0. 25                            | _    |           |               |         |             |

| b                   | . 038                                                           | . 042       | 0. 96  | 1. 07                            | _    |           |               |         |             |

| D                   | . 465                                                           | . 485       | 11. 81 | 12. 32                           | -    |           |               |         |             |

| E                   | . 717                                                           | BSC         | 18     | .21 BSC                          | _    |           |               |         |             |

| E1                  | . 465                                                           | . 485       | 11. 81 | 12. 32                           | -    |           |               |         |             |

| e                   | . 100                                                           | ) BSC       | 2.     | 54 BSC                           | -    | -         |               |         |             |

| F                   | . 245                                                           | . 255       | 6. 22  | 6. 47                            | -    |           |               |         |             |

| K                   | . 120                                                           | . 130       | 3. 05  | 3. 30                            | -    |           |               |         |             |

| L                   | . 061                                                           | . 071       | 1. 55  | 1. 80                            | _    |           |               |         |             |

| М                   | . 270                                                           | . 290       | 6. 86  | 7. 36                            | _    |           |               |         |             |

| N                   | . 080                                                           | . 090       | 2. 03  | 2. 28                            | _    |           |               |         |             |

| Р                   | . 009                                                           | . 011       | 0. 23  | 0. 28                            | -    |           |               |         |             |

| Т                   | . 115                                                           | . 125       | 2. 92  | 3. 17                            | -    |           |               |         |             |

|                     | EDEECON E CE                                                    | MICONDUCTOR | TNO    |                                  |      |           |               |         |             |

|                     | © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.  MECHANICA |             |        |                                  | L OU | TLINE     | PRINT VER     | SION NO | OT TO SCALE |

| TITLE:              |                                                                 |             |        |                                  | DOC  | JMENT NO  | ): 98ASA99303 | 3D      | REV: B      |

| 8 LD SOP, SIDE PORT |                                                                 |             |        | CASE NUMBER: 1369-01 24 MAY 2005 |      |           |               |         |             |

|                     |                                                                 |             |        |                                  | STAI | NDARD: NO | N-JEDEC       |         |             |

## CASE 1369-01 ISSUE B SMALL OUTLINE PACKAGE

### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

# Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 010 5879 8000 support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or +1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2009. All rights reserved.