# **SerialLite**

# **MegaCore Function User Guide**

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 www.altera.com

MegaCore Function Version: 1.1.0

Document Version: 1.1.0 rev. 1

Document Date: August 2005

Copyright © 2005 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

UG-SERIALLT-1.1

ii MegaCore Function Version 1.1.0 SerialLite MegaCore Function User Guide

**Altera Corporation**

| About This User Guide                               | N           |

|-----------------------------------------------------|-------------|

| Revision History                                    | v           |

| How to Contact Altera                               | v           |

| Typographic Conventions                             | V           |

| Chapter 1. About This MegaCore Function             |             |

| Release Information                                 | 1–1         |

| Device Family Support                               | 1–1         |

| New in Version 1.1.0                                | 1–2         |

| Features                                            | 1–2         |

| OpenCore Plus Evaluation                            | 1–3         |

| Performance                                         | 1–4         |

| Chapter 2. Getting Started                          |             |

| System Requirements                                 | 2–1         |

| Design Flow                                         | 2–1         |

| Obtain & Install the SerialLite MegaCore Function   |             |

| Download the SerialLite MegaCore Function           | 2–2         |

| Install the SerialLite MegaCore Function Files      | <b>2–</b> 3 |

| Directory Structure                                 |             |

| SerialLite MegaCore Function Walkthrough            |             |

| Create a New Quartus II Project                     |             |

| Launch IP Toolbench                                 | 2–6         |

| Step 1: Parameterize                                | 2–7         |

| Step 2: Set Up Simulation                           | 2–13        |

| Step 3: Generate                                    | 2–15        |

| Simulate the Design                                 | 2–17        |

| Compile the Design                                  |             |

| Apply Constraints                                   | 2–18        |

| Set Up Licensing                                    |             |

| Append the License to Your license.dat File         |             |

| Specify the License File in the Quartus II Software |             |

| Chapter 3. Specifications                           |             |

| Functional Description                              |             |

| OpenCore Plus Time-Out Behavior                     |             |

| SerialLite Link Configuration                       |             |

| Link Consistency                                    |             |

| Interface Overview                                  |             |

| Achieving the Desired Bandwidth                     |             |

**Altera Corporation**

| Clock Compensation                | 3–19 |

|-----------------------------------|------|

| Lane Polarity & Order Reversal    |      |

| Choosing Ports                    |      |

| Streaming & Packet Data           |      |

| Packet Sizes                      | 3–30 |

| Channel Multiplexing              | 3–33 |

| Data Integrity Protection: CRC    | 3–36 |

| Retry on Error                    | 3–38 |

| Flow Control                      | 3–42 |

| The Receive FIFO Buffers          | 3–45 |

| Error Handling                    | 3–54 |

| Transceiver Settings              |      |

| Optimizing the Implementation     |      |

| Initialization & Restart          | 3–70 |

|                                   |      |

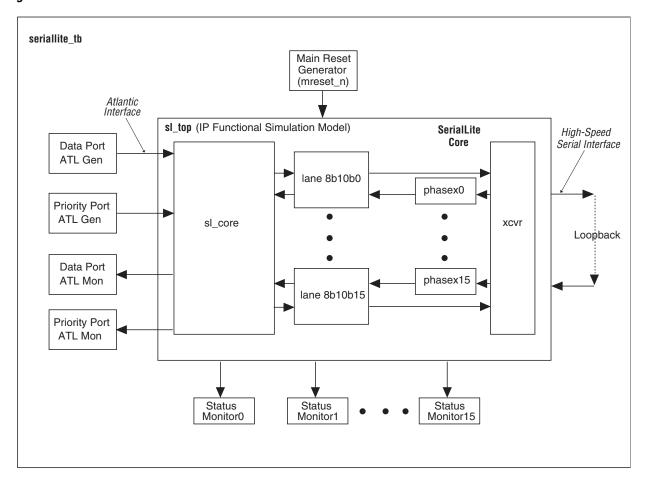

| Chapter 4. SerialLite Testbench   |      |

| General Description               | 4–1  |

| Testbench Environment             | 4–1  |

| Methodology Overview              | 4–2  |

| Configuring the Simulation        | 4–3  |

| ModelSim Simulator                | 4–3  |

| Other Simulators                  | 4–5  |

| Sending & Receiving Data Tasks    | 4–8  |

| User Packet Data                  | 4–11 |

| Running a Simulation              | 4–13 |

| Simulation Pass & Fail Conditions | 4–14 |

## **About This User Guide**

## **Revision History**

The table below displays the revision history for the chapters in this user guide.

| Chapter | Date           | Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | August 2005    | 1.1.0   | <ul><li>Updated the release information.</li><li>Updated the performance information.</li></ul>                                                                                                                                                                                                                                                                                                                                 |

| 2       | August 2005    | 1.1.0   | <ul> <li>Updated the system requirements.</li> <li>Updated Table 2-1. IP Toolbench-Generated Files.</li> <li>Added a reference to the Quartus<sup>®</sup> II Design Space Explorer optimization utility.</li> </ul>                                                                                                                                                                                                             |

| 3       | August 2005    | 1.1.0   | <ul> <li>Corrected the THDAV signal description in Table 3–2.</li> <li>Added a reference to the SerialLite Bandwidth Calculator.</li> <li>Added the Clock Pad Restrictions section.</li> <li>Updated the description of the STATUS PORT[155] signal in Table 3–41.</li> <li>Added a description of the serial loopback (RX_SLPBK) signal to Table 3–54.</li> <li>Corrected the Initialization &amp; Restart section.</li> </ul> |

| 4       | August 2005    | 1.1.0   | <ul> <li>Modified the "Configuring the Simulation" section to correct the<br/>testbench parameter names.</li> </ul>                                                                                                                                                                                                                                                                                                             |

| All     | September 2004 | 1.0.0   | First version of user guide.                                                                                                                                                                                                                                                                                                                                                                                                    |

## How to Contact Altera

For the most up-to-date information about Altera® products, go to the Altera world-wide web site at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

| Information Type           | USA & Canada                                                   | All Other Locations                                                   |

|----------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------|

| Technical support          | www.altera.com/mysupport/                                      | www.altera.com/mysupport/                                             |

|                            | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) | +1 408-544-8767<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time |

| Product literature         | www.altera.com                                                 | www.altera.com                                                        |

| Altera literature services | literature@altera.com                                          | literature@altera.com                                                 |

| Information Type               | USA & Canada   | All Other Locations                                                    |

|--------------------------------|----------------|------------------------------------------------------------------------|

| Non-technical customer service | (800) 767-3753 | + 1 408-544-7000<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time |

| FTP site                       | ftp.altera.com | ftp.altera.com                                                         |

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                                                                                                                                                                                 |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file.                                                                                                                                                                                                                            |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Design.                                                                                                                                                                                                                                                                                                                                                            |

| Italic type                                 | Internal timing parameters and variables are shown in italic type. Examples: $t_{PIA}$ , $n+1$ .  Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <i><file name=""></file></i> , <i><project name=""></project></i> .pof file.                                                                                                                                                                                                      |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                                                                                                                                                                               |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                                                                                                                                                                               |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.  Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc.         | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                                                                                                                                                                           |

| •••                                         | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                                                                                                                                                                       |

| ✓                                           | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                                                                                                                                                                            |

| Visual Cue | Meaning                                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAUTION    | The caution indicates required information that needs special consideration and understanding and should be read prior to starting or continuing with the procedure or process. |

| A          | The warning indicates information that should be read prior to starting or continuing the procedure or processes                                                                |

| 4          | The angled arrow indicates you should press the Enter key.                                                                                                                      |

|            | The feet direct you to more information on a particular topic.                                                                                                                  |

Altera Corporation vii

# 1. About This MegaCore Function

## Release Information

Table 1–1 provides information about this release of the Altera® SerialLite MegaCore® function.

| Table 1–1. SerialLite Release Information |               |  |  |  |

|-------------------------------------------|---------------|--|--|--|

| Item                                      | Description   |  |  |  |

| Version                                   | 1.1.0         |  |  |  |

| Release Date                              | August 2005   |  |  |  |

| Ordering Code                             | IP-SERIALLITE |  |  |  |

| Product ID                                | 00A6          |  |  |  |

| Vendor ID                                 | 6AF7          |  |  |  |

# Device Family Support

MegaCore functions provide either full or preliminary support for target Altera device families:

- Full support means the MegaCore function meets all functional and timing requirements for the device family and may be used in production designs.

- Preliminary support means the MegaCore function meets all functional requirements, but may still be undergoing timing analysis for the device family; it may be used in production designs with caution.

Table 1–2 shows the level of support offered by the SerialLite MegaCore function to each Altera device family.

| Table 1–2. Device Family Support |              |  |

|----------------------------------|--------------|--|

| Device Family                    | Support      |  |

| Stratix <sup>®</sup> GX          | Full support |  |

| Other device families            | No support   |  |

#### Introduction

The SerialLite MegaCore function is a simple, high-speed, low-latency, low-resource, point-to-point serial data communication link. It implements the full SerialLite protocol with performance up to 3.125 Gbps across the serial data communication link. It is highly configurable, providing a wide range of functionality suited to moving data in many different environments.

# New in Version 1.1.0

Maintenance release

For details, refer to the *SerialLite MegaCore Function Errata Sheet* v1.0.0 and v1.1.0 available at **www.altera.com/literature/lit-es.jsp.**

#### **Features**

- 500 Mbps to 3.125 Gbps per lane

- Supports up to 16 lanes

- Support for two user packet types: data packet and priority packet

- Nesting of time-critical priority packets within regular data packets

- Unrestricted data packet size

- Priority packet size up to 256 bytes

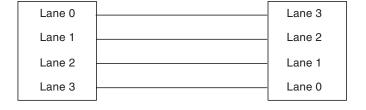

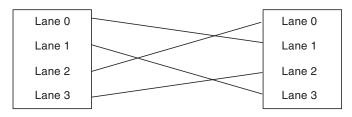

- Optional lane polarity reversal

- Optional lane order reversal

- Optional packet integrity protection using cyclic redundancy code CRC-32 or CRC-16

- Optional priority packet retry-on-error

- Optional flow control

- Automatic handling of idles

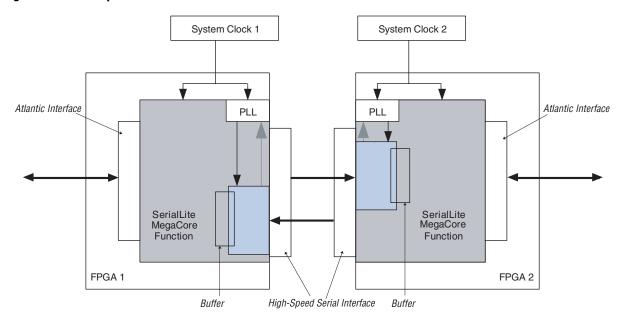

- Synchronous or asynchronous operation

- Automatic clock rate compensation for asynchronous use

- 100 and 300 parts per million (ppm)

- Error detection

- Atlantic<sup>™</sup> interface compliant

- 8B/10B physical layer encoding and decoding

- Electricals based on familiar XAUI standard

- Low protocol overhead and logic usage

- Low point-to-point transfer latency

- No inter-frame gaps required

- Easy-to-use IP Toolbench interface

- IP functional simulation models for use in Altera-supported VHDL and Verilog HDL simulators

- Support for OpenCore® Plus evaluation

# General Description

The SerialLite MegaCore function provides a simple and lightweight way to move data from one point to another reliably at high speeds. It consists of a serial link of up to 16 bonded lanes, with logic to provide a number of basic and optional link support functions. The Atlantic interface is used as the primary access for delivering and receiving data.

The SerialLite protocol specifies a link that is simple to build, uses as little logic as possible, and requires little work for a logic designer to utilize. All of the features available in the SerialLite protocol have been implemented in the SerialLite MegaCore function and are parameterizable through a powerful MegaWizard® Plug-In Manager interface.

A link built using the SerialLite MegaCore function can operate at speeds from 500 Mbps to 3.125 Gbps. Link reliability is enhanced by the 8B/10B encoding scheme and optional cyclic redundancy code (CRC) capabilities. Further reductions in the bit-error rate can be achieved using the optional retry-on-error feature. Data rate and consumption mismatches can be accommodated using the optional clock-compensation and flow-control features to ensure that no data is lost.

The combination of optional capabilities makes the link well-suited to a wide variety of applications. It is intended to support chip-to-chip, board-to-board, and cross-backplane data transfers.

#### OpenCore Plus Evaluation

With the free Altera OpenCore Plus evaluation feature, you can perform the following actions:

- Simulate the behavior of a MegaCore function within your system

- Verify the functionality of your design, as well as quickly and easily evaluate its size and speed

- Generate time-limited device programming files for designs that include MegaCore functions

- Program a device and verify your design in hardware

You only need to purchase a license for the MegaCore function when you are completely satisfied with its functionality and performance, and want to take your design to production.

For more information on OpenCore Plus hardware evaluation using the SerialLite MegaCore function, see "OpenCore Plus Time-Out Behavior" on page 3–1 and *AN 320: OpenCore Plus Evaluation of Megafunctions*.

## **Performance**

Table 1–3 shows typical expected performance for different parameters, using the Quartus® II software, version 5.0 Service Pack 1.

| Table 1–3. Performance |                 |                  |           |        |                 |                   |                   |      |     |                           |

|------------------------|-----------------|------------------|-----------|--------|-----------------|-------------------|-------------------|------|-----|---------------------------|

| Parameters             |                 |                  |           |        |                 | Lania             | Memory            |      |     |                           |

| Number of Lanes        | Regular<br>Port | Priority<br>Port | Mode      | CRC    | Flow<br>Control | Retry<br>on Error | Logic<br>Elements | M512 | M4K | f <sub>MAX</sub><br>(MHz) |

| 1                      | <b>✓</b>        | _                | Streaming | _      | -               | -                 | 795               | 2    | 1   | >156                      |

| 4                      | <b>✓</b>        | _                | Streaming | _      | _               | _                 | 2,088             | 12   | 8   | >156                      |

| 1                      | <b>✓</b>        | <b>✓</b>         | Packet    | CRC-16 | <b>✓</b>        | <b>✓</b>          | 2,319             | 5    | 15  | >156                      |

| 1                      | <b>✓</b>        | _                | Packet    | CRC-16 | _               | -                 | 1,072             | 2    | 3   | >156                      |

| 1                      | _               | <b>✓</b>         | Packet    | CRC-16 | <b>✓</b>        | <b>✓</b>          | 1,878             | 3    | 12  | >156                      |

| 1                      | <b>✓</b>        | <b>✓</b>         | Packet    | CRC-32 | _               | -                 | 3,189             | 5    | 10  | >156                      |

| 1                      | <b>✓</b>        | <b>✓</b>         | Packet    | CRC-32 | <b>✓</b>        | ✓                 | 4,117             | 7    | 16  | >156                      |

| 2                      | <b>✓</b>        | <b>✓</b>         | Packet    | CRC-32 | -               | -                 | 5,443             | 21   | 10  | >156                      |

| 2                      | <b>✓</b>        | <b>✓</b>         | Packet    | CRC-32 | <b>✓</b>        | ✓                 | 6,452             | 19   | 18  | >156                      |

| 4                      | <b>✓</b>        | <b>✓</b>         | Packet    | _      | <b>✓</b>        | -                 | 3,686             | 27   | 17  | >156                      |

| 4                      | <b>✓</b>        | <b>✓</b>         | Packet    | _      | <b>✓</b>        | <b>✓</b>          | 4,653             | 24   | 31  | >156                      |

| 4                      | <b>✓</b>        | <b>✓</b>         | Packet    | CRC-16 | <b>✓</b>        | <b>✓</b>          | 5,196             | 26   | 32  | >156                      |

| 4                      | <b>✓</b>        | _                | Packet    | CRC-16 | -               | -                 | 2,880             | 22   | 5   | >156                      |

| 4                      | _               | <b>✓</b>         | Packet    | CRC-16 | <b>✓</b>        | ✓                 | 4,050             | 20   | 25  | >156                      |

| 4                      | <b>✓</b>        | <b>✓</b>         | Packet    | CRC-32 | <b>✓</b>        | ✓                 | 10,809            | 30   | 33  | >156                      |

| 4                      | _               | <b>✓</b>         | Packet    | CRC-32 | <b>✓</b>        | ✓                 | 7,143             | 24   | 26  | >156                      |

| 4                      | <b>✓</b>        | _                | Packet    | CRC-32 | <b>✓</b>        | -                 | 6,350             | 24   | 7   | >156                      |

| 4                      | <b>✓</b>        | <b>✓</b>         | Packet    | CRC-32 | _               | <b>✓</b>          | 10,703            | 30   | 33  | 139                       |

| 4                      | <b>✓</b>        | <b>✓</b>         | Packet    | CRC-32 | _               | _                 | 9,560             | 36   | 17  | >156                      |

| 7                      | <b>✓</b>        | <b>✓</b>         | Packet    | _      | <b>✓</b>        | <b>✓</b>          | 6,827             | 34   | 53  | 145                       |

| 7                      | <b>✓</b>        | <b>✓</b>         | Packet    | CRC-32 | <b>✓</b>        | <b>✓</b>          | 18,471            | 50   | 53  | 139                       |

| 16                     | <b>✓</b>        | <b>✓</b>         | Packet    | _      | <b>✓</b>        | <b>✓</b>          | 13,138            | 32   | 131 | 128                       |

| 16                     | <b>✓</b>        | <b>✓</b>         | Packet    | CRC-32 | <b>✓</b>        | <b>✓</b>          | 38,529            | 96   | 117 | 105                       |

## 2. Getting Started

## System Requirements

The instructions in this section require the following hardware and software:

- A PC running the Windows NT/2000/XP, Red Hat Linux 7.3 or 8.0, or Red Hat Enterprise Linux 3.0 operating system; or a Sun workstation running the Solaris 8 or 9 operating system

- Quartus® II software version 5.0 Service Pack 1 or higher

- ModelSim<sup>®</sup> version 6.0c or higher for running the testbench

- Verilog 2000 support

- 2 GB of RAM highly recommended

### **Design Flow**

The design flow to evaluate the SerialLite MegaCore<sup>®</sup> function using the OpenCore<sup>®</sup> Plus feature involves the following steps:

- 1. Obtain and install the SerialLite MegaCore function.

- 2. Create a custom variation of the SerialLite MegaCore function using IP Toolbench.

IP Toolbench is a toolbar from which you can quickly and easily view documentation, specify parameters, and generate all of the files necessary for integrating the parameterized MegaCore function into your design. You can launch IP Toolbench from within the Quartus II software.

- 3. Implement the rest of your design using the design entry method of your choice.

- 4. Use the IP Toolbench-generated IP functional simulation model to verify the operation of your design.

For more information on IP functional simulation models, see the *Simulating Altera in Third-Party Simulation Tools* chapter in Volume 3 of the *Quartus II Handbook*.

5. Use the Quartus II software to compile your design.

You may also generate an OpenCore Plus time-limited programming file, which you can use to verify the operation of your design in hardware.

6. Purchase a license for the SerialLite MegaCore function.

Once you have purchased a license for the SerialLite MegaCore function, the design flow involves the following additional steps:

- 1. Set up licensing.

- 2. Generate a programming file for the Altera® device(s) on your board.

- 3. Program the Altera device(s) with the completed design.

- 4. Perform design verification.

# Obtain & Install the SerialLite MegaCore Function

Before you can start using Altera MegaCore functions, you must obtain the MegaCore files and install them on your computer. Altera MegaCore functions can be installed from the MegaCore IP Library CD-ROM either during or after Quartus II installation, or downloaded individually from the Altera web site and installed separately.

The following instructions describe the process of downloading and installing the SerialLite MegaCore function. If you have already installed the SerialLite MegaCore function from the MegaCore IP Library CD-ROM, skip to "Directory Structure" on page 2–4.

#### Download the SerialLite MegaCore Function

If you have Internet access, you can download MegaCore functions from Altera's web site at **www.altera.com**. Follow the instructions below to obtain the SerialLite MegaCore function via the Internet. If you do not have Internet access, contact your local Altera representative to obtain the MegaCore IP Library CD-ROM.

- 1. Point your web browser to www.altera.com/ipmegastore.

- 2. Type SerialLite in the **IP MegaSearch** box.

- Click Go.

- 4. Choose **SerialLite** from the search results page. The product description web page displays.

- Click **Download Free Evaluation** on the top right of the product description web page.

- Fill out the registration form and click **Submit Request**.

- Read the Altera MegaCore license agreement, turn on the I have read the license agreement check box, and click Proceed to Download Page.

- Follow the instructions on the SerialLite MegaCore function download and installation page to download the MegaCore function and save it to your hard disk.

There is a specific MegaCore function download file for each supported operating system.

#### Install the SerialLite MegaCore Function Files

The following instructions describe how you install the SerialLite MegaCore function on computers running the Windows, Linux, or Solaris operating systems.

#### Windows

Follow these steps to install the SerialLite MegaCore function on a PC running a supported version of the Windows operating system:

- 1. Choose **Run** (Windows Start menu).

- 2. Type <path name>\slite-v1.1.0.exe, where <path name> is the location of the downloaded MegaCore function.

- Click **OK**. The **SerialLite Installation** dialog box appears. Follow the on-screen instructions to finish installation.

#### Solaris & Linux

Follow these steps to install the SerialLite MegaCore function on a computer running supported versions of the Solaris and Linux operating systems:

Move the compressed files to the desired installation directory and make that directory your current directory.

2. Decompress the package by typing the following command:

```

gzip -d slite-v1.1.0_linux.tar.gz

or

gzip -d slite-v1.1.0 solaris.tar.gz

✓

```

3. Extract the package by typing the following command:

```

tar -xvf slite-v1.1.0_linux.tar←

or

tar -xvf slite-v1.1.0 solaris.tar←

```

#### **Directory Structure**

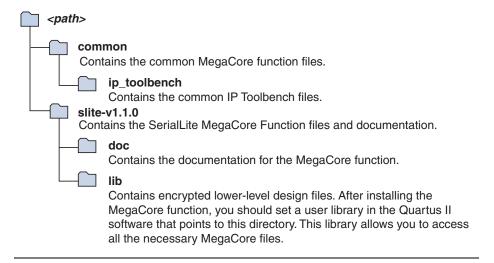

Figure 2–1 shows the directory structure for the SerialLite MegaCore function, where *<path>* is the installation directory.

Figure 2-1. SerialLite MegaCore Function Directory Structure

## SerialLite MegaCore Function Walkthrough

This walkthrough explains how to create a SerialLite MegaCore function variation using the Altera SerialLite IP Toolbench and the Quartus II software on a PC. When you are finished generating a SerialLite MegaCore function variation, you can incorporate it into your overall project.

This walkthrough involves the following steps:

- "Create a New Quartus II Project" on page 2–5

- "Launch IP Toolbench" on page 2–6

- Step 1: Parameterize" on page 2–7

- "Step 2: Set Up Simulation" on page 2–13

- "Step 3: Generate" on page 2–15

#### Create a New Quartus II Project

Before you begin, you must create a new Quartus II project. With the New Project wizard, you specify the working directory for the project, assign the project name, and designate the name of the top-level design entity. You also specify the SerialLite MegaCore function user library. To create a new project, follow these steps:

- 1. Choose **Programs > Altera > Quartus II** <*version>* (Windows Start menu) to run the Quartus II software. You can also use the Quartus II Web Edition software.

- 2. Choose **New Project Wizard** (File menu).

- 3. Click **Next** in the introduction (the introduction does not display if you turned it off previously).

- 4. Specify the working directory for your project. This walkthrough uses the directory **c:\temp**.

- 5. Specify the name of the project. This walkthrough uses **example**.

- You must specify the same name for the project name and the top-level design entity name.

- Click Next.

- Steps 7 to 10 are only required if you are running the Solaris or Linux operating system.

- 7. Click User Libraries.

- 8. Type <path>\slite-v1.1.0\lib\ into the **Library name** box, where <path> is the directory in which you installed the SerialLite MegaCore function. The default installation directory is c:\MegaCore.

- 9. Click **Add**.

- 10. Click **OK**.

- 11. Click Next.

- 12. Choose the Stratix<sup>®</sup> GX family in the **Family** list.

- 13. Click Finish.

You have finished creating your new Quartus II project.

#### Launch IP Toolbench

To launch IP Toolbench in the Quartus II software, follow these steps:

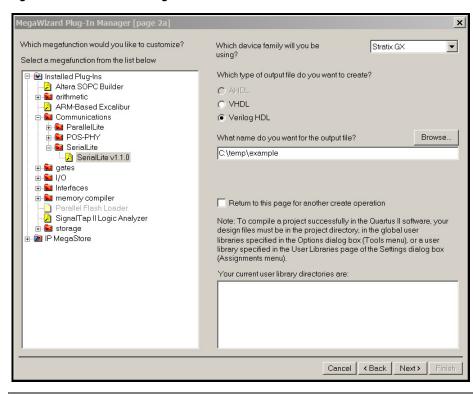

1. Start the MegaWizard® Plug-In Manager by choosing **MegaWizard Plug-In Manager** (Tools menu). The **MegaWizard Plug-In Manager** dialog box is displayed.

Refer to the Quartus II Help for more information on how to use the MegaWizard Plug-In Manager.

- 2. Specify that you want to create a new megafunction variation and click **Next**.

- 3. Choose **SerialLite v1.1.0** in the **Communications > SerialLite** directory.

- 4. Select the output file type for your design; the wizard supports VHDL and Verilog HDL.

- 5. Specify a name for the MegaCore function files, <*directory name*>\<*variation name*>. Figure 2–2 on page 2–7 shows the wizard after you have made these settings.

Figure 2–2. Select the MegaCore Function

Click Next to launch IP Toolbench.

#### **Step 1: Parameterize**

There are four pages in the Parameterize - SerialLite MegaCore function wizard available for parameterizing your link. All of the settings for these pages are detailed in Chapter 3, Specifications.

No changes to the default configuration are made in this walkthrough.

You move from page to page either by clicking the tabs at the top of the pages or by navigating using the First, Previous, Next, and Last buttons. The First button takes you to the Basic Configuration page, the Previous button takes you to the page whose tab is to the left of the current page, the Next button takes you to the page whose tab is to the right of the current page, and the Last button takes you to the Advanced Electricals page. You can make changes in any order, but if you move through the pages in the order indicated, no setting changes are required for you to revisit a page you have already completed.

To parameterize your MegaCore function, follow these steps:

1. Click **Step 1: Parameterize** in IP Toolbench (see Figure 2–3).

Figure 2-3. IP Toolbench—Parameterize

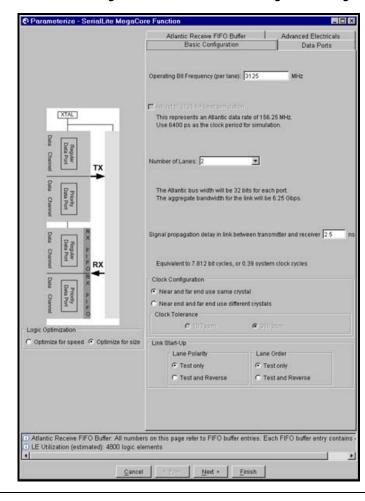

1. This brings up the Basic Configuration page (see Figure 2–4 on page 2–9).

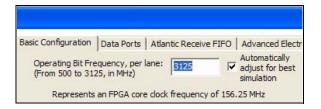

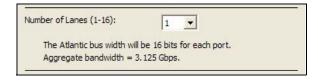

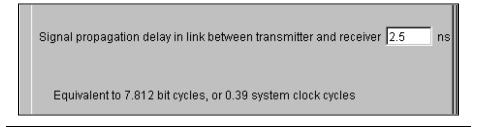

The Basic Configuration page allows you to configure the general characteristics of the link. Included on this page are settings for the following:

- Bit rate

- Lane count

- Signal propagation delay

- Clock configuration

- Lane polarity reversal

- Lane order reversal

Figure 2-4. SerialLite MegaCore Function Basic Configuration Page

2. After you choose your settings on the Basic Configuration page, click **Next** to go to the Data Ports page.

This page allows you to select and configure the data ports, as shown in Figure 2–5 on page 2–10. You can select the regular data port and the priority data port. For the regular data port, you can set the following:

- Data mode (packet or streaming)

- Channel multiplexing options

- Cyclic redundancy code (CRC) options

For the priority port, you can set the following:

- Maximum packet length

- Channel multiplexing options

- CRC options

- Retry-on-error options

Figure 2-5. SerialLite MegaCore Function Data Ports Page

3. After you choose your settings on the Data Ports page, click **Next** to go to the Atlantic Receive FIFO Buffer page.

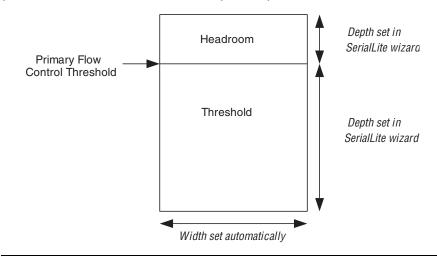

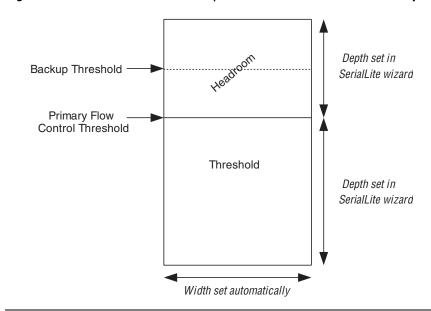

On this page you can configure flow control and the receive FIFO buffer sizes. The options on this page depend heavily on whether or not flow control is enabled. Figure 2–6 on page 2–11 shows the options with flow control disabled. The default configuration, used in this walkthrough, uses no flow control.

Figure 2–6. SerialLite MegaCore Function Atlantic Receive FIFO Buffer Page (Flow Control Disabled)

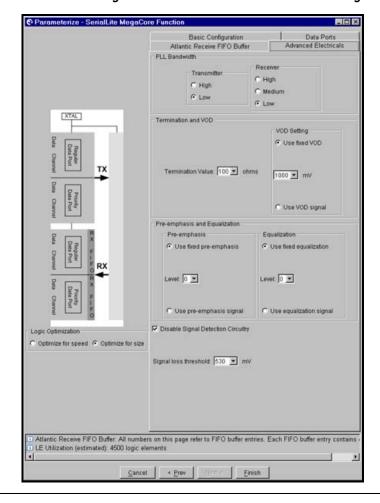

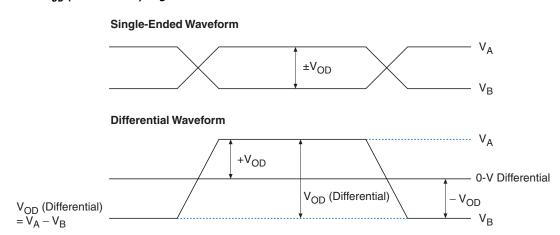

- 4. After you choose your settings on the Atlantic Receive FIFO Buffer page, click **Next** to go to the Advanced Electricals page. This page, shown in Figure 2–7 on page 2–12, allows you to configure electrical settings for the ALTGXB transceivers found in the Stratix GX devices. You can set the following characteristics:

- Transmitter phase-locked loop (PLL) bandwidth

- Receiver PLL bandwidth

- Transmitter termination

- Output differential voltage (V<sub>OD</sub>)

- Pre-emphasis

- Equalization

- Signal loss behavior

Figure 2-7. SerialLite MegaCore Function Advanced Electricals Page

You can also bias the design to optimize for speed or size. This selection is available independently of the four pages.

The wizard gives you an estimate of the logic used. This is only an estimate, and depends on what else is being instantiated in the Stratix GX device. For an accurate count of resources utilized, you must synthesize the design.

5. Continue with the default configuration and click **Finish**.

#### **Step 2: Set Up Simulation**

An IP functional simulation model is a cycle-accurate VHDL or Verilog HDL model file produced by the Quartus II software. It allows for fast functional simulation of IP using industry-standard VHDL and Verilog HDL simulators.

You may only use these simulation model output files for simulation purposes and expressly not for synthesis or any other purposes. Using these models for synthesis creates a non-functional design.

To generate an IP functional simulation model for your MegaCore function, follow these steps:

Click **Step 2: Set Up Simulation** in IP Toolbench (see Figure 2–8).

Figure 2-8. IP Toolbench—Set Up Simulation

Turn on **Generate Simulation Model** (see Figure 2–9 on page 2–14).

2-13

Set Up Simulation - SerialLite MegaCore Function \_ 🗆 × IP Functional Simulation Model ☑ Generate Simulation Model Language • Verilog HDL An IP Functional Simulation Model is a cycle-accurate VHDL or Verilog HDL model produced by the Quartus® II software. These models allow fast functional simulations of IP using industry-standard VHDL and Verilog HDL simulators. You may only use these simulation model output files for simulation purposes and expressly not for synthesis or any other purposes. Using these models for synthesis will create a non-functional design. Cancel OK

Figure 2-9. Generate Simulation Model

- 3. Choose the language in the **Language** list.

- To use the IP Toolbench-generated testbench, choose the same language as you chose for your variation.

- If VHDL is selected, your simulation environment must support mixed-language simulation to use the SerialLite testbench. If it does not, generate a second simulation model using Verilog HDL for use with the SerialLite testbench by repeating step 2.

- 4. Click OK.

#### Step 3: Generate

To generate your MegaCore function variation, follow these steps:

1. Click **Step 3: Generate** in IP Toolbench (see Figure 2–10).

Figure 2–10. IP Toolbench—Generate

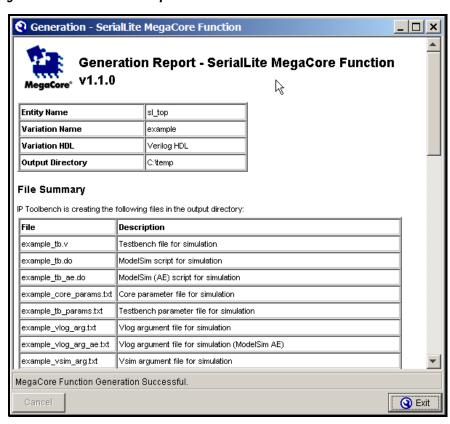

2. The generation report lists the design files that IP Toolbench creates (see Figure 2-11 on page 2-16). Click Exit.

Figure 2-11. Generation Report

Table 2-1 describes IP Toolbench-generated files

For full details, see the generation report or the .html generation report file.

| Table 2–1. IP Toolbench-Generated Files (Part 1 of 2) |                                                                                                                                                                                                                                                                               |  |  |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Extension                                             | Description                                                                                                                                                                                                                                                                   |  |  |  |

| .vhd or .v                                            | A MegaCore function variation file, which defines a VHDL or Verilog HDL top-level description of the MegaCore function variation. Instantiate the entity defined by this file inside of your design. Include this file when compiling your design in the Quartus II software. |  |  |  |

| .cmp                                                  | A VHDL component declaration file for the MegaCore function variation. Add the contents of this file to any VHDL architecture that instantiates the MegaCore function.                                                                                                        |  |  |  |

| _bb.v                                                 | Verilog HDL black-box file for the MegaCore function variation. Use this file when using a third-party EDA tool to synthesize your design.                                                                                                                                    |  |  |  |

| .bsf                                                  | Quartus II symbol file for the MegaCore function variation. You can use this file in the Quartus II block diagram editor.                                                                                                                                                     |  |  |  |

| .html                                                 | MegaCore function report file.                                                                                                                                                                                                                                                |  |  |  |

| Table 2–1. IP Toolbench-Generated Files (Part 2 of 2) |                                                                                                                                                                                               |  |  |  |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Extension                                             | Description                                                                                                                                                                                   |  |  |  |

| _sl_core.vo or<br>_sl_core.vho                        | VHDL or Verilog HDL IP functional simulation model.                                                                                                                                           |  |  |  |

| _inst.vhd or _inst.v                                  | VHDL or Verilog HDL sample instantiation file.                                                                                                                                                |  |  |  |

| _core_params.txt                                      | SerialLite MegaCore function configuration information for use by the testbench.                                                                                                              |  |  |  |

| _constraints.tcl                                      | Tcl script for applying virtual pin constraints when compiling the SerialLite MegaCore function by itself.                                                                                    |  |  |  |

| _tb.do                                                | SerialLite testbench script. Used for simulating a SerialLite MegaCore function variation using the SerialLite testbench in the Model Technology ModelSim (standard edition) simulation tool. |  |  |  |

| _tb_ae.do                                             | SerialLite testbench script. Used for simulating a SerialLite MegaCore function variation using the SerialLite testbench in the Model Technology ModelSim-Altera simulation tool.             |  |  |  |

| _tb.v                                                 | SerialLite testbench top-level file. Used when simulating a SerialLite MegaCore function variation using the SerialLite testbench.                                                            |  |  |  |

| _vsim_arg.txt                                         | ModelSim simulation arguments file. Used when simulating a SerialLite MegaCore function variation using the SerialLite testbench.                                                             |  |  |  |

| _vlog_arg.txt                                         | ModelSim compilation arguments file. Used when simulating a SerialLite MegaCore function variation using the SerialLite testbench.                                                            |  |  |  |

| _tb_params.txt                                        | SerialLite testbench parameter file. You change parameter values in this file to control testbench behavior.                                                                                  |  |  |  |

| .inc                                                  | An AHDL include declaration file for the MegaCore function variation. Include this file with any AHDL architecture that instantiates the MegaCore function.                                   |  |  |  |

You can now integrate your custom megafunction variation into your design and simulate and compile.

# Simulate the Design

You can simulate your design using IP Toolbench-generated VHDL and Verilog HDL IP functional simulation models.

For more information on IP functional simulation models, see the *Simulating Altera in Third-Party Simulation Tools* chapter in Volume 3 of the *Quartus II Handbook*.

Altera also provides a configurable testbench for use in evaluating the SerialLite MegaCore function. The testbench is described in detail in Chapter 4, SerialLite Testbench.

# Compile the Design

You can use the Quartus II software to compile your design. Refer to Quartus II Help for instructions on performing compilation.

#### **Apply Constraints**

If you are compiling the SerialLite MegaCore function variation by itself, the pins must be declared as virtual pins. A Tcl script handles that for you.

- 1. From the Tools menu, select **Tcl Scripts** to bring up the script browser.

- 2. In the project directory, select < design name>\_constraints.tcl.

- Click Run.

The Tcl script also adds several timing constraints and fitter guide settings that typically produce the best  $f_{MAX}$ . Use this script as a guide when setting constraints for the SerialLite MegaCore function variation when implementing an actual design. The timing constraints are currently for the SerialLite MegaCore function variation by itself, and must be updated with hierarchy information in your own design.

The fitter guide settings may cause conflicts with your Quartus II software settings. These following guide settings are used:

- STRATIX OPTIMIZATION TECHNIQUE SPEED

- AUTO PACKED REGISTERS STRATIX OFF

- MUX RESTRUCTURE OFF

- STATE MACHINE PROCESSING AUTO

- FITTER EFFORT "STANDARD FIT"

If, after using the constraints Tcl script and the fitter guide settings, your design still does not meet timing, try using the Quartus II Design Space Explorer optimization utility.

For more information see the *Design Space Explorer* chapter in Volume 2 of the *Quartus II Handbook*.

You can now integrate your MegaCore function variation into your design and simulate and compile.

# Program a Device

After you have compiled your design, program your targeted Altera device and verify your design in hardware.

With Altera's free OpenCore Plus evaluation feature, you can evaluate the SerialLite MegaCore function before you purchase a license. OpenCore Plus evaluation allows you to generate an IP functional simulation model and produce a time-limited programming file.

For more information on IP functional simulation models, see the *Simulating Altera in Third-Party Simulation Tools* chapter in Volume 3 of the *Quartus II Handbook*.

You can simulate the SerialLite MegaCore function in your design, and perform a time-limited evaluation of your design in hardware.

For more information on OpenCore Plus hardware evaluation using the SerialLite MegaCore Function, see "OpenCore Plus Time-Out Behavior" on page 3–1 and *AN 320: OpenCore Plus Evaluation of Megafunctions*.

## **Set Up Licensing**

You need to purchase a license for the MegaCore function only when you are completely satisfied with its functionality and performance, and want to take your design to production.

After you purchase a license for the SerialLite MegaCore function, you can request a license file from the Altera web site at **www.altera.com/licensing** and install it on your computer. When you request a license file, Altera e-mails you a **license.dat** file. If you do not have Internet access, contact your local Altera representative.

To install your license, you can either append the license to your **license.dat** file or you can specify the MegaCore function's **license.dat** file in the Quartus II software.

Before you set up licensing for the SerialLite MegaCore function, you must already have the Quartus II software installed on your computer with licensing set up.

#### Append the License to Your license.dat File

To append the license, follow these steps:

- 1. Close the following software if it is running on your PC:

- Quartus II software

- MAX+PLUS<sup>®</sup> II software

- LeonardoSpectrum<sup>TM</sup> synthesis tool

Altera Corporation August 2005

- Synplify software

- ModelSim simulator

- 2. Open the SerialLite MegaCore function license file in a text editor. The file should contain one FEATURE line, spanning 2 lines.

- 3. Open your Quartus II **license.dat** file in a text editor.

- 4. Copy the FEATURE line from the SerialLite MegaCore function license file and paste it into the Quartus II license file.

- Do not delete any FEATURE lines from the Quartus II license file.

- 5. Save the Quartus II license file.

When using editors such as Microsoft Word or Notepad, ensure that the file does not have extra extensions appended to it after you save (e.g., license.dat.txt or license.dat.doc). Verify the filename in a DOS box or at a command prompt.

#### Specify the License File in the Quartus II Software

To specify the MegaCore function's license file, follow these steps:

Altera recommends that you give the file a unique name, for example, <*MegaCore name*>\_license.dat.

- 1. Run the Quartus II software.

- 2. Choose **License Setup** (Tools menu). The **Options** dialog box opens to the **License Setup** page.

- 3. In the **License file** box, add a semicolon to the end of the existing license path and filename.

- 4. Type the path and filename of the MegaCore function license file after the semicolon.

Do not include any spaces either around the semicolon or in the path/filename.

5. Click **OK** to save your changes.

## 3. Specifications

# Functional Description

The SerialLite MegaCore<sup>®</sup> function consists of parameterized logic and a parameterized testbench. The following sections detail the various possible configurations and things you should consider when deciding how to configure the link.

#### OpenCore Plus Time-Out Behavior

OpenCore<sup>®</sup> Plus hardware evaluation can support the following two modes of operation:

- *Untethered*—the design runs for a limited time

- *Tethered*—requires a connection between your board and the host computer. If tethered mode is supported by all megafunctions in a design, the device can operate for a longer time or indefinitely

All megafunctions in a device time out simultaneously when the most restrictive evaluation time is reached. If there is more than one megafunction in a design, a specific megafunction's time-out behavior may be masked by the time-out behavior of the other megafunctions.

For MegaCore functions, the untethered timeout is 1 hour; the tethered timeout value is indefinite.

Your design stops working after the hardware evaluation time expires. The TENA and THENA signals ignore attempts to write to the SerialLite MegaCore function, and the RENA and RHENA signals ignore attempts to read from the SerialLite MegaCore function.

For more information on OpenCore Plus hardware evaluation, see "OpenCore Plus Evaluation" on page 1–3 and *AN 320: OpenCore Plus Evaluation of Megafunctions* on **www.altera.com**.

# SerialLite Link Configuration

The general decisions you must make for your SerialLite MegaCore function are:

- High-level link configuration

- Bandwidth required

- Which port(s) to use

- Whether to use packet or streaming data

- Whether to multiplex multiple channels

- Whether to use CRC

- Whether to implement the retry-on-error feature

- Whether to implement flow control

- How to size the receive FIFO buffers

- Electrical characteristics of the Stratix<sup>®</sup> GX transceivers

IP Toolbench provides a fully functional default SerialLite MegaCore function variation ready for instantiation. The result is a link with the characteristics shown in Table 3–1. The following sections describe all of these features.

| Table 3–1. Default SerialLite Link            |                                                                     |

|-----------------------------------------------|---------------------------------------------------------------------|

| Feature                                       | Default Configuration                                               |

| Bit rate                                      | 3.125 Gbps                                                          |

| Lane count                                    | 1                                                                   |

| Signal propagation delay                      | 2.5 ns                                                              |

| Clock configuration                           | Both ends of link use the same clock source (no clock compensation) |

| Lane polarity reversal                        | Test only, no reversal                                              |

| Lane order reversal                           | NA (only one lane)                                                  |

| Regular data port                             | Enabled                                                             |

| Data mode                                     | Packet                                                              |

| Channel multiplexing (regular data port)      | Disabled                                                            |

| CRC (regular data port)                       | Disabled                                                            |

| Priority data port                            | Disabled                                                            |

| Retry on error                                | NA (priority data port disabled)                                    |

| Flow control                                  | Disabled                                                            |

| Receive FIFO buffer size (regular data port)  | Minimum (16 entries)                                                |

| Transmitter phase-locked loop (PLL) bandwidth | Low                                                                 |

| Receiver PLL bandwidth                        | Low                                                                 |

| Transmitter termination                       | 100 Ω                                                               |

| V <sub>OD</sub>                               | 1,000 mV                                                            |

| Pre-emphasis                                  | 0                                                                   |

| Equalization                                  | 0                                                                   |

| Signal detection                              | Disabled                                                            |

#### **Link Consistency**

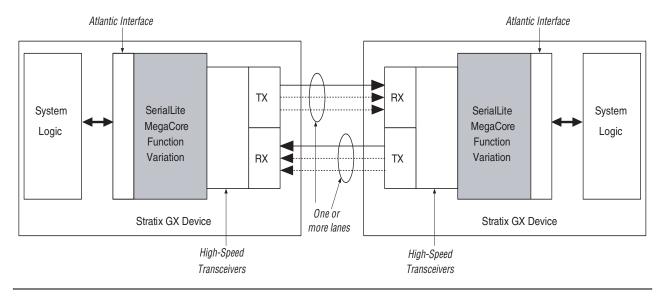

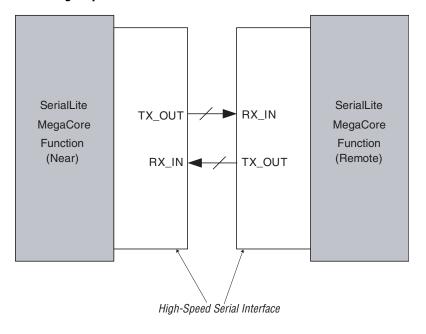

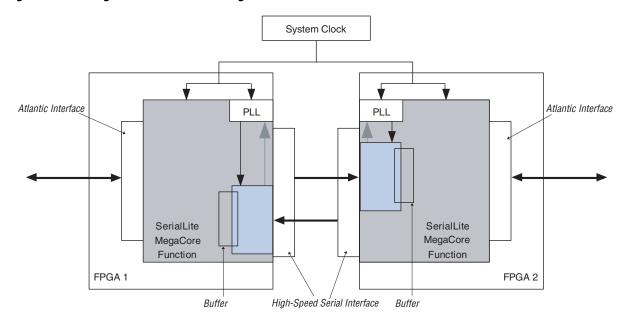

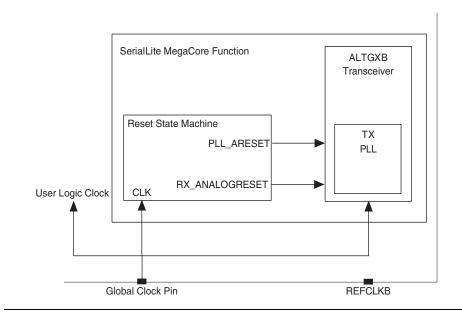

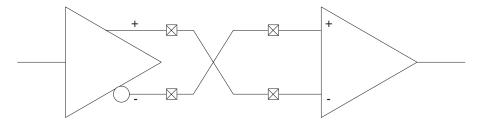

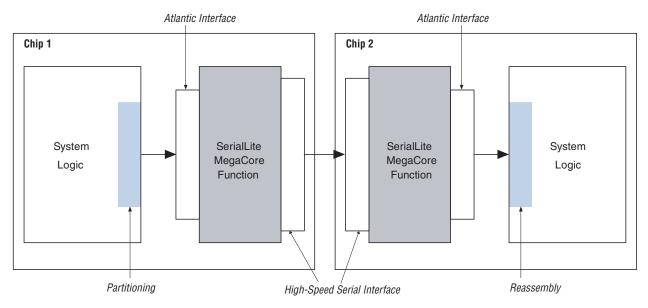

A SerialLite link consists of two instantiations of logic implementing the SerialLite protocol. Each end of the link has a transmitter and a receiver, as shown in Figure 3–1.

Figure 3-1. Complete SerialLite Link

The SerialLite protocol is not a plug-and-play protocol. While there are many configurations to choose from, you must make sure that both ends of your link have the same configuration.

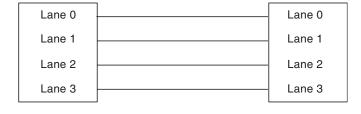

In particular, the SerialLite protocol specifies a symmetric link. The number of lanes in one direction must match the number of lanes in the other direction.

#### **Interface Overview**

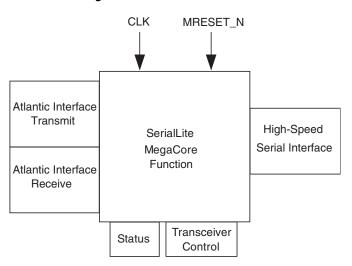

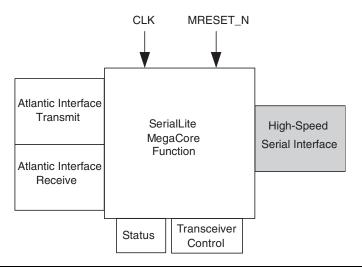

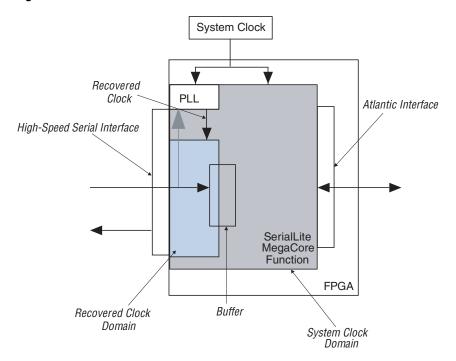

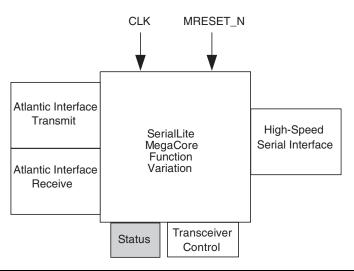

The SerialLite MegaCore function has four interfaces, shown in Figure 3–2:

- The Atlantic<sup>™</sup> interface

- The high-speed serial interface

- The status interface

- The transceiver control interface

3-3

Figure 3-2. SerialLite MegaCore Function Interfaces

For clarity, the word *interface* is used to refer to the four interfaces noted above, and the word *port* is used to refer to the specific data ports on the Atlantic interface that allow for regular or priority data.

The status interface is discussed in "Status Interface" on page 3–56. The transceiver control interface is discussed in "Transceiver Settings" on page 3–58.

### Atlantic Interface

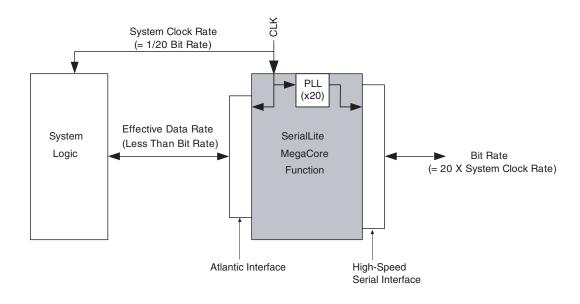

The Atlantic interface (see Figure 3–3) provides a standard mechanism for delivering data to and accepting data from the SerialLite MegaCore function. It is a full-duplex, synchronous point-to-point connection interface that supports a variety of data widths.

For more information on this interface, refer to FS 13: Atlantic Interface, available at www.altera.com.

Figure 3–3. Atlantic Interfaces

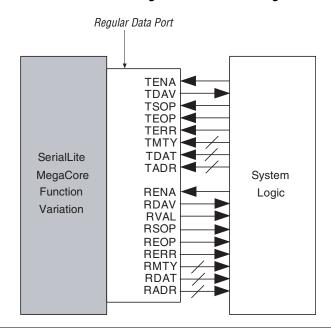

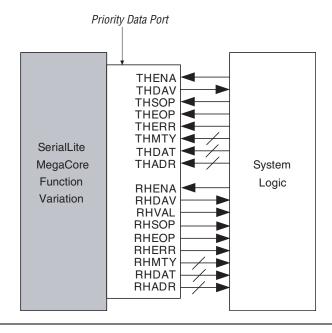

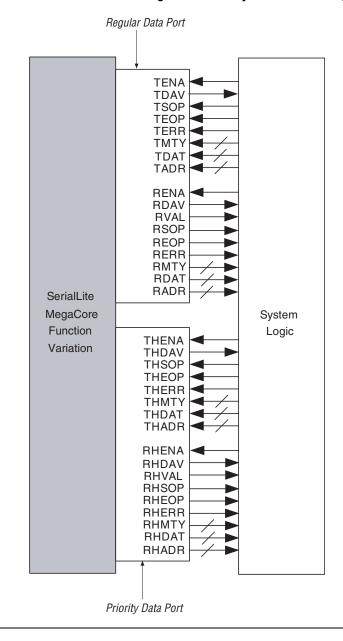

The SerialLite MegaCore function allows you to create one or two data ports: one for regular data and one for priority data. Each of these ports has a full Atlantic interface. Therefore, you may have one of the three configurations shown in Figures 3–4, 3–5, and 3–6. See "Choosing Ports" on page 3–27 for a full description of the behavior of these ports.

Figure 3-4. Atlantic Interface for Regular Data Port Configuration

Figure 3-6. Atlantic Interface for Regular & Priority Data Port Configuration

The SerialLite MegaCore function is always an Atlantic interface slave. The logic on either side of the SerialLite link always acts as a master. This document refers to the logic that drives data into the SerialLite MegaCore function or receives data from the SerialLite MegaCore function as the "system logic."

3-7

The Atlantic interface signals are described in Table 3–2. The signals required for a given configuration, as well as the appropriate bus widths, are created automatically by IP Toolbench based upon the features you select. All Atlantic interface signals operate in the system clock domain.

| Table 3–2. Atlantic Interface Signals (Part 1 of 4) |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-----------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                                                | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| TDAT[] THDAT[]                                      | Input     | Data buses. A data bus carries the main payload data. The width of the bus is determined by the number of lanes in the SerialLite MegaCore function configuration. The width, in bytes, is twice the number of lanes. For example, a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| RDAT[]<br>RHDAT[]                                   | Output    | 1-lane configuration is 2 bytes wide and a 4-lane configuration is 8 bytes wide. The system logic places data on the data bus for transmission, and reads data on the data bus for reception.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                     |           | Data is presented in big-endian order. Valid bytes are aligned with the most significant byte (MSB). For example, in a 2-lane configuration (which has a 4-byte-wide data bus), if only 3 bytes are valid on the final cycle of a packet, the valid data appears on bits [318] of the data bus, and the invalid byte is bits [70] of the data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |