CY7C341

#### **Features**

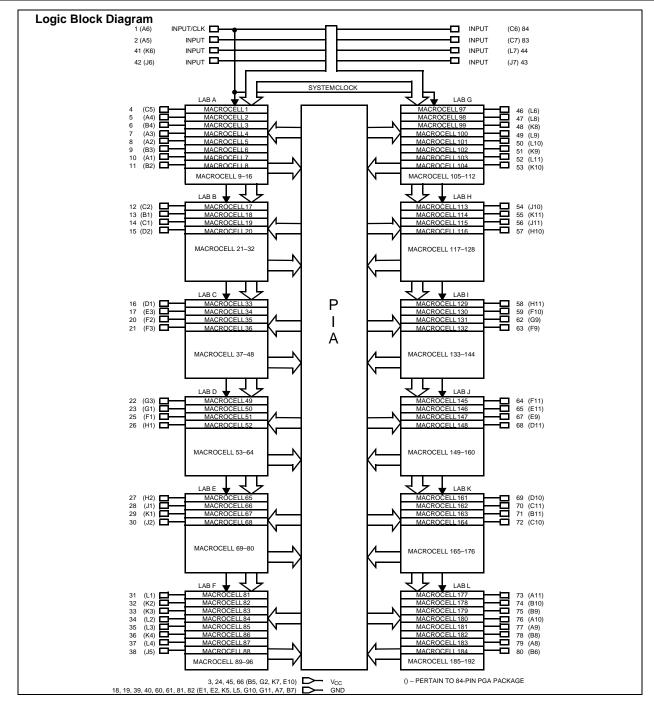

- 192 macrocells in 12 logic array blocks (LABs)

- · Eight dedicated inputs, 64 bidirectional I/O pins

- 0.8-micron double-metal CMOS EPROM technology

- Programmable interconnect array

- 384 expander product terms

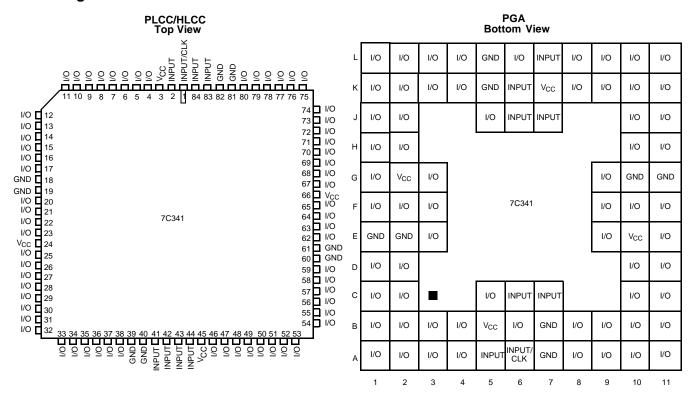

- Available in 84-pin HLCC, PLCC, and PGA packages

### **Functional Description**

The CY7C341 is an Erasable Programmable Logic Device (EPLD) in which CMOS EPROM cells are used to configure logic functions within the device. The MAX® architecture is 100% user-configurable, allowing the devices to accommodate a variety of independent logic functions.

The 192 macrocells in the CY7C341 are divided into 12 LABs. 16 per LAB. There are 384 expander product terms, 32 per LAB, to be used and shared by the macrocells within each LAB. Each LAB is interconnected with a programmable interconnect array, allowing all signals to be routed throughout the

The speed and density of the CY7C341 allows them to be used in a wide range of applications, from replacement of large amounts of 7400-series TTL logic, to complex controllers and multifunction chips. With greater than 37 times the functionality of 20-pin PLDs, the CY7C341 allows the replacement of over 75 TTL devices. By replacing large amounts of logic, the CY7C341 reduces board space and part count, and increases system reliability.

Each LAB contains 16 macrocells. In LABs A, F, G, and L, eight macrocells are connected to I/O pins and eight are buried, while for LABs B, C, D, E, H, I, J, and K, four macrocells are connected to I/O pins and 12 are buried. Moreover, in addition to the I/O and buried macrocells, there are 32 single product term logic expanders in each LAB. Their use greatly enhances the capability of the macrocells without increasing the number of product terms in each macrocell.

# **Logic Array Blocks**

There are 12 logic array blocks in the CY7C341. Each LAB consists of a macrocell array containing 16 macrocells, an expander product term array containing 32 expanders, and an I/O block. The LAB is fed by the programmable interconnect array and the dedicated input bus. All macrocell feedbacks go to the macrocell array, the expander array, and the programmable interconnect array. Expanders feed themselves and the macrocell array. All I/O feedbacks go to the programmable interconnect array so that they may be accessed by macrocells in other LABs as well as the macrocells in the LAB in which they are situated.

Externally, the CY7C341 provides eight dedicated inputs, one of which may be used as a system clock. There are 64 I/O pins

# 192-Macrocell MAX

that may be individually configured for input, output, or bidirectional data flow.

### Programmable Interconnect Array

The Programmable Interconnect Array (PIA) solves interconnect limitations by routing only the signals needed by each logic array block. The inputs to the PIA are the outputs of every macrocell within the device and the I/O pin feedback of every pin on the device.

Unlike masked or programmable gate arrays, which induce variable delay dependent on routing, the PIA has a fixed delay. This eliminates undesired skews among logic signals, which may cause glitches in internal or external logic. The fixed delay, regardless of programmable interconnect array configuration, simplifies design by assuring that internal signal skews or races are avoided. The result is ease of design implementation, often in a single pass, without the multiple internal logic placement and routing iterations required for a programmable gate array to achieve design timing objectives.

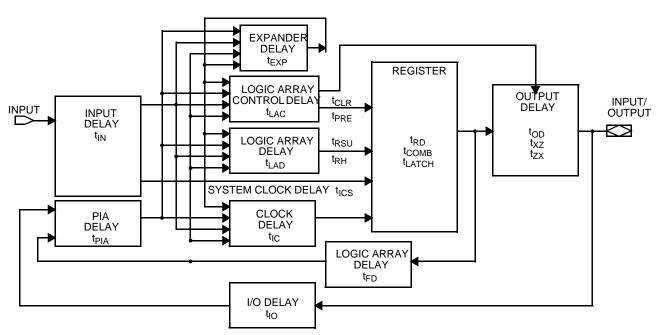

# Timing Delays

Timing delays within the CY7C341 may be easily determined using Warp™, Warp Professional™, or Warp Enterprise™ software. The CY7C341 has fixed internal delays, allowing the user to determine the worst case timing delays for any design.

#### **Design Recommendations**

For proper operation, input and output pins must be constrained to the range GND  $\leq$  (V<sub>IN</sub> or V<sub>OUT</sub>)  $\leq$  V<sub>CC</sub>. Unused inputs must always be tied to an appropriate logic level (either V<sub>CC</sub> or GND). Each set of V<sub>CC</sub> and GND pins must be connected together directly at the device. Power supply decoupling capacitors of at least 0.2 µF must be connected between V<sub>CC</sub> and GND. For the most effective decoupling, each V<sub>CC</sub> pin should be separately decoupled to GND, directly at the device. Decoupling capacitors should have good frequency response, such as monolithic ceramic types.

#### **Design Security**

The CY7C341 contains a programmable design security feature that controls the access to the data programmed into the device. If this programmable feature is used, a proprietary design implemented in the device cannot be copied or retrieved. This enables a high level of design control to be obtained since programmed data within EPROM cells is invisible. The bit that controls this function, along with all other program data, may be reset simply by erasing the device. The CY7C341 is fully functionally tested and guaranteed through complete testing of each programmable EPROM bit and all internal logic elements thus ensuring 100% programming yield.

The erasable nature of these devices allows test programs to be used and erased during early stages of the production flow. The devices also contain on-board logic test circuitry to allow verification of function and AC specification once encapsulated in non-windowed packages.

**Cypress Semiconductor Corporation** Document #: 38-03034 Rev. \*B

3901 North First Street

San Jose, CA 95134

408-943-2600 Revised April 9, 2004

# **Selection Guide**

|                           |            | 7C341-25 | 7C341-30 | 7C341-35 | Unit |

|---------------------------|------------|----------|----------|----------|------|

| Maximum Access Time       |            | 25       | 30       | 35       | ns   |

| Maximum Operating Current | Commercial | 380      | 380      | 380      | mA   |

|                           | Industrial | 480      | 480      | 480      |      |

|                           | Military   | 480      | 480      | 480      |      |

| Maximum Standby Current   | Commercial | 360      | 360      | 360      | mA   |

|                           | Industrial | 435      | 435      | 435      |      |

|                           | Military   | 435      | 435      | 435      |      |

# **Pin Configurations**

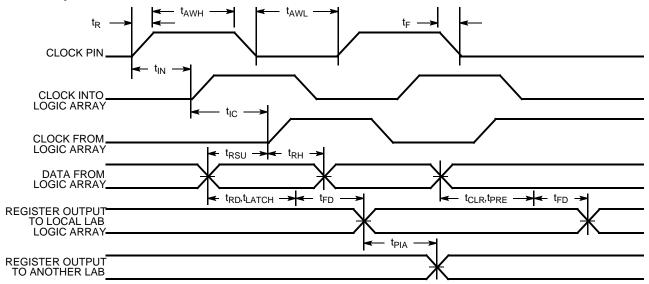

Figure 1. CY7C341 Internal Timing Model

# USE ULTRA37000™ FOR

# **Maximum Ratings**

| (Above which the useful life may be impaired. For user guid lines, not tested.) | le- |

|---------------------------------------------------------------------------------|-----|

| Storage Temperature65°C to +150°                                                | С   |

| Ambient Temperature with Power Applied                                          | С   |

| Maximum Junction Temperature (Under Bias)150°                                   | С   |

| Supply Voltage to Ground Potential2.0V to +7.0                                  | V   |

| Maximum Power Dissipation2500 m\                                                | Ν   |

| DC V <sub>CC</sub> or GND Current500 m                                          | ıΑ  |

| DC Output Current, per Pin                             | 25 mA to +25 mA |

|--------------------------------------------------------|-----------------|

| DC Input Voltage <sup>[1]</sup>                        | 3.0V to +7.0V   |

| DC Program Voltage                                     | 13.0V           |

| Static Discharge Voltage(per MIL-STD-883, method 3015) | >1100V          |

# **Operating Range**

| Range      | Ambient Temperature    | V <sub>CC</sub> |

|------------|------------------------|-----------------|

| Commercial | 0°C to +70°C           | 5V ± 5%         |

| Industrial | –40°C to +85°C         | 5V ± 10%        |

| Military   | –55°C to +125°C (Case) | 5V ± 10%        |

# Electrical Characteristics Over the Operating Range<sup>[2]</sup>

| Parameter                         | Description                         | Test Condition                                                    | ons                 | Min. | Max.                  | Unit |

|-----------------------------------|-------------------------------------|-------------------------------------------------------------------|---------------------|------|-----------------------|------|

| V <sub>OH</sub>                   | Output HIGH Voltage                 | $V_{CC} = Min., I_{OH} = -4.0 \text{ mA}$                         |                     | 2.4  |                       | V    |

| V <sub>OL</sub>                   | Output LOW Voltage                  | $V_{CC} = Min., I_{OL} = 8 \text{ mA}$                            |                     |      | 0.45                  | V    |

| V <sub>IH</sub>                   | Input HIGH Level                    |                                                                   |                     | 2.2  | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub>                   | Input LOW Level                     |                                                                   |                     | -0.3 | 0.8                   | V    |

| I <sub>IX</sub>                   | Input Current                       | $GND \leq V_{IN} \leq V_{CC}$                                     |                     | -10  | +10                   | μА   |

| I <sub>OZ</sub>                   | Output Leakage Current              | $V_O = V_{CC}$ or GND                                             |                     | -40  | +40                   | μΑ   |

| I <sub>OS</sub>                   | Output Short<br>Circuit Current     | $V_{CC} = Max., V_{OUT} = GND^{[3, 4]}$                           |                     | -30  | -90                   | mA   |

| I <sub>CC1</sub>                  | Power Supply Current                | V <sub>I</sub> = V <sub>CC</sub> or GND (No Load)                 | Commercial          | 360  |                       | mA   |

|                                   | (Standby)                           |                                                                   | Military/Industrial |      | 435                   | mA   |

| I <sub>CC2</sub>                  | Power Supply Current <sup>[5]</sup> | $V_1 = V_{CC}$ or GND (No Load)<br>$f = 1.0 \text{ MHz}^{[3, 5]}$ | Commercial          |      | 380                   | mA   |

|                                   |                                     | f = 1.0 MHz <sup>[3, 3]</sup>                                     | Military/Industrial |      | 480                   | mA   |

| t <sub>R</sub> (Recommended)      | Input Rise Time                     |                                                                   |                     |      | 100                   | ns   |

| t <sub>F</sub> (Recom-<br>mended) | Input Fall Time                     |                                                                   |                     |      | 100                   | ns   |

# Capacitance<sup>[6]</sup>

| Parameter        | Description        | Test Conditions                              | Max. | Unit |

|------------------|--------------------|----------------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25$ °C, $f = 1$ MHz, $V_{CC} = 5.0$ V | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance |                                              | 20   | pF   |

#### Notes:

- 1. Minimum DC input is -0.3V. During transitions, the inputs may undershoot to -2.0V for periods less than 20 ns.

- Typical values are for T<sub>A</sub> = 25°C and V<sub>CC</sub> = 5V.

Guaranteed but not 100% tested.

No more than one output should be tested at a time. Duration of the short circuit should not be more than one second. V<sub>OUT</sub> = 0.5V has been chosen to avoid test problems caused by tester ground degradation.

This parameter is measured with device programmed as a 16-bit counter in each LAB and is tested periodically by sampling production material.

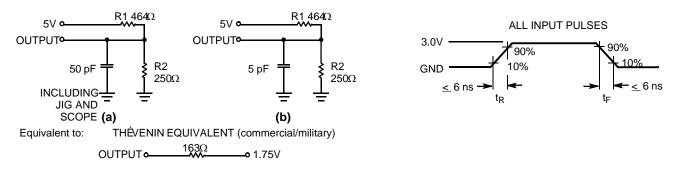

- 6. Part (a) in AC Test Load and Waveforms is used for all parameters except t<sub>ER</sub> and t<sub>XZ</sub>, which is used for part (b) in AC Test Load and Waveforms. All external timing parameters are measured referenced to external pins of the device.

# **AC Test Loads and Waveforms**

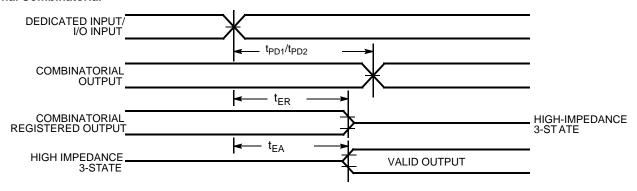

### External Synchronous Switching Characteristics Over the Operating Range<sup>[6]</sup>

|                  |                                                                                   |       | 7C3  | 41-25 | 7C34 | 41-30 | 7C3  | 41-35 |      |  |

|------------------|-----------------------------------------------------------------------------------|-------|------|-------|------|-------|------|-------|------|--|

| Parameter        | Description                                                                       |       | Min. | Max   | Min. | Max   | Min. | Max   | Unit |  |

| t <sub>PD1</sub> | Dedicated Input to Combinatorial                                                  | Com'l |      | 25    |      | 30    |      | 35    | ns   |  |

|                  | Output Delay <sup>[7]</sup>                                                       | Mil   |      | 25    |      | 30    |      | 35    |      |  |

| t <sub>PD2</sub> | I/O Input to Combinatorial                                                        | Com'l |      | 40    |      | 45    |      | 55    | ns   |  |

|                  | Output Delay <sup>[8]</sup>                                                       | Mil   |      | 40    |      | 45    |      | 55    |      |  |

| t <sub>PD3</sub> | Dedicated Input to Combinatorial                                                  | Com'l |      | 37    |      | 44    |      | 55    | ns   |  |

|                  | Output Delay with Expander Delay <sup>[9]</sup>                                   | Mil   |      | 37    |      | 44    |      | 55    |      |  |

| t <sub>PD4</sub> | I/O Input to Combinatorial Output<br>Delay with Expander Delay <sup>[3, 10]</sup> | Com'l |      | 52    |      | 59    |      | 75    | ns   |  |

|                  | Delay with Expander Delay <sup>[3, 10]</sup>                                      | Mil   |      | 52    |      | 59    |      | 75    |      |  |

| t <sub>EA</sub>  | Input to Output Enable Delay[3, 7]                                                | Com'l |      | 25    |      | 30    |      | 35    | ns   |  |

|                  |                                                                                   | Mil   |      | 25    |      | 30    |      | 35    |      |  |

| t <sub>ER</sub>  | Input to Output Disable Delay <sup>[6]</sup>                                      | Com'l |      | 25    |      | 30    |      | 35    | ns   |  |

|                  |                                                                                   | Mil   |      | 25    |      | 30    |      | 35    |      |  |

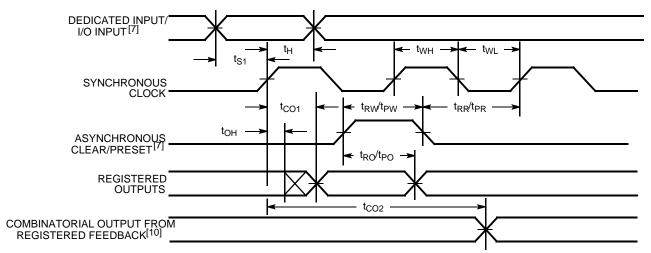

| t <sub>CO1</sub> | Synchronous Clock Input to                                                        | Com'l |      | 14    |      | 16    |      | 20    | ns   |  |

|                  | Output Delay                                                                      | Mil   |      | 14    |      | 16    |      | 20    |      |  |

| t <sub>CO2</sub> | Synchronous Clock to Local                                                        | Com'l |      | 30    |      | 35    |      | 42    | ns   |  |

|                  | Feedback to Combinatorial Output <sup>[3, 11]</sup>                               | Mil   |      | 30    |      | 35    |      | 42    |      |  |

| t <sub>S1</sub>  | Dedicated Input or Feedback Set-up                                                | Com'l | 15   |       | 20   |       | 25   |       | ns   |  |

|                  | Time to Synchronous Clock<br>Output <sup>[6, 12]</sup>                            | Mil   | 15   |       | 20   |       | 25   |       |      |  |

| t <sub>S2</sub>  | I/O Input Set-up Time to                                                          | Com'l | 30   |       | 39   |       | 45   |       | ns   |  |

|                  | Synchronous Clock Input <sup>[8]</sup>                                            | Mil   | 30   |       | 39   |       | 45   |       |      |  |

#### Notes:

<sup>Notes:

7. This specification is a measure of the delay from input signal applied to a dedicated input to combinatorial output on any output pin. This delay assumes that no expander terms are used to form the logic function. When this note is applied to any parameter specification it indicates that the signal (data, asynchronous clock, asynchronous clear, and/or asynchronous preset) is applied to a dedicated input only and no signal path (either clock or data) employs expander logic. If an input signal is applied to an I/O pin an additional delay equal to t<sub>PIA</sub> should be added to the comparable delay for a dedicated input. If expanders are used, add the maximum expander delay t<sub>EXP</sub> to the overall delay for the comparable delay without expanders.

8. This specification is a measure of the delay from input signal applied to an I/O macrocell pin to any output. This delay assumes no expander terms are used to form the logic function.</sup>

<sup>10.</sup> This specification is a measure of the delay from an input signal applied to a dedicated input to combinatorial output on any output pin. This delay assumes expander terms are used to form the logic functions and includes the worst-case expander logic delay for one pass through the expander logic.

10. This specification is a measure of the delay from an input signal applied to an I/O macrocell pin to any output. This delay assumes expander terms are used to form the logic function and includes the worst-case expander logic delay for one pass through the expander logic. This parameter is tested periodically by

<sup>11.</sup> This specification is a measure of the delay from synchronous register clock to internal feedback of the register output signal to the input of the LAB logic array and then to a combinatorial output. This delay assumes no expanders are used, register is synchronously clocked and all feedback is within the same LAB. This parameter is tested periodically by sampling production material.

<sup>12.</sup> If data is applied to an I/O input for capture by a macrocell register, the I/O pin set-up time minimums should be observed. These parameters are ts2 for synchronous operation and t<sub>AS2</sub> for asynchronous operation.

# USE ULTRA37000™ FOR ALL NEW DESIGNS

# External Synchronous Switching Characteristics Over the Operating Range<sup>[6]</sup> (continued)

|                   |                                                                              |       | 7C3  | 41-25 | 7C34 | 41-30 | 7C34 | 41-35 |      |

|-------------------|------------------------------------------------------------------------------|-------|------|-------|------|-------|------|-------|------|

| Parameter         | Description                                                                  |       | Min. | Max   | Min. | Max   | Min. | Max   | Unit |

| t <sub>H</sub>    | Input Hold Time from                                                         | Com'l | 0    |       | 0    |       | 0    |       | ns   |

|                   | Synchronous Clock Input <sup>[6]</sup>                                       | Mil   | 0    |       | 0    |       | 0    |       |      |

| t <sub>WH</sub>   | Synchronous Clock Input                                                      | Com'l | 8    |       | 10   |       | 12.5 |       | ns   |

|                   | High Time                                                                    | Mil   | 8    |       | 10   |       | 12.5 |       |      |

| t <sub>WL</sub>   | Synchronous Clock Input                                                      | Com'l | 8    |       | 10   |       | 12.5 |       | ns   |

|                   | Low Time                                                                     | Mil   | 8    |       | 10   |       | 12.5 |       |      |

| t <sub>RW</sub>   | Asynchronous Clear Width <sup>[3, 6]</sup>                                   | Com'l | 25   |       | 30   |       | 35   |       | ns   |

|                   |                                                                              | Mil   | 25   |       | 30   |       | 35   |       |      |

| t <sub>RO</sub>   | Asynchronous Clear to                                                        | Com'l |      | 25    |      | 30    |      | 35    | ns   |

|                   | Registered Output Delay <sup>[5]</sup>                                       | Mil   |      | 25    |      | 30    |      | 35    |      |

| t <sub>RR</sub>   | Asynchronous Clear Recovery[3, 7]                                            | Com'l | 25   |       | 30   |       | 35   |       | ns   |

|                   |                                                                              | Mil   | 25   |       | 30   |       | 35   |       |      |

| t <sub>PW</sub>   | Asynchronous Preset Width <sup>[3, 6]</sup>                                  | Com'l | 25   |       | 30   |       | 35   |       | ns   |

|                   |                                                                              | Mil   | 25   |       | 30   |       | 35   |       |      |

| t <sub>PR</sub>   | Asynchronous Preset Recovery                                                 | Com'l | 25   |       | 30   |       | 35   |       | ns   |

|                   | Time <sup>[3, 6]</sup>                                                       | Mil   | 25   |       | 30   |       | 35   |       |      |

| t <sub>PO</sub>   | Asynchronous Preset to                                                       | Com'l |      | 25    |      | 30    |      | 35    | ns   |

|                   | Registered Output Delay <sup>[6]</sup>                                       | Mil   |      | 25    |      | 30    |      | 35    |      |

| t <sub>CF</sub>   | Synchronous Clock to Local                                                   | Com'l |      | 3     |      | 3     |      | 5     | ns   |

|                   | Feedback Input <sup>[3, 13]</sup>                                            | Mil   |      | 3     |      | 3     |      | 5     |      |

| t <sub>P</sub>    | External Synchronous Clock Period                                            | Com'l | 16   |       | 20   |       | 25   |       | ns   |

|                   | (1/f <sub>MAX3</sub> ) <sup>[3]</sup>                                        | Mil   | 16   |       | 20   |       | 25   |       |      |

| f <sub>MAX1</sub> | External Feedback Maximum                                                    | Com'l | 34.5 |       | 27.7 |       | 22.2 |       | MHz  |

|                   | Frequency (1/(t <sub>CO1</sub> + t <sub>S1</sub> )) <sup>[3, 14]</sup>       | Mil   | 34.5 |       | 27.7 |       | 22.2 |       |      |

| f <sub>MAX2</sub> | Internal Local Feedback Maximum                                              | Com'l | 55.5 |       | 43   |       | 33   |       | MHz  |

|                   | Frequency, lesser of $(1/(t_{S1} + t_{CF}))$ or $(1/t_{CO1})^{[3, 15]}$      | Mil   | 55.5 |       | 43   |       | 33   |       |      |

| f <sub>MAX3</sub> | Data Path Maximum Frequency, least                                           | Com'l | 62.5 |       | 50   |       | 40.0 |       | MHz  |

|                   | of $1/(t_{WL} + t_{WH})$ , $1/(t_{S1} + t_{H})$ , or $(1/t_{CO1})^{[3, 16]}$ | Mil   | 62.5 |       | 50   |       | 40.0 |       |      |

| f <sub>MAX4</sub> | Maximum Register Toggle                                                      | Com'l | 62.5 |       | 50   |       | 40.0 |       | MHz  |

|                   | Frequency $(1/(t_{WL} + t_{WH}))^{[3, 17]}$                                  | Mil   | 62.5 |       | 50   |       | 40.0 |       |      |

| t <sub>OH</sub>   | Output Data Stable Time from                                                 | Com'l | 3    |       | 3    |       | 3    |       | ns   |

|                   | Synchronous Clock Input <sup>[3, 18]</sup>                                   | Mil   | 3    |       | 3    |       | 3    |       |      |

#### Notes:

<sup>13.</sup> This specification is a measure of the delay associated with the internal register feedback path. This is the delay from synchronous clock to LAB logic array input. This delay plus the register set-up time, t<sub>S1</sub>, is the minimum internal period for an internal synchronous state machine configuration. This delay is for feedback within the same LAB. This parameter is tested periodically by sampling production material.

<sup>14.</sup> This specification indicates the guaranteed maximum frequency, in synchronous mode, at which a state machine configuration with external feedback can operate. It is assumed that all data inputs and feedback signals are applied to dedicated inputs. All feedback is assumed to be local originating within the same LAB.

<sup>15.</sup> This specification indicates the guaranteed maximum frequency at which a state machine, with internal-only feedback, can operate. If register output states must also control external points, this frequency can still be observed as long as this frequency is less than 1/l<sub>CO1</sub>.

16. This frequency indicates the maximum frequency at which the device may operate in data path mode (dedicated input pin to output pin). This assumes data input signals are applied to dedicated input pins and no expander logic is used. If any of the data inputs are I/O pins, t<sub>S2</sub> is the appropriate t<sub>S</sub> for calculation.

<sup>17.</sup> This specification indicates the guaranteed maximum frequency, in synchronous mode, at which an individual output or buried register can be cycle by a clock signal applied to the dedicated clock input pin.

<sup>18.</sup> This parameter indicates the minimum time after a synchronous register clock input that the previous register output data is maintained on the output pin.

# External Synchronous Switching Characteristics Over the Operating Range<sup>[6]</sup> (continued)

|                     |                                                                                          |       | 7C34 | 41-25 | 7C34 | 41-30 | 7C3  | 7C341-35 |      |

|---------------------|------------------------------------------------------------------------------------------|-------|------|-------|------|-------|------|----------|------|

| Parameter           | Description                                                                              |       | Min. | Max   | Min. | Max   | Min. | Max      | Unit |

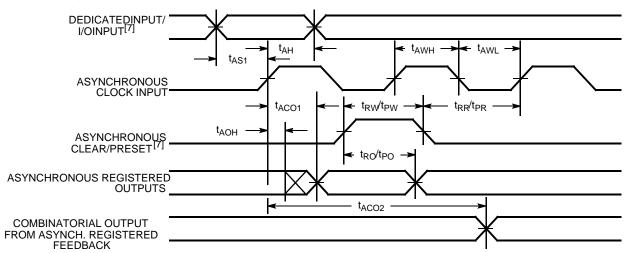

| t <sub>ACO1</sub>   | Dedicated Asynchronous Clock Input                                                       | Com'l |      | 25    |      | 30    |      | 35       | ns   |

|                     | to Output Delay <sup>[6]</sup>                                                           | Mil   |      | 25    |      | 30    |      | 35       |      |

| t <sub>ACO2</sub>   | Asynchronous Clock Input to Local                                                        | Com'l |      | 40    |      | 46    |      | 55       | ns   |

|                     | Feedback to Combinatorial Output <sup>[19]</sup>                                         | Mil   |      | 40    |      | 46    |      | 55       |      |

| t <sub>AS1</sub>    | Dedicated Input or Feedback Set-up                                                       | Com'l | 5    |       | 6    |       | 8    |          | ns   |

|                     | Time to Asynchronous Clock Input <sup>[6]</sup>                                          | Mil   | 5    |       | 6    |       | 8    |          |      |

| t <sub>AS2</sub>    | I/O Input Set-Up Time to                                                                 | Com'l | 20   |       | 27   |       | 30   |          | ns   |

|                     | Asynchronous Clock Input <sup>[6]</sup>                                                  | Mil   | 20   |       | 27   |       | 30   |          |      |

| t <sub>AH</sub>     | Input Hold Time from                                                                     | Com'l | 6    |       | 8    |       | 10   |          | ns   |

|                     | Asynchronous Clock Input <sup>[6]</sup>                                                  | Mil   | 6    |       | 8    |       | 10   |          |      |

| t <sub>AWH</sub> As | Asynchronous Clock Input                                                                 | Com'l | 11   |       | 14   |       | 16   | ns       | ns   |

|                     | HIĞH Time <sup>[6]</sup>                                                                 | Mil   | 11   |       | 14   |       | 16   |          |      |

| t <sub>AWL</sub>    | Asynchronous Clock Input                                                                 | Com'l | 9    |       | 11   |       | 14   |          | ns   |

|                     | LOW Time <sup>[6, 20]</sup>                                                              | Mil   | 9    |       | 11   |       | 14   |          |      |

| t <sub>ACF</sub>    | Asynchronous Clock to                                                                    | Com'l |      | 15    |      | 18    |      | 22       | ns   |

|                     | Local Feedback Input <sup>[21]</sup>                                                     | Mil   |      | 15    |      | 18    |      | 22       |      |

| t <sub>AP</sub>     | External Asynchronous                                                                    | Com'l | 20   |       | 25   |       | 30   |          | ns   |

|                     | Clock Period (1/f <sub>MAX4</sub> )                                                      | Mil   | 20   |       | 25   |       | 30   |          |      |

| f <sub>MAXA1</sub>  | External Feedback Maximum                                                                | Com'l | 33.3 |       | 27   |       | 23   |          | MHz  |

|                     | Frequency in Asynchronous Mode 1/(t <sub>ACO1</sub> + t <sub>AS1</sub> ) <sup>[22]</sup> | Mil   | 33.3 |       | 27   |       | 23   |          |      |

| f <sub>MAXA2</sub>  | Maximum Internal                                                                         | Com'l | 50   |       | 40   |       | 33.3 |          | MHz  |

|                     | Asynchronous Frequency <sup>[23]</sup>                                                   | Mil   | 50   |       | 40   |       | 33.3 |          |      |

| f <sub>MAXA3</sub>  | Data Path Maximum Frequency in                                                           | Com'l | 40   |       | 33.3 |       | 28.5 |          | MHz  |

|                     | Asynchronous Mode <sup>[24]</sup>                                                        | Mil   | 40   |       | 33.3 |       | 28.5 |          |      |

| f <sub>MAXA4</sub>  | Maximum Asynchronous Register                                                            | Com'l | 50   |       | 40   |       | 33.3 |          | MHz  |

|                     | Toggle Frequency 1/(t <sub>AWH</sub> + t <sub>AWL</sub> ) <sup>[25]</sup>                | Mil   | 50   |       | 40   |       | 33.3 |          |      |

| t <sub>AOH</sub>    | Output Data Stable Time from                                                             | Com'l | 15   |       | 15   |       | 15   |          | ns   |

|                     | Asynchronous Clock Input <sup>[26]</sup>                                                 | Mil   | 15   |       | 15   |       | 15   |          |      |

- 19. This specification is a measure of the delay from an asynchronous register clock input to internal feedback of the register output signal to the input of the LAB logic array and then to a combinatorial output. This delay assumes no expanders are used in the logic of combinatorial output or the asynchronous clock input. The clock signal is applied to the dedicated clock input pin and all feedback is within a single LAB. This parameter is tested periodically by sampling production

- This parameter is measured with a positive-edge-triggered clock at the register. For negative-edge triggering, the t<sub>AWH</sub> and t<sub>AWL</sub> parameters must be swapped. If a given input is used to clock multiple registers with both positive and negative polarity, t<sub>AWH</sub> should be used for both t<sub>AWH</sub> and t<sub>AWL</sub>.

This specification is a measure of the delay associated with the internal register feedback path for an asynchronous clock to LAB logic array input. This delay plus the asynchronous register set-up time, t<sub>AS1</sub>, is the minimum internal period for an internal asynchronously clocked state machine configuration. This delay is for feedback within the same LAB, and assumes there is no expander logic in the clock path and the clock input signal is applied to a dedicated input pin. This parameter is tested periodically by sampling production material.

- 22. This specification indicates the guaranteed maximum frequency at which an asynchronously clocked state machine configuration with external feedback can operate. It is assumed that all data inputs, clock inputs, and feedback signals are applied to dedicated inputs, and that no expander logic is employed in the clock signal path or data path.

- 23. This specification indicates the guaranteed maximum frequency at which an asynchronously clocked state machine with internal-only feedback can operate. This parameter is determined by the lesser of (1/t<sub>ACF</sub>+t<sub>AS1</sub>)) or (1/(t<sub>AWH</sub>+t<sub>AWL</sub>)). If register output states must also control external points, this frequency can still be observed. as long as this frequency is less than 1/t<sub>ACO1</sub>.

- 24. This frequency is the maximum frequency at which the device may operate in the asynchronously clocked data path mode. This specification is determined by the least of 1/(t<sub>AWH</sub> + t<sub>AW</sub>), 1/(t<sub>AS1</sub> + t<sub>AH</sub>) or 1/t<sub>ACO1</sub>. It assumes data and clock input signals are applied to dedicated input pins and no expander logic is used.

25. This specification indicates the guaranteed maximum frequency at which an individual output or buried register can be cycled in asynchronously clocked mode by a clock signal applied to an external dedicated input pin.

- 26. This parameter indicates the minimum time that the previous register output data is maintained on the output after an asynchronous register clock input applied to an external dedicated input pin.

# Internal Switching Characteristics Over the Operating $\mathsf{Range}^{[2]}$

|                    |                                            |       | 7C3  | 41-25 | 7C3  | 41-30 | 7C3  | 41-35 |      |

|--------------------|--------------------------------------------|-------|------|-------|------|-------|------|-------|------|

| Parameter          | Description                                |       | Min. | Max   | Min. | Max   | Min. | Max   | Unit |

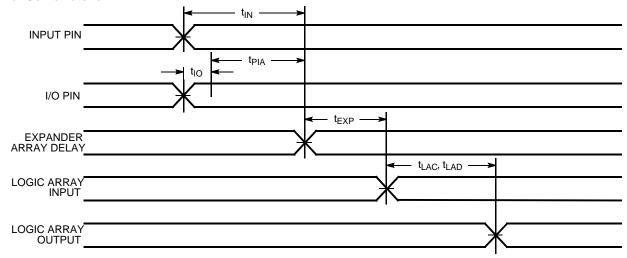

| t <sub>IN</sub>    | Dedicated Input Pad and                    | Com'l |      | 5     |      | 7     |      | 9     | ns   |

|                    | Buffer Delay                               | Mil   |      | 5     |      | 7     |      | 9     |      |

| t <sub>IO</sub>    | I/O Input Pad and Buffer Delay             | Com'l |      | 6     |      | 6     |      | 9     | ns   |

|                    |                                            | Mil   |      | 6     |      | 6     |      | 9     |      |

| t <sub>EXP</sub>   | Expander Array Delay                       |       |      | 12    |      | 14    |      | 20    | ns   |

|                    |                                            | Mil   |      | 12    |      | 14    |      | 20    |      |

| t <sub>LAD</sub>   | Logic Array Data Delay                     | Com'l |      | 12    |      | 14    |      | 16    | ns   |

|                    |                                            | Mil   |      | 12    |      | 14    |      | 16    |      |

| t <sub>LAC</sub>   | Logic Array Control Delay                  | Com'l |      | 10    |      | 12    |      | 13    | ns   |

|                    |                                            | Mil   |      | 10    |      | 12    |      | 13    |      |

| t <sub>OD</sub>    | Output Buffer and Pad Delay                | Com'l |      | 5     |      | 5     |      | 6     | ns   |

|                    |                                            | Mil   |      | 5     |      | 5     |      | 6     |      |

| t <sub>ZX</sub>    | Output Buffer Enable Delay <sup>[27]</sup> | Com'l |      | 10    |      | 11    |      | 13    | ns   |

|                    |                                            | Mil   |      | 10    |      | 11    |      | 13    |      |

| t <sub>XZ</sub>    | Output Buffer Disable Delay                | Com'l |      | 10    |      | 11    |      | 13    | ns   |

|                    |                                            | Mil   |      | 10    |      | 11    |      | 13    |      |

| t <sub>RSU</sub>   | Register Set-Up Time Relative to           | Com'l | 6    |       | 8    |       | 10   |       | ns   |

|                    | Clock Signal at Register                   |       | 6    |       | 8    |       | 10   |       |      |

| t <sub>RH</sub>    | Register Hold Time Relative to             | Com'l | 6    |       | 8    |       | 10   |       | ns   |

|                    | Clock Signal at Register                   | Mil   | 6    |       | 8    |       | 10   |       |      |

| t <sub>LATCH</sub> | Flow-Through Latch Delay                   | Com'l |      | 3     |      | 4     |      | 4     | ns   |

|                    |                                            | Mil   |      | 3     |      | 4     |      | 4     |      |

| t <sub>RD</sub>    | Register Delay                             | Com'l |      | 1     |      | 2     |      | 2     | ns   |

|                    |                                            | Mil   |      | 1     |      | 2     |      | 2     |      |

| t <sub>COMB</sub>  | Transparent Mode Delay <sup>[28]</sup>     | Com'l |      | 3     |      | 4     |      | 4     | ns   |

|                    |                                            | Mil   |      | 3     |      | 4     |      | 4     |      |

| t <sub>CH</sub>    | Clock High Time                            | Com'l | 8    |       | 10   |       | 12.5 |       | ns   |

|                    |                                            | Mil   | 8    |       | 10   |       | 12.5 |       |      |

| t <sub>CL</sub>    | Clock Low Time                             | Com'l | 8    |       | 10   |       | 12.5 |       | ns   |

|                    |                                            | Mil   | 8    |       | 10   |       | 12.5 |       |      |

| t <sub>IC</sub>    | Asynchronous Clock Logic Delay             | Com'l |      | 14    |      | 16    |      | 18    | ns   |

|                    |                                            | Mil   |      | 14    |      | 16    |      | 18    |      |

| t <sub>ICS</sub>   | Synchronous Clock Delay                    | Com'l |      | 2     |      | 2     |      | 3     | ns   |

|                    |                                            | Mil   |      | 2     |      | 2     |      | 3     |      |

| t <sub>FD</sub>    | Feedback Delay                             | Com'l |      | 1     |      | 1     |      | 2     | ns   |

|                    |                                            | Mil   |      | 1     |      | 1     |      | 2     |      |

| t <sub>PRE</sub>   | Asynchronous Register Preset               | Com'l |      | 5     |      | 6     |      | 7     | ns   |

|                    | Time                                       | Mil   |      | 5     |      | 6     |      | 7     |      |

| t <sub>CLR</sub>   | Asynchronous Register Clear                | Com'l |      | 5     |      | 6     |      | 7     | ns   |

|                    | Time                                       | Mil   |      | 5     |      | 6     |      | 7     | 1    |

# Internal Switching Characteristics Over the Operating Range<sup>[2]</sup> (continued)

|                  |                               |       | 7C341-25 |     | 7C34 | 41-30 7C3 |      | 41-35 |      |

|------------------|-------------------------------|-------|----------|-----|------|-----------|------|-------|------|

| Parameter        | Description                   |       | Min.     | Max | Min. | Max       | Min. | Max   | Unit |

| t <sub>PCW</sub> | Asynchronous Preset and Clear | Com'l | 5        |     | 6    |           | 7    |       | ns   |

|                  | Pulse Width                   | Mil   | 5        |     | 6    |           | 7    |       |      |

| t <sub>PCR</sub> | Asynchronous Preset and Clear |       | 5        |     | 6    |           | 7    |       | ns   |

|                  | Recovery Time                 | Mil   | 5        |     | 6    |           | 7    |       |      |

| t <sub>PIA</sub> |                               |       |          | 14  |      | 16        |      | 20    | ns   |

|                  | Array Delay                   | Mil   |          |     |      | 16        |      | 20    |      |

#### Notes:

- 27. Sample tested only for an output change of 500 mV.

- 28. This specification guarantees the maximum combinatorial delay associated with the macrocell register bypass when the macrocell is configured for combinatorial operation.

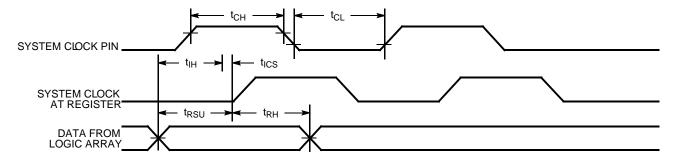

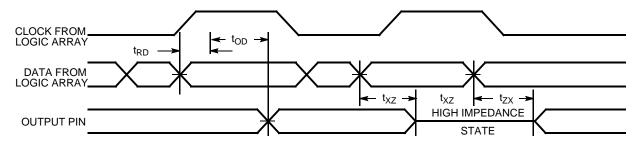

# **Switching Waveforms**

#### **External Combinatorial**

### **External Synchronous**

# Switching Waveforms (continued)

#### **External Asynchronous**

### **Internal Combinatorial**

# Switching Waveforms (continued)

#### **Internal Asynchronous**

#### **Internal Synchronous**

### **Internal Synchronous**

# **Ordering Information**

| Speed<br>(ns) | Ordering Code   | Package<br>Name | Package Type                         | Operating<br>Range    |

|---------------|-----------------|-----------------|--------------------------------------|-----------------------|

| 25            | CY7C341-25HC/HI | H84             | 84-Lead Windowed Leaded Chip Carrier | Commercial/Industrial |

|               | CY7C341-25JC/JI | J83             | 84-Lead Plastic Leaded Chip Carrier  |                       |

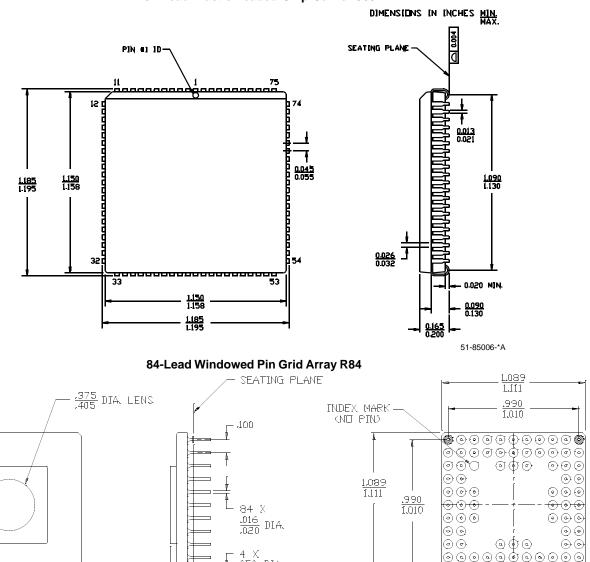

|               | CY7C341-25RC/RI | R84             | 84-Lead Windowed Pin Grid Array      |                       |

| 30            | CY7C341-30HC/HI | H84             | 84-Lead Windowed Leaded Chip Carrier | Commercial/Industrial |

|               | CY7C341-30JC/JI | J83             | 84-Lead Plastic Leaded Chip Carrier  |                       |

|               | CY7C341-30RC/RI | R84             | 84-Lead Windowed Pin Grid Array      |                       |

|               | CY7C341-30HMB   | H84             | 84-Lead Windowed Leaded Chip Carrier | Military              |

|               | CY7C341-30RMB   | R84             | 84-Lead Windowed Pin Grid Array      |                       |

| 35            | CY7C341-35HC/HI | H84             | 84-Lead Windowed Leaded Chip Carrier | Commercial/Industrial |

|               | CY7C341-35JC/JI | J83             | 84-Lead Plastic Leaded Chip Carrier  |                       |

|               | CY7C341-35RC/RI | R84             | 84-Lead Windowed Pin Grid Array      |                       |

|               | CY7C341-35HMB   | H84             | 84-Lead Windowed Leaded Chip Carrier | Military              |

|               | CY7C341-35RMB   | R84             | 84-Lead Windowed Pin Grid Array      |                       |

# MILITARY SPECIFICATIONS Group A Subgroup Testing

#### **DC Characteristics**

| Parameter        | Subgroups |

|------------------|-----------|

| V <sub>OH</sub>  | 1, 2, 3   |

| V <sub>OL</sub>  | 1, 2, 3   |

| V <sub>IH</sub>  | 1, 2, 3   |

| V <sub>IL</sub>  | 1, 2, 3   |

| I <sub>IX</sub>  | 1, 2, 3   |

| I <sub>OZ</sub>  | 1, 2, 3   |

| I <sub>CC1</sub> | 1, 2, 3   |

# **Switching Characteristics**

| Parameter         | Subgroups       |

|-------------------|-----------------|

| t <sub>PD1</sub>  | 7, 8, 9, 10, 11 |

| t <sub>PD2</sub>  | 7, 8, 9, 10, 11 |

| t <sub>PD3</sub>  | 7, 8, 9, 10, 11 |

| t <sub>CO1</sub>  | 7, 8, 9, 10, 11 |

| t <sub>S1</sub>   | 7, 8, 9, 10, 11 |

| t <sub>H</sub>    | 7, 8, 9, 10, 11 |

| t <sub>ACO1</sub> | 7, 8, 9, 10, 11 |

| t <sub>ACO2</sub> | 7, 8, 9, 10, 11 |

| t <sub>AS1</sub>  | 7, 8, 9, 10, 11 |

| t <sub>AH</sub>   | 7, 8, 9, 10, 11 |

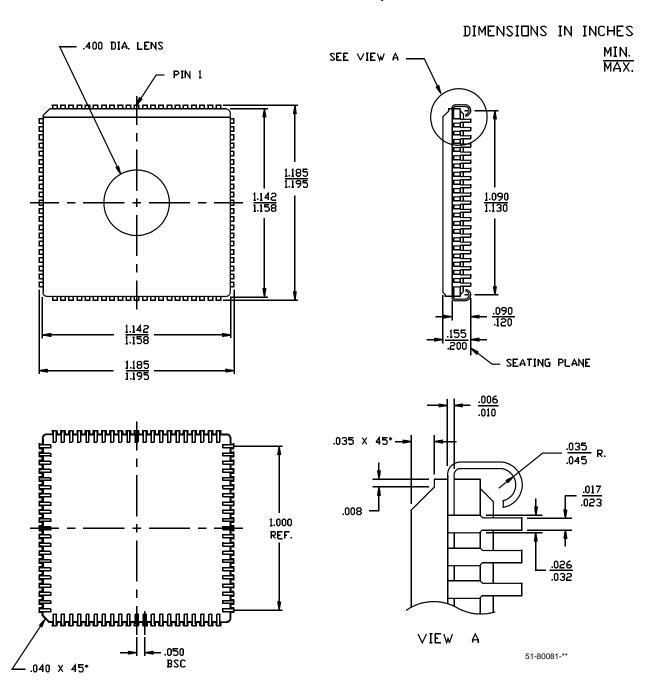

# **Package Diagrams**

# 84-Leaded Windowed Leaded Chip Carrier H84

# Package Diagrams (continued)

#### 84-Lead Plastic Leaded Chip Carrier J83

MAX and *Warp* are registered trademarks and Ultra37000, *Warp* Professional, and *Warp* Enterprise are trademarks of Cypress Semiconductor Corporation. All products and company names mentioned in this document are the trademarks of their respective holders.

<u>.040</u> .060

TOP VIEW

BUTTOM VIEW

51-80026-\*B

84 X ,080 DIA, MAX.

# USE ULTRA37000™ FOR ALL NEW DESIGNS

CY7C341

# **Document History Page**

| Document Title: CY7C341 192-Macrocell MAX® EPLD Document Number: 38-03034 |         |            |                 |                                                                |

|---------------------------------------------------------------------------|---------|------------|-----------------|----------------------------------------------------------------|

| REV.                                                                      | ECN NO. | Issue Date | Orig. of Change | Description of Change                                          |

| **                                                                        | 106379  | 06/18/01   | SZV             | Change from Spec#: 38-00499 to 38-03034                        |

| *A                                                                        | 111355  | 12/17/01   | MYN             | PGA package diagram dimensions were updated                    |

| *B                                                                        | 213375  | See ECN    | FSG             | Added note to title page: "Use Ultra37000 For All New Designs" |

Document #: 38-03034 Rev. \*B Page 15 of 15