### Intel<sup>®</sup> 80314 I/O Processor Companion Chip

**Specification Update**

July 2005

**Notice:** The Intel<sup>®</sup> 80314 I/O Processor Companion Chip may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in this specification update.

Order Number: 273759-010US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantlP, Intel, Intel Centrino, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel Xeon, Pertium, IIX Keon, Performance at Your Command, RemoteExpress, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, Intel on June Subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2005, Intel Corporation

# int<sub>e</sub>l<sub>®</sub> Contents

| Revision History             | 5  |

|------------------------------|----|

| Preface                      | 7  |

| Summary Table of Changes     | 8  |

| Identification Information   | 14 |

| Errata                       | 16 |

| Specification Changes        | 28 |

| Specification Clarifications | 32 |

| Documentation Changes        | 37 |

### THIS PAGE INTENTIONALLY LEFT BLANK

# **Revision History**

L

| Date        | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| July 2005   | 010     | Added Documentation Changes 21 and 22.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| April 2005  | 009     | <ul> <li>Corrected Port_Arb settings in Erratum 34 and 40 and updated them to include a setting of 11b as fixed in the B1 stepping.</li> <li>Corrected Errata 43 to read "PCI Class Override Register".</li> <li>Edited Specification Clarification 17, adding "PORT_ARB=11 is not effected" to the description.</li> <li>Added Documentation Change 20.</li> </ul>                                                                                                                                                                                                                                       |  |  |  |

| March 2005  | 008     | <ul><li>Added Specification Change 13.</li><li>Added Documentation Change 19.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| August 2004 | 007     | Added erratum 46 ("Possible lost interrupt due to read/write of aliased IACKx registers" on page 27).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| July 2004   | 006     | <ul> <li>Post-silicon B1 update:</li> <li>Added erratum 45 ("External PCI/X DMA to SRAM sync packet" on page 27).</li> <li>Added specification change 12 ("Removal of shadow registers" on page 31).</li> <li>Added specification clarification 17 ("Driver consideration for shared memory structures under PORT_ARB = 01" on page 35).</li> <li>Added specification clarification 18 ("PCI Target Abort when Start Address + Cache Line exceeds physical memory" on page 36).</li> <li>Added documentation change 18 ("GPIO attribute reversal" on page 42).</li> <li>Minor edits throughout</li> </ul> |  |  |  |

| May 2004    | 005     | <ul> <li>Added information for B1 identification.</li> <li>Updated Errata 42 (External PCI/X DMA to SDRAM Sync Packet).</li> <li>Added Errata 44 (GPIO[7:0] pins are driven on reset).</li> <li>Changed power sequencing requirement in Specification Change 7.</li> <li>Added Specification Changes 9, 10, and 11.</li> </ul>                                                                                                                                                                                                                                                                            |  |  |  |

| April 2004  | 004     | <ul> <li>Added information for B0 stepping</li> <li>Changed status of several errata to "Fixed" (for B0 stepping).</li> <li>Text corrected in Errata 37 from "low" to "high".</li> <li>Added Errata 38–43.</li> <li>Added Specification Changes 8, 9.</li> <li>Added Specification Clarifications 11–16.</li> <li>Added Documentation Changes 15–17.</li> </ul>                                                                                                                                                                                                                                           |  |  |  |

| Date           | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| January 2004   | 003     | <ul> <li>Added Errata 31 to 37.</li> <li>Added Specification Changes 6 and 7.</li> <li>Removed Specification Change 4.</li> <li>Added Specification Clarifications 8, 9, and 10.</li> <li>Added Documentation Changes 6 to 13.</li> <li>Changed all references to the Intel<sup>®</sup> 80314 I/O Processor Companion Chip Developer Manual to version 273756-002.</li> <li>Minor edits for style, grammar, and consistency throughout.</li> </ul> |  |  |  |

| December 2003  | 002     | <ul> <li>Added Errata 28, 29, 30</li> <li>Updated Documentation Changes section, added specific references and added documentation change 5</li> <li>Updated Specification Changes, Specification Clarifications and Documentation Changes sections with correct formats and sub-sections</li> <li>Updated this specification update document with Intel template changes</li> </ul>                                                               |  |  |  |

| September 2003 | 001     | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

# intel® Preface

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

### Affected Documents/Related Documents

| Title                                                                    | Order  |

|--------------------------------------------------------------------------|--------|

| Intel <sup>®</sup> 80314 I/O Processor Companion Chip Developer's Manual | 273756 |

| Intel <sup>®</sup> 80314 I/O Processor Companion Chip Datasheet          | 273757 |

| Intel <sup>®</sup> 80314 I/O Processor Companion Chip Design Guide       | 273758 |

### **Nomenclature**

Errata are design defects or errors. These may cause the behavior of the Intel<sup>®</sup> 80314 I/O Processor Companion Chip to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

Specification Changes are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

Specification Clarifications describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

Note: Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

int<sub>el</sub>

### **Summary Table of Changes**

The following table indicates the errata, specification changes, specification clarifications, or documentation changes which apply to the Intel<sup>®</sup> 80314 I/O Processor Companion Chip. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

### **Codes Used in Summary Table**

### Stepping

| X:              | Errata exists in the stepping indicated. Specification Change or Clarification that applies to this stepping. |

|-----------------|---------------------------------------------------------------------------------------------------------------|

| (No mark)       |                                                                                                               |

| or (Blank box): | This erratum is fixed in listed stepping or specification change does not apply to listed stepping.           |

### Page

| (Page): | Page location of item in this document |

|---------|----------------------------------------|

|         |                                        |

### **Status**

| Doc:      | Document change or update will be implemented.                          |

|-----------|-------------------------------------------------------------------------|

| Fix:      | This erratum is intended to be fixed in a future step of the component. |

| Fixed:    | This erratum has been previously fixed.                                 |

| No Fix:   | There are no plans to fix this erratum.                                 |

| Plan Fix: | This erratum may be fixed in a future stepping of the product.          |

### Row

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

### Errata (Sheet 1 of 2)

|     | Steppings |     | Steppings |      | Steppings |                                                                                      |  | _ |

|-----|-----------|-----|-----------|------|-----------|--------------------------------------------------------------------------------------|--|---|

| No. | A-0       | B-0 | B-1       | Page | Status    | Errata                                                                               |  |   |

| 1.  | Х         |     |           | 16   | Fixed     | PE_CSR[R_TA] status bit may not be set                                               |  |   |

| 2.  | Х         |     |           | 16   | Fixed     | Large burst read may result in SFN queue overwrite                                   |  |   |

| 3.  | Х         |     |           | 16   | Fixed     | TX FIFO may be mismanaged in half-duplex mode                                        |  |   |

| 4.  | Х         | Х   | Х         | 17   | No Fix    | Frame abort feature does not work                                                    |  |   |

| 5.  | Х         | Х   | Х         | 17   | No Fix    | CLK_EN signal may glitch high                                                        |  |   |

| 6.  | Х         | Х   | Х         | 17   | No Fix    | High DC current draw when core supply collapses                                      |  |   |

| 7.  | х         |     |           | 17   | Fixed     | LS_VECTOR field of the VECTORx registers may report incorrect value 0                |  |   |

| 8.  | х         |     |           | 17   | Fixed     | A VECTORx read of 0xFF does not always mean that no interrupts are pending           |  |   |

| 9.  | х         |     |           | 18   | Fixed     | Two Intel XScale® cores cannot be the target of a single interrupt                   |  |   |

| 10. | Х         | Х   | Х         | 18   | No Fix    | DMA channel may require reset following SFN TEA errors                               |  |   |

| 11. | Х         |     |           | 18   | Fixed     | Limitations on SFN outstanding transactions                                          |  |   |

| 12. | х         | Х   | Х         | 18   | No Fix    | DMA and CRC32 or byte-swapping and CRC32 in a single operation may corrupt data      |  |   |

| 13. | Х         | Х   | Х         | 19   | No Fix    | RxQueue INT is not triggered on error condition                                      |  |   |

| 14. | х         |     |           | 19   | Fixed     | Blank EPROM delays booting of the Intel® 80314 I/O<br>Processor Companion Chip       |  |   |

| 15. | Х         |     |           | 19   | Fixed     | Inconsistent results when using SRAM                                                 |  |   |

| 16. | х         | Х   | Х         | 19   | No Fix    | Multi-byte writes are not supported on the Intel® 80314 I/O Processor Companion Chip |  |   |

| 17. | Х         |     |           | 20   | Fixed     | Register swapping lock up                                                            |  |   |

| 18. | Х         |     |           | 20   | Fixed     | Enable Relaxed Ordering Bit attributes                                               |  |   |

| 19. | Х         |     |           | 20   | Fixed     | Bus master enable bit not functional                                                 |  |   |

| 20. | х         | Х   | Х         | 20   | No Fix    | Remaining byte-count in split completion message may be incorrect                    |  |   |

| 21. | Х         |     |           | 20   | Fixed     | SDRAM bridging throughput performance limitations                                    |  |   |

| 22. | Х         |     |           | 21   | Fixed     | Extra clock cycle on SRAM reads                                                      |  |   |

| 23. | Х         |     |           | 21   | Fixed     | Use of MSI                                                                           |  |   |

| 24. | Х         |     |           | 21   | Fixed     | IRP_INTAD must be used to mask PCI INTs                                              |  |   |

| 25. | Х         |     |           | 21   | Fixed     | MemRead DWORD transaction writes to reserved bits                                    |  |   |

| 26. | Х         |     |           | 21   | Fixed     | PFAB_CSR TEA bit is not functional                                                   |  |   |

| 27. | х         |     |           | 22   | Fixed     | Bus Number is not updated correctly in the PCI-X Status Register                     |  |   |

| 28. | Х         |     |           | 22   | Fixed     | PCIXCAP[1:0] = 01b is not a valid setting                                            |  |   |

| 29. | Х         |     |           | 22   | Fixed     | Clock synchronization issues                                                         |  |   |

| 30. | х         | Х   | Х         | 22   | No Fix    | DMA channel hangs when it is stopped with STOP_REQ while CRC is enabled              |  |   |

### Errata (Sheet 2 of 2)

| No. | Steppings |            | gs  | Page | Status | Errata                                                                           |

|-----|-----------|------------|-----|------|--------|----------------------------------------------------------------------------------|

| NO. | A-0       | <b>B-0</b> | B-1 | Fage | Status | Elfala                                                                           |

| 31. | Х         | Х          | Х   | 22   | No Fix | 5-volt tolerance                                                                 |

| 32. | Х         |            |     | 23   | Fixed  | INT_PIN field PE_MISC2 00 for A0                                                 |

| 33. | х         | х          | х   | 23   | No Fix | Default SDRAM port arbitration setting can cause SFN starvation                  |

| 34. | Х         | Х          | Х   | 23   | No Fix | 80/20 port arbitration is not functional                                         |

| 35. | Х         | Х          | Х   | 24   | No Fix | Erroneous "undersize frame counter" increment                                    |

| 36. | Х         | Х          | Х   | 24   | No Fix | I2C hang condition                                                               |

| 37. | Х         |            |     | 24   | Fixed  | Incorrect PME output signaling                                                   |

| 38. | Х         | Х          | Х   | 25   | No Fix | Testing SDRAM single-bit ECC errors with 64-bit writes                           |

| 39. | Х         |            |     | 25   | Fixed  | INT_DIS read-only field prevents enabling INTx# assertion                        |

| 40. |           | Х          |     | 25   | Fixed  | 80200 lockup for Port Arbitration settings 11                                    |

| 41. | х         | х          | х   | 26   | No Fix | INTx_EN (x = A, B, C, D) bits of IRP_INTAD register do not function properly     |

| 42. | Х         | Х          |     | 26   | Fixed  | External PCI/X DMA to SDRAM Sync Packet                                          |

| 43. | х         | Х          |     | 26   | Fixed  | Bit[0] of the Revision ID field of the PCI Class Override Register is stuck at 0 |

| 44. | Х         | Х          | Х   | 26   | No Fix | GPIO[7:0] pins are driven on reset                                               |

| 45. | Х         | Х          | Х   | 27   | No Fix | External PCI/X DMA to SRAM sync packet                                           |

| 46. | х         | х          | х   | 27   | No Fix | Possible lost interrupt due to read/write of aliased IACKx registers             |

### **Specification Changes**

| No. | Document<br>Revision     | Page | Specification Changes                                                                                         |

|-----|--------------------------|------|---------------------------------------------------------------------------------------------------------------|

| 1.  | 273756-002               | 28   | Intel® 80314 I/O Processor Companion Chip does not support transparent mode operation                         |

| 2.  | 273756-002               | 28   | SFN buffer sizes for PCI-X and SDRAM interfaces                                                               |

| 3.  | 273756-002               | 28   | Only two REQ/GNT pairs are available with the internal arbiter when the PCI-X interface is 100 MHz or greater |

| 4.  | N/A                      | 28   | This item has been corrected and removed from this specification update                                       |

| 5.  | 273756-002               | 28   | CacheLineWrap mode is not supported                                                                           |

| 6.  | 273757-001               | 29   | Additional nominal and maximum power data; correction of power dissipation values                             |

| 7.  | 273757-001<br>273758-001 | 29   | Power-sequencing requirement                                                                                  |

| 8.  | 273756-002               | 30   | MPIC interrupt mapping change                                                                                 |

| 9.  | 273757-001               | 30   | Input hold time on CPU interface                                                                              |

| 10. | 273757-001<br>273758-001 | 30   | Reset slew rate for battery-backup entry                                                                      |

| 11. | 273757-001<br>273758-001 | 31   | Reset input hold time for HBA battery-backup entry                                                            |

| 12. | 273758-001               | 31   | Removal of shadow registers                                                                                   |

| 13. | 273756-002               | 31   | Single Data Rate SDRAM is not supported                                                                       |

### **Specification Clarifications**

| No. | Document<br>Revision     | Page | Specification Clarifications                                                                           |

|-----|--------------------------|------|--------------------------------------------------------------------------------------------------------|

| 1.  | 273756-002               | 32   | Byte swapping must be on data word-aligned boundaries                                                  |

| 2.  | 273756-002               | 32   | MISC_CSR register SOFT_RESET not only asserts the Px_RST pin but also resets the PCI block             |

| 3.  | 273756-002               | 32   | SD_BANK_CTRL register programming restrictions                                                         |

| 4.  | 273756-002               | 32   | Multi-bit ECC error behaviors                                                                          |

| 5.  | 273756-002               | 32   | Requirements for booting to other than an 8-bit PBI width                                              |

| 6.  | 273756-002               | 33   | Time-outs may result in data overwrites                                                                |

| 7.  | 273756-002               | 33   | The Intel® 80314 I/O Processor Companion Chip configuration retry mechanism requires the use of SEEROM |

| 8.  | 273756-002               | 33   | Intel® 80314 I/O Processor Companion Chip is capable of up to 12 GB but tested only to 3 GB $$         |

| 9.  | 273756-002               | 33   | Maximum I2C memory                                                                                     |

| 10. | 273756-002               | 33   | Proper handling of Gigabit Ethernet WAIT condition                                                     |

| 11. | 273756-002               | 34   | Proper handling of multi-bit ECC errors in abort handler                                               |

| 12. | 273756-002               | 34   | Enabling ECC/parity for SRAM                                                                           |

| 13. | 273756-002               | 34   | 64-bit PCI/X addressability                                                                            |

| 14. | 273756-002               | 35   | Reset of Intel® 80314 I/O Processor Companion Chip primary PCI/X without host PCI/X reset              |

| 15. | 273756-002               | 35   | PCI/X cannot be the destination of a sync packet                                                       |

| 16. | 273756-002<br>273757-001 | 35   | SRAM enable/disable pin                                                                                |

| 17. | 273756-002               | 35   | Driver consideration for shared memory structures under PORT_ARB = 01                                  |

| 18. | 273756-002               | 36   | PCI Target Abort when Start Address + Cache Line exceeds physical memory                               |

### **Documentation Changes**

| No. | Document<br>Revision     | Page | Documentation Changes                                                                                                |  |

|-----|--------------------------|------|----------------------------------------------------------------------------------------------------------------------|--|

| 1.  | 273756-002               | 37   | PCI-X Bridge Status Register (Embedded Mode) (PE_PCI/X _S) has incorrect values for default bus and function numbers |  |

| 2.  | 273756-002               | 37   | PFAB_CSR Register is described incorrectly                                                                           |  |

| 3.  | 273756-002               | 37   | Removed and moved to Errata #39                                                                                      |  |

| 4.  | 273756-002               | 37   | Various attribute bits are not correct                                                                               |  |

| 5.  | 273756-002               | 37   | I2C_RD_DATA Register defines incorrect byte order                                                                    |  |

| 6.  | 273756-002               | 37   | GPIO offset is not correct                                                                                           |  |

| 7.  | 273757-001               | 38   | Various ball map diagram signals are not correct                                                                     |  |

| 8.  | 273758-001               | 38   | SDRAM feedback clock length                                                                                          |  |

| 9.  | 273756-002               | 38   | PCI Interrupt Assertion register IRP_PIA added                                                                       |  |

| 10. | 273756-002               | 38   | PFAB_MEM32[11:0] field description should be reserved                                                                |  |

| 11. | 273756-002<br>273757-001 | 39   | Incorrect GPIO mappings for UART signals                                                                             |  |

| 12. | 273756-002               | 40   | I2C capability wording                                                                                               |  |

| 13. | 273756-002               | 40   | PCI/X initialization sequence                                                                                        |  |

| 14. | 273757-001               | 41   | Signal Listing Corrections                                                                                           |  |

| 15. | 273757-001               | 42   | SDRAM PLL bypass                                                                                                     |  |

| 16. | 273758-001               | 42   | PWRDELAY circuitry not required for non-battery-backup designs                                                       |  |

| 17. | 273758-001               | 42   | Design guideline table missing data                                                                                  |  |

| 18. | 273756-002               | 42   | GPIO attribute reversal                                                                                              |  |

| 19. | 273756-002               | 42   | Single Data Rate SDRAM is not supported                                                                              |  |

| 20. | 273756-003               | 42   | EE_Bx_ADDR Register Bit [31:8] description is not correct                                                            |  |

| 21. | 273756-003               | 42   | Section 2.3.1.3 and 2.3.1.4 not correct                                                                              |  |

| 22. | 273756-003               | 43   | Table 12 not correct                                                                                                 |  |

Intel<sup>®</sup> 80314 I/O Processor Companion Chip Specification Update

I I

### **Identification Information**

### **Markings**

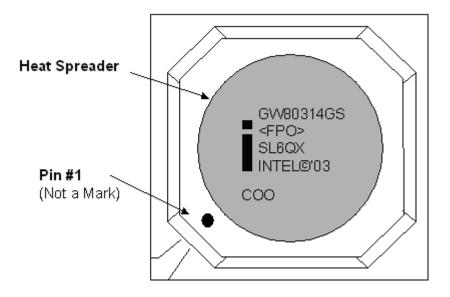

### **Topside Markings (A-0 Example)**

### **Die Details**

| Stepping | Part Number | QDF (Q)/<br>Specification<br>Number (SL) | Notes |

|----------|-------------|------------------------------------------|-------|

| A-0      | GW80314GH   | Q468                                     |       |

| A-0      | GW80314GN   | Q469                                     |       |

| A-0      | GW80314GS   | Q471                                     |       |

| A-0      | GW80314GS   | Q472                                     |       |

| B-0      | GW80314GN   | Q738                                     |       |

| B-0      | GW80314GN   | Q739                                     |       |

| B-0      | GW80314GN   | SL7DC                                    |       |

| B-0      | GW80314GS   | Q740                                     |       |

| B-0      | GW80314GS   | Q741                                     |       |

| B-0      | GW80314GS   | SL7DD                                    |       |

| B-1      | GW80314GN   | Q869                                     |       |

| B-1      | GW80314GN   | Q865                                     |       |

| B-1      | GW80314GN   | SL7NL                                    |       |

| B-1      | GW80314GS   | Q868                                     |       |

| B-1      | GW80314GS   | Q864                                     |       |

| B-1      | GW80314GS   | SL7NK                                    |       |

### **Device ID Registers**

| Device and<br>Stepping | PCI ID Register<br>(Offset 0x000)                                                                  | PCI Revision ID<br>(Offset 0x008) | JTAG Device ID                                                                |

|------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------|

| 80314 A-0              | <ul> <li>0x5378 = with SRAM</li> <li>0x5389 = without SRAM</li> <li>VID = 0x8060 always</li> </ul> | 0x0                               | <ul> <li>0x00584013 = with SRAM</li> <li>0x00585013 = without SRAM</li> </ul> |

| 80314 B-0              | <ul> <li>0x5378 = with SRAM</li> <li>0x5389 = without SRAM</li> <li>VID = 0x8060 always</li> </ul> | 0x1                               | <ul> <li>0x10584013 = with SRAM</li> <li>0x10585013 = without SRAM</li> </ul> |

| 80314 B-1              | <ul> <li>0x5378 = with SRAM</li> <li>0x5389 = without SRAM</li> <li>VID = 0x8060 always</li> </ul> | 0x2                               | <ul> <li>0x20584013 = with SRAM</li> <li>0x20585013 = without SRAM</li> </ul> |

### Errata

| 1.           | PE_CSR[R_TA] status bit may not be set                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | When the Intel <sup>®</sup> 80314 I/O Processor Companion Chip (called hereafter "the 80314") is configured for embedded mode and the destination is one of the PCI-X interfaces, when the 80314 masters a Mem_Read_Mult command for which it receives target abort, the PE_CSR[R_TA] status bit is not set.                                                                                                                         |

| Implication: | This behavior prevents the assertion of an interrupt that may be mapped to this bit.                                                                                                                                                                                                                                                                                                                                                 |

| Workaround:  | When the source is one of the PCI interfaces, the 80314 signals a target abort to the originating master.                                                                                                                                                                                                                                                                                                                            |

|              | When the source is one of the PCI-X interfaces, the 80314 returns a split completion message indicating a device-specific error. When the initiator receives one of these error indications and finds no status detailing the source of the error after interrogating the PE_CSR register, then the initiator must interrogate the CSR register of the destination targets to determine whether one of them signaled a target abort. |

|              | All other sources other than the PCI-X blocks receive an SFN response indicating an error.                                                                                                                                                                                                                                                                                                                                           |

| Status:      | Fixed                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.           | Large burst read may result in SFN queue overwrite                                                                                                                                                                                                                                                                                                                                                                                   |

| Problem:     | When the 80314 PCI-X interface accepts a burst read that is decomposed (broken down to 256-<br>byte chunks) for SFN transmission, and an error response is received from the SFN while doing the<br>completion, then the 80314 overwrites the SFN queue.                                                                                                                                                                             |

| Implication: | This may or may not overwrite the data for the related transaction, and it may also cause issues with other PCI-X transactions.                                                                                                                                                                                                                                                                                                      |

| Workaround:  | Sources of the error can be a Master Abort, Target Abort, PERR, SERR on the other PCI-X port, or a parity error on the SDRAM interface. When the system sees any of these errors, it must address the problem and reset the system.                                                                                                                                                                                                  |

| Status:      | Fixed                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.           | TX FIFO may be mismanaged in half-duplex mode                                                                                                                                                                                                                                                                                                                                                                                        |

| Problem:     | When operating in half-duplex mode, it is possible for the TX FIFO to be mismanaged.                                                                                                                                                                                                                                                                                                                                                 |

| Implication: | Mismanagement of the TX FIFO may result in under-run reporting and dropped frames. Ultimately this may lead to a lockup condition in which TX data is no longer transmitted.                                                                                                                                                                                                                                                         |

| Workaround:  | Use only full-duplex mode.                                                                                                                                                                                                                                                                                                                                                                                                           |

| Status:      | Fixed                                                                                                                                                                                                                                                                                                                                                                                                                                |

17

| 4.           | Frame abort feature does not work                                                                                                                                                                                                                                                                                                                               |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | The MAC has a feature that allows an "excessively deferred frame" to be aborted when it is backed<br>up in the TX outgoing FIFO due to heavy Ethernet traffic. This feature does not work correctly.                                                                                                                                                            |

| Implication: | When enabled, the firmware sees status indicating that the frame is aborted, when in fact it still sits in the FIFO. The FIFO status is reported correctly, so no over-run occurs.                                                                                                                                                                              |

| Workaround:  | Do not enable this feature at offset 0x00c or 0x40c, or use only full-duplex mode. Note that this feature is disabled by default.                                                                                                                                                                                                                               |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                                          |

| 5.           | CLK_EN signal may glitch high                                                                                                                                                                                                                                                                                                                                   |

| Problem:     | The SSTL2 I/O can glitch and change state when the 2.5 V supply is held up as the 1.2 V core supply collapses.                                                                                                                                                                                                                                                  |

| Implication: | This problem can cause the CLK_EN signal, which must be held low when entering power-down mode, to glitch high.                                                                                                                                                                                                                                                 |

| Workaround:  | The 2.5 V supply to the 80314 must be isolated by means of a FET switch during power-down to ensure that the I/Os on the interface cannot switch.                                                                                                                                                                                                               |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                                          |

| 6.           | High DC current draw when core supply collapses                                                                                                                                                                                                                                                                                                                 |

| Problem:     | The SSTL2 I/O potentially drives to a high state when the 2.5 V supply is held up and the 1.2 V core supply collapses.                                                                                                                                                                                                                                          |

| Implication: | This problem causes high DC current draw, since all signals are terminated to 1.25 V through a 65 $\Omega$ resistor. Current is 20 mA per I/O, or 2.5 A for the entire interface.                                                                                                                                                                               |

| Workaround:  | The 2.5 V supply to the 80314 must be isolated by means of a FET switch during power-down to ensure that the I/Os on the interface cannot switch.                                                                                                                                                                                                               |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                                          |

| 7.           | LS_VECTOR field of the VECTORx registers may report incorrect value 0                                                                                                                                                                                                                                                                                           |

| Problem:     | In the event that a level-sensitive interrupt is de-asserted prior to processing, the LS_VECTOR field of the VECTORx registers may intermittently report 0 instead of the correct vector value.                                                                                                                                                                 |

| Implication: | The source vector for a spurious vector might be reported at 0x0.                                                                                                                                                                                                                                                                                               |

| Workaround:  | When configured to use level-sensitive interrupts, initialize all source vector registers to non-zero values. These values are application-dependent and must be chosen so as not to adversely impact the system. Upon receiving notification of a spurious vector, first check to see that the source is non-zero to ensure that it is a real spurious vector. |

| Status:      | Fixed                                                                                                                                                                                                                                                                                                                                                           |

| 8.           | A VECTORx read of 0xFF does not always mean that no interrupts are pending                                                                                                                                                                                                                                                                                      |

| Problem:     | A VECTORx read of 0xFF does not always mean that no interrupts are pending.                                                                                                                                                                                                                                                                                     |

| Implication: | Software mechanisms that poll the VECTOR register in their ISR in order to process multiple INTs with minimal context switches cannot use the value of 0xFF to identify when no INTs are pending.                                                                                                                                                               |

| Workaround:  | When a spurious vector is reported, software must read the register indicated by the LS_VECTOR field in the VECTORx register to determine whether the INT is truly spurious                                                                                                                                                                                     |

| Status:      | Fixed                                                                                                                                                                                                                                                                                                                                                           |

|              |                                                                                                                                                                                                                                                                                                                                                                 |

Errata

| 9.           | Two Intel XScale $^{	extsf{B}}$ cores cannot be the target of a single interrupt                                                                                                                                                                                                                                                                                    |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | Only one interrupt output may be selected in the SEL_OUT field of the control registers for each interrupt source.                                                                                                                                                                                                                                                  |

| Implication: | When two Intel XScale <sup>®</sup> cores are implemented in a single design, they cannot both be the target of an interrupt.                                                                                                                                                                                                                                        |

| Workaround:  | When both cores require notification of an interrupt, one core must be specified as the target and must use an application-specific mechanism to report the interrupt to the other core. Examples are shared memory, use of the doorbell interrupt in the MPIC, and so on.                                                                                          |

| Status:      | Fixed                                                                                                                                                                                                                                                                                                                                                               |

| 10.          | DMA channel may require reset following SFN TEA errors                                                                                                                                                                                                                                                                                                              |

| Problem:     | When a DMA receives a TEA from the SFN, a channel may get hung in the active state (DACT asserted).                                                                                                                                                                                                                                                                 |

| Implication: | When a DMA channel is hung with DACT asserted, the DMA channel cannot be re-programmed for another DMA transfer until it is soft-reset.                                                                                                                                                                                                                             |

| Workaround:  | When firmware detects a TEA from the SFN, it must ensure that the DMA channel(s) affected are soft-reset by means of the CHx_GCSR if they are hung with DACT asserted.                                                                                                                                                                                              |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                                              |

| 11.          | Limitations on SFN outstanding transactions                                                                                                                                                                                                                                                                                                                         |

| Problem:     | When a read transaction is decomposed internally by the 80314 with one PCI-X bus master controlling traffic to the other PCI-X block in embedded mode, all additional reads are held up until there is only one remaining segment to be returned.                                                                                                                   |

| Implication: | In a worst-case scenario, only one outstanding transaction that is 256 bytes (or misaligned transaction $> \sim 128$ bytes) is serviced at one time.                                                                                                                                                                                                                |

| Workaround:  | None                                                                                                                                                                                                                                                                                                                                                                |

| Status:      | Fixed                                                                                                                                                                                                                                                                                                                                                               |

| 12.          | DMA and CRC32 or byte-swapping and CRC32 in a single operation may corrupt data                                                                                                                                                                                                                                                                                     |

| Problem:     | Performing a DMA+CRC32 operation or ByteSwap+CRC32 with one of the PCI-X blocks as source may corrupt the CRC because PCI-X read completions might complete out of order.                                                                                                                                                                                           |

| Implication: | CRC32 cannot be calculated during a DMA operation with one of the PCI-X blocks as the source. Byte swapping cannot be performed together with a CRC32.                                                                                                                                                                                                              |

| Workaround:  | The software workaround requires the data to be transferred from a PCI-X block to memory (SDRAM or SRAM), and then have the CRC calculated in place as a separate operation. As long as the data going into the DMA engine does not originate directly from a PCI-X block, the data can be transferred to any location (including PCI-X) while calculating the CRC. |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                                              |

| 13.          | RxQueue INT is not triggered on error condition                                                                                                                                                                                                                                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | The RxQueue interrupt bit of the Gigabit Ethernet port interrupt status register is not set when an error condition occurs.                                                                                                                                                                                                |

| Implication: | An RxQueue interrupt may be missed without proper attention to this errata.                                                                                                                                                                                                                                                |

| Workaround:  | The driver must understand that when an RxError interrupt is seen in the Gigabit Ethernet port interrupt status register, an RXQueue interrupt is also associated, even though it is not set in the port interrupt status register.                                                                                        |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                     |

| 14.          | Blank EPROM delays booting of the Intel <sup>®</sup> 80314 I/O Processor Companion Chip                                                                                                                                                                                                                                    |

| Problem:     | When a blank EPROM is attached to the 80314 $I^2C$ bus, the 80314 may take up to 90 seconds to boot.                                                                                                                                                                                                                       |

| Implication: | Longer boot time.                                                                                                                                                                                                                                                                                                          |

| Workaround:  | Program the EPROM to set some register values.                                                                                                                                                                                                                                                                             |

| Status:      | Fixed                                                                                                                                                                                                                                                                                                                      |

| 15.          | Inconsistent results when using SRAM                                                                                                                                                                                                                                                                                       |

| Problem:     | Data header integrity issues have been seen when DMA or GigE descriptors are placed in SRAM.                                                                                                                                                                                                                               |

| Implication: | SRAM should not be used.                                                                                                                                                                                                                                                                                                   |

| Workaround:  | Use SDRAM.                                                                                                                                                                                                                                                                                                                 |

| Status:      | Fixed                                                                                                                                                                                                                                                                                                                      |

| 16.          | Multi-byte writes are not supported on the Intel <sup>®</sup> 80314 I/O Processor<br>Companion Chip                                                                                                                                                                                                                        |

| Problem:     | When performing a multi-byte write on $I^2C$ , the 80314 breaks up the write into multiple single-byte writes. The $I^2C$ EEPROM requires at least 10 ms before accepting the next write. The $I^2C$ does not provide enough time for one byte to complete before starting the next.                                       |

|              | Read accesses are not affected by this issue.                                                                                                                                                                                                                                                                              |

| Implication: | For multi-byte writes on $I^2C$ remaining byte, write(s) following the first time-out while waiting for the target device to come out of the busy state.                                                                                                                                                                   |

| Workaround:  | Multi-byte writes must not be performed. The software must write one byte at a time and must wait the proper amount of time between single-byte writes. The software must also monitor the status of the $I^2C$ to ensure that the write went out and that enough time was given for the target device to become non-busy. |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                     |

### Errata

| 17.                         | Register swapping lock up                                                                                                                                    |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:                    | The following two combinations of BSWAP, WSWAP, and RGSWAP registers causes the 80314 to lock up:                                                            |

|                             | RGSWAP and WSWAP without BSWAP                                                                                                                               |

|                             | RGSWAP and BSWAP without WSWAP                                                                                                                               |

| Implication:                | RGSWAP is not available without data swap.                                                                                                                   |

| Workaround:                 | None                                                                                                                                                         |

| Status:                     | Fixed                                                                                                                                                        |

| 18.                         | Enable Relaxed Ordering Bit attributes                                                                                                                       |

| Problem:                    | The Enable Relaxed Order Bit (RO_EN) in the PCI-X Capability Register (PE_PCI/X_C) is incorrectly reset to 0. This bit should be reset to 1.                 |

| Implication:                | None                                                                                                                                                         |

| Workaround:                 | Because the value is read/write, firmware may change the value to 0.                                                                                         |

| Status:                     | Fixed                                                                                                                                                        |

| 19.                         | Bus master enable bit not functional                                                                                                                         |

| Problem:                    | Setting the Bus Master Enable bit to 0 in the PCI-X Command Register may not prohibit the 80314 from mastering transactions on the respective PCI-X segment. |

| Implication:                | Implications vary depending on usage/reliance of the BME bit.                                                                                                |

| Workaround:                 | None                                                                                                                                                         |

| Status:                     | Fixed                                                                                                                                                        |

| 20.                         | Remaining byte-count in split completion message may be incorrect                                                                                            |

| Problem:                    | The 80314 may return the incorrect byte-count on a split completion message when both of the following occur:                                                |

|                             | 1. A read is accepted that is greater than 1024 bytes, and                                                                                                   |

|                             | 2. An error occurs in the first 256 bytes.                                                                                                                   |

| Implication:                | Some upstream bridges may use this byte count to optimize their own buffer usage.                                                                            |

| Workaround:                 | None                                                                                                                                                         |

| Status:                     | No Fix                                                                                                                                                       |

| 21.                         | SDRAM bridging throughput performance limitations                                                                                                            |

| Problem:                    | There is an issue with the way the synchronization is done between the SFN and SDRAM clock domains that may impact performance.                              |

|                             |                                                                                                                                                              |

| Implication:                | Performance through SDRAM (one PCI bus writing and one reading) is impacted by approximately 5%.                                                             |

| Implication:<br>Workaround: |                                                                                                                                                              |

Errata

| 22.          | Extra clock cycle on SRAM reads                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | When making multiple 32-byte reads to internal SRAM, there is a dead clock cycle inserted between the 32-byte accesses.                                                                                                                                                                                                                                                                                                                                                  |

| Implication: | Performance on multiple 32-byte reads to SRAM may be impacted by up to 20%.                                                                                                                                                                                                                                                                                                                                                                                              |

| Workaround:  | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Status:      | Fixed                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 23.          | Use of MSI                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Problem:     | The MM_CAP[2:0] field in the P_MSIC register at offset 0x0E0 cannot be changed from its default value of four messages.                                                                                                                                                                                                                                                                                                                                                  |