# AMD-8132™ HyperTransport™ PCI-X<sup>®</sup> 2.0 Tunnel Product Summary

#### **Overview**

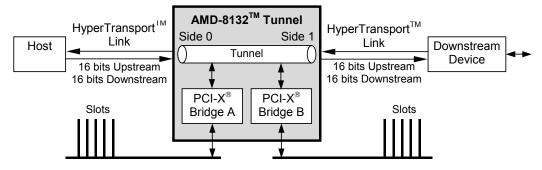

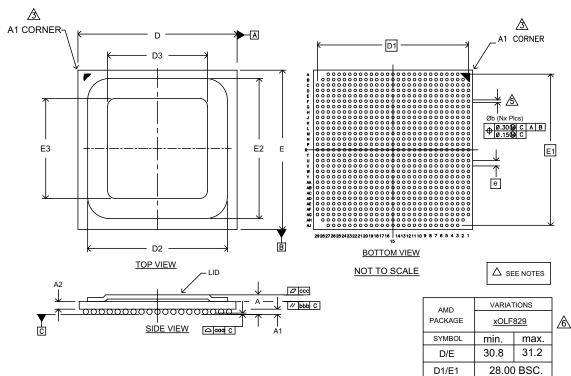

The AMD-8132<sup>TM</sup> HyperTransport<sup>TM</sup> PCI-X<sup>®</sup>2.0 tunnel developed by AMD provides two PCI-X bridges supporting DDR transfer rates. The AMD-8132 tunnel is compliant with *HyperTransport<sup>TM</sup> I/O Link Specification, Rev 2.0* including errata up to specification Rev 1.05c. The package is a 31 x 31 millimeter, 829 ball, flip-chip organic BGA. The core is 1.2 volts. Power dissipation is 8 watts.

### HyperTransport™ Features:

- HyperTransport tunnel with side 0 16-bit input/ 16-bit output and side 1 16-bit input/16-bit output.

- Either side can connect to the host or to a downstream HyperTransport technology compliant device.

- Each side supports HyperTransport technology-defined reduced bit widths: 8-bit, 4-bit, and 2-bit.

- Each side supports transfer rates of 2000, 1600, 1200, 1000, 800, and 400 mega-bits per second per wire.

- Maximum bandwidth is 8 gigabytes per second across each side (half upstream and half downstream).

- Independent transfer rate for each side and each direction.

- Independent bit width selection for each side and each direction.

- Link disconnect protocol support.

- HyperTransport interrupt control support.

- 64-bit address support.

### **PCI-X<sup>®</sup> Features:**

- Two PCI-X bridges: bridge A and bridge B.

- Each bridge supports a 64-bit data bus.

- Each bridge supports operational Modes 1 and 2 of PCI-X and conventional PCI protocol.

- In PCI-X Mode 2, bridges support transfer rates of 266 and 200 MHz.

- In PCI-X Mode 1, bridges support transfer rates of 133, 100, 66, and 50 MHz.

- In PCI mode, bridges support transfer rates of 66, 50, 33, and 25 MHz.

- Independent transfer rates and operational modes for each bridge.

- Each bridge includes support for up to 5 PCI masters with clock, request, and grant signals.

- Each bridge includes a HyperTransport<sup>TM</sup> technology compliant interrupt controller. Legacy interrupt controller and IOAPIC modes are also supported.

- Each bridge can receive PCI device interrupts via INTA/B/C/D pins or via MSI/MSI-X transactions.

- SHPC-compliant hot-plug controller and support.

- PCI-X Mode 2, 1.5 V link signaling. PCI-X Mode 1, 3.3 V link signaling. PCI, 3.3 V link signaling.

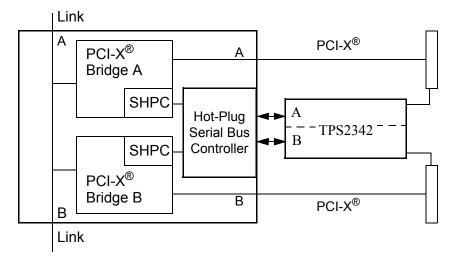

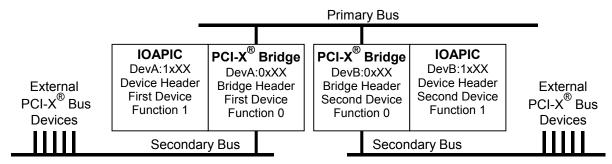

Example system block diagram.

© 2004, 2005 Advanced Micro Devices, Inc.

All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD Arrow logo, and combinations thereof, and AMD-8132 are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

PCI-X is a registered trademark of the PCI-SIG Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# **Table of Contents**

| Revisio | n History  | y                                                            |    |

|---------|------------|--------------------------------------------------------------|----|

| Preface | e          |                                                              |    |

|         | References | s and Resources                                              | 13 |

|         |            | ns                                                           |    |

|         |            | and Terms                                                    |    |

|         | •          | ınctional Operation                                          |    |

| Chapte  |            | <del>-</del>                                                 |    |

|         |            | rviewnel Links                                               |    |

|         |            |                                                              |    |

|         | 1.2.1      | Link Frequency                                               |    |

|         | 1.2.2      | Link Width                                                   |    |

|         | 1.2.3      | Link Behavior                                                |    |

|         | 1.2.4      | Link PHY and Compensation                                    |    |

|         |            | X <sup>®</sup> 2.0 Bridges                                   |    |

|         | 1.3.1      | Arbiters                                                     |    |

|         |            | 3.1.1 Internal Arbiters                                      |    |

|         |            | 3.1.2 External Arbiters                                      |    |

|         | 1.3.2      | Interrupts                                                   |    |

|         |            | 3.2.1 Interrupt Discovery and Configuration                  |    |

|         |            | 3.2.2 SHPC_INTR and Fatal/Nonfatal Interrupts                |    |

|         |            | 3.2.3 Message Signalled Interrupts (MSI/MSI-X)               |    |

|         | 1.3.3      | 3.2.4 INTx Virtual Wire Messages                             |    |

|         | 1.3.3      | Prefetching In Conventional PCI Mode                         |    |

|         |            | •                                                            |    |

|         | 1.3.5      | HyperTransport <sup>TM</sup> Requests Claimed by the Bridges |    |

|         | 1.3.6      | Transaction Considerations                                   |    |

|         |            | 3.6.1General                                                 |    |

|         |            | 3.6.2Pullups on Upper PCI Bus3.6.3Upstream Transactions      |    |

|         |            | 3.6.4 Downstream Transactions                                |    |

|         | 1.3.7      |                                                              |    |

|         |            | 3.7.1 Multi-Slot Hot-Plug                                    |    |

|         |            | 3.7.2 Single-Slot Hot-Plug                                   |    |

|         |            | 3.7.3 TPS2340A Hot-Plug Power Controller                     |    |

|         | 2.0        | 1.3.7.3.1 TPS2340A Serial Interface                          |    |

|         |            | 1.3.7.3.2 TPS2340A Serial Data: Power Controllers to Tunnel  |    |

| 1.3.7.3.3 TPS2340A Serial Data: Tunnel to Power                              | Controllers |

|------------------------------------------------------------------------------|-------------|

| 1.3.7.3.4 TPS2340A SHPC Interrupts, Events, And                              | Errors      |

| 1.3.7.4 TPS2342 Hot-Plug Power Controller                                    |             |

| 1.3.7.4.1 TPS2342 Serial Interface                                           |             |

| 1.3.7.4.2 TPS2342 Serial Data: Power Controllers to                          |             |

| 1.3.7.4.3 TPS2342 Serial Data: Tunnel to Power Co                            |             |

| 1.3.7.4.4 TPS2342 SHPC Interrupts, Events, And E                             |             |

| 1.3.8 PCI-X 2.0 PHY Compensation Update                                      |             |

| Chapter 2 Signal Descriptions                                                |             |

| 2.1 HyperTransport Link Signals                                              |             |

| 2.2 PCI-X and Hot-Plug Controller Signals                                    |             |

| 2.3 Miscellaneous Signals                                                    |             |

| 2.3.1 JTAG Signals                                                           |             |

| 2.4 Power and Ground                                                         |             |

| 2.5 Straps During Initialization                                             |             |

| 2.6 Pins With Alternate Functions                                            |             |

| 2.7 AMD-8132 <sup>™</sup> Tunnel Configurations: Their Effect on Alter       |             |

| 2.7.1 Internal Arbiter                                                       |             |

| 2.7.1.1 Single Slot: Mode 2                                                  |             |

| 2.7.1.2 Multiple Slots: Mode 1 ECC                                           |             |

| 2.7.1.3 Multiple Slots: Model Without ECC                                    |             |

| 2.7.2 External Arbiter                                                       |             |

| 2.7.2.1 Single Slot       Single Slot         2.7.2.2 Multiple Slots: Mode 1 |             |

| Chapter 3 Registers                                                          |             |

| 3.1 Register Overview                                                        |             |

| 3.1.1 Configuration Space                                                    |             |

| 3.1.2 Register Naming and Description Conventions                            |             |

| 3.2 PCI-X Bridge Configuration Registers                                     |             |

| PCI-X Bridge Vendor and Device ID                                            |             |

| PCI-X Bridge Status and Command                                              |             |

| PCI-X Bridge Revision and Class Code                                         |             |

| PCI-X Bridge BIST-Header-Latency-Cache                                       |             |

| PCI-X SHPC Base Address Low                                                  |             |

| PCI-X SHPC Base Address High                                                 |             |

| PCI-X Bridge Bus Numbers and Secondary Latency                               |             |

| PCI-X Bridge Memory Base/Limit, I/O Base/Limit, and S                        |             |

| PCI-X Bridge Capabilities Pointer                                            |             |

|                                                                              |             |

|     | PCI-X Bridge Interrupt and Bridge Control              |     |

|-----|--------------------------------------------------------|-----|

|     | PCI-X Miscellaneous                                    | 79  |

|     | PCI-X Scratch                                          | 83  |

|     | PCI-X Misc II and Pins Latched at Rising Edge of PWROK | 83  |

|     | Prefetch Control                                       | 86  |

|     | PCI-X Secondary Status                                 | 89  |

|     | PCI-X Bridge Status                                    | 90  |

|     | PCI-X Upstream Split Transaction                       |     |

|     | PCI-X Downstream Split Transaction                     | 91  |

|     | PCI-X ECC Control and Status                           |     |

|     | PCI-X ECC First Address                                | 95  |

|     | PCI-X ECC Second Address                               | 95  |

|     | PCI-X ECC Attribute                                    |     |

|     | Misc Bridge Errors                                     | 96  |

|     | Misc Error Enables                                     | 98  |

|     | SHPC Capabilities                                      | 99  |

|     | SHPC Data                                              | 99  |

|     | Power Management Capabilities                          | 100 |

|     | Power Management Status and Control                    | 101 |

|     | Extended Configuration Address Range                   | 102 |

|     | Interrupt Discovery and Configuration                  | 102 |

|     | HyperTransport Revision ID Capability Block            | 103 |

|     | Link Command                                           | 104 |

|     | Link Configuration and Control                         | 105 |

|     | Link Revision, Errors, and Frequency Capability 0      | 107 |

|     | Feature, Link Errors, and Frequency Capability 1       | 107 |

|     | Error Handling and Link Enumeration                    | 108 |

|     | Link Non-Prefetchable Memory Space Extension           | 109 |

|     | Tunnel Control                                         | 110 |

|     | Clock Control                                          | 112 |

|     | MSI Mapping Capability Block Header                    | 113 |

|     | MSI Mapping Capability Block Lower Address             | 113 |

|     | MSI Mapping Capability Block Upper Address             | 113 |

| 3.3 | PCI-X IOAPIC Configuration Registers                   | 113 |

|     | IOAPIC Vendor and Device ID                            |     |

|        |      | IO    | APIC Status and Command                          | .114  |

|--------|------|-------|--------------------------------------------------|-------|

|        |      | IO    | APIC Revision and Class Code                     | .115  |

|        |      | IO    | APIC Device BIST-Header-Latency-Cache            | .115  |

|        |      | IO    | APIC Base Address Low                            | .115  |

|        |      | IO    | APIC Base Address High                           | .116  |

|        |      | IO    | APIC Device Subsystem ID and Subsystem Vendor ID | .116  |

|        |      |       | inter to Capabilities Block                      |       |

|        |      | IO    | APIC Control                                     | .116  |

|        |      | Ну    | perTransport Revision Capabilities Block         | .117  |

|        | 3.4  | PHY   | Compensation Control                             | . 118 |

|        |      | PC    | CI-X PHY Compensation Control                    | .118  |

|        |      | Lir   | nk PHY Compensation Control                      | .121  |

|        | 3.5  | Perfo | ormance Counters                                 | . 125 |

|        |      | Per   | rformance Counters and Control                   | .125  |

|        | 3.6  | IOAI  | PIC Register Space                               | . 131 |

|        | 3.7  |       | C Working Registers                              |       |

|        |      |       | IPC Base Offset                                  |       |

|        |      |       | IPC Slots Available I                            |       |

|        |      |       | IPC Slots Available II                           |       |

|        |      |       | IPC Slot Configuration                           |       |

|        |      | SH    | IPC Secondary Bus Configuration                  | .136  |

|        |      | SH    | IPC Command and Status                           | .136  |

|        |      | SH    | IPC Interrupt Locator                            | .139  |

|        |      | SH    | IPC SERR Locator                                 | .140  |

|        |      | SH    | IPC SERR-INT                                     | .140  |

|        |      | SH    | IPC Logical Slot                                 | .141  |

| Chapte | er 4 | Cl    | ocks and Reset                                   | .143  |

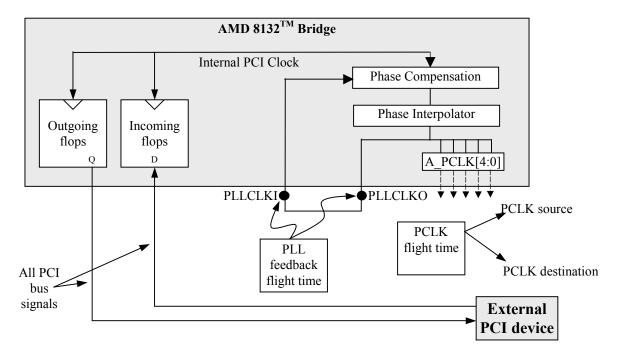

|        | 4.1  | Clock | king                                             |       |

|        |      | 4.1.1 | Systemboard Requirements                         |       |

|        | 4.0  | 4.1.2 | Clock Gating                                     |       |

|        | 4.2  |       | t and Initialization                             |       |

|        |      | 4.2.1 | HyperTransport Reset And Initialization          |       |

|        |      |       | 2.1.2 LDTSTOP_L Link Re-Connect Sequence         |       |

|        |      | 4.2.2 | PCI/PCI-X Reset                                  |       |

|        |      | 4.2.3 | Non-Hot-Plug Initialization                      | . 146 |

|        |      |       |                                                  |       |

|           | 4.2.4  | Hot-Plug Initialization                               | 148 |

|-----------|--------|-------------------------------------------------------|-----|

| Chapter 5 | Er     | ror Conditions and Handling                           | 149 |

| 5.1       |        | erTransport Interface Errors                          |     |

|           | 5.1.1  | Sync Flood                                            | 149 |

|           | 5.1.2  | CRC Errors                                            | 149 |

|           | 5.1.3  | Protocol Errors                                       | 149 |

|           | 5.1.4  | Receive Buffer Overflow Errors                        | 150 |

|           | 5.1.5  | End of Chain (EOC) Errors                             | 150 |

|           | 5.1.6  | Atomic Read-Modify-Write Requests                     | 150 |

|           | 5.1.7  | Illegal Configuration and I/O Accesses                | 150 |

|           | 5.1.8  | Posted Write Data Errors                              | 151 |

|           | 5.1.9  | Response Match Errors                                 | 151 |

|           | 5.1.10 | Error Responses                                       | 151 |

|           | 5.1    | 10.1 Master Aborts                                    | 151 |

|           | 5.1    | .10.2 Target Aborts                                   | 152 |

|           | 5.1    | .10.3 Data Errors                                     | 152 |

| 5.2       | PCI/I  | PCI-X Interface Errors                                | 152 |

|           | 5.2.1  | SERR_L Assertion                                      | 152 |

|           | 5.2.2  | Addressing Errors                                     | 153 |

|           | 5.2    | 2.2.1 Address/Byte Enable Mismatch                    |     |

|           | 5.2    | 2.2.2 Bursts Across Address Range Boundaries          | 153 |

|           | 5.2.3  |                                                       |     |

|           | 5.2    | PERR_L Assertion on Posted Write Data                 |     |

|           | 5.2    | PERR_L Assertion on Nonposted Write Data              |     |

|           |        | PERR_L Assertion on Read or Split Completion Data     |     |

|           | 5.2.4  |                                                       |     |

|           |        | 2.4.1 Address/Attribute Phase Uncorrectable Errors    |     |

|           |        | 2.4.2 Posted Write Data Phase Uncorrectable Errors    |     |

|           |        | 2.4.3 Nonposted Write Data Phase Uncorrectable Errors |     |

|           |        | 2.4.4 Read Data Phase Uncorrectable Errors            |     |

|           | 5.2.5  | End of Chain Errors                                   |     |

|           | 5.2.6  | PCI Discard Timeouts                                  |     |

|           | 5.2.7  | Master Aborts                                         |     |

|           | 5.2.8  | Target Aborts                                         |     |

|           | 5.2.9  | Split Completion Error Messages                       |     |

|           | 5.2.10 | Unexpected Split Completions                          |     |

|           | 5.2.10 | PCI/PCI-X Busy Time Out                               |     |

| 5.3       |        | D-8132 Tunnel Error Signaling Methods                 |     |

| 5.5       | AIVIL  | 7-0192 Tullion Littor Signaturg Michigas              | 133 |

| 5.3.1      | 1 HyperTransport Interface                          | 159 |

|------------|-----------------------------------------------------|-----|

|            | 5.3.1.1 Sync Flood                                  | 159 |

|            | 5.3.1.2 Posted Write Data Errors                    | 159 |

|            | 5.3.1.3 Error Responses                             | 159 |

| 5.3.2      | 2 Fatal/Nonfatal Interrupts                         | 159 |

| 5.3.3      | B PCI/PCI-X Interface                               | 160 |

|            | 5.3.3.1 PERR# Assertion                             | 160 |

|            | 5.3.3.2 Target Aborts                               | 160 |

|            | 5.3.3.3 Split Completion Error Messages             | 160 |

|            | 5.3.3.4 Data Poisoning                              | 160 |

| Chapter 6  | Test                                                | 161 |

| 6.1 Po     | ower-Down Mode                                      | 161 |

| 6.2 JT     | 'AG                                                 | 161 |

| Chapter 7  | Electrical Data                                     | 163 |

| 7.1 Po     | ower Requirements                                   | 163 |

| 7.1.3      | 1 Absolute Ratings                                  | 163 |

| 7.1.2      | 2 Operating Ranges                                  | 163 |

| 7.1.3      | 3 Current and Power Consumption                     | 164 |

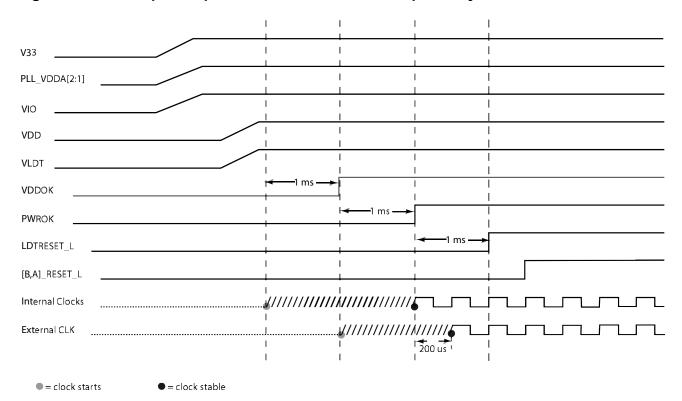

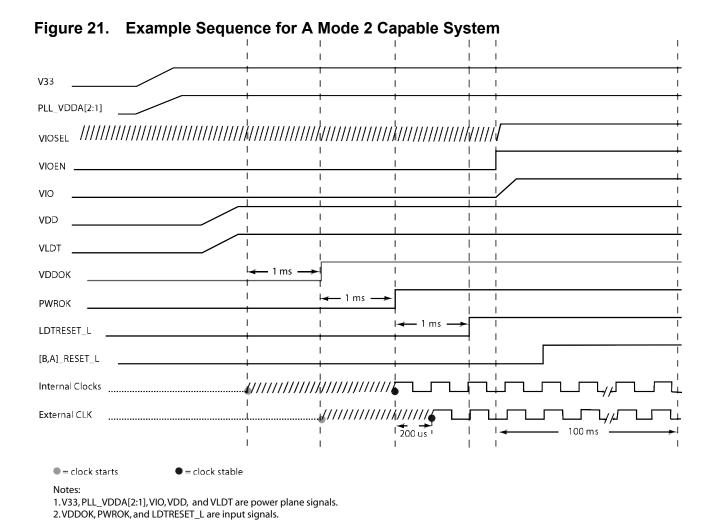

| 7.1.4      | 4 Power Plane Sequencing                            | 164 |

| 7.2 In     | put Requirements for REFCLK_[H,L]                   | 167 |

| 7.2.       | REFCLK_[H,L]: DC Requirements                       | 167 |

| 7.2.2      | 2 REFCLK_[H,L]: AC Requirements                     | 168 |

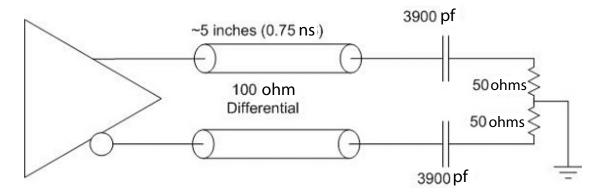

| 7.2.3      | B Differential Clock Test Load                      | 168 |

| 7.3 3      | 3 Volt Signals                                      | 170 |

| 7.3.       | DC Characteristics: Signals on V33 Power Plane      | 170 |

| 7.3.2      | 2 AC Input Requirements: Signals on V33 Power Plane | 170 |

| 7.4 In     | put Requirements for PCIXCAP                        | 170 |

| 7.4.       | DC Input Requirements: PCIXCAP                      | 170 |

| 7.4.2      | 2 AC Input Requirements: PCIXCAP                    | 171 |

| 7.5 H      | yperTransport Signal Characteristics                |     |

| 7.6 PC     | CI and PCI-X Signal Characteristics                 | 171 |

| Chapter 8  | Package and Pin Designations                        | 173 |

| =          | ickage Specification                                |     |

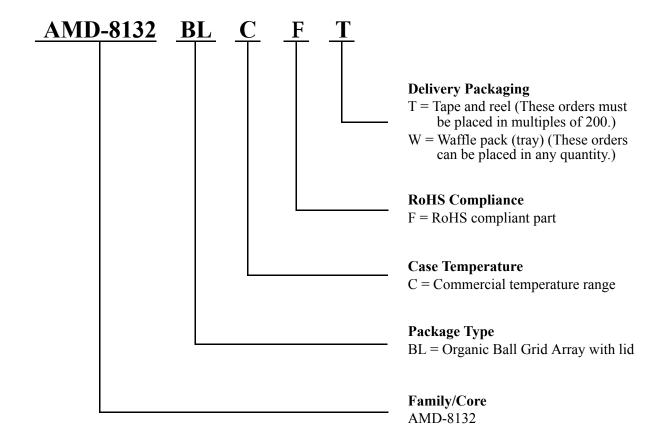

| Appendix A | Ordering Part Number                                | 195 |

# **List of Figures**

| Figure 1.  | AMD-8132 <sup>TM</sup> Tunnel: Block Diagram               | 18  |

|------------|------------------------------------------------------------|-----|

| Figure 2.  | Link Buffer Diagram                                        |     |

| Figure 3.  | AMD-8132 Tunnel Interrupt Routing                          | 22  |

| Figure 4.  | System Diagram: Multiple Hot-Plug Slots on a Bridge        | 32  |

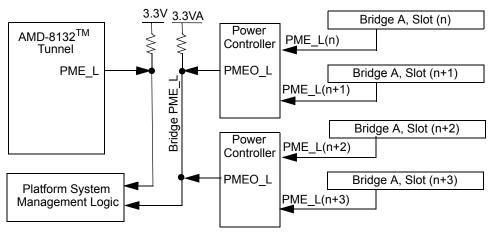

| Figure 5.  | System Diagram: PME_L Signals                              | 33  |

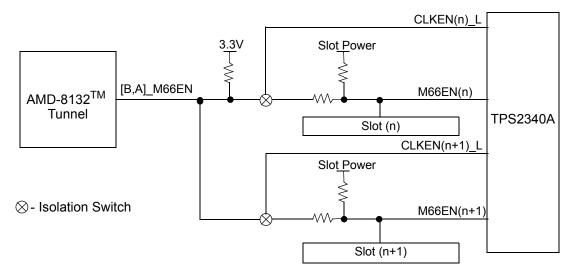

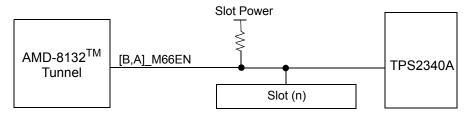

| Figure 6.  | System Diagram: M66EN Signals With TPS2340A                | 34  |

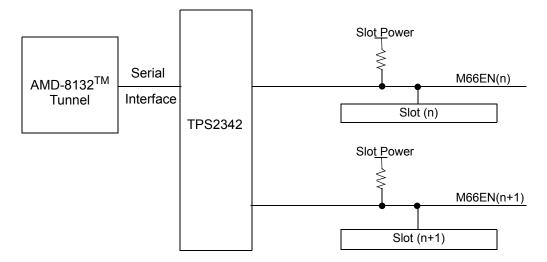

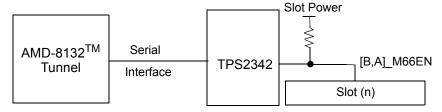

| Figure 7.  | System Diagram: M66EN Signals With TPS2342.                | 34  |

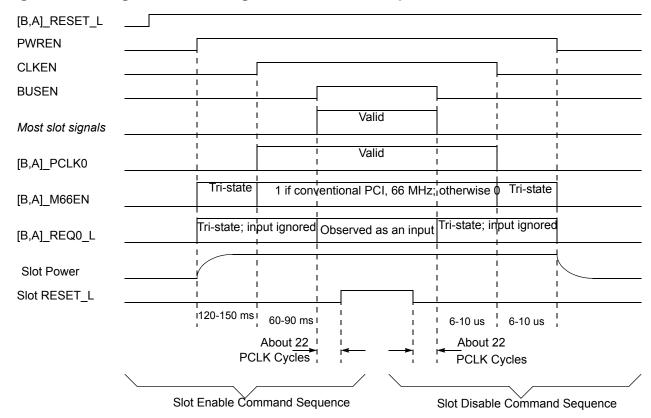

| Figure 8.  | Multi-Slot Hot-Plug Enable/Disable Sequence                | 35  |

| Figure 9.  | System Diagram: Single-Slot Hot-Plug for TPS2340A          | 36  |

| Figure 10. | System Diagram: Single-Slot Hot-Plug for TPS2342           | 36  |

| Figure 11. | Single-Slot Hot-Plug Enable/Disable Sequence               | 37  |

| Figure 12. | Single-Slot Hot-Plug M66EN Connections: TPS2340A           | 38  |

| Figure 13. | Single-Slot Hot-Plug M66EN Connections: TPS2342            | 38  |

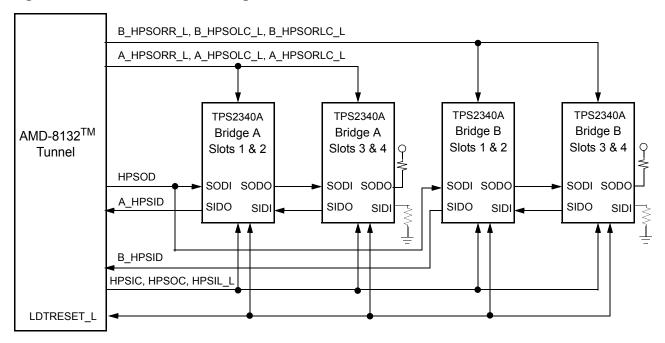

| Figure 14. | TPS2340A Hot-Plug Serial Interface Connections             | 39  |

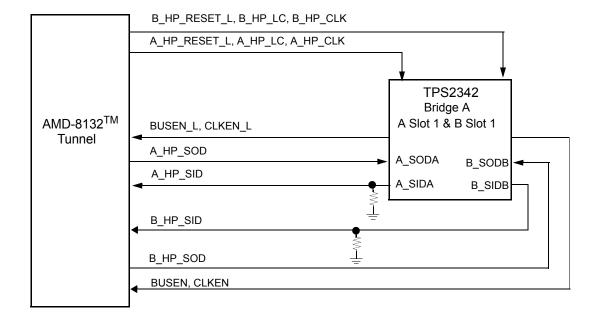

| Figure 15. | TPS2342 Hot-Plug Serial Interface Connections: Single Slot | 40  |

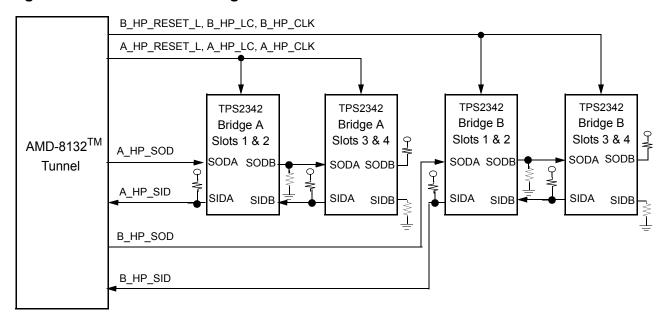

| Figure 16. | TPS2342 Hot-Plug Serial Interface Connections: Multi-Slot  | 41  |

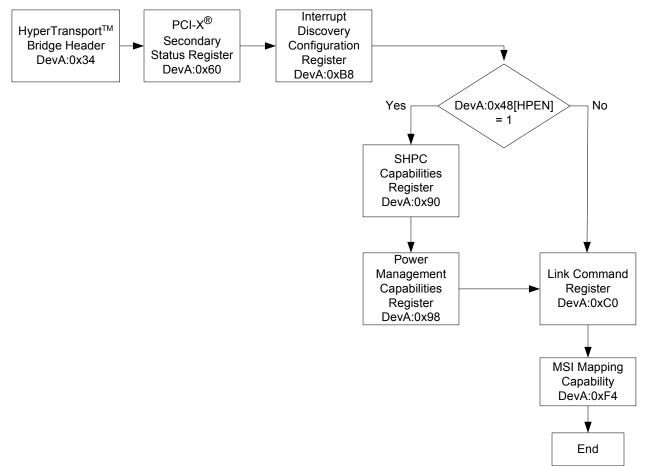

| Figure 17. | Example Capability Block Chain: Device A.                  | 65  |

| Figure 18. | Configuration Space.                                       | 66  |

| Figure 19. | Systemboard Clocking                                       | 144 |

| Figure 20. | Example Sequence for A Not Mode 2 Capable System           | 166 |

| Figure 21. | Example Sequence for A Mode 2 Capable System               | 167 |

| Figure 22. | Differential Test Load                                     | 169 |

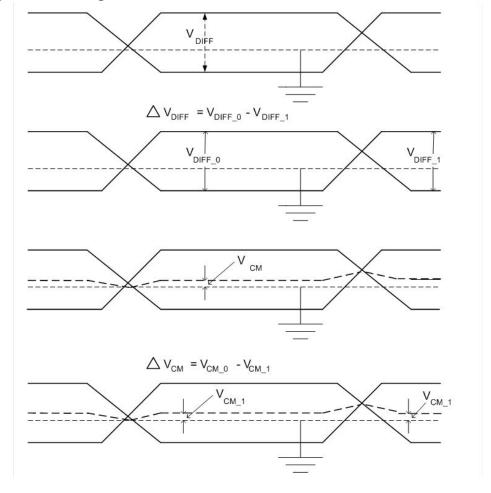

| Figure 23. | Single-Ended Measurement Definitions                       | 169 |

| Figure 24. | AMD-8132 Tunnel: Ball Designations                         | 173 |

| Figure 25. | Package Mechanical Drawing.                                | 194 |

# **List of Tables**

| Table 1.  | MSI/MSI-X Mapping: PCI to HyperTransport <sup>TM</sup> | 24  |

|-----------|--------------------------------------------------------|-----|

| Table 2.  | Signal Isolation Groups                                |     |

| Table 3.  | Register Naming Conventions                            |     |

| Table 4.  | Memory Mapped Address Spaces                           |     |

| Table 5.  | Register Attributes                                    |     |

| Table 6.  | AMD-8132™ Tunnel Registers and Register Addresses      | 68  |

| Table 7.  | SHPC Command Codes                                     |     |

| Table 8.  | Mode 1 Bus Speed Encodings                             |     |

| Table 9.  | Mode 2 Bus Speed Encodings                             | 138 |

| Table 10. | Non-Hot-Plug Operational Modes and Selects             | 146 |

| Table 11. | TMODE[2:0] Encodings                                   |     |

| Table 12. | Absolute Maximum Ratings                               | 163 |

| Table 13. | Temperature                                            | 163 |

| Table 14. | Operating Ranges                                       | 163 |

| Table 15. | DC Current and Power Consumption                       | 164 |

| Table 16. | REFCLK_[H,L] DC Requirements                           | 167 |

| Table 17. | REFCLK_[H,L] AC Requirements                           | 168 |

| Table 18. | V33: DC Signal Characteristics                         | 170 |

| Table 19. | V33: AC Input Requirements                             | 170 |

| Table 20. | PCIXCAP: DC Input Requirements                         | 170 |

| Table 21. | PCIXCAP: AC Input Requirements                         | 171 |

| Table 22. | Signals Sorted by Location A - C                       | 174 |

| Table 23. | Signals Sorted by Location D - F                       | 175 |

| Table 24. | Signals Sorted by Location G - J                       | 176 |

| Table 25. | Signals Sorted by Location K - M                       | 177 |

| Table 26. | Signals Sorted by Location N - R                       | 178 |

| Table 27. | Signals Sorted by LocationT - V                        | 179 |

| Table 28. | Signals Sorted by Location W - AA                      | 180 |

| Table 29. | Signals Sorted by Location AB - AD                     |     |

| Table 30. | Signals Sorted by Location AE - AG                     |     |

| Table 31. | Signals Sorted by Location AH - AJ                     |     |

| Table 32. | Signals Sorted by Name A_A - A_M                       |     |

| Table 33. | Signals Sorted by Name A_P - B_A                       |     |

| Table 34. | Signals Sorted by Name B_C - L0_CADIN                  |     |

| Table 35. | Signals Sorted by Name L0_CADOUT - L1_CADIN            |     |

| Table 36. | Signals Sorted by Name L1_CADOUT - V33                 |     |

| Table 37. | Signals Sorted by Name VDD - VDD                       |     |

| Table 38. | Signals Sorted by Name VDD - VIOA                      |     |

| Table 39. | Signals Sorted by Name VIOB - VSS                      |     |

| Table 40. | Signals Sorted by Name VSS - VSS                       |     |

| Table 41. | Signals Sorted by Name VSS - VSS                       | 193 |

# **Revision History**

| Rev  | Date    | Description                                                                                                                                                                                                                      |

|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.07 | 07/2005 | Fourth public release Updated default register values in Chapter 3 to include revision B2 silicon. Bx indicates that a value is used for revision B1 and revision B2. Updates since Revision 3.00 are marked with revision bars. |

| 3.05 | 06/2005 | Third public release. Updated the OPN on page 195.                                                                                                                                                                               |

| 3.02 | 04/2005 | Second public release. Updates since Revision 3.00 are marked with revision bars.                                                                                                                                                |

| 3.0  | 03/2005 | Initial public release.                                                                                                                                                                                                          |

# **Preface**

This manual provides the technical specifications for the AMD-8132<sup>TM</sup> HyperTransport<sup>TM</sup> PCI-X<sup>®</sup>2.0 tunnel. Users of this document are expected to be familiar with current revs of the HyperTransport<sup>TM</sup> I/O link, PCI, and PCI-X protocols.

# **References and Resources**

HyperTransport™ I/O Link Specification, Rev 2.0

PCI-X Protocol Addendum to the PCI Local Bus Specification, Rev 2.0a

PCI-X Electrical and Mechanical Addendum to the PCI Local Bus Specification, Rev 2.0a

PCI Local Bus Specification, Rev 2.3

PCI Hot-Plug Specification, Rev 1.1

PCI Bus Power Management Interface Specification, Rev 1.1

PCI-to-PCI Bridge Architecture Specification, Rev 1.2

PCI Standard Hot-Plug Controller and Subsystem Specification, Rev 1.0

TPS2340A Dual-Slot PCI Hot-Plug Power Controller Product Data

82093AA I/O Advanced Programmable Interrupt Controller (IOAPIC) Product Data

# **Conventions**

- HyperTransport, HyperTransport™ technology, and HyperTransport™ all refer to the same technology (formerly LDT).

- For any signal, the suffix L indicates it is an active low.

- [B,A] in the signal name refers to the B and A PCI bridges or buses.

- [1,0] in the signal name refers to sides 1 and 0 of the tunnel.

- [H,L] are the signals associated with the positive and negative sides of differential pairs.

- Configuration register sets are provided for each logical bridge. Configuration register locations are referenced with mnemonics that take the form of Dev[A|B]:[7:0]x[FF:0] where the first bracket contains the bridge, the second bracket contains the function number, and the last bracket contains the offset.

# **Acronyms and Terms**

| Acronym/Term | Description                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|

| ADQ          | A 128-byte aligned data quantum as defined by the PCI-X specification, rev 2.0a.                                                     |

| Cell         | 32 bits of CAD aligned to a 32-bit boundary in the HyperTransport™ protocol with associated CTL bit.                                 |

| CFF          | Clock Forwarding FIFO.                                                                                                               |

| DDR          | In the case of PCI-X <sup>®</sup> Mode 2, this data transfer rate is two times the common clock.                                     |

| DEST         | Destination.                                                                                                                         |

| DM           | Interrupt destination mode.                                                                                                          |

| DS           | Downstream, away from the host bridge. Also Delivery Status.                                                                         |

| DW           | 32 bits.                                                                                                                             |

| GCM          | Link interface cycle manager.                                                                                                        |

| IM           | Interrupt Mask.                                                                                                                      |

| IOAPIC       | I/O Advanced Programmable Interrupt Controller.                                                                                      |

| IRR          | Interrupt Request Register.                                                                                                          |

| IV           | Interrupt Vector.                                                                                                                    |

| LI           | AMD-8132™ tunnel HyperTransport™ interface. This interface is the data/command transfer mechanism between the links and the bridges. |

| LR[0,1]      | Link receive module.                                                                                                                 |

| LT[0,1]      | Link transmit module.                                                                                                                |

| Link         | Connection between two HyperTransport™ devices.                                                                                      |

| MT           | Interrupt message type.                                                                                                              |

| PD           | Pulldown.                                                                                                                            |

| PHY          | The physical interface layer of the AMD-8132™ tunnel.                                                                                |

| POL          | Polarity.                                                                                                                            |

| PU           | Pullup.                                                                                                                              |

| RDR          | Interrupt redirection register.                                                                                                      |

| SDR          | Single Data Rate. This data transfer rate is one time the common clock.                                                              |

| SHPC         | Standard Hot-Plug Controller                                                                                                         |

| TM           | Interrupt trigger mode.                                                                                                              |

14 Preface

| Acronym/Term | Description                                                                                              |

|--------------|----------------------------------------------------------------------------------------------------------|

| TPS*         | Combinatorial reference indicating both the TPS2340A and TPS2342 Texas Instruments hot-plug controllers. |

| US           | Upstream, toward the host bridge.                                                                        |

26792 Rev. 3.07 July 2005

16 Preface

# **Chapter 1 Functional Operation**

### 1.1 Overview

The AMD-8132<sup>TM</sup> HyperTransport<sup>TM</sup> PCI-X<sup>®</sup>2.0 tunnel provides interfaces to HyperTransport and to PCI-X.

The AMD-8132 tunnel contains a HyperTransport tunnel as defined in the *HyperTransport* IO *Link Specification, Rev. 2.0*. This tunnel consists of two HyperTransport interfaces: side 0 and side 1. HyperTransport packets can be passed through from one interface to the other (tunneled), or they can be accepted and responded to by this device.

The AMD-8132 tunnel contains two HyperTransport-to-PCI-X bridges as defined in the *HyperTransport*™ *Link Specification, Rev. 2.0; PCI Local Bus Specification, Rev 2.3; PCI-X Protocol Addendum to the PCI Local Bus Specification, Rev. 2.0a*; and *PCI-to-PCI Bridge Architecture Specification, Rev 1.2*.

HyperTransport packets can be accepted by the AMD-8132 tunnel and passed to one of the two PCI-X buses (bridged), or routed to configuration registers in each bridge.

PCI-X transactions can be accepted by the AMD-8132 tunnel and passed to the HyperTransport chain.

To system software, the AMD-8132 tunnel appears to contain two PCI devices, each of which contains a PCI-to-PCI bridge header as defined in the *PCI-to-PCI Bridge Architecture Specification, Rev 1.2*, with additions as defined in the *PCI-X Protocol Addendum to the PCI Local Bus Specification, Rev 2.0a*. Each bridge actually bridges between a HyperTransport chain (the primary bus) and a PCI-X bus (the secondary bus).

The AMD-8132 tunnel can be connected to the HyperTransport host device through either the side 0 or the side 1 HyperTransport link interface; this is the upstream link. The AMD-8132 tunnel can be attached directly to the host device, or there can be a chain of one or more additional HyperTransport tunnels between the upstream link and the host device. The other HyperTransport link interface on the AMD-8132 tunnel, the downstream link, may or may not be connected to another device or chain of devices.

Host-initiated transactions that do not target the AMD-8132 tunnel or the bridge flow through the tunnel to the downstream device if one exists. Transactions claimed by the device are passed to internal registers or to one of the PCI-X bridges.

- See section 3.1 for details about the software view of the AMD-8132 tunnel.

- See section 3.1.2 for a description of the register naming convention.

- See the AMD-8132<sup>TM</sup> HyperTransport<sup>TM</sup> PCI-X<sup>®</sup> 2.0 Tunnel Design Guide for additional information.

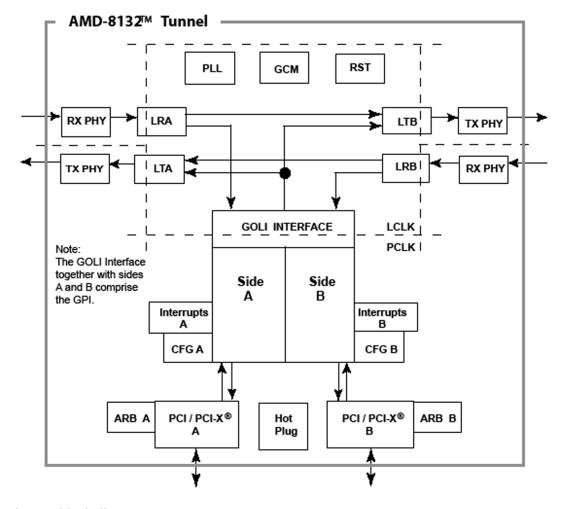

Figure 1. AMD-8132™ Tunnel: Block Diagram

In the Figure 1 block diagram:

- ARB [B,A] Internal arbiter for the PCI bus.

- CFG [B,A] Control and status registers for bridge [B,A].

- GCM Link interface cycle manager.

- GPI Bridge functions between the HyperTransport primary bus and the PCI/PCI-X secondary buses, split into a bridge B and a bridge A.

- Hot-Plug Interfaces to the external TPS2340A or TPS2342 hot-plug power controller and provides SHPC functions.

- INT [B,A] Interrupts/IOAPIC for bridge [B,A].

- LRx HyperTransport receive logic.

- LTx HyperTransport transmit logic.

- PCI/PCI-X [B,A] Interface and protocol state machines for PCI/PCI-X buses.

- PLL PLL that generates the core clock (LCLK) and the PCI clocks.

- RST Module that handles reset and device initialization.

- RX PHY HyperTransport link receive physical layer.

• TX PHY - HyperTransport link transmit physical layer.

Figure 2 shows buffers in the AMD-8132 tunnel.

Figure 2. Link Buffer Diagram

# 1.2 Tunnel Links

# 1.2.1 Link Frequency

Each HyperTransport link supports transmit clock frequencies of 200, 400, 500, 600, 800, and 1000 MHz. Side 0 and side 1 frequencies are independent of each other. The links can operate in asynchronous mode, as defined in *HyperTransport* I/O *Link Specification*, *Rev 2.0* up to a maximum of 1000 MHz receive clock rate. On cold reset, each link begins transmitting at 200 MHz and then can be reprogrammed for higher clock rates per *HyperTransport* I/O *Link Specification*, *Rev 2.0*.

#### 1.2.2 Link Width

Each HyperTransport link supports 2-bit, 4-bit, 8-bit, and 16-bit widths. Side 0 and side 1 widths are independent of each other. On cold reset, each link initializes its width as specified in the *HyperTransport* I/O Link Specification, Rev 2.0 and then can be reprogrammed.

#### 1.2.3 Link Behavior

After a cold or warm reset, the AMD-8132 tunnel initializes its base UnitID (see DevA:0xC0 in section 3.2) to 0. At this point it responds to HyperTransport configuration accesses to device 0 or 1, and passes any other HyperTransport commands on to the other link if the other HyperTransport link is active. Once the base UnitID register is initialized, the AMD-8132 tunnel responds to configuration accesses to this UnitID or this UnitID+1.

All HyperTransport memory or I/O operations pass through to the other HyperTransport link until the appropriate address ranges are programmed into the AMD-8132 tunnel. See section 3.2 PCI-X<sup>®</sup> Bridge Configuration Registers for details.

The first write to the base UnitID also sets the master host bit to point to the link that received this write, which also determines the default location of the upstream link.

# 1.2.4 Link PHY and Compensation

The electrical specification in *HyperTransport* TMI/O *Link Specification, Rev 2.0* requires an on-die differential termination as well as tightly controlled output impedance. The HyperTransport PHY used in the AMD-8132 tunnel maintains tight control of these parameters, regardless of temperature, voltage, or process variations. The HyperTransport PHY accomplishes this by the use of compensation circuitry. Each HyperTransport link has balls which are connected to external calibration resistors. By default, the PHY periodically samples calibration values and updates the receive and transmit parameters.

# 1.3 PCI-X<sup>®</sup>2.0 Bridges

The AMD-8132 tunnel includes two 64-bit PCI-X bridges, bridge A and bridge B. See Figure 1.

- Each bridge independently supports conventional PCI mode, or PCI-X Mode 1 or Mode 2.

- Each bridge independently supports clock speeds of 25, 33, 50, 66, 100, 133 MHz; and DDR with the common clock at 100 or 133 MHz.

- Each bridge independently supports SHPC-compatible hot-plug.

- Each bridge includes an interrupt controller register set.

- Each bridge supports 64-bit addressing in PCI-X and conventional PCI modes.

#### 1.3.1 Arbiters

#### 1.3.1.1 Internal Arbiters

Each bridge contains a PCI/PCI-X arbiter with five request/grant pairs available for each bus. Only a subset of these request/grant pairs are available for hot-plug, 66 MHz PCI, PCI-X Mode 1, or PCI-X Mode 2 operation. See section 4.2.3 for more details.

Depending on the current mode of the bus, the arbiter operates as a conventional PCI arbiter, a PCI-X Mode 1 arbiter, or a PCI-X Mode 2 arbiter. In PCI-X Mode 2 there are CSRs controlling the number of idle cycles before the arbiter goes into low-power mode. See section 3.2, Dev[B,A]:0x48.

The arbiter arbitrates between the external requests, represented by [B,A]\_REQ\_L[4:0], and internal requests. Internal requests are generated when:

- A HyperTransport operation is accepted by the bridge and will be forwarded to the PCI bus (the bridge wants to be master on the PCI bus).

- A hot-plug command occurs which requires the SHPC to own the PCI bus.

When no internal or external requests are asserted to the arbiter, it parks (asserts a grant) to one master in order to keep the bus from floating. The choice of master is controlled by Dev[B,A]:0x48[PARKATHOST].

#### 1.3.1.2 External Arbiters

An external arbiter can be used in all PCI and PCI-X modes except for PCI-X Mode 2. The internal arbiter for the AMD-8132 tunnel can be disabled and an external customer-supplied arbiter used instead. Disabling the internal arbiter can be done on a per PCI bus basis using the setting for EXTARB L at Dev[B,A]:0x48.

In external arbiter mode, the AMD-8132 tunnel produces a non-preemptable and a preemptable request.

- A non-preemptable request is a request to own the PCI bus for hot-plug. Once asserted, the external arbiter must keep its non-preemptable grant asserted until the AMD-8132 tunnel deasserts its non-preemptable request. The external arbiter should not park the bus on this grant line. The non-preemptable request comes out on the signal [B,A]\_GNT\_L1. The non-preemptable grant from the external arbiter is driven to the AMD-8132 tunnel on the signal [B,A]\_REQ\_L1. If this bus is not enabled for hot-plug, the non-preemptable request/grant lines do not need to be implemented and this grant line should be pulled high.

- A preemptable request is a request to own the PCI bus for normal usage. The preemptable request and grant behave as normal PCI or PCI-X request and grant signals. The preemptable request comes out on the signal [B,A]\_GNT\_L0. The preemptable grant from the external arbiter is driven to the AMD-8132 tunnel on the signal [B,A]\_REQ\_L0.

# 1.3.2 Interrupts

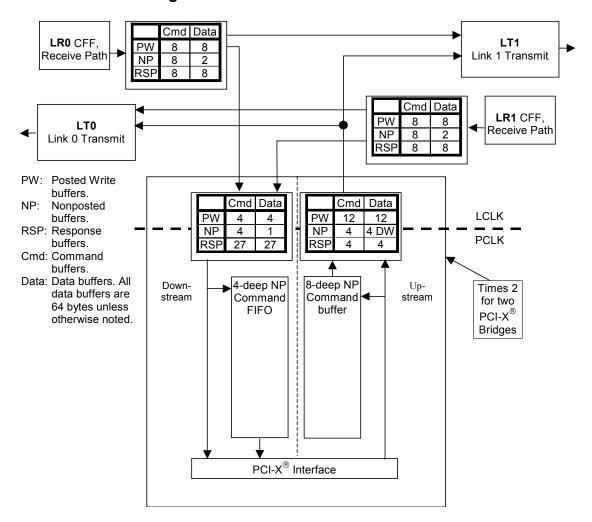

The AMD-8132 tunnel has capabilities to handle internal and external interrupts. It contains a standard IOAPIC and can accept Message Signalled Interrupts (MSIs) from the PCI buses. Incoming interrupts can result in HyperTransport interrupt packets, HyperTransport virtual wire packets, or assertions of the NIOAIRQ pins. Figure 3 shows interrupt routing possibilities.

Figure 3. AMD-8132™ Tunnel Interrupt Routing

# 1.3.2.1 Interrupt Discovery and Configuration

The HyperTransport interrupt discovery and configuration capability block defines the mechanism for declaring the number of interrupt sources for each bridge and allows software to configure each interrupt independently. Each bridge has its own capability block to facilitate mapping interrupt sources to HyperTransport interrupt packets. If existing software cannot use this mapping, then see *HyperTransport* TMI/O *Link Specification, Rev 2.0,* Appendix F.1.4 and section 3.6 herein for APIC compatible interrupt configuration. This alternative method of configuring and mapping interrupts utilizes a standard set of IOAPIC registers. Each bridge has an associated set of IOAPIC registers that includes a standard PCI function header (function 1 of each bridge) and memory mapped registers. This mapping provides an alternate way to access a subset of the interrupt discovery and configuration register set.

Each bridge supports the four PCI-defined interrupt signals, [B,A]\_PIRQ[D,C,B,A]\_L. Assertion of these interrupt signals may be converted to link interrupt request messages or cause assertion of the

NIOAIRQ[D:A]\_L pins. It is expected that system BIOS sets both Dev[B,A]:0x40[NIOAMODE] bits and that the interrupt is determined by the way the operating system programs the interrupt mask bit RDR[IM] of the redirection registers. Non IOAPIC-capable operating systems will not modify the indexing and mask bits of the redirection registers RDR[IM] and interrupts will continue to be delivered through NIOAIRQ[D:A]\_L assertions or Virtual Wire INTx packets, as set up by the BIOS. IOAPIC-capable operating systems clear the mask bits resulting in interrupt request messages to the host. The NIOAIRQ[D:A]\_L signals from all instances of the AMD-8132 tunnel on a platform can be connected together; respectively: A to A, B to B, etc. These four nodes are expected to be passed to the system's legacy interrupt controller to generate interrupts on behalf of the AMD-8132 tunnel bridges when IOAPIC interrupts are not supported.

Typically for PCI interrupts, the redirection register (RDR; see section 3.6) is set up as follows: MT = fixed; DM = physical mode; POL = active low; TM = level sensitive; and IM = not masked. The RDR fields are mapped into link interrupt request messages as follows:

RDR Field Field in HyperTransport Link Packet

IV[7:0] (Interrupt Vector) Vector (bit time 5)

MT[2:0] (Message Type) MT[2:0] (bits[4:2] of bit time 3); MT[3] (bit[7] of bit time 3) should always be

low. The encoding of these bits changes between the value in the RDR and the value placed into the link packet because HyperTransport and the APIC stan-

dard use different encodings for MT.

DM (Destination Mode) DM (bit[6] of bit time 3)

TM (Trigger Mode) RQEOI (bit[5] of bit time 3)

DEST[7:0] (Destination) IntrInfo[15:8] (bit time 4); IntrInfo[55:16] should always be low.

DS, POL, IRR, and IM from the RDR are not included in the HyperTransport link interrupt packet.

The state of PASSPW and INTRINFO[55:24, 7] from the IDRDR register (see Dev[B,A]:0x[BC, B8]) are also passed along in the link interrupt packet.

If RDR[TM] = level sensitive for the interrupt request, then the IRR register is set when the interrupt is detected. After the interrupt request message is sent to the host, the host is required to generate an EOI broadcast or CSR write message when finished with that interrupt. IRR is cleared in any RDRs in either bridge with IDRDR/RDR fields that match the IntrInfo fields of the EOI broadcast as follows:

IntrInfo[15:8] Match fields

$00h IntrInfo[31:16] = \{IDRDR[31:24], RDR/IDRDR[IV]\}$

01h-FFh IntrInfo[31:8] = {IDRDR[31:24], RDR/IDRDR[IV], RDR/IDRDR[DEST]}

If the interrupt signal is still asserted when the corresponding RDR logic receives an IRR-clearing EOI, then IRR is immediately set again and a new interrupt request message is sent. If the interrupt signal is deasserted near the time the corresponding IRR-clearing EOI is received, then it is undefined whether an additional interrupt request message is sent. If RDR[TM] = edge sensitive, then the state of the IRR bit is not specified and the RDR logic for that interrupt does not observe EOIs.

Each RDR in the AMD-8132 tunnel operates independently. If interrupts are received simultaneously by two RDR controllers, then the corresponding interrupt request messages from each are transmitted in an unspecified order. If LDTSTOP L is asserted near the time that an interrupt is asserted, then the corresponding

interrupt request message may or may not be sent before the disconnect sequence completes. If it is not sent before the disconnect sequence completes, then it is not dropped; it is sent after the link is re-connected.

External devices are required to assert PIRQ[D:A]\_L for at least 3 PCLK cycles in order to guarantee that the AMD-8132 tunnel detects the assertion, regardless of the state of the corresponding RDR[TM] field.

### 1.3.2.2 SHPC\_INTR and Fatal/Nonfatal Interrupts

In addition to the four PCI interrupt pins on each PCI bus, each bridge contains three internal signals that can generate interrupts. These are the SHPC\_INTR signal and the fatal and nonfatal error signals. For each of these three signals there is an Interrupt Definition register/IOAPIC entry, yielding a total of seven for each bridge. See section 3.7 for more about SHPC\_INTR. See Chapter 5 for more about error reporting.

### 1.3.2.3 Message Signalled Interrupts (MSI/MSI-X)

The AMD-8132 tunnel responds to MSIs (as specified in *PCI Local Bus Specification, Rev 2.3*, section 6.8) and MSI-Xs (as specified in *PCI Local Bus Specification, Rev 3.0*, section 6.8) with the following restriction imposed by HyperTransport:

MSI/MSI-X transactions are treated as such only if Dev[B,A]:0xF4[MSI\_ENABLE] is set and if bits [63:20] of the address match the address created by concatenating Dev[B,A]:0xFC[UPPER\_ADDRESS] with Dev[B,A]:0xF8[LOWER\_ADDRESS]. Otherwise, they are treated as posted memory writes.

MSI/MSI-X transactions result in a HyperTransport interrupt packet. The address and data from the MSI/MSI-X transaction are distributed across that packet according to Table 1.

| Table 1. | MSI/MSI-X Mapping: PCI to HyperTransport™ |

|----------|-------------------------------------------|

|----------|-------------------------------------------|

| MSI/MSI-X Field           | HyperTransport™ Interrupt Field          |

|---------------------------|------------------------------------------|

| Address[2], Data[15,10:8] | IntrInfo[6:2] (x86 DM, RQEOI, MT[2:0])   |

| Address[19:12]            | IntrInfo[15:8] (x86 Destination[7:0])    |

| Data[7:0]                 | IntrInfo[23:16] (x86 Vector)             |

| Address[11:4]             | IntrInfo[39:32] (x86 Destination[15:8])  |

| Address[30:20]            | IntrInfo[50:40] (x86 Destination[26:16]) |

| Address[3]                | IntrInfo[51] (x86 Destination[27])       |

| Data[14:11]               | IntrInfo[55:52] (x86 Destination[31:28]) |

|                           | ·                                        |

#### Notes:

- 1. Data[15]/IntrInfo[5] (x86 RQEOI) must be set to 0 by software in PCI and PCI-X devices because they do not receive HyperTransport EOI (End of Interrupt) broadcasts.

- 2. Data[10:8]/IntrInfo[4:2] (x86 Message Type) can be either 000b for fixed destination delivery or 001b for lowest priority delivery.

- 3. IntrInfo[7] (x86MT[3]) is 0b.

- 4. IntrInfo[31:24] is F8h.

For more information see PCI Local Bus Specification, Rev 2.3, section 6.8.

### 1.3.2.4 INTx Virtual Wire Messages

There is an alternative method of delivering interrupt information over HyperTransport. Transitions on the PCI interrupt pins can cause INTx virtual wire packets to be issued on the upstream HyperTransport link instead of HyperTransport interrupt packets. Generation of INTx virtual wire packets is enabled with Dev[B,A]:0x48 [INTx PACKET EN].

# 1.3.3 Write Chaining

Write chaining refers to issuing two or more write requests from the HyperTransport bus as a single PCI or PCI-X operation. Write chaining is used to maximize available PCI or PCI-X bandwidth by avoiding the protocol overhead of issuing multiple operations that would each have its own address/attribute phases, wait states, and turnaround cycles.

The AMD-8132 tunnel implements chaining posted WrSized requests from the HyperTransport bus under the following conditions:

- The writes must be posted Doubleword WrSized requests (as opposed to byte-sized requests) that are all targeted to the same secondary PCI or PCI-X bus below the AMD-8132 tunnel. Doubleword WrSized requests from one to sixteen doublewords in size can be chained.

- The address of the last doubleword of one write must be adjacent to the address of the first doubleword of the subsequent write. The addresses spanned by the writes must not cross a 128-byte (32-doubleword) address boundary; e.g., a PCI-X ADB, although this restriction also applies to conventional PCI secondary buses.

- For the targeted AMD-8132 tunnel bridge, the WriteChainEnable bit Dev[B,A]:0x40[31] must be set.

- The data for all writes must have been received by the AMD-8132 tunnel internal buffers. A write whose data is still being transferred across the HyperTransport bus won't be chained.

- The writes must not have the COMPAT bit set in the HyperTransport request.

- The writes must not have data errors, or the Downstream Post Data Error Disable bit DevA:0xDC[6] must be set.

- The PassPW, UnitID, SeqID, Isoc, and Coherent attributes in the HyperTransport request packets must be the same for all writes in the chain.

If these conditions are all true when the AMD-8132 tunnel posted channel for one of its bridges wins internal arbitration over the nonposted and response channels to issue its traffic to the PCI or PCI-X bus, up to four WrSized requests from the HyperTransport bus are issued as as a single PCI Memory Write or Memory Write and Invalidate or PCI-X Memory Write Block operation.

# 1.3.4 Prefetching In Conventional PCI Mode

Prefetching refers to the acquisition of memory read data from the host prior to the master's request for the data. When using the internal arbiter, prefetching in conventional PCI mode is enabled on a per-master basis through Dev[B,A]:0x40[PFEN[4:0]\_L]. When using an external arbiter, the prefetching logic cannot distinguish between masters and all traffic is treated as if coming from master 0.

The following are definitions used in the rules for prefetching:

• Memory Read: any of the three PCI commands for reading memory - MR (Memory Read), MRL (Memory Read Line), or MRM (Memory Read Multiple). In this section, memory read is a collective term for all three types of reads. When a specific type of memory read is meant, its acronym is used.

- Burst Request: a cycle in which FRAME\_L is held asserted during the first clock in which IRDY\_L is asserted, indicating the master wishes to transfer more than one beat of data. In the event that STOP\_L is asserted before IRDY\_L asserts, FRAME\_L always deasserts as IRDY\_L asserts (*PCI Local Bus Specification, Rev 2.3*, section 3.3.3.2.1). In such case, the master's intention to burst cannot be determined and the AMD-8132 tunnel pessimistically treats such cycles as burst requests.

- Acquired Line: all or part of a requested line of data within a 64-byte aligned block that has made it back to the AMD-8132 tunnel from the HyperTransport interface.

- Requested Prefetch: the prefetch of up to a line of data in which the master has explicitly requested the line by initiating a transaction in which the address is within the prefetched line.

- Unrequested Prefetch: the speculative prefetch of a full line before a master has generated a transaction that includes the address of the line. If a master bursts up to the end of a requested prefetched line while keeping FRAME\_L asserted and the AMD-8132 tunnel disconnects with data at that point, then the next line is still considered an unrequested prefetch even though the master has attempted to burst into the next line. Even if a burst is sustained from a requested line through any or all of an unrequested line, the second line is not considered requested by the master. If after a disconnect before or during data phases of an unrequested line the master subsequently attempts to continue the burst and generates an address phase that resides within the unrequested line, then that line changes from an unrequested prefetch to a requested prefetch.

In general, the PCI specification indicates that MRLs and MRMs are always prefetchable; it is the responsibility of masters to issue them only to prefetchable targets. No such assumption can be made for MRs. If, by means outside the PCI specification, it is known that MRs issued by the devices on this bus are to prefetchable targets, then the Dev[B,A]:0x4C[MRPFEN] bit can be set to enable prefetching for MRs. In this case, the MRL prefetching controls are used to control MR prefetching as well.

When prefetching is disabled for a memory read request (either Dev[B,A]:0x40[PFEN\_L] deasserted for the particular master, or the request is an MR with Dev[B,A]:0x4C[MRPFEN] deasserted), these rules are followed:

- The AMD-8132 tunnel generates no unrequested prefetches.

- MRs with prefetching off are one DW, regardless of REO64 L, and never assert ACK64 L.

- If REQ64\_L is asserted, MRLs and MRMs with prefetching off assert ACK64\_L and fetch two DW from HyperTransport. If REQ64\_L is deasserted, only one DW is fetched.

When prefetching is enabled for a memory read request (Dev[B,A]:0x40[PFEN\_L] asserted for the particular master and Dev[B,A]:0x4C[MRPFEN] asserted if the request is an MR), these rules are followed:

- The AMD-8132 tunnel may contain between 0 and 8 cache lines of prefetched data for a memory read at one time.

- If not bursted, all types of memory reads assert ACK64\_L if REQ64\_L is asserted and fetch two DW from HyperTransport. If REQ64\_L is deasserted, only one DW is fetched.

- When there is a memory burst request, then the AMD-8132 tunnel sends out a requested prefetch of data starting from the transaction address up to the end of the line. Additionally, the AMD-8132 tunnel may send out 0 to 7 unrequested prefetches as controlled by Dev[B,A]:0x4C[IPF\_x] where x is either an MRL or MRM. Prefetch-enabled MRs use IPF\_MRL.

- As soon as the AMD-8132 tunnel completes transferring data for a given line, it may send another unrequested prefetch as controlled by Dev[B,A]:0x4C[CPFEN\_x] where x could be an MRL or MRM. Prefetch-enabled MRs use CPF MRL.

- In no event does prefetching continue past an address range boundary to an address for which the AMD-8132 tunnel would not be a PCI bus target. Range boundaries that are checked include:

- top of 64-bit memory address space

- top of 40-bit memory address space (FD 0000 0000h)

- non-prefetchable memory base, if enabled (Dev[B,A]:0x[D8,20])

- prefetchable memory base, if enabled (Dev[B,A]:0x[28,24])

- base of VGA memory space, if enabled (A 0000h)

- A requested prefetch is allowed to burst until it is complete or until the master terminates the burst.

- If the master terminates a burst, all requested and unrequested prefetch data is discarded if Dev[B,A]:0x4C[DPDMD L] is asserted for that master.

- If the AMD-8132 tunnel terminates a burst because the required next data line was not acquired and if Dev[B,A]:0x4C[DPDTD] is asserted, all unrequested prefetch data for that request is discarded as it arrives. Note that DPDTD should only be set if all Dev[B,A]:0x4C[20:16] DPDMD\_L bits are 0 for that bridge. Setting DPDTD when any DPDMD\_L bits are set may result in undefined behavior.

- If the discard timer times out for the initial data transfer, then all requested and unrequested prefetch data is discarded and Dev[B,A]:0x3C[DTS] is set and an error may be signalled.

- If a burst is terminated for any reason and the data is not discarded, a separate discard timer value controlled by Dev[B,A]:0x4C[URP\_TIMER] is used for reconnections. This timer measures the time between the point of disconnection to when the master attempts to reconnect, regardless of whether the AMD-8132 tunnel has acquired the data. The timer restarts every time reconnection is attempted, whether or not data is transferred. If the timer expires, all prefetched data is discarded but no error is logged.

- The Dev[B,A]:0x4C[MRD\_ALIAS] bit can be asserted to relax the requirements for reconnection. For example, if the bit is set and a master issues an MRM for a long burst but then switches to MRL to complete the burst after being disconnected near the end, the MRL will be allowed to reconnect and receive the unrequested prefetch data fetched by the MRM.

- Prefetching automatically stops when a memory window boundary defined by the configuration registers is reached. Optionally, based on Dev[B,A]:0x4C[PFDISC 4K] the prefetch stops on 4-K boundaries.

- If Dev[B,A]:0x4C[DPDH] is asserted, all unrequested prefetch data is discarded when a host request is issued by the AMD-8132 tunnel onto the PCI bus.

- If Dev[B,A]:0x4C[DPDMAC] is asserted, all unrequested prefetch data for a particular master is discarded if that master issues a read request that does not hit the acquired lines.

- The AMD-8132 tunnel can prefetch for up to eight PCI requests at a time, limited by Dev[B,A]:0x4C[OUTSTDELREQ]. Additionally, Dev[B,A]:0x4C[SDRPM] can be set to prevent a single master from having more than one outstanding request. If a request is received that would violate either of these limits, it is retried.

Prefetch CSR values should not be changed while reads from the PCI bus to HyperTransport are outstanding or the resulting behavior is undefined. The PCI bus should be quiesced and any active buffers allowed time to discard before CSR values are changed.

# 1.3.5 HyperTransport™ Requests Claimed by the Bridges

The bridges claim no upstream HyperTransport requests, but do claim the following downstream HyperTransport requests if the COMPAT bit is clear:

- All requests to memory and I/O space specified by Dev[B,A]:0x[30:1C] if Dev[B,A]:0x04[MEMEN, IOEN] are set.

- All configuration and extended configuration requests to the implemented functions of DevA or DevB (also see section 3.1.1).

- All configuration and extended configuration requests to buses behind bridge A or bridge B.

- All EOI broadcasts.

- All Stop Grant and STPCLK broadcasts (see section 4.1.2).

The bridges never claim a HyperTransport device message.

If the COMPAT bit is set and DevA:0x48[COMPAT] = 1, then all memory space, I/O space, and interrupt acknowledge requests are claimed and passed to bridge A.

If the COMPAT bit is set in the transaction and DevA:0x48[COMPAT] = 0, then per the HyperTransport link protocol the AMD-8132 tunnel never claims the transaction. Such transactions are automatically passed to the other side of the tunnel or master aborted if the AMD-8132 tunnel is at the end of the chain.

# 1.3.6 Transaction Considerations

#### 1.3.6.1 General

The following are general considerations for AMD-8132 tunnel transactions:

- The PCIXCAP pins are implemented as described in *PCI-X Protocol Addendum to the PCI Local Bus Specification, Rev 2.0a.*

- PCI cache line wrap mode is not supported. If a transaction is initiated that indicates this protocol, it is disconnected at the cacheline boundary.

- PCI-X transactions that cross address space boundaries as defined by the window configuration registers Dev[B,A]:0x[30:1C] result in undefined behavior.

- If there is a downstream nonposted request to PCI-X that results in a device-specific error in a completion message, then the response passed to the link indicates a target abort.

- When the AMD-8132 tunnel asserts [B,A]\_DEVSEL\_L, it does so as a medium decode speed device in conventional PCI mode and decode speed B device in PCI-X Mode 1 and Mode 2.

- If there is a HyperTransport transaction to I/O or configuration space that targets one of the bridges or is claimed by that bridge and it crosses a naturally aligned doubleword (dword) boundary, then the AMD-8132 tunnel does not send the transaction to the bus and the HyperTransport response is a target abort. Any I/O or config transactions not claimed by the AMD-8132 tunnel are forwarded to the next device on the HyperTransport chain, regardless of the alignment and length.

# 1.3.6.2 Pullups on Upper PCI Bus

While in conventional PCI mode or PCI-X Mode 1, the upper half of the PCI bus [B,A]\_AD[63:32], [B,A]\_CBE\_L[7:4], and [B,A]\_PAR64, is pulled high with weak pullups per *PCI Local Bus Specification, Rev* 2.3, section 3.8.1. These pullups are disabled for PCI-X Mode 2 or if Dev[B,A]:0x40[DISPU] is asserted.

# 1.3.6.3 Upstream Transactions

The following apply to AMD-8132 tunnel upstream transactions:

- The AMD-8132 tunnel requires two HyperTransport-defined UnitIDs. The first UnitID applies to bridge A. The second UnitID applies to bridge B and is contained in the following HyperTransport transactions:

- External master requests associated with the bridge.

- Interrupt requests associated with the bridge.

- Responses to host-initiated requests that enter the address space of the bridge including configuration registers (DevA registers for bridge A and DevB registers for bridge B); secondary I/O

or memory spaces; configuration space windows defined in the configuration registers of the bridge; and the base address register spaces defined by the bridge.

The UnitID associated with the bridge is also returned in the response to upstream requests and is used to determine the destination of the response (bridge A or bridge B).

- Upstream PCI-initiated memory writes which include no valid byte enables complete normally over the PCI bus. However, the transaction may be dropped by the AMD-8132 tunnel resulting in no corresponding HyperTransport link transactions. This does not apply to I/O transactions.

- Secondary bus configuration cycles are never claimed by the AMD-8132 tunnel; including configuration cycles to device 31 in which special cycles are encoded per the *PCI-to-PCI Bridge Architecture Specification, Rev 1.2*.

- PCI-X Device ID Messages (DIMs) are never claimed by the AMD-8132 tunnel.

- For each bridge, up to 27 nonposted requests to the link may be outstanding at a given time. Based on the state of Dev[B,A]:0x40[NZSEQID], the AMD-8132 tunnel may or may not generate non-zero SeqID values in the upstream link requests that result from external PCI/PCI-X master read requests. Up to 8 outstanding PCI/PCI-X read sequences can be active at one time. If enabled, each outstanding secondary read sequence is assigned a unique SeqId from 8h to Fh. All bridge-sourced transactions are compliant to PCI or PCI-X ordering rules. As PCI or PCI-X transactions are converted to link transactions, they are translated as described in *HyperTransport*\*\*I/O Link Specification, Rev 2.0.

- The HyperTransport coherent bit in upstream requests is always set for interrupt requests (including MSI/MSI-X transactions) and all requests from the secondary bus when it is in PCI mode. If the secondary bus is in PCI-X mode, the HyperTransport coherent bit is the inverse of the no snoop bit from the PCI-X request.

The following comparisons show the relationship between PCI-X transactions in which the relaxed ordering bit is set and link packets:

| Upstream PCI-X <sup>®</sup> 2.0 Transaction                                                                                  | Corresponding Link Transaction                                                           |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| A memory write request in which the relaxed ordering bit of the attribute field is set.                                      | PassPW is set in the request.                                                            |

| A read request in which the relaxed ordering bit of the attribute field is set.                                              | Bit[3] of the command field (response may pass posted write) in the read request is set. |

| Any response to a downstream link read request in which bit[3] of the command field (response may pass posted write) is set. | PassPW is set in the response.                                                           |

#### 1.3.6.4 Downstream Transactions

The following apply to AMD-8132 tunnel downstream transactions:

- Downstream special cycles that are encoded in configuration cycles to device 31 of the bridge secondary bus number (per the *PCI-to-PCI Bridge Architecture Specification, Rev 1.2*) are translated to special cycles on the PCI bus.

- In the translation from type 1 HyperTransport link configuration cycles to secondary bus type 0 configuration cycles, the AMD-8132 tunnel converts the device number to an IDSEL AD signal as follows: device 0 maps to AD[16]; device 1 maps to AD[17]; and so forth. Device numbers 16 through 31

are not valid. When Dev[B,A]:0x40[SSS\_L] is low, a config access to device 1 also causes [B,A] GNT L1 to be asserted. See section 2.6.

In a system capable of operating in PCI-X Mode 2, there can only be one slot. The IDSEL signal for this slot should be attached to [B,A]\_GNT\_L1, which has the alternative function of IDSEL for device 1 while Dev[B,A]:0x40[SSS L] is asserted (low).

- If the bus number matches the secondary bus number of the bridge, HyperTransport type 1 accesses and extended HyperTransport type 1 accesses are forwarded onto the PCI/PCI-X bus as type 0 accesses. If the bus number is greater than the secondary bus number of the bridge and less than or equal to the subordinate bus number of the bridge, HyperTransport type 1 accesses and extended HyperTransport type 1 accesses are forwarded onto the PCI/PCI-X bus as type 1 accesses.

- If the PCI/PCI-X bus is not operating in PCI-X Mode 2 and if an extended HyperTransport type 1 access attempts to access a register number above 255, the operation is dropped and a response returned as if it was master aborted on the PCI/PCI-X bus.

- HyperTransport device messages are never claimed by the AMD-8132 tunnel.

- Downstream nonposted HyperTransport link requests to a PCI/PCI-X bus that contain non-zero SeqID values are required to complete on that bus prior to initiating subsequent nonposted requests with the same SeqID value to that PCI/PCI-X bus. Consequently, only one downstream nonposted request with each non-zero SeqID value can be outstanding on a PCI/PCI-X bus at a time.

- The PCI-X no snoop bit is the inverse of the HyperTransport coherent bit for downstream memory requests. For downstream nonmemory requests, no snoop is always be 0.

The following comparisons show the relationship between PCI-X transactions in which the relaxed ordering bit is set and link packets:

| Downstream Link Transaction                                                                  | Corresponding PCI-X <sup>®</sup> 2.0 Transaction                                                        |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| A posted memory write request with PassPW set.                                               | Relaxed ordering bit of the attribute field is set.                                                     |

| A read request in which bit[3] of the command field (response may pass posted write) is set. | Relaxed ordering bit of the attribute field is set.                                                     |

| A response to an upstream request.                                                           | Relaxed ordering bit of the attribute field is copied from the attribute field of the original request. |

# 1.3.7 Hot-Plug

Note: Where information in this section applies to both the TPS2340A and TPS2342 hot-plug controllers, they are referred to combinatorially as TPS\* in the text.

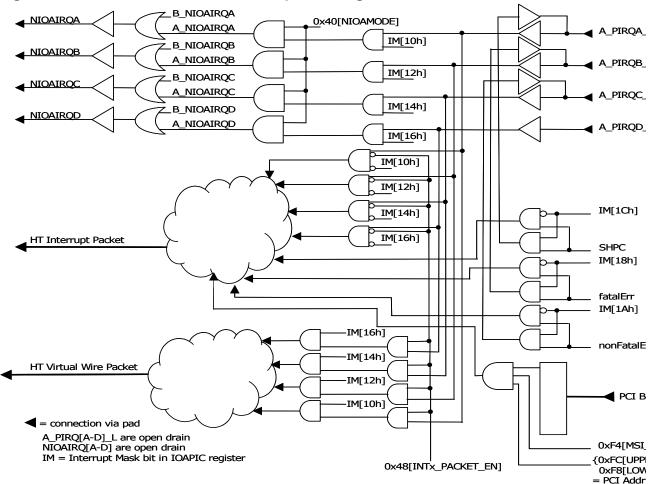

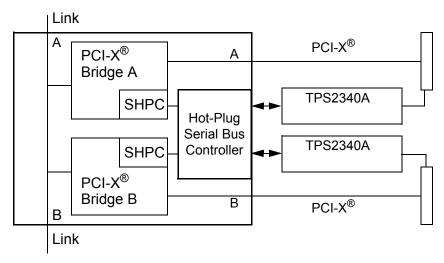

Each PCI-X bridge includes an SHPC-compliant hot-plug controller that may be used to support hot-plug capable PCI-X or conventional PCI slots. Strapping options on [B,A]\_REQ\_L4 specify whether hot-plug is supported on bridge A and bridge B. If hot-plug is supported on a bridge, then all slots connected to that bridge are required to include hot-plug support circuitry. With the exception of a single-slot hot-plug implementation, the hot-plug support circuitry includes one or more TPS\* hot-plug power controllers, power switches, and associated slot isolation switches to provide electrical isolation for most of the slot signals. For a single-slot hot-plug implementation, the AMD-8132 tunnel provides the bus isolation function so only the TPS\* hot-plug power controller and the power switches are required. Each bridge supports a maximum of 4 slots when hot-plug mode is enabled.

The hot-plug controller is designed to interface with either TPS\*. The TPS2342 must be used if PCI-X Mode 2 hot-plug is supported. A strapping option on HPSOD indicates whether the TPS2340A or TPS2342 is used. Each TPS\* controls two slots and provides two separate sets of isolation switch controls. TPS\* controllers can be cascaded to support additional slots. If the TPS2340A is used, a single hot-plug power controller cannot be shared across bridge A and bridge B. If the TPS2342 is used, a single hot-plug power controller can be shared by bridge A and bridge B. The AMD-8132 tunnel is connected to the power controller via a serial bus. If the TPS2340A is used, one serial interface supports the power controllers for bridge A and bridge B. If the TPS2342 is used, there are two serial interfaces - one for each bridge.

#### **Multi-Slot Hot-Plug** 1.3.7.1

Note: Where information in this section applies to both the TPS2340A and TPS2342 hot-plug controllers, they are referred to combinatorially as TPS\* in the text.

If multiple hot-plug slots are supported on a bridge, isolation switches are required for each slot to provide electrical isolation. Each TPS\* hot-plug power controller provides two pairs of isolation switch control signals, BUSENx L and CLKENx L, to control the state of the switches.

PCI-X® Link Α PCI-X® Bridge A Α Hot Plug SHPC \*Power Power and Serial Controllers **Isolation Control** Bus Controller SHPC PCI-X® Bridge B В В ⊗- Isolation Switch  $PCI-X^{\mathbb{R}}$